Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx170f512lt-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: PIN NAMES FOR 100-PIN USB DEVICES (CONTINUED)

| 10    | 0-PIN TQFP (TOP VIEW)                                                                                          |     |       |                           |

|-------|----------------------------------------------------------------------------------------------------------------|-----|-------|---------------------------|

|       | PIC32MX230F128L<br>PIC32MX530F128L<br>PIC32MX250F256L<br>PIC32MX550F256L<br>PIC32MX270F512L<br>PIC32MX570F512L |     |       | 100                       |

|       |                                                                                                                |     |       | 1                         |

| Pin # | Full Pin Name                                                                                                  |     | Pin # | Full Pin Name             |

| 71    | RPD11/PMA14/RD11                                                                                               | 1 1 | 86    | VDD                       |

| 72    | RPD0/INT0/RD0                                                                                                  | ĪĪ  | 87    | AN44/C3INA/RPF0/PMD11/RF0 |

| 73    | SOSCI/RPC13/RC13                                                                                               | ĪĪ  | 88    | AN45/RPF1/PMD10/RF1       |

| 74    | SOSCO/RPC14/T1CK/RC14                                                                                          | t t | 89    | RPG1/PMD9/RG1             |

| 75    | Vss                                                                                                            | Ī   | 90    | RPG0/PMD8/RG0             |

| 76    | AN24/RPD1/RD1                                                                                                  | 11  | 91    | RA6                       |

| 77    | AN25/RPD2/RD2                                                                                                  | 11  | 92    | CTED8/RA7                 |

| 78    | AN26/C3IND/RPD3/RD3                                                                                            | ] [ | 93    | AN46/PMD0/RE0             |

| 79    | AN40/RPD12/PMD12/RD12                                                                                          | [   | 94    | AN47/PMD1/RE1             |

| 80    | AN41/PMD13/RD13                                                                                                | [   | 95    | RG14                      |

| 81    | RPD4/PMWR/RD4                                                                                                  | [   | 96    | RG12                      |

| 82    | RPD5/PMRD/RD5                                                                                                  | [   | 97    | RG13                      |

| 83    | AN42/C3INC/PMD14/RD6                                                                                           | ] [ | 98    | AN20/PMD2/RE2             |

| 84    | AN43/C3INB/PMD15/RD7                                                                                           | [   | 99    | RPE3/CTPLS/PMD3/RE3       |

| 85    | VCAP                                                                                                           | [   | 100   | AN21/PMD4/RE4             |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 3 and MPLAB REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- *"Using MPLAB<sup>®</sup> ICD 3"* (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- *"MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide"* DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

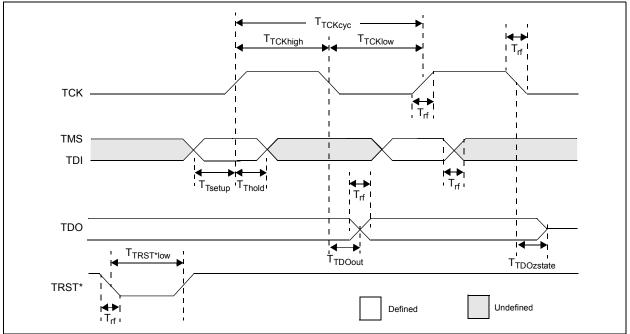

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer or debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements

## 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

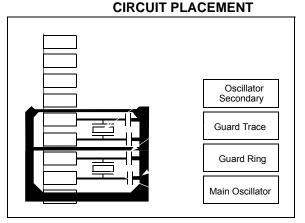

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

# FIGURE 2-3: SUGGESTED OSCILLATOR

<sup>© 2014-2016</sup> Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | —                 | _                 | _                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 |                   | _                 | _                 | —                 | —                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXDK             | PBA<15:8>         |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXDK             | PBA<7:0>          |                   |                  |                  |

#### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

# Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | —                 |                   | _                 |                   |                  |                  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 |                   | -                 |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | _                 | _                 |                   | -                 |                   |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7.0          |                   |                   |                   | _                 |                   |                   | FRMH<2:0>        |                  |

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| J                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_ \_\_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

- 0001 = OUT (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 1101 = SETUP (TX) token type transaction

- Note: All other values are reserved and must not be used.

- bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

**Note 1:** All other values are reserved and must not be used.

|                             |                                 | P         |       | 170551 | 2H DEV | ICES O | NLY   |       |      |      |      |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|--------|--------|--------|-------|-------|------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 |           |       |        |        |        |       |       |      | Bi   | ts   |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14  | 29/13  | 28/12  | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | —     | _      | —      | _      | —     | _     | _    | —    | -    | —            |              | _            | _            | _            | —            | —            | 0000          |

| 0010                        | INIO                            | 15:0      | —     | _      | _      | _      | _     | _     | -    | _    | -    | TRISF6       | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | 007F          |

| 6520                        | PORTF                           | 31:16     | —     | —      | —      |        | —     | _     |      |      |      |              | —            |              | —            | —            | —            | —            | 0000          |

| 0020                        | 1 OKI                           | 15:0      | —     | —      | —      |        | —     | _     | _    |      |      | RF6          | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | —     | _      | _      | _      | _     | _     | -    | _    | -    | —            | —            | -            | —            | _            | —            | —            | 0000          |

| 0000                        | L/(II                           | 15:0      | —     | —      | —      |        | —     | _     | _    |      |      | LATF6        | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | —     | —      | —      | _      | —     | _     | —    | _    | —    |              | —            | _            | —            | —            | —            | —            | 0000          |

| 0010                        | 0201                            | 15:0      | —     | —      | —      | _      | —     | _     | —    |      | —    | ODCF6        | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | 0000          |

| 6550                        | CNPUF                           | 31:16     | —     | _      | —      | —      | —     | —     | _    | —    | _    |              | —            | —            | —            | —            | —            | —            | 0000          |

| 0000                        |                                 | 15:0      | —     | _      | —      | —      | —     | —     | _    | —    | _    | CNPUF6       | CNPUF5       | CNPUF4       | CNPUF3       | CNPUF2       | CNPUF1       | CNPUF0       |               |

| 6560                        | CNPDF                           | 31:16     | —     | —      | —      | _      | —     | _     | —    |      | —    |              | —            | —            | —            | —            | —            | —            | 0000          |

|                             | 0.11 51                         | 15:0      | —     | —      | —      | _      | —     | —     | -    | —    | -    | CNPDF6       | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | 0000          |

| 6570                        | CNCONF                          | 31:16     | —     | —      | —      | _      | —     | —     | -    | —    | -    | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             | 0.10011                         | 15:0      | ON    | —      | SIDL   | _      | —     | —     | -    | —    | -    | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | —      | —      | _      | —     | —     | -    | —    | -    |              | —            | —            | —            | —            | —            | —            | 0000          |

|                             | -                               | 15:0      | —     | —      | —      | _      | —     | —     | -    | —    | -    | CNIEF6       | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | 0000          |

|                             |                                 | 31:16     | —     | —      | —      | —      | —     | _     | _    | —    | _    |              | —            | —            | —            | —            | —            | —            | 0000          |

| 6590                        | CNSTATF                         | 15:0      | —     | —      | —      | -      | —     | -     | -    | —    | _    | CN<br>STATF6 | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | 0000          |

# TABLE 11-13: PORTF REGISTER MAP FOR PIC32MX120F064H, PIC32MX130F128H, PIC32MX150F256H, AND PIC32MX170F512H DEVICES ONLY

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| ss                          |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |      |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

|                             |                  | 31:16     | -     | _     | _     | _     | -     | _     | _    | -    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FBFC                        | RPD15R           | 15:0      | _     |       |       | _     |       |       |      |      |      | _    | _    |      |      | RPD1 | 5<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FC0C                        | RPE3R            | 15:0      | _     | _     |       | _     | _     | _     | _    | _    |      | —    | _    | _    |      | RPE  | 3<3:0> |      | 0000       |

| 50.1.1                      |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FC14                        | RPE5R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPE  | 5<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FC20                        | RPE8R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPE  | 3<3:0> |      | 0000       |

| 5001                        | 00540            | 31:16     | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | _    | _    | _    | —    | _      | —    | 0000       |

| FC24                        | RPE9R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPES | )<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | —     | _     | _    | —    | _    | _    | _    | _    | _    | —    | _      | _    | 0000       |

| FC40                        | RPF0R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPFC | )<3:0> | •    | 0000       |

|                             | 00540            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FC44                        | RPF1R            | 15:0      | _     | _     | _     | _     | —     | _     | _    | —    | _    | _    | _    | _    |      | RPF1 | <3:0>  | •    | 0000       |

| 50.00                       |                  | 31:16     | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | _    | _    | _    | —    | _      | —    | 0000       |

| FC48                        | RPF2R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF2 | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | —     | _     | _    | —    | _    | _    | _    | _    | _    | —    | _      | _    | 0000       |

| FC4C                        | RPF3R            | 15:0      | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | _    | _    |      | RPF3 | 8<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FC50                        | RPF4R            | 15:0      | _     | _     | _     | _     | —     | _     | _    | —    | _    | _    | _    | _    |      | RPF4 | <3:0>  | •    | 0000       |

|                             | 00550            | 31:16     | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      | —    | 0000       |

| FC54                        | RPF5R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF5 | <3:0>  |      | 0000       |

| 5050                        | DDCAD            | 31:16     | _     | _     | _     | —     | —     | —     | —    | —    | _    | —    | —    | —    | _    | —    | —      | —    | 0000       |

| FC58                        | RPF6R            | 15:0      | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | _    | _    |      | RPF6 | 6<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | —     | _     | _    | —    | _    | _    | _    | _    | _    | —    | _      | _    | 0000       |

| FC5C                        | RPF7R            | 15:0      | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | _    | _    |      | RPF6 | 6<3:0> | •    | 0000       |

| 5000                        | DDEAD            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | —    | —      | _    | 0000       |

| FC60                        | RPF8R            | 15:0      | _     | _     | _     | —     | _     | _     | _    | _    | _    | —    | _    | _    |      | RPF7 | /<3:0> |      | 0000       |

| F0-0                        | 005/00           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FC70                        | RPF12R           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF1 | 2<3:0> |      | 0000       |

| 507/                        | 005405           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | —    | _    | —    | —    | —    | —      | _    | 0000       |

| FC74                        | RPF13R           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF1 | 3<3:0> |      | 0000       |

|                             | RPG0R            | 31:16     | _     |       |       | _     |       | _     | _    | _    | _    | _    | _    |      | _    |      |        |      | 0000       |

| FC80                        |                  |           |       |       |       |       |       |       |      |      |      |      |      |      |      |      |        |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

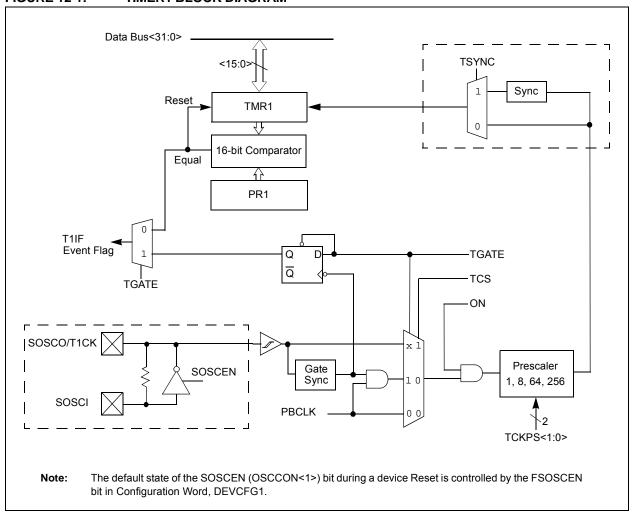

### 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a freerunning interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

### 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

### FIGURE 12-1: TIMER1 BLOCK DIAGRAM

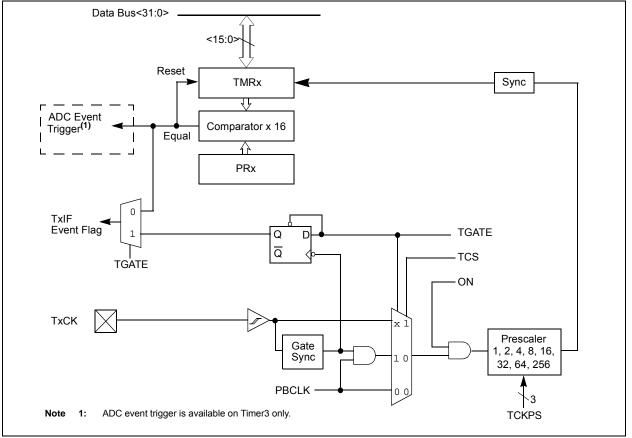

### 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- · Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- · Synchronous internal 32-bit timer

- Synchronous internal 32-bit gated timer

- · Synchronous external 32-bit timer

- Note: In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

### 13.1 Additional Supported Features

- Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/ 3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

### FIGURE 13-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

|              |                                                                                                                                               | PIxCON: SF                                                                                                                                                      |                                                                                                                |                                                                                                   |                                                                                  | D:/               | <b>D</b> **      | D:"                  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------|------------------|----------------------|

| Bit<br>Range | Bit<br>31/23/15/7                                                                                                                             | Bit<br>30/22/14/6                                                                                                                                               | Bit<br>29/21/13/5                                                                                              | Bit<br>28/20/12/4                                                                                 | Bit<br>27/19/11/3                                                                | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

| 31:24        | R/W-0                                                                                                                                         | R/W-0                                                                                                                                                           | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |

| 31.24        | FRMEN                                                                                                                                         | FRMSYNC                                                                                                                                                         | FRMPOL                                                                                                         | MSSEN                                                                                             | FRMSYPW                                                                          | F                 | RMCNT<2:0        | )>                   |

| 23:16        | R/W-0                                                                                                                                         | U-0                                                                                                                                                             | U-0                                                                                                            | U-0                                                                                               | U-0                                                                              | U-0               | R/W-0            | R/W-0                |

| 23.10        | MCLKSEL <sup>(2)</sup>                                                                                                                        | _                                                                                                                                                               | _                                                                                                              | —                                                                                                 | _                                                                                | —                 | SPIFE            | ENHBUF <sup>(2</sup> |

| 15:8         | R/W-0                                                                                                                                         | U-0                                                                                                                                                             | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |

| 15.0         | ON <sup>(1)</sup>                                                                                                                             | _                                                                                                                                                               | SIDL                                                                                                           | DISSDO                                                                                            | MODE32                                                                           | MODE16            | SMP              | CKE <sup>(3)</sup>   |

| 7.0          | R/W-0                                                                                                                                         | R/W-0                                                                                                                                                           | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |

| 7:0          | SSEN                                                                                                                                          | CKP <sup>(4)</sup>                                                                                                                                              | MSTEN                                                                                                          | DISSDI                                                                                            | STXISE                                                                           | L<1:0>            | SRXIS            | EL<1:0>              |

| Legend:      |                                                                                                                                               |                                                                                                                                                                 |                                                                                                                |                                                                                                   |                                                                                  |                   |                  |                      |

| R = Read     | lable hit                                                                                                                                     |                                                                                                                                                                 | W = Writable                                                                                                   | a hit                                                                                             |                                                                                  | mented bit, rea   | ad as '0'        |                      |

| -n = Valu    |                                                                                                                                               |                                                                                                                                                                 | '1' = Bit is se                                                                                                |                                                                                                   | '0' = Bit is cle                                                                 |                   | x = Bit is un    | known                |

|              | e al POR                                                                                                                                      |                                                                                                                                                                 |                                                                                                                | ÷l                                                                                                |                                                                                  | areu              | x = bit is un    | IKHOWH               |

| bit 31       | 0 = Framed S                                                                                                                                  | SPI support is<br>SPI support is                                                                                                                                | enabled (SS<br>disabled                                                                                        | _                                                                                                 | S FSYNC input                                                                    |                   |                  |                      |

| bit 30       | FRMSYNC: F<br>1 = Frame sy<br>0 = Frame sy                                                                                                    | nc pulse inpu                                                                                                                                                   | it (Slave mod                                                                                                  | e)                                                                                                | SSx pin bit (Fra                                                                 | amed SPI mo       | de only)         |                      |

| bit 29       | <b>FRMPOL:</b> Fra<br>1 = Frame pu<br>0 = Frame pu                                                                                            | ame Sync Po<br>Ilse is active-                                                                                                                                  | larity bit (Frar<br>high                                                                                       |                                                                                                   | e only)                                                                          |                   |                  |                      |

| bit 28       | MSSEN: Mas<br>1 = Slave sele                                                                                                                  | ter Mode Sla<br>ect SPI suppo<br>ode. Polarity i                                                                                                                | ve Select Ena<br>ort enabled. T<br>s determined                                                                | he <u>SS</u> pin is a by the FRMF                                                                 | automatically o<br>POL bit.                                                      | driven during t   | transmission     | in                   |

| bit 27       | <b>FRMSYPW:</b> F                                                                                                                             | Frame Sync F                                                                                                                                                    | ulse Width b                                                                                                   | it                                                                                                |                                                                                  |                   |                  |                      |

|              | 0 = Frame sy                                                                                                                                  |                                                                                                                                                                 |                                                                                                                | viac                                                                                              |                                                                                  |                   |                  |                      |

| bit 26-24    | FRMCNT<2:0<br>pulse. This bit<br>111 = Reserv<br>110 = Reserv<br>101 = Genera<br>010 = Genera<br>010 = Genera<br>010 = Genera<br>001 = Genera | t is only valid<br>red; do not us<br>red; do not us<br>ate a frame sy<br>ate a frame sy | in FRAMED_<br>e<br>e<br>ync pulse on e<br>ync pulse on e<br>ync pulse on e<br>ync pulse on e<br>ync pulse on e | SYNC mode<br>every 32 data<br>every 16 data<br>every 8 data o<br>every 4 data o<br>every 2 data o | characters<br>characters<br>characters<br>characters<br>characters<br>characters | nber of data c    | characters tra   | ansmitted pe         |

| bit 23       | <b>MCLKSEL:</b> M<br>1 = REFCLK<br>0 = PBCLK is                                                                                               | is used by the                                                                                                                                                  | e Baud Rate                                                                                                    |                                                                                                   |                                                                                  |                   |                  |                      |

| bit 22-18    | Unimplemen                                                                                                                                    | ted: Read as                                                                                                                                                    | '0'                                                                                                            |                                                                                                   |                                                                                  |                   |                  |                      |

| Note 1:      | SYSCLK cyc                                                                                                                                    | le immediatel                                                                                                                                                   | y following th                                                                                                 | e instruction                                                                                     | e should not re<br>that clears the                                               |                   |                  | SFRs in the          |

| 2:           | This bit can c                                                                                                                                | •                                                                                                                                                               |                                                                                                                |                                                                                                   |                                                                                  |                   |                  |                      |

| 3:           | This bit is not mode (FRME                                                                                                                    |                                                                                                                                                                 | Framed SPI n                                                                                                   | node. The use                                                                                     | er should prog                                                                   | ram this bit to   | 0 '0' for the F  | ramed SPI            |

| 4:           | When AUDE                                                                                                                                     | N = 1, the SP                                                                                                                                                   | I module fund                                                                                                  | tions as if the                                                                                   | e CKP bit is eq                                                                  | ual to '1', rega  | ardless of the   | actual value         |

####

of CKP.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   |                   |                   | SID<1             | 0:3>              |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 23.10        |                   | SID<2:0>          |                   | —                 | MIDE              | _                 | EID<'            | 17:16>           |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         |                   |                   |                   | EID<1             | 5:8>              |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | EID<7             | 7:0>              |                   |                  |                  |

#### REGISTER 23-9: C1RXMn: CAN ACCEPTANCE FILTER MASK 'n' REGISTER (n = 0, 1, 2 OR 3)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Include the SIDx bit in filter comparison

- 0 = The SIDx bit is a 'don't care' in filter operation

- bit 20 Unimplemented: Read as '0'

- bit 19 MIDE: Identifier Receive Mode bit

- 1 = Match only message types (standard/extended address) that correspond to the EXID bit in filter

- Match either standard or extended address message if filters match (that is, if (Filter SID) = (Message SID) or if (FILTER SID/EID) = (Message SID/EID))

#### bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Include the EIDx bit in filter comparison

- 0 = The EIDx bit is a 'don't care' in filter operation

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31.24        |                   | SID<10:3>         |                   |                   |                   |                   |                  |                  |  |  |

| 02:16        | R/W-x             | R/W-x             | R/W-x             | U-0               | R/W-0             | U-0               | R/W-x            | R/W-x            |  |  |

| 23:16        | SID<2:0>          |                   |                   | _                 | EXID              | _                 | — EID<17:16>     |                  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

|              |                   |                   |                   | EID<              | :7:0>             |                   |                  |                  |  |  |

#### REGISTER 23-14: C1RXFn: CAN ACCEPTANCE FILTER 'n' REGISTER ('n' = 0 THROUGH 15)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Message address bit SIDx must be '1' to match filter

- 0 = Message address bit SIDx must be '0' to match filter

- bit 20 Unimplemented: Read as '0'

- bit 19 **EXID:** Extended Identifier Enable bits

- 1 = Match only messages with extended identifier addresses

- 0 = Match only messages with standard identifier addresses

- bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Message address bit EIDx must be '1' to match filter

- 0 = Message address bit EIDx must be '0' to match filter

**Note:** This register can only be modified when the filter is disabled (FLTENn = 0).

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

### 27.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

#### 27.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The peripheral bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 19-10 **PWP<9:0>:** Program Flash Write-Protect bits

| dit 19-10     | <b>PWP&lt;9:0&gt;:</b> Program Flash Write-Protect bits                                                                                                                                          |  |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|               | Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages. |  |  |  |  |  |  |  |

|               | 1111111111 = Disabled                                                                                                                                                                            |  |  |  |  |  |  |  |

|               | 1111111110 = Memory below 0x0400 address is write-protected<br>1111111101 = Memory below 0x0800 address is write-protected                                                                       |  |  |  |  |  |  |  |

|               | 1111111100 = Memory below 0x0C00 address is write-protected                                                                                                                                      |  |  |  |  |  |  |  |

|               | 1111111011 = Memory below 0x1000 (4K) address is write-protected                                                                                                                                 |  |  |  |  |  |  |  |

|               | 1111111010 = Memory below 0x1400 address is write-protected                                                                                                                                      |  |  |  |  |  |  |  |

|               | 1111111001 = Memory below 0x1800 address is write-protected                                                                                                                                      |  |  |  |  |  |  |  |

|               | 1111111000 = Memory below 0x1C00 address is write-protected<br>1111110111 = Memory below 0x2000 (8K) address is write-protected                                                                  |  |  |  |  |  |  |  |

|               | 1111110110 = Memory below 0x2400 address is write-protected                                                                                                                                      |  |  |  |  |  |  |  |

|               | 1111110101 = Memory below 0x2800 address is write-protected                                                                                                                                      |  |  |  |  |  |  |  |

|               | 1111110100 = Memory below 0x2C00 address is write-protected                                                                                                                                      |  |  |  |  |  |  |  |

|               | 1111110011 = Memory below 0x3000 address is write-protected                                                                                                                                      |  |  |  |  |  |  |  |

|               | 1111110010 = Memory below 0x3400 address is write-protected<br>1111110001 = Memory below 0x3800 address is write-protected                                                                       |  |  |  |  |  |  |  |

|               | 1111110000 = Memory below 0x3C00 address is write-protected                                                                                                                                      |  |  |  |  |  |  |  |

|               | 1111101111 = Memory below 0x4000 (16K) address is write-protected                                                                                                                                |  |  |  |  |  |  |  |

|               | •                                                                                                                                                                                                |  |  |  |  |  |  |  |

|               | •<br>1110111111 = Memory below 0x10000 (64K) address is write-protected                                                                                                                          |  |  |  |  |  |  |  |

|               | •                                                                                                                                                                                                |  |  |  |  |  |  |  |

|               |                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|               | 1101111111 = Memory below 0x20000 (128K) address is write-protected                                                                                                                              |  |  |  |  |  |  |  |

|               | •                                                                                                                                                                                                |  |  |  |  |  |  |  |

|               | •                                                                                                                                                                                                |  |  |  |  |  |  |  |

|               | 1011111111 = Memory below 0x40000 (256K) address is write-protected                                                                                                                              |  |  |  |  |  |  |  |

|               |                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|               | O111111111 = Memory below 0x80000 (512K) address is write-protected                                                                                                                              |  |  |  |  |  |  |  |

|               | •                                                                                                                                                                                                |  |  |  |  |  |  |  |

|               | •                                                                                                                                                                                                |  |  |  |  |  |  |  |

|               | •<br>000000000 = All possible memory is write-protected                                                                                                                                          |  |  |  |  |  |  |  |

|               | <b>Note:</b> These bits are effective only if Boot Flash is also protected by clearing the BWP bit                                                                                               |  |  |  |  |  |  |  |

|               | (DEVCFG0<24>).                                                                                                                                                                                   |  |  |  |  |  |  |  |

| bit 9-5       | Reserved: Write '1'                                                                                                                                                                              |  |  |  |  |  |  |  |

| bit 4-3       | ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits                                                                                                                      |  |  |  |  |  |  |  |

|               | 11 = PGEC1/PGED1 pair is used                                                                                                                                                                    |  |  |  |  |  |  |  |

|               | 10 = PGEC2/PGED2 pair is used                                                                                                                                                                    |  |  |  |  |  |  |  |

|               | 01 = PGEC3/PGED3 pair is used<br>00 = Reserved                                                                                                                                                   |  |  |  |  |  |  |  |

| <b>h</b> it 0 |                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| bit 2         | JTAGEN: JTAG Enable bit <sup>(1)</sup><br>1 = JTAG is enabled                                                                                                                                    |  |  |  |  |  |  |  |

|               | 0 = JTAG is disabled                                                                                                                                                                             |  |  |  |  |  |  |  |

| bit 1-0       | <b>DEBUG&lt;1:0&gt;:</b> Background Debugger Enable bits (forced to '11' if code-protect is enabled)                                                                                             |  |  |  |  |  |  |  |

|               | 1x = Debugger is disabled                                                                                                                                                                        |  |  |  |  |  |  |  |

|               | 0x = Debugger is enabled                                                                                                                                                                         |  |  |  |  |  |  |  |

|               |                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Note 1.       | This bit sets the value for the JTAGEN bit in the CEGCON register                                                                                                                                |  |  |  |  |  |  |  |

#### **Note 1:** This bit sets the value for the JTAGEN bit in the CFGCON register.

#### REGISTER 28-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 2-0 **FPLLIDIV<2:0>:** PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 001 = 2x divider

- 000 = 1x divider

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

| REGIOTE      |                   |                   |                       |                        |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                     | _                      | _                 | —                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | -                     | _                      | _                 | —                 | _                | —                |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 |                   | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> |                   | —                 |                  | _                |

| 7:0          | U-0               | U-0               | U-0                   | U-0                    | R/W-0             | U-0               | U-0              | R/W-1            |

| 7:0          | _                 |                   |                       | _                      | JTAGEN            | _                 | _                | TDOEN            |

### REGISTER 28-5: CFGCON: CONFIGURATION CONTROL REGISTER

#### Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

- bit 13 **IOLOCK:** Peripheral Pin Select Lock bit<sup>(1)</sup>

- 1 = Peripheral Pin Select is locked. Writes to PPS registers is not allowed

- 0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed

- bit 12 PMDLOCK: Peripheral Module Disable bit<sup>(1)</sup>

- 1 = Peripheral module is locked. Writes to PMD registers is not allowed

- 0 = Peripheral module is not locked. Writes to PMD registers is allowed

- bit 11-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2-1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

- Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| DC CHARACT                                                         | ERISTICS               |      | (unless oth      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |               |  |