Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f128h-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Device Pin Tables**

## TABLE 2: PIN NAMES FOR 64-PIN GENERAL PURPOSE DEVICES

| 64·   | PIN QFN <sup>(4)</sup> AND TQFP (TOP VIEW)                                     |                   |                        |

|-------|--------------------------------------------------------------------------------|-------------------|------------------------|

|       | PIC32MX120F064H<br>PIC32MX130F128H<br>PIC32MX150F256H<br>PIC32MX170F512H<br>64 | QFN <sup>(4</sup> | 1<br>64<br><b>TQFP</b> |

| Pin # | Full Pin Name                                                                  | Pin #             | Full Pin Name          |

| 1     | AN22/RPE5/PMD5/RE5                                                             | 33                | RPF3/RF3               |

| 2     | AN23/PMD6/RE6                                                                  | 34                | RPF2/RF2               |

| 3     | AN27/PMD7/RE7                                                                  | 35                | RPF6/SCK1/INT0/RF6     |

| 4     | AN16/C1IND/RPG6/SCK2/PMA5/RG6                                                  | 36                | SDA1/RG3               |

| 5     | AN17/C1INC/RPG7/PMA4/RG7                                                       | 37                | SCL1/RG2               |

| 6     | AN18/C2IND/RPG8/PMA3/RG8                                                       | 38                | VDD                    |

| 7     | MCLR                                                                           | 39                | OSC1/CLKI/RC12         |

| 8     | AN19/C2INC/RPG9/PMA2/RG9                                                       | 40                | OSC2/CLKO/RC15         |

| 9     | Vss                                                                            | 41                | Vss                    |

| 10    | VDD                                                                            | 42                | RPD8/RTCC/RD8          |

| 11    | AN5/C1INA/RPB5/RB5                                                             | 43                | RPD9/RD9               |

| 12    | AN4/C1INB/RB4                                                                  | 44                | RPD10/PMA15/RD10       |

| 13    | PGED3/AN3/C2INA/RPB3/RB3                                                       | 45                | RPD11/PMA14/RD11       |

| 14    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2                                          | 46                | RPD0/RD0               |

| 15    | PGEC1/VREF-/AN1/RPB1/CTED12/RB1                                                | 47                | SOSCI/RPC13/RC13       |

| 16    | PGED1/VREF+/AN0/RPB0/PMA6/RB0                                                  | 48                | SOSCO/RPC14/T1CK/RC14  |

| 17    | PGEC2/AN6/RPB6/RB6                                                             | 49                | AN24/RPD1/RD1          |

| 18    | PGED2/AN7/RPB7/CTED3/RB7                                                       | 50                | AN25/RPD2/RD2          |

| 19    | AVDD                                                                           | 51                | AN26/C3IND/RPD3/RD3    |

| 20    | AVss                                                                           | 52                | RPD4/PMWR/RD4          |

| 21    | AN8/RPB8/CTED10/RB8                                                            | 53                | RPD5/PMRD/RD5          |

| 22    | AN9/RPB9/CTED4/PMA7/RB9                                                        | 54                | C3INC/RD6              |

| 23    | TMS/CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                      | 55                | C3INB/RD7              |

| 24    | TDO/AN11/PMA12/RB11                                                            | 56                | VCAP                   |

| 25    | Vss                                                                            | 57                | Vdd                    |

| 26    | Vdd                                                                            | 58                | C3INA/RPF0/RF0         |

| 27    | TCK/AN12/PMA11/RB12                                                            | 59                | RPF1/RF1               |

| 28    | TDI/AN13/PMA10/RB13                                                            | 60                | PMD0/RE0               |

| 29    | AN14/RPB14/SCK3/CTED5/PMA1/RB14                                                | 61                | PMD1/RE1               |

| 30    | AN15/RPB15/OCFB/CTED6/PMA0/RB15                                                | 62                | AN20/PMD2/RE2          |

| 31    | RPF4/SDA2/PMA9/RF4                                                             | 63                | RPE3/CTPLS/PMD3/RE3    |

| 32    | RPF5/SCL2/PMA8/RF5                                                             | 64                | AN21/PMD4/RE4          |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 11.0 "I/O Ports" for more information.

Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

NOTES:

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

## TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

## 3.3 **Power Management**

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 27.0 "Power-Saving Features".

## 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX-1XX/2XX/5XX 64/100-pin family core is in the clock tree and clocking registers. The PIC32MX family uses extensive use of local gated-clocks to reduce this dynamic power consumption.

## 3.4 EJTAG Debug Support

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K<sup>®</sup> core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

#### TABLE 4-1: SFR MEMORY MAP

| Devinheral             | Virtual | Address      |

|------------------------|---------|--------------|

| Peripheral             | Base    | Offset Start |

| Interrupt Controller   |         | 0x1000       |

| Bus Matrix             |         | 0x2000       |

| DMA                    | 0       | 0x3000       |

| USB                    | 0xBF88  | 0x5000       |

| PORTA-PORTG            |         | 0x6000       |

| CAN1                   |         | 0xB000       |

| Watchdog Timer         |         | 0x0000       |

| RTCC                   |         | 0x0200       |

| Timer1-Timer5          |         | 0x0600       |

| IC1-IC5                |         | 0x2000       |

| OC1-OC5                |         | 0x3000       |

| I2C1-I2C2              |         | 0x5000       |

| SPI1-SPI4              |         | 0x5800       |

| UART1-UART5            | 0xBF80  | 0x6000       |

| PMP                    | UXBF80  | 0x7000       |

| ADC1                   |         | 0x9000       |

| DAC                    |         | 0x9800       |

| Comparator 1, 2, 3     |         | 0xA000       |

| Oscillator             |         | 0xF000       |

| Device and Revision ID |         | 0xF200       |

| Flash Controller       |         | 0xF400       |

| PPS                    |         | 0xFA00       |

| Configuration          | 0xBFC0  | 0x0BF0       |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |  |

| 31:24        | —                 | _                 | _                 | _                 | _                 | -                 | _                | —                    |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |  |

| 23:16        | —                 | _                 | _                 | —                 | _                 |                   |                  | _                    |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |  |

| 10.0         | —                 | _                 |                   | —                 | _                 |                   | —                | _                    |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |  |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | SWRST <sup>(1)</sup> |  |  |  |  |

## REGISTER 7-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:      HC = Cleared by hardware |                  |                                       |                    |  |  |  |  |  |

|---------------------------------------|------------------|---------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit                      | W = Writable bit | ut U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR                     | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup>

- 1 = Enable software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section

6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 =Clock is multiplied by 17

- 001 =Clock is multiplied by 16

- 000 = Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = PLL module is in lock or PLL module start-up timer is satisfied

- 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 **CF:** Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| REGISTER 10-3. OTFWRC: 03B FOWER CONTROL REGISTER |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|---------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range                                      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24                                             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24                                             | —                 | —                 | -                 | —                 | —                 | -                 | —                | —                |  |  |  |

| 23:16                                             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10                                             | —                 | —                 | -                 | —                 | —                 | _                 | —                | _                |  |  |  |

| 15:8                                              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0                                              | —                 | —                 |                   | _                 |                   |                   | —                | —                |  |  |  |

| 7:0                                               | R-0               | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |  |

| 7.0                                               | UACTPND           | —                 | _                 | USLPGRD           | USBBUSY           | _                 | USUSPEND         | USBPWR           |  |  |  |

## REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| Logonal           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

#### **Control Registers** 13.2

## TABLE 13-1: TIMER2 THROUGH TIMER5 REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |             | Bi   | its    |      |           |      |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|-------------|------|--------|------|-----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9        | 24/8 | 23/7   | 22/6 | 21/5      | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16     |       | —     | _     | _     | —     | -     | —           | -    | _      | l    | _         | _    | —    | —    | _    | _    | 0000       |

| 0000                        | 12001                           | 15:0      | ON    | —     | SIDL  | _     | —     | _     | _           | _    | TGATE  | -    | TCKPS<2:0 | >    | T32  | _    | TCS  | _    | 0000       |

| 0810                        | TMR2                            | 31:16     | _     | —     | —     | —     | —     | —     | —           | —    | —      | _    | —         | _    | —    | —    | —    | _    | 0000       |

| 0010                        | TIVITYZ                         | 15:0      |       | -     |       |       | -     |       |             | TMR2 | <15:0> |      |           |      |      |      |      |      | 0000       |

| 0820                        | PR2                             | 31:16     | _     | —     | —     | —     | —     | —     | —           | —    | —      | _    | —         | _    | —    | —    | —    | _    | 0000       |

| 0020                        | 1112                            | 15:0      |       |       |       |       |       |       |             | PR2< | 15:0>  |      |           |      |      |      |      |      | FFFF       |

| 0400                        | T3CON                           | 31:16     | _     | _     | —     | _     |       | _     | —           | _    | —      |      | —         | _    | —    |      | _    |      | 0000       |

| 0/100                       | 10001                           | 15:0      | ON    |       | SIDL  | _     |       | _     | —           | _    | TGATE  | -    | TCKPS<2:0 | >    | —    |      | TCS  |      | 0000       |

| 0A10                        | TMR3                            | 31:16     | —     | —     | —     | —     | —     | —     | —           | —    | —      | —    | —         | —    | —    | —    | —    | —    | 0000       |

| 0/110                       | 1111110                         | 15:0      |       |       |       |       |       |       |             | TMR3 | <15:0> |      |           |      |      |      |      |      | 0000       |

| 0A20                        | PR3                             | 31:16     |       | _     | —     | —     |       | —     | —           | —    | —      | —    | —         | _    | —    | —    | —    | —    | 0000       |

| 0/ 120                      |                                 | 15:0      |       |       |       |       |       |       |             | PR3< | 15:0>  |      |           |      |      |      |      |      | FFFF       |

| 0C00                        | T4CON                           | 31:16     | _     |       | —     | _     |       | _     | _           | _    | —      |      | —         | _    | -    |      | _    |      | 0000       |

|                             |                                 | 15:0      | ON    | —     | SIDL  | _     | —     | _     | _           | _    | TGATE  |      | TCKPS<2:0 | >    | T32  | —    | TCS  |      | 0000       |

| 0C10                        | TMR4                            | 31:16     | _     | —     | —     | —     | —     | —     | —           | —    | —      | _    | —         | —    | —    | —    | —    |      | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |             | TMR4 | <15:0> |      |           |      |      |      |      |      | 0000       |

| 0C20                        | PR4                             | 31:16     | _     | —     | —     | —     | —     | —     | —           | —    | —      | —    | —         | —    | —    | —    | —    | _    | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |             | PR4< | 15:0>  |      |           |      |      |      |      |      | FFFF       |

| 0E00                        | T5CON                           | 31:16     | -     | —     | -     | _     | —     | _     | _           | _    | _      |      | —         | _    | —    | —    | -    | _    | 0000       |

|                             |                                 | 15:0      | ON    | —     | SIDL  | _     | _     | _     | _           | _    | TGATE  |      | TCKPS<2:0 | >    | _    | _    | TCS  |      | 0000       |

| 0E10                        | TMR5                            | 31:16     |       | —     | _     | —     | _     | _     | —           | -    | —      | _    | _         | _    | _    | _    | —    | _    | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |             |      |        |      |           | 0000 |      |      |      |      |            |

| 0E20                        | PR5                             | 31:16     |       | —     | —     | _     | —     | —     | —           | _    | —      | _    | —         | _    | _    | —    | —    | —    | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       | ara ahaum i | PR5< |        |      |           |      |      |      |      |      | FFFF       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

## 16.1 Control Registers

## TABLE 16-1: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |            |                                                                                                              |       |       |       |       |      | Bi    | its     |      |      |       |        |      |          |      |              |

|-----------------------------|---------------------------------|---------------|------------|--------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|------|-------|---------|------|------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15      | 30/14                                                                                                        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7    | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16         | —          | —                                                                                                            | —     | —     | —     | —     | —    | —     | —       | _    | _    | —     | —      | _    | —        |      | 0000         |

| 3000                        |                                 | 15:0          | ON         | ON      —      SIDL      —      —      —      —      —      OC32      OCFLT      OCTSEL      OCM<2:0>      0 |       |       |       |       |      |       |         |      |      | 0000  |        |      |          |      |              |

| 3010                        | OC1R                            | 31:16<br>15:0 |            |                                                                                                              |       |       |       |       |      | OC1R  | <31:0>  |      |      |       |        |      |          |      | xxxx<br>xxxx |

| 3020                        | OC1RS                           | 31:16<br>15:0 |            |                                                                                                              |       |       |       |       |      | OC1RS | 6<31:0> |      |      |       |        |      |          |      | xxxx<br>xxxx |

|                             |                                 | 31:16         | _          | _                                                                                                            | _     | _     | _     | —     | —    | —     | _       | _    | _    | _     | _      | _    | _        | _    | 0000         |

| 3200                        | OC2CON                          | 15:0          | ON         | _                                                                                                            | SIDL  | _     | _     | _     | _    | _     | _       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

|                             |                                 | 31:16         |            |                                                                                                              |       |       |       |       |      |       |         |      |      |       |        |      |          |      | xxxx         |

| 3210                        | OC2R                            | 15:0          | OC2R<31:0> |                                                                                                              |       |       |       |       |      |       |         |      | xxxx |       |        |      |          |      |              |

|                             |                                 | 31:16         |            | · · · · · · · · · · · · · · · · · · ·                                                                        |       |       |       |       |      |       |         |      |      | xxxx  |        |      |          |      |              |

| 3220                        | OC2RS                           | 15:0          |            |                                                                                                              |       |       |       |       |      | OC2RS | 6<31:0> |      |      |       |        |      |          |      | xxxx         |

|                             |                                 | 31:16         |            | _                                                                                                            | _     | _     | _     | _     |      | _     | _       |      |      | _     | _      | _    | _        | _    | 0000         |

| 3400                        | OC3CON                          | 15:0          | ON         | _                                                                                                            | SIDL  | -     | _     | _     | _    | _     | _       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 0.440                       | 0.000                           | 31:16         |            |                                                                                                              |       |       |       |       |      | 0.000 | -0.1.0: |      |      |       |        |      |          |      | xxxx         |

| 3410                        | OC3R                            | 15:0          |            |                                                                                                              |       |       |       |       |      | OC3R  | <31:0>  |      |      |       |        |      |          |      | xxxx         |

| 3420                        | OC3RS                           | 31:16         |            |                                                                                                              |       |       |       |       |      | OC3R5 | 221.05  |      |      |       |        |      |          |      | xxxx         |

| 3420                        | UCSRS                           | 15:0          |            |                                                                                                              |       |       |       |       |      | UCSRE | 5<31.0> |      |      |       |        |      |          |      | xxxx         |

| 3600                        | OC4CON                          | 31:16         | —          | —                                                                                                            | _     | —     | —     | —     | —    | —     | _       | —    | —    | —     | —      |      | —        |      | 0000         |

| 3000                        | 004001                          | 15:0          | ON         | _                                                                                                            | SIDL  | _     | _     | _     | -    | _     | _       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3610                        | OC4R                            | 31:16         |            |                                                                                                              |       |       |       |       |      | OC4R  | ~31.0>  |      |      |       |        |      |          |      | xxxx         |

| 3010                        | 0040                            | 15:0          |            |                                                                                                              |       |       |       |       |      | 0040  | <31.02  |      |      |       |        |      |          |      | xxxx         |

| 3620                        | OC4RS                           | 31:16         |            |                                                                                                              |       |       |       |       |      | OC4RS | 2<31.05 |      |      |       |        |      |          |      | xxxx         |

| 3020                        | 00403                           | 15:0          |            | -                                                                                                            |       | -     | -     | -     | -    | 00400 | 5-51.0- | -    |      |       | -      |      |          |      | xxxx         |

| 3800                        | OC5CON                          | 31:16         | —          | —                                                                                                            | —     | —     | —     |       |      |       | —       | —    | —    |       | —      |      | —        | —    | 0000         |

| 5000                        | 00000                           | 15:0          | ON         | —                                                                                                            | SIDL  | _     |       | _     | —    | _     | —       |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3810                        | OC5R                            | 31:16         |            |                                                                                                              |       |       |       |       |      | OC5R  | <31.0>  |      |      |       |        |      |          |      | xxxx         |

| 3010                        | 0001                            | 15:0          |            |                                                                                                              |       |       |       |       |      |       | xxxx    |      |      |       |        |      |          |      |              |

| 3820                        | OC5RS                           | 31:16         |            |                                                                                                              |       |       |       |       |      | 00589 | S<31:0> |      |      |       |        |      |          |      | xxxx         |

| 0020                        | 000100                          | 15:0          |            |                                                                                                              |       |       |       |       |      | OUSKE | -01.0-  |      |      |       |        |      |          |      | xxxx         |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                    | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:10        | —                 | _                 | _                 | —                    | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

#### **REGISTER 16-1:** OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER ('x' = 1 THROUGH 5)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

#### bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

## **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

#### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 31:24        | —                 | —                 | —                 | - RXBUFELM<       |                   |                   | )>               |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23:16        | —                 | —                 | —                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |

| 15:8         | —                 | _                 | —                 | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            |                   | SPITBF           | SPIRBF           |  |

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 **SPITUR:** Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

- This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

- This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 SPIRBE: RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR ≠ SWPTR)

- bit 4 Unimplemented: Read as '0'

### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- 0001 = Wait of 2 Трв 0000 = Wait of 1 Трв (default)

bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

11 = Wait of 4 TPB 10 = Wait of 3 TPB 01 = Wait of 2 TPB 00 = Wait of 1 TPB (default)

For Read operations: 11 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 1 TPB

- 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

#### REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                          | —                 | _                 | _                 | _                 |                   | —                | _                |  |

| 00.40        | U-0                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                        | —                 | _                 | —                 | —                 | —                 | —                | _                |  |

| 45.0         | R/W-0                    | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | ADRC                     | —                 | _                 |                   |                   | SAMC<4:0>(1)      |                  |                  |  |

| 7.0          | R/W-0                    | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W              | R/W-0            |  |

| 7:0          | ADCS<7:0> <sup>(2)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB 2 (ADCS<7:0> + 1) = 4 TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- 2: This bit is not used if the ADRC bit (AD1CON3<15>) = 1.

#### 23.1 **Control Registers**

## TABLE 23-1: CAN1 REGISTER SUMMARY

| ess                         |                                 |               |                               |              |              |                                                            |              |              |             | Bit         | 5       |             |             |             |             |            |           |         |            |

|-----------------------------|---------------------------------|---------------|-------------------------------|--------------|--------------|------------------------------------------------------------|--------------|--------------|-------------|-------------|---------|-------------|-------------|-------------|-------------|------------|-----------|---------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                         | 30/14        | 29/13        | 28/12                                                      | 27/11        | 26/10        | 25/9        | 24/8        | 23/7    | 22/6        | 21/5        | 20/4        | 19/3        | 18/2       | 17/1      | 16/0    | All Resets |

|                             | 01001                           | 31:16         |                               | _            | _            | _                                                          | ABAT         | F            | REQOP<2:0   | >           | C       | OPMOD<2:0   | >           | CANCAP      | _           | _          | _         | _       | 0480       |

| B000                        | C1CON                           | 15:0          | ON                            | -            | SIDLE        |                                                            | CANBUSY      | —            | _           | _           |         | _           | _           |             | D           | NCNT<4:0>  | •         |         | 0000       |

| B010                        | C1CFG                           | 31:16         | _                             |              | _            |                                                            | _            | _            | -           |             | -       | WAKFIL      | _           | _           | -           | S          | EG2PH<2:0 | >       | 0000       |

| вото                        | CICFG                           | 15:0          | SEG2PHTS                      | SAM          | S            | EG1PH<2:0                                                  | )>           | ŀ            | PRSEG<2:0   | >           | SJW     | <1:0>       |             |             | BRP<        | :5:0>      |           |         | 0000       |

| B020                        | C1INT                           | 31:16         | IVRIE                         | WAKIE        | CERRIE       | SERRIE                                                     | RBOVIE       |              | _           |             | _       | _           | _           | _           | MODIE       | CTMRIE     | RBIE      | TBIE    | 0000       |

| 0020                        | 01111                           | 15:0          | IVRIF                         | WAKIF        | CERRIF       | SERRIF                                                     | RBOVIF       | —            | —           | —           | —       | —           | —           | —           | MODIF       | CTMRIF     | RBIF      | TBIF    | 0000       |

| B030                        | C1VEC                           | 31:16         | —                             | _            | —            | —                                                          | —            | _            | —           | —           | _       | —           | —           | —           | —           | —          | —         | —       | 0000       |

| 2000                        |                                 | 15:0          | —                             |              | _            |                                                            |              | FILHIT<4:0>  | >           |             |         |             |             | r           | CODE<6:0>   |            |           |         | 0040       |

| B040                        | C1TREC                          | 31:16         | _                             | —            | _            | —                                                          | _            | _            | —           | —           | _       | _           | TXBO        | TXBP        | RXBP        | TXWARN     | RXWARN    | EWARN   | 0000       |

|                             |                                 | 15:0          |                               |              |              | TERRC                                                      | NT<7:0>      |              |             |             |         |             |             | RERRCN      | T<7:0>      |            |           |         | 0000       |

| B050                        | C1FSTAT                         | 31:16         | -                             | -            | -            | -                                                          | -            | -            | -           | -           | -       | -           | -           | -           | -           | -          | -         | -       | 0000       |

|                             |                                 | 15:0          | FIFOIP15                      | FIFOIP14     | FIFOIP13     | FIFOIP12                                                   | FIFOIP11     | FIFOIP10     | FIFOIP9     | FIFOIP8     | FIFOIP7 | FIFOIP6     | FIFOIP5     | FIFOIP4     | FIFOIP3     | FIFOIP2    | FIFOIP1   | FIFOIP0 | 0000       |

| B060                        | C1RXOVF                         | 31:16<br>15:0 | –<br>RXOVF15                  | —<br>RXOVF14 | –<br>RXOVF13 |                                                            | –<br>RXOVF11 | –<br>RXOVF10 | –<br>RXOVF9 | –<br>RXOVF8 | RXOVF7  | –<br>RXOVF6 | –<br>RXOVF5 | —<br>RXOVF4 | –<br>RXOVF3 | RXOVF2     | RXOVF1    | RXOVF0  | 0000       |

|                             |                                 | 31:16         | RAUVE 15                      | KAUVF14      | RAUVEIS      | RAUVE 12                                                   | RAUVEII      | RAUVEIU      | KAUVF9      |             |         | RAUVEO      | RAUVED      | KAUVF4      | RAUVES      | RAUVEZ     | RAUVEI    | RAUVFU  | 0000       |

| B070                        | C1TMR                           | 15:0          | CANTS<15:0><br>CANTSPRE<15:0> |              |              |                                                            |              |              |             | 0000        |         |             |             |             |             |            |           |         |            |

|                             |                                 | 31:16         |                               |              |              | SID<10:0>                                                  |              |              |             |             |         | MIDE        | _           | EID<1       | 7.16>       | xxxx       |           |         |            |

| B080                        | C1RXM0                          | 15:0          |                               |              |              |                                                            |              | 0.0 10.0     |             | EID<1       | 5.0>    |             |             |             |             |            | 2.0       |         | XXXX       |

|                             |                                 | 31:16         |                               |              |              |                                                            |              | SID<10:0>    |             |             |         |             |             |             | MIDE        |            | EID<1     | 7.16>   | xxxx       |

| B090                        | C1RXM1                          | 15:0          |                               |              |              |                                                            |              | 0.0 10.0     |             | EID<1       | 5.0>    |             |             |             |             |            | 2.0       |         | XXXX       |

|                             |                                 | 31:16         |                               |              |              |                                                            |              | SID<10:0>    |             | 210 11      |         |             |             |             | MIDE        | _          | EID<1     | 7.16>   | xxxx       |

| B0A0                        | C1RXM2                          | 15:0          |                               |              |              |                                                            |              | 0.0 10.0     |             | EID<1       | 5:0>    |             |             |             |             |            | 2.0       |         | XXXX       |

|                             |                                 | 31:16         |                               |              |              |                                                            |              | SID<10:0>    |             |             |         |             |             |             | MIDE        | _          | EID<1     | 7:16>   | xxxx       |

| B0B0                        | C1RXM3                          | 15:0          |                               |              |              |                                                            |              |              |             | EID<1       | 5:0>    |             |             |             |             |            | ļ         |         | xxxx       |

|                             |                                 | 31:16         | FLTEN3                        | MSEL         | 3<1:0>       |                                                            |              | FSEL3<4:0>   | >           |             | FLTEN2  | MSEL        | 2<1:0>      |             | F           | SEL2<4:0>  |           |         | 0000       |

| B0C0                        | C1FLTCON0                       | 15:0          | FLTEN1                        | MSEL         | 1<1:0>       |                                                            |              | FSEL1<4:0>   | >           |             | FLTEN0  | MSEL        | 0<1:0>      |             | F           | SEL0<4:0>  |           |         | 0000       |

|                             | 0.151 700114                    | 31:16         | FLTEN7                        | MSEL         | 7<1:0>       | FSEL7<4:0>      FLTEN6      MSEL6<1:0>      FSEL6<4:0>     |              |              |             |             |         | 0000        |             |             |             |            |           |         |            |

| B0D0                        | C1FLTCON1                       | 15:0          | FLTEN5                        | MSEL         | 5<1:0>       | FSEL5<4:0>      FLTEN4      MSEL4<1:0>      FSEL4<4:0>     |              |              |             |             |         | 0000        |             |             |             |            |           |         |            |

|                             |                                 | 31:16         | FLTEN11                       | MSEL'        | 11<1:0>      | FSEL11<4:0>      FLTEN10      MSEL10<1:0>      FSEL10<4:0> |              |              |             |             |         | 0000        |             |             |             |            |           |         |            |

| B0E0                        | C1FLTCON2                       | 15:0          | FLTEN9                        | MSEL         | 9<1:0>       |                                                            |              | FSEL9<4:0>   | <b>`</b>    |             | FLTEN8  | MSEL        | 8<1:0>      |             | F           | SEL8<4:0>  |           |         | 0000       |

| B0F0                        | C1FLTCON3                       | 31:16         | FLTEN15                       | MSEL1        | 15<1:0>      |                                                            |              | FSEL15<4:0   | >           |             | FLTEN14 | MSEL'       | 14<1:0>     |             | F           | SEL14<4:0> | •         |         | 0000       |

| BUFU                        | GIFLI CONS                      | 15:0          | FLTEN13                       | MSEL1        | 13<1:0>      |                                                            |              | FSEL13<4:0   | >           |             | FLTEN12 | MSEL'       | 12<1:0>     |             | F           | SEL12<4:0> | ·         |         | 0000       |

| B140                        | Onoan                           | 31:16         |                               |              |              |                                                            |              | SID<10:0>    |             |             |         |             |             |             | EXID        |            | EID<1     | 7:16>   | xxxx       |

| 0+10                        | (n = 0-15)                      | 15:0          |                               |              |              |                                                            |              | aa ara ahawr |             | EID<1       | 5:0>    |             |             |             |             |            |           |         | xxxx       |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information. Note 1:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | —                 | —                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | —                 | —                 | _                | -                |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | RXOVF15           | RXOVF14           | RXOVF13           | RXOVF12           | RXOVF11           | RXOVF10           | RXOVF9           | RXOVF8           |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | RXOVF7            | RXOVF6            | RXOVF5            | RXOVF4            | RXOVF3            | RXOVF2            | RXOVF1           | RXOVF0           |

## REGISTER 23-7: C1RXOVF: CAN RECEIVE FIFO OVERFLOW STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 RXOVF<15:0>: FIFOx Receive Overflow Interrupt Pending bit

1 = FIFO has overflowed

0 = FIFO has not overflowed

## REGISTER 23-8: C1TMR: CAN TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 51.24        |                   | CANTS<15:8>       |                   |                   |                   |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | CANTS<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |                   |                   | CANTSPR           | E<15:8>           |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                   |                   |                   | CANTSPF           | RE<7:0>           |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 CANTS<15:0>: CAN Time Stamp Timer bits

This is a free-running timer that increments every CANTSPRE system clocks when the CANCAP bit (C1CON<20>) is set.

## bit 15-0 CANTSPRE<15:0>: CAN Time Stamp Timer Prescaler bits 1111 1111 1111 1111 = CAN time stamp timer (CANTS) increments every 65,535 system clocks . . 0000 0000 0000 = CAN time stamp timer (CANTS) increments every system clock

**Note 1:** C1TMR will be paused when CANCAP = 0.

2: The C1TMR prescaler count will be reset on any write to C1TMR (CANTSPRE will be unaffected).

## 29.0 INSTRUCTION SET

The PIC32MX1XX/2XX/5XX 64/100-pin family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to *"MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set"* at www.imgtec.com for more information.

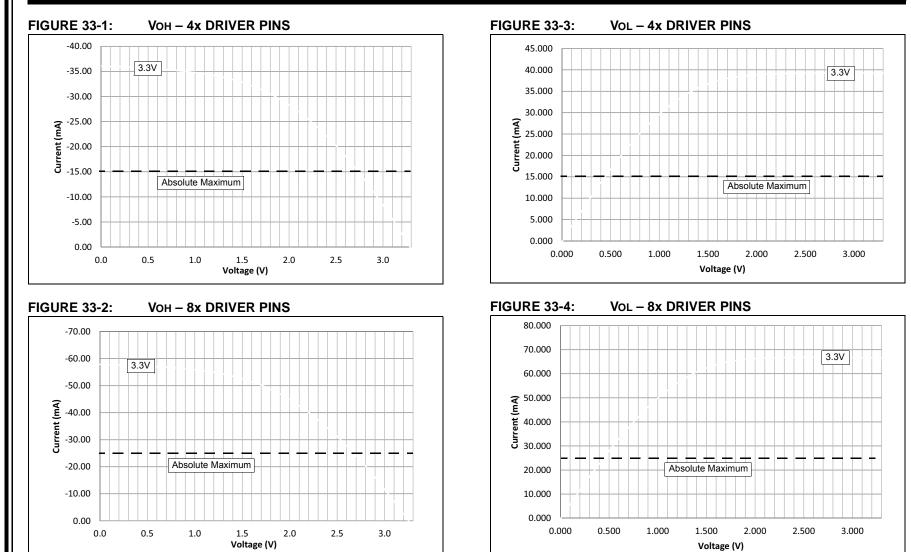

## 32.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX/5XX 64/100-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 31.0 "40 MHz Electrical Characteristics"**, with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 31.0** "40 MHz Electrical Characteristics", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX/5XX 64/100-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +85°C            |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                              | -0.3V to +4.0V           |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge$ 2.3V (Note 3) | -0.3V to +5.5V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | -0.3V to +3.6V           |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      | 15 mA                    |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 32-2).

- 3: See the "Device Pin Tables" section for the 5V tolerant pins.