Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                    |                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------|

| roduct Status             | Active                                                                            |

| ore Processor             | MIPS32® M4K™                                                                      |

| ore Size                  | 32-Bit Single-Core                                                                |

| peed                      | 50MHz                                                                             |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| eripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| umber of I/O              | 49                                                                                |

| rogram Memory Size        | 128KB (128K x 8)                                                                  |

| ogram Memory Type         | FLASH                                                                             |

| EPROM Size                | -                                                                                 |

| AM Size                   | 16K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| ata Converters            | A/D 28x10b                                                                        |

| scillator Type            | Internal                                                                          |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| ounting Type              | Surface Mount                                                                     |

| ackage / Case             | 64-TQFP                                                                           |

| upplier Device Package    | 64-TQFP (10x10)                                                                   |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f128ht-50i-pi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 5: PIN NAMES FOR 100-PIN USB DEVICES

100-PIN TQFP (TOP VIEW)

PIC32MX230F128L PIC32MX530F128L PIC32MX250F256L PIC32MX550F256L PIC32MX270F512L PIC32MX570F512L

100

1

| Pin# | Full Pin Name                         |

|------|---------------------------------------|

| 1    | AN28/RG15                             |

| 2    | VDD                                   |

| 3    | AN22/RPE5/PMD5/RE5                    |

| 4    | AN23/PMD6/RE6                         |

| 5    | AN27/PMD7/RE7                         |

| 6    | AN29/RPC1/RC1                         |

| 7    | AN30/RPC2/RC2                         |

| 8    | AN31/RPC3/RC3                         |

| 9    | RPC4/CTED7/RC4                        |

| 10   | AN16/C1IND/RPG6/SCK2/PMA5/RG6         |

| 11   | AN17/C1INC/RPG7/PMA4/RG7              |

| 12   | AN18/C2IND/RPG8/PMA3/RG8              |

| 13   | MCLR                                  |

| 14   | AN19/C2INC/RPG9/PMA2/RG9              |

| 15   | Vss                                   |

| 16   | VDD                                   |

| 17   | TMS/CTED1/RA0                         |

| 18   | AN32/RPE8/RE8                         |

| 19   | AN33/RPE9/RE9                         |

| 20   | AN5/C1INA/RPB5/VBuson/RB5             |

| 21   | AN4/C1INB/RB4                         |

| 22   | PGED3/AN3/C2INA/RPB3/RB3              |

| 23   | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 |

| 24   | PGEC1/AN1/RPB1/CTED12/RB1             |

| 25   | PGED1/AN0/RPB0/RB0                    |

| 26   | PGEC2/AN6/RPB6/RB6                    |

| 27   | PGED2/AN7/RPB7/CTED3/RB7              |

| 28   | VREF-/PMA7/RA9                        |

| 29   | VREF+/PMA6/RA10                       |

| 30   | AVDD                                  |

| 31   | AVss                                  |

| 32   | AN8/RPB8/CTED10/RB8                   |

| 33   | AN9/RPB9/CTED4/RB9                    |

| 34   | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| 35   | AN11/PMA12/RB11                       |

| Pin # | Full Pin Name                   |

|-------|---------------------------------|

|       |                                 |

| 36    | Vss                             |

| 37    | VDD                             |

| 38    | TCK/CTED2/RA1                   |

| 39    | AN34/RPF13/SCK3/RF13            |

| 40    | AN35/RPF12/RF12                 |

| 41    | AN12/PMA11/RB12                 |

| 42    | AN13/PMA10/RB13                 |

| 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 45    | Vss                             |

| 46    | VDD                             |

| 47    | AN36/RPD14/RD14                 |

| 48    | AN37/RPD15/SCK4/RD15            |

| 49    | RPF4/PMA9/RF4                   |

| 50    | RPF5/PMA8/RF5                   |

| 51    | USBID/RPF3/RF3                  |

| 52    | AN38/RPF2/RF2                   |

| 53    | AN39/RPF8/RF8                   |

| 54    | VBUS                            |

| 55    | VUSB3V3                         |

| 56    | D-                              |

| 57    | D+                              |

| 58    | SCL2/RA2                        |

| 59    | SDA2/RA3                        |

| 60    | TDI/CTED9/RA4                   |

| 61    | TDO/RA5                         |

| 62    | VDD                             |

| 63    | OSC1/CLKI/RC12                  |

| 64    | OSC2/CLKO/RC15                  |

| 65    | Vss                             |

| 66    | RPA14/SCL1/RA14                 |

| 67    | RPA15/SDA1/RA15                 |

| 68    | RPD8/RTCC/RD8                   |

| 69    | RPD9/RD9                        |

| 70    | RPD10/SCK1/PMA15/RD10           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

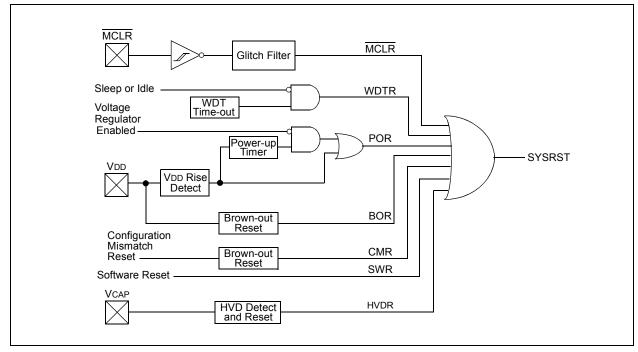

## 7.0 RESETS

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · MCLR: Master Clear Reset pin

- · SWR: Software Reset

- · WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- · CMR: Configuration Mismatch Reset

- HVDR: High Voltage Detect Reset

A simplified block diagram of the Reset module is illustrated in Figure 7-1.

FIGURE 7-1: SYSTEM RESET BLOCK DIAGRAM

### REGISTER 9-2: DMASTAT: DMA STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | -                 | _                 | -                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | -                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | ı                 | ı                 | _                 | ı                 | -                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 | _                 |                   |                   | RDWR              |                   | OMACH<2:0>       | •                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-4 **Unimplemented:** Read as '0' bit 3 **RDWR:** Read/Write Status bit

1 = Last DMA bus access was a read0 = Last DMA bus access was a write

bit 2-0 DMACH<2:0>: DMA Channel bits

These bits contain the value of the most recent active DMA channel.

## REGISTER 9-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 22.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 15:8         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

### REGISTER 9-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        | _                          | _                 | _                 | _                 |                      | _                 | _                | _                |  |  |  |  |  |

| 22:46        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |  |  |  |

| 15:8         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |

| 13.6         |                            |                   |                   | CHSIRQ-           | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |  |

| 7:0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |  |  |  |  |  |

| 7.0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN               |                   | -                | _                |  |  |  |  |  |

Legend:S = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-16 CHAIRQ<7:0>: Channel Transfer Abort IRQ bits(1)

11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag

•

•

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag

00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits(1)

11111111 = Interrupt 255 will initiate a DMA transfer

•

00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

bit 6 CABORT: DMA Abort Transfer bit

1 = A DMA transfer is aborted when this bit is written to a '1'

0 = This bit always reads '0'

bit 5 PATEN: Channel Pattern Match Abort Enable bit

1 = Abort transfer and clear CHEN on pattern match

0 = Pattern match is disabled

bit 4 SIRQEN: Channel Start IRQ Enable bit

1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

0 = Interrupt number CHSIRQ is ignored and does not start a transfer

bit 3 AIRQEN: Channel Abort IRQ Enable bit

1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

bit 2-0 Unimplemented: Read as '0'

Note 1: See Table 5-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

### REGISTER 10-3: U10TGSTAT: USB OTG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | -                 | -                 | -                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | -                 | -                 | -                 | _                 | _                 | _                | _                |

| 7.0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7:0          | ID                | _                 | LSTATE            | _                 | SESVD             | SESEND            | _                | VBUSVD           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **ID:** ID Pin State Indicator bit

1 = No cable is attached or a Type-B cable has been plugged into the USB receptacle

0 = A Type-A cable has been plugged into the USB receptacle

bit 6 Unimplemented: Read as '0'

bit 5 LSTATE: Line State Stable Indicator bit

1 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has been stable for the previous 1 ms

0 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has not been stable for the previous 1 ms

bit 4 Unimplemented: Read as '0'

bit 3 SESVD: Session Valid Indicator bit

1 = VBUS voltage is above Session Valid on the A or B device

0 = VBUS voltage is below Session Valid on the A or B device

bit 2 SESEND: B-Device Session End Indicator bit

1 = VBUS voltage is below Session Valid on the B device

0 = VBUS voltage is above Session Valid on the B device

bit 1 **Unimplemented:** Read as '0'

bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

1 = VBUS voltage is above Session Valid on the A device

0 = VBUS voltage is below Session Valid on the A device

## REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 31.24        | _                 | _                 | -                    | _                    | _                 | _                 | _                      | _                |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 23.10        | -                 | -                 | 1                    | -                    | -                 | _                 | _                      | _                |  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |

| 13.6         | _                 | _                 | -                    | _                    | _                 | _                 | _                      | _                |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |

| 7:0          | BTSEF             | BTSEF BMXEF       | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |

|              | DIOLI             | DIVIXLI           | DIVIALI              | DIOLI ·              | DINOLI            | ONOTOLI           | EOFEF <sup>(3,5)</sup> | TIDEF            |  |

Legend: WC = Write '1' to clear HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **BTSEF:** Bit Stuff Error Flag bit

1 = Packet rejected due to bit stuff error

0 = Packet accepted

bit 6 **BMXEF:** Bus Matrix Error Flag bit

1 = The base address, of the BDT, or the address of an individual buffer pointed to by a BDT entry, is invalid.

0 = No address error

bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup>

1 = USB DMA error condition detected

0 = No DMA error

bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

1 = Bus turnaround time-out has occurred

0 = No bus turnaround time-out

bit 3 DFN8EF: Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

bit 2 CRC16EF: CRC16 Failure Flag bit

1 = Data packet rejected due to CRC16 error

0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

## 11.4 Control Registers

TABLE 11-3: PORTA REGISTER MAP 100-PIN DEVICES ONLY

| ress<br>)                   | <b>L</b> .                      | е         |               |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | ANSELA                          | 31:16     | _             | _             |       | _     | _     | _             | _            | _    | _            | _            |              |              | _            | _            | I            | _            | 0000          |

| 0000                        | ANGLLA                          | 15:0      | _             | _             | _     | _     | _     | ANSELA10      | ANSELA9      |      | _            | _            | _            | _            | _            | _            | _            | _            | 0060          |

| 6010                        | TRISA                           | 31:16     | _             | _             |       | _     | _     | _             | _            | _    | _            | _            | _            |              | _            | _            |              | _            | 0000          |

| 0010                        | 11(10)(                         | 15:0      | TRISA15       | TRISA14       | _     | _     |       | TRISA10       | TRISA9       | _    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | C6FF          |

| 6020                        | PORTA                           | 31:16     | _             | _             | -     | _     | _     | _             | _            | _    | _            | _            | _            | -            | _            | _            | -            | _            | 0000          |

| 0020                        | 1 011171                        | 15:0      | RA15          | RA14          | _     | _     | _     | RA10          | RA9          | _    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                            | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            |              | _            | 0000          |

| 0000                        | DAIA                            | 15:0      | LATA15        | LATA14        | _     | _     |       | LATA10        | LATA9        | _    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                            | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            |              | _            | 0000          |

| 0040                        | ODON                            | 15:0      | ODCA15        | ODCA14        | _     | _     |       | ODCA10        | ODCA9        | _    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | 0000          |

| 6050                        | CNPUA                           | 31:16     | _             | _             | _     | _     | _     | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | OIII O/I                        | 15:0      | CNPUA15       | CNPUA14       | _     | _     | _     | CNPUA10       | CNPUA9       | _    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | 0000          |

| 6060                        | CNPDA                           | 31:16     | _             | _             | _     | _     | _     | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | 0 2                             | 15:0      | CNPDA15       | CNPDA14       | _     | _     | _     | CNPDA10       | CNPDA9       | _    | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       | 0000          |

| 6070                        | CNCONA                          | 31:16     | _             | _             | _     | _     | _     | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0070                        | 011001111                       | 15:0      | ON            | _             | SIDL  | _     | _     | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 6080                        | CNENA                           | 31:16     | _             | _             | _     | _     | _     | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | SIVEIVA                         | 15:0      | CNIEA15       | CNIEA14       | _     | _     | _     | CNIEA10       | CNIEA9       |      | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | 0000          |

|                             |                                 | 31:16     | _             | _             | _     | _     | _     | _             | _            |      | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 6090                        | CNSTATA                         | 15:0      | CN<br>STATA15 | CN<br>STATA14 | _     | _     | _     | CN<br>STATA10 | CN<br>STATA9 | _    | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | 0000          |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

TABLE 11-10: PORTE REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |      | E    | Bits         |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6400                        | ANSELE                          | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0400                        | ANOLLL                          | 15:0      | _     | -     | _     | _     | _     | -     | _    | _    | ANSELE7      | ANSELE6      | ANSELE5      | ANSELE4      | _            | ANSELE2      | _            | _            | 03F4          |

| 6410                        | TRISE                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0410                        | TINIOL                          | 15:0      | _     |       | _     | _     | _     |       | _    |      | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | 00FF          |

| 6420                        | PORTE                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0420                        | TORTE                           | 15:0      | _     | -     | _     | _     | _     | -     | _    | _    | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 6440                        | LATE                            | 31:16     | _     | -     | _     | _     | _     | -     | _    | _    | _            | _            | _            | -            | _            | _            | _            | _            | 0000          |

| 0440                        | LAIL                            | 15:0      | _     | -     | _     | _     | _     | -     | _    | _    | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | xxxx          |

| 6440                        | ODCE                            | 31:16     | _     | -     | _     | _     | _     | -     | _    | _    | _            | _            | _            | -            | _            | _            | _            | _            | 0000          |

| 0440                        | ODOL                            | 15:0      | _     | -     | _     | _     | _     | -     | _    | _    | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 6450                        | CNPUE                           | 31:16     | _     | -     | _     | _     | _     | -     | _    | _    | _            | _            | _            | -            | _            | _            | _            | _            | 0000          |

| 0430                        | CIVIOL                          | 15:0      | _     | -     | _     | _     | _     | -     | _    | _    | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPDE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 6460                        | CNPDE                           | 31:16     | _     | -     | _     | _     | _     | -     | _    | _    | _            | _            | _            | -            | _            | _            | _            | _            | 0000          |

| 0400                        | ON DL                           | 15:0      | _     | -     | _     | _     | _     | -     | _    | _    | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

| 6470                        | CNCONE                          | 31:16     | _     | -     | _     | _     | _     | -     | _    | _    | _            | _            | _            | -            | _            | _            | _            | _            | 0000          |

| 0470                        | CINCOINL                        | 15:0      | ON    | -     | SIDL  | _     | _     | -     | _    | _    | _            | _            | _            | -            | _            | _            | _            | _            | 0000          |

| 6480                        | CNENE                           | 31:16     | _     | ı     | -     | _     | _     | -     | -    | -    | _            | _            | -            | ı            | -            | _            | _            | -            | 0000          |

| 0400                        | CINCINC                         | 15:0      | _     | ı     | -     | _     | _     | -     | -    | -    | CNIEE7       | CNIEE6       | CNIEE5       | CNIEE4       | CNIEE3       | CNIEE2       | CNIEE1       | CNIEE0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 6490                        | CNSTATE                         | 15:0      | _     | -     | _     | _     | _     |       | _    | _    | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### REGISTER 20-4: PMDOUT: PARALLEL PORT OUTPUT DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15.6         |                   |                   |                   | DATAOUT           | <15:8>            |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

|              | DATAOUT<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **DATAOUT<15:0>:** Port Data Output bits

This register is used for Read operations in the Enhanced Parallel Slave mode and Write operations for Dual Buffer Master mode.

In Dual Buffer Master mode, the DUALBUF bit (PMPCON<17>) = 1, a write to the MSB triggers the transaction on the PMP port. When MODE16 = 1, MSB = DATAOUT<15:8>. When MODE16 = 0, MSB = DATAOUT<7:0>.

**Note:** In Master mode, a read will return the last value written to the register. In Slave mode, a read will return indeterminate results.

#### REGISTER 20-5: PMDIN: PARALLEL PORT INPUT DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 |                  | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 13.6         |                   |                   |                   | DATAIN<           | 15:8>             |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              | DATAIN<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 DATAIN<15:0>: Port Data Input bits

This register is used for both Parallel Master Port mode and Enhanced Parallel Slave mode.

In Parallel Master mode, a write to the MSB triggers the write transaction on the PMP port. Similarly, a read to the MSB triggers the read transaction on the PMP port.

When MODE16 = 1, MSB = DATAIN<15:8>. When MODE16 = 0, MSB = DATAIN<7:0>.

Note: This register is not used in Dual Buffer Master mode (i.e., DUALBUF bit (PMPCON<17>) = 1).

## REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit (4)

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- **4:** The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

## REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(3)</sup>

11111111 = Alarm will trigger 256 times

•

00000000 =Alarm will trigger one time

The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

**Note:** This register is reset only on a Power-on Reset (POR).

### REGISTER 21-6: ALRMDATE: ALARM DATE VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 |                   | -                 | _                 | -                 | _                | _                |  |

| 22.46        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   | MONT              | H10<3:0>          |                   | MONTH01<3:0>      |                   |                  |                  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   | DAY′              | 10<1:0>           |                   | DAY01<3:0>        |                   |                  |                  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

|              | _                 | _                 | _                 | _                 | WDAY01<3:0>       |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1s place digit; contains a value from 0 to 6

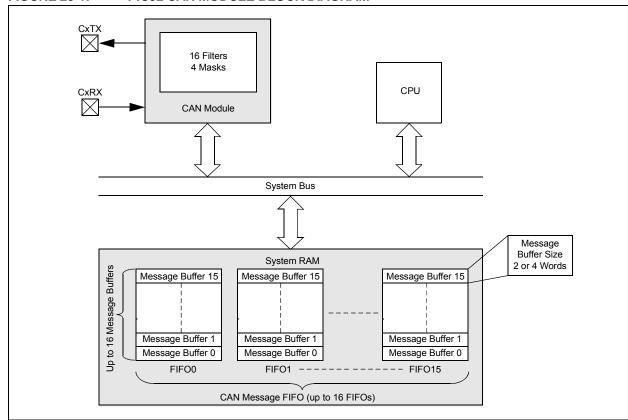

# 23.0 CONTROLLER AREA NETWORK (CAN)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 34.** "**Controller Area Network (CAN)**" (DS60001154) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Controller Area Network (CAN) module supports the following key features:

- · Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- · Message Reception and Transmission:

- 16 message FIFOs

- Each FIFO can have up to 16 messages for a total of 256 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 16 acceptance filters for message filtering

- Four acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

- DeviceNet™ addressing support

- · Additional Features:

- Loopback, Listen All Messages, and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32 system bus

- Use of DMA is not required

- Dedicated time-stamp timer

- Dedicated DMA channels

- Data-only Message Reception mode

Figure 23-1 illustrates the general structure of the CAN module.

### FIGURE 23-1: PIC32 CAN MODULE BLOCK DIAGRAM

#### 23.1 **Control Registers**

## TABLE 23-1: CAN1 REGISTER SUMMARY

| ess                         |                                 |                            |                                 |                   |           |                             |          |                              |                                | Bit     | s          |                             |         |            |           |            |           |         |            |

|-----------------------------|---------------------------------|----------------------------|---------------------------------|-------------------|-----------|-----------------------------|----------|------------------------------|--------------------------------|---------|------------|-----------------------------|---------|------------|-----------|------------|-----------|---------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                  | 31/15                           | 30/14             | 29/13     | 28/12                       | 27/11    | 26/10                        | 25/9                           | 24/8    | 23/7       | 22/6                        | 21/5    | 20/4       | 19/3      | 18/2       | 17/1      | 16/0    | All Resets |

| B000                        | C1CON                           | 31:16                      | _                               | _                 | _         | 1                           | ABAT     |                              | REQOP<2:0                      | >       | (          | DPMOD<2:0                   | >       | CANCAP     | -         | -          | _         | _       | 0480       |

| БООО                        | CICON                           | 15:0                       | ON                              | _                 | SIDLE     | _                           | CANBUSY  | _                            | _                              | _       | _          | _                           | _       |            | D         | NCNT<4:0>  | •         |         | 0000       |

| B010                        | C1CFG                           | 31:16                      | _                               | _                 | _         | _                           | _        | _                            | _                              | _       | _          | WAKFIL                      | _       | _          | _         | S          | EG2PH<2:0 | >       | 0000       |

| D010                        | 01010                           |                            | SEG2PHTS                        | SAM               |           | EG1PH<2:0                   |          |                              | PRSEG<2:0                      | >       | SJW        | <1:0>                       |         |            | BRP<      |            |           |         | 0000       |

| B020                        | C1INT                           | 31:16                      | IVRIE                           | WAKIE             | CERRIE    | SERRIE                      | RBOVIE   | _                            | _                              | _       | _          | _                           | _       | _          | MODIE     | CTMRIE     | RBIE      | TBIE    | 0000       |

| D020                        | 011111                          | 15:0                       | IVRIF                           | WAKIF             | CERRIF    | SERRIF                      | RBOVIF   |                              | _                              | _       | _          | _                           | _       | _          | MODIF     | CTMRIF     | RBIF      | TBIF    | 0000       |

| B030                        | C1VEC                           | 31:16                      | _                               | _                 | _         | _                           | _        | _                            | _                              | _       | _          | _                           | _       | _          | _         | _          | _         | _       | 0000       |

| Вооо                        | 01120                           | 15:0                       | _                               | _                 | _         |                             |          | FILHIT<4:0                   | >                              |         | _          |                             |         |            | CODE<6:0> |            | ,         |         | 0040       |

| B040                        | C1TREC                          | 31:16                      | _                               | _                 | _         | _                           | _        | _                            | _                              | _       | _          | _                           | TXBO    | TXBP       | RXBP      | TXWARN     | RXWARN    | EWARN   | 0000       |

| 50.0                        | 0111120                         | 15:0                       |                                 | •                 |           | TERRO                       | NT<7:0>  |                              |                                |         |            | •                           | •       | RERRCN     | IT<7:0>   |            | •         |         | 0000       |

| B050                        | C1FSTAT                         | 31:16                      | _                               | _                 | _         | _                           | _        | _                            | _                              | _       | _          | _                           | _       | _          | _         | _          | _         | _       | 0000       |

|                             | 011 01711                       | 15:0                       | FIFOIP15                        | FIFOIP14          | FIFOIP13  | FIFOIP12                    | FIFOIP11 | FIFOIP10                     | FIFOIP9                        | FIFOIP8 | FIFOIP7    | FIFOIP6                     | FIFOIP5 | FIFOIP4    | FIFOIP3   | FIFOIP2    | FIFOIP1   | FIFOIP0 | 0000       |

| B060                        | B060 C1RXOVF                    | 31:16                      | _                               | _                 | _         | _                           | _        | _                            | _                              | _       | _          | _                           | _       | _          | _         | _          | _         | _       | 0000       |

| 2000                        | 01101011                        | 15:0                       | RXOVF15                         | RXOVF14           | RXOVF13   | RXOVF12                     | RXOVF11  | RXOVF10                      | RXOVF9                         | RXOVF8  | RXOVF7     | RXOVF6                      | RXOVF5  | RXOVF4     | RXOVF3    | RXOVF2     | RXOVF1    | RXOVF0  |            |

| B070                        | C1TMR                           | 31:16                      |                                 |                   |           |                             |          |                              |                                | CANTS<  |            |                             |         |            |           |            |           |         | 0000       |

|                             |                                 | 15:0                       |                                 |                   |           |                             |          |                              |                                |         |            |                             | 0000    |            |           |            |           |         |            |

| B080                        | C1RXM0                          | 31:16                      | SID<10:0> — MIDE — EID<17:16> 2 |                   |           |                             |          |                              |                                |         |            | xxxx                        |         |            |           |            |           |         |            |

|                             | 0 0 0                           | 15:0                       |                                 |                   |           |                             |          |                              |                                | EID<1   | 5:0>       |                             |         |            |           |            |           |         | xxxx       |

| B090                        | C1RXM1                          | 31:16                      |                                 |                   |           |                             |          |                              |                                |         |            |                             | xxxx    |            |           |            |           |         |            |

| D000                        | Onown                           | 15:0                       |                                 | EID<15:0> xxx     |           |                             |          |                              |                                |         |            |                             |         |            | xxxx      |            |           |         |            |

| B0A0                        | C1RXM2                          | 31:16                      |                                 |                   |           |                             |          | SID<10:0>                    |                                |         |            |                             |         |            | MIDE      | _          | EID<1     | 7:16>   | xxxx       |

| DUAU                        | CTIVAIVIZ                       | 15:0                       | EID<15:0>                       |                   |           |                             |          |                              |                                |         |            |                             | xxxx    |            |           |            |           |         |            |

| B0B0                        | C1RXM3                          | 31:16                      |                                 |                   |           | SID<10:0> — MIDE            |          |                              |                                |         |            | _                           | EID<1   | 7:16>      | xxxx      |            |           |         |            |

| БОБО                        | CIRXIVIS                        | 15:0                       | EID<15:0>                       |                   |           |                             |          |                              |                                |         |            |                             | xxxx    |            |           |            |           |         |            |

| DOCO                        | C1FLTCON0                       | 31:16                      | FLTEN3                          | MSEL              | 3<1:0>    |                             |          | FSEL3<4:0> FLTEN2 MSEL2<1:0> |                                |         | FSEL2<4:0> |                             |         |            | 0000      |            |           |         |            |

| ВОСО                        | CIFLICONO                       | 15:0                       | FLTEN1                          | MSEL              | 1<1:0>    |                             |          | FSEL1<4:0                    | >                              |         | FLTEN0     | MSEL                        | 0<1:0>  | FSEL0<4:0> |           |            | 0000      |         |            |

| DUDU                        | C1FLTCON1                       | 31:16 FLTEN7 MSEL7<1:0> FS |                                 |                   | FSEL7<4:0 | SEL7<4:0> FLTEN6 MSEL6<1:0> |          |                              | FSEL6<4:0>                     |         |            |                             | 0000    |            |           |            |           |         |            |

| БООО                        | CIFLICONI                       | 15:0                       | FLTEN5                          | MSEL              | 5<1:0>    |                             |          | FSEL5<4:0                    | >                              |         | FLTEN4     | MSEL                        | 4<1:0>  | FSEL4<4:0> |           |            |           | 0000    |            |

| DUEU                        | C1FLTCON2                       | 31:16                      | FLTEN11                         | MSEL <sup>2</sup> | 11<1:0>   |                             |          | FSEL11<4:0                   | SEL11<4:0> FLTEN10 MSEL10<1:0> |         |            | FSEL10<4:0>                 |         |            |           | 0000       |           |         |            |

| POEO                        | GIFLICONZ                       | 15:0                       | FLTEN9                          | MSEL              | 9<1:0>    |                             |          | FSEL9<4:0                    | >                              |         | FLTEN8     | N8 MSEL8<1:0> FSEL8<4:0> 00 |         |            |           |            | 0000      |         |            |

| BUEU                        | C1FLTCON3                       | 31:16                      | FLTEN15                         | MSEL1             | 15<1:0>   |                             |          | FSEL15<4:0                   | >                              | -       | FLTEN14    | MSEL1                       | 14<1:0> |            | F         | SEL14<4:0> | >         | -       | 0000       |

| POLO                        | O IFLI CONS                     | 15:0                       | FLTEN13                         | MSEL1             | 13<1:0>   |                             |          | FSEL13<4:0                   | >                              |         | FLTEN12    | MSEL1                       | 12<1:0> |            | F         | SEL12<4:0> | ·         |         | 0000       |

| D140                        | C1RXFn                          | 31:16                      |                                 |                   |           |                             | ·        | SID<10:0>                    |                                |         | ·          |                             |         | -          | EXID      | _          | EID<1     | 7:16>   | xxxx       |

| B140 (n = 0-15)             | 15:0                            |                            |                                 |                   |           |                             |          |                              |                                |         |            |                             |         |            |           |            |           | xxxx    |            |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information. Note 1:

### REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/P               | R/P               | R/P               | R/P               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 | _                 |                  | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 |                  | _                |  |  |  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 7:0          | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           | r = Reserved bit | P = Programmable bit |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 **FVBUSONIO:** USB VBUS\_ON Selection bit

1 = VBUSON pin is controlled by the USB module

0 = VBUSON pin is controlled by the port function

bit 30 FUSBIDIO: USB USBID Selection bit

1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

bit 29 **IOL1WAY:** Peripheral Pin Select Configuration bit

1 = Allow only one reconfiguration

0 = Allow multiple reconfigurations

bit 28 **PMDL1WAY:** Peripheral Module Disable Configuration bit

1 = Allow only one reconfiguration

0 = Allow multiple reconfigurations

bit 27-16 Unimplemented: Read as '0'

bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

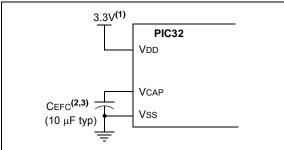

## 28.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX/5XX 64/100-pin devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX/5XX 64/100-pin family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 28-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 31.1** "DC Characteristics".

**Note:** It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

## 28.3.1 HIGH VOLTAGE DETECT (HVD)

The HVD module monitors the core voltage at the VCAP pin. If a voltage above the required level is detected on VCAP, the I/O pins are disabled and the device is held in Reset as long as the HVD condition persists. See parameter HV10 (VHVD) in Table 31-11 in **Section 31.1** "**PC Characteristics**" for more information.

### 28.3.2 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

### 28.3.3 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX/5XX 64/100-pin devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 31.1 "DC Characteristics"**.

FIGURE 28-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

- Note 1: These are typical operating voltages. Refer to Section 31.1 "DC Characteristics" for the full operating ranges of VDD.

- 2: It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

- 3: The typical voltage on the VCAP pin is 1.8V.

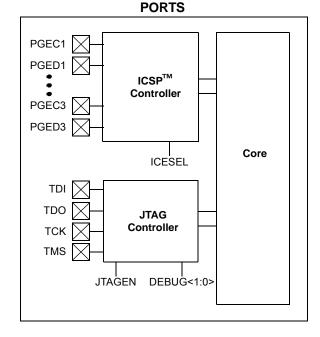

### 28.4 Programming and Diagnostics

PIC32MX1XX/2XX/5XX 64/100-pin devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming™ (ICSP™) interfaces

- · Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules that provide a range of functions to the application developer.

FIGURE 28-2: BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE

### 30.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 30.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 30.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 30.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

## **30.10 MPLAB PM3 Device Programmer**

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

TABLE 31-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS                    |                             |      |       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                                                 |  |  |  |  |  |

|---------------------------------------|-----------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup>      | Max. | Units | Conditions                                                                                                                                                                                                                                     |                                                 |  |  |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                             |      |       |                                                                                                                                                                                                                                                |                                                 |  |  |  |  |  |

| DC40k                                 | 33                          | 78   | μА    | -40°C                                                                                                                                                                                                                                          |                                                 |  |  |  |  |  |

| DC40I                                 | 49                          | 78   | μА    | +25°C                                                                                                                                                                                                                                          | Base Power-Down Current                         |  |  |  |  |  |

| DC40n                                 | 281                         | 450  | μА    | +85°C                                                                                                                                                                                                                                          | Base Power-Down Current                         |  |  |  |  |  |

| DC40m                                 | 559                         | 895  | μA    | +105°C                                                                                                                                                                                                                                         |                                                 |  |  |  |  |  |