Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f128ht-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4: PIN NAMES FOR 100-PIN GENERAL PURPOSE DEVICES

### **100-PIN TQFP (TOP VIEW)**

### PIC32MX130F128L PIC32MX150F256L PIC32MX170F512L

100

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                   |

|-------|---------------------------------------|-------|---------------------------------|

| 1     | AN28/RG15                             | 36    | Vss                             |

| 2     | Vdd                                   | 37    | VDD                             |

| 3     | AN22/RPE5/PMD5/RE5                    | 38    | TCK/CTED2/RA1                   |

| 4     | AN23/PMD6/RE6                         | 39    | AN34/RPF13/SCK3/RF13            |

| 5     | AN27/PMD7/RE7                         | 40    | AN35/RPF12/RF12                 |

| 6     | AN29/RPC1/RC1                         | 41    | AN12/PMA11/RB12                 |

| 7     | AN30/RPC2/RC2                         | 42    | AN13/PMA10/RB13                 |

| 8     | AN31/RPC3/RC3                         | 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 9     | RPC4/CTED7/RC4                        | 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 10    | AN16/C1IND/RPG6/SCK2/PMA5/RG6         | 45    | Vss                             |

| 11    | AN17/C1INC/RPG7/PMA4/RG7              | 46    | VDD                             |

| 12    | AN18/C2IND/RPG8/PMA3/RG8              | 47    | AN36/RPD14/RD14                 |

| 13    | MCLR                                  | 48    | AN37/RPD15/SCK4/RD15            |

| 14    | AN19/C2INC/RPG9/PMA2/RG9              | 49    | RPF4/PMA9/RF4                   |

| 15    | Vss                                   | 50    | RPF5/PMA8/RF5                   |

| 16    | Vdd                                   | 51    | RPF3/RF3                        |

| 17    | TMS/CTED1/RA0                         | 52    | AN38/RPF2/RF2                   |

| 18    | AN32/RPE8/RE8                         | 53    | AN39/RPF8/RF8                   |

| 19    | AN33/RPE9/RE9                         | 54    | RPF7/RF7                        |

| 20    | AN5/C1INA/RPB5/RB5                    | 55    | RPF6/SCK1/INT0/RF6              |

| 21    | AN4/C1INB/RB4                         | 56    | SDA1/RG3                        |

| 22    | PGED3/AN3/C2INA/RPB3/RB3              | 57    | SCL1/RG2                        |

| 23    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 | 58    | SCL2/RA2                        |

| 24    | PGEC1/AN1/RPB1/CTED12/RB1             | 59    | SDA2/RA3                        |

| 25    | PGED1/AN0/RPB0/RB0                    | 60    | TDI/CTED9/RA4                   |

| 26    | PGEC2/AN6/RPB6/RB6                    | 61    | TDO/RA5                         |

| 27    | PGED2/AN7/RPB7/CTED3/RB7              | 62    | VDD                             |

| 28    | VREF-/PMA7/RA9                        | 63    | OSC1/CLKI/RC12                  |

| 29    | VREF+/PMA6/RA10                       | 64    | OSC2/CLKO/RC15                  |

| 30    | AVdd                                  | 65    | Vss                             |

| 31    | AVss                                  | 66    | RPA14/RA14                      |

| 32    | AN8/RPB8/CTED10/RB8                   | 67    | RPA15/RA15                      |

| 33    | AN9/RPB9/CTED4/RB9                    | 68    | RPD8/RTCC/RD8                   |

| 34    | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 69    | RPD9/RD9                        |

| 35    | AN11/PMA12/RB11                       | 70    | RPD10/PMA15/RD10                |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 3 and MPLAB REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- *"Using MPLAB<sup>®</sup> ICD 3"* (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- *"MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide"* DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

## 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer or debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements

## 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

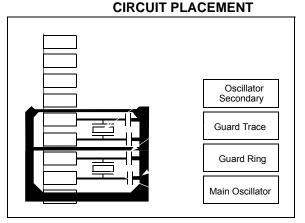

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

# FIGURE 2-3: SUGGESTED OSCILLATOR

<sup>© 2014-2016</sup> Microchip Technology Inc.

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source.For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX/5XX 64/100-pin devices to execute from data memory.

The key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1) mode address space

- Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- · Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

## 4.1 Memory Layout

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX/5XX 64/ 100-pin devices are illustrated in Figure 4-1 through Figure 4-4.

## 6.1 Control Registers

# TABLE 6-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | a         |       |                                                                                                                         |       |       |       |       |      | Bi        | ts      |      |      |      |      |      |      |      | 6          |

|-----------------------------|------------------------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|------|-----------|---------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14                                                                                                                   | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8      | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     | _     | —                                                                                                                       | —     | —     | _     |       | —    |           | —       | —    | —    | —    |      |      | —    | —    | 0000       |

| 1400                        |                        | 15:0      | WR    | WR         WRER         LVDERR         LVDSTAT         —         —         —         —         —         —         0000 |       |       |       |       |      |           |         |      |      |      |      |      |      |      |            |

| F410                        | NVMKEY                 | 31:16     |       | NVMKEY<31:0>                                                                                                            |       |       |       |       |      |           |         | 0000 |      |      |      |      |      |      |            |

|                             |                        | 15:0      |       |                                                                                                                         |       |       |       |       |      |           | 1501.02 |      |      |      |      |      |      |      | 0000       |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                                                                                                                         |       |       |       |       |      | NVMADE    | P<31.05 |      |      |      |      |      |      |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |       |                                                                                                                         |       |       |       |       |      | INVIVIADE | K~51.02 |      |      |      |      |      |      |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       |                                                                                                                         |       |       |       |       |      |           | A-31.0> |      |      |      |      |      |      |      | 0000       |

| 1430                        | NVINDAIA               | 15:0      |       | NVMDATA<31:0>                                                                                                           |       |       |       |       |      |           |         | 0000 |      |      |      |      |      |      |            |

| F440                        | NVMSRC                 | 31:16     |       | NUMERCARER 201.0                                                                                                        |       |       |       |       |      |           |         | 0000 |      |      |      |      |      |      |            |

| F440                        | ADDR                   | 15:0      |       | NVMSRCADDR<31'0>                                                                                                        |       |       |       |       |      |           |         | 0000 |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 =Clock is multiplied by 17

- 001 =Clock is multiplied by 16

- 000 = Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = PLL module is in lock or PLL module start-up timer is satisfied

- 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 **CF:** Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

NOTES:

| KE0131E      | $\frac{1}{2} = \frac{1}{2} = \frac{1}$ |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                 | —                 | _                 | —                 | _                 | _                | _                |  |  |

| 00.40        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                 | —                 | _                 | —                 | _                 | —                | —                |  |  |

| 45.0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | 0N <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |  |  |

| 7.0          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |  |  |

| 7:0          | GCEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |  |  |

# **REGISTER 18-1:** I2CxCON: $I^2C'x'$ CONTROL REGISTER ('x' = 1 AND 2)

| Legend:           | HC = Cleared in Hardwar | e                        |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the I<sup>2</sup>C module; all I<sup>2</sup>C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- SCLREL: SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

bit 12

0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 =Strict I<sup>2</sup>C Reserved Address Rule not enabled

### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                       | —                     | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 00.40        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                       | —                     | _                 | _                 | _                 | _                 | —                | —                |  |  |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    |                   |                   |                   |                   |                  |                  |  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> | ADDR<13:8>        |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                       |                       | ADDR<7:0>         |                   |                   |                   |                  |                  |  |  |

### REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

**Note:** If the DUALBUF bit (PMCON<17>) = 0, the bits in this register control both read and write target addressing. If the DUALBUF bit = 1, the bits in this register are not used. In this instance, use the PMRADDR register for Read operations and the PMWADDR register for Write operations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | —                 | _                 | —                 | —                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | -                 | —                 | —                 | -                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | RDATAIN<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                   |                   |                   | RDATAIN<          | <7:0>             |                   |                  |                  |  |

### REGISTER 20-10: PMRDIN: PARALLEL PORT READ INPUT DATA REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **RDATAIN<15:0>:** Port Read Input Data bits

**Note:** This register is only used when the DUALBUF bit (PMCON<17>) is set to '1' and exclusively for reads. If the DUALBUF bit is '0', the PMDIN register (Register 20-5) is used for reads instead of PMRDIN.

| REGIST  | ER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)                                               |

|---------|--------------------------------------------------------------------------------------------------------|

| bit 7-0 | ARPT<7:0>: Alarm Repeat Counter Value bits <sup>(3)</sup>                                              |

|         | 11111111 =Alarm will trigger 256 times                                                                 |

|         | •                                                                                                      |

|         | •                                                                                                      |

|         | •<br>00000000 =Alarm will trigger one time                                                             |

|         | The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1. |

| Note 1: | Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = $00$ and CHIME = $0$ . |

| 2:      | This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.             |

| 3:      | This assumes a CPU read will execute in less than 32 PBCLKs.                                           |

| Note:   | This register is reset only on a Power-on Reset (POR).                                                 |

|         |                                                                                                        |

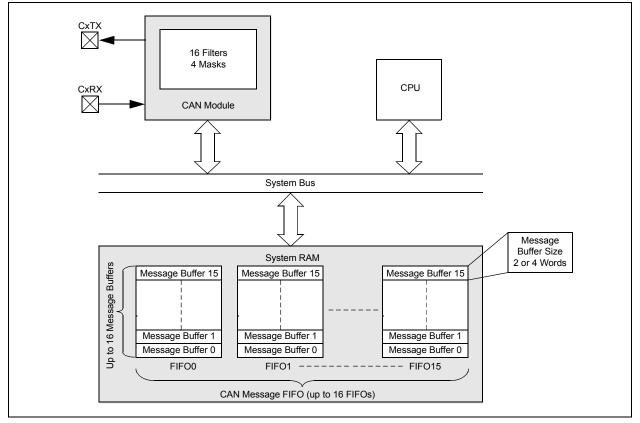

# 23.0 CONTROLLER AREA NETWORK (CAN)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Controller Area Network (CAN)" (DS60001154) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Controller Area Network (CAN) module supports the following key features:

- · Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- Message Reception and Transmission:

- 16 message FIFOs

- Each FIFO can have up to 16 messages for a total of 256 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 16 acceptance filters for message filtering

- Four acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

- DeviceNet<sup>™</sup> addressing support

- Additional Features:

- Loopback, Listen All Messages, and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32 system bus

- Use of DMA is not required

- Dedicated time-stamp timer

- Dedicated DMA channels

- Data-only Message Reception mode

Figure 23-1 illustrates the general structure of the CAN module.

### FIGURE 23-1: PIC32 CAN MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 |                   | —                 | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 |                   | —                 | _                 | —                | -                |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | RXOVF15           | RXOVF14           | RXOVF13           | RXOVF12           | RXOVF11           | RXOVF10           | RXOVF9           | RXOVF8           |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | RXOVF7            | RXOVF6            | RXOVF5            | RXOVF4            | RXOVF3            | RXOVF2            | RXOVF1           | RXOVF0           |

### REGISTER 23-7: C1RXOVF: CAN RECEIVE FIFO OVERFLOW STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 RXOVF<15:0>: FIFOx Receive Overflow Interrupt Pending bit

1 = FIFO has overflowed

0 = FIFO has not overflowed

### REGISTER 23-8: C1TMR: CAN TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 51.24        | 31:24 CANTS<15:8> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        |                   | CANTS<7:0>        |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.6         | CANTSPRE<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          |                   |                   |                   | CANTSPF           | RE<7:0>           |                   |                  |                  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 CANTS<15:0>: CAN Time Stamp Timer bits

This is a free-running timer that increments every CANTSPRE system clocks when the CANCAP bit (C1CON<20>) is set.

### bit 15-0 CANTSPRE<15:0>: CAN Time Stamp Timer Prescaler bits 1111 1111 1111 1111 = CAN time stamp timer (CANTS) increments every 65,535 system clocks . . 0000 0000 0000 = CAN time stamp timer (CANTS) increments every system clock

**Note 1:** C1TMR will be paused when CANCAP = 0.

2: The C1TMR prescaler count will be reset on any write to C1TMR (CANTSPRE will be unaffected).

| REGISTE   | R 23-10: C1FLTCON0: CAN FILTER CONTROL REGISTER 0 (CONTINUED)                               |

|-----------|---------------------------------------------------------------------------------------------|

| bit 20-16 | FSEL2<4:0>: FIFO Selection bits                                                             |

|           | 11111 = Reserved                                                                            |

|           | •                                                                                           |

|           | •                                                                                           |

|           | 10000 = Reserved                                                                            |

|           | 01111 = Message matching filter is stored in FIFO buffer 15                                 |

|           |                                                                                             |

|           | •                                                                                           |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                  |

| bit 15    | FLTEN1: Filter 1 Enable bit                                                                 |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                             |

| bit 14-13 | MSEL1<1:0>: Filter 1 Mask Select bits                                                       |

|           | 11 = Acceptance Mask 3 selected                                                             |

|           | 10 = Acceptance Mask 2 selected                                                             |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                          |

| bit 12-8  | FSEL1<4:0>: FIFO Selection bits                                                             |

| DIL 12-0  | 11111 = Reserved                                                                            |

|           | •                                                                                           |

|           |                                                                                             |

|           | •<br>10000 = Reserved                                                                       |

|           | 01111 = Message matching filter is stored in FIFO buffer 15                                 |

|           | •                                                                                           |

|           | •                                                                                           |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                  |

| bit 7     | FLTEN0: Filter 0 Enable bit                                                                 |

|           | 1 = Filter is enabled                                                                       |

|           | 0 = Filter is disabled                                                                      |

| bit 6-5   | MSEL0<1:0>: Filter 0 Mask Select bits                                                       |

|           | 11 = Acceptance Mask 3 selected                                                             |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                          |

|           | 00 = Acceptance Mask 0 selected                                                             |

| bit 4-0   | FSEL0<4:0>: FIFO Selection bits                                                             |

|           | 11111 = Reserved                                                                            |

|           | •                                                                                           |

|           |                                                                                             |

|           | •<br>10000 = Reserved                                                                       |

|           | 01111 = Message matching filter is stored in FIFO buffer 15                                 |

|           |                                                                                             |

|           | •                                                                                           |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                  |

| Nata      | The bits in this register can only be medified if the corresponding filter enable (ELTEN) b |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED) bit 20-16 FSEL10<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 FLTEN9: Filter 9 Enable bit bit 15 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL9<1:0>: Filter 9 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL9<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN8: Filter 8 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL8<1:0>: Filter 8 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL8<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. Note:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4                 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-0               | r-1               | r-1               | R/P                               | r-1               | r-1               | r-1              | R/P              |

| 31:24        | —                 | —                 | _                 | СР                                | —                 | —                 | _                | BWP              |

| 00.40        | r-1               | r-1               | r-1               | r-1                               | R/P               | R/P               | R/P              | R/P              |

| 23:16        | —                 | _                 | _                 | _                                 | PWP<9:6>          |                   |                  |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P                               | R/P               | R/P               | r-1              | r-1              |

| 15:8         | PWP<5:0>          |                   |                   |                                   |                   | _                 | —                |                  |

| 7.0          | r-1               | r-1               | r-1               | R/P                               | R/P               | R/P               | R/P              | R/P              |

| 7:0          | _                 | _                 | _                 | ICESEL<1:0> JTAGEN <sup>(1)</sup> |                   |                   | DEBU             | G<1:0>           |

### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | P = Programmable bit     |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31 Reserved: Write '0'

- bit 30-29 Reserved: Write '1'

- bit 28 **CP:** Code-Protect bit

- Prevents boot and program Flash memory from being read or modified by an external programming device.

- 1 = Protection is disabled

- 0 = Protection is enabled

- bit 27-25 Reserved: Write '1'

- bit 24 **BWP:** Boot Flash Write-Protect bit

- Prevents boot Flash memory from being modified during code execution.

- 1 = Boot Flash is writable

- 0 = Boot Flash is not writable

- bit 23-20 Reserved: Write '1'

- Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

# 29.0 INSTRUCTION SET

The PIC32MX1XX/2XX/5XX 64/100-pin family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to *"MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set"* at www.imgtec.com for more information.

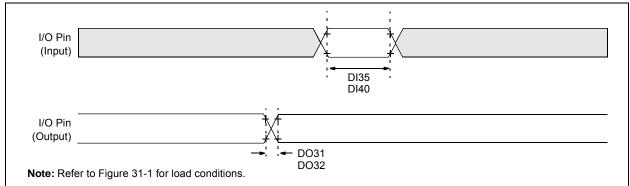

### FIGURE 31-3: I/O TIMING CHARACTERISTICS

### TABLE 31-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                       |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |                        |      |         |            |

|--------------------|---------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|------|---------|------------|

| Param.<br>No.      | Symbol Characteristics <sup>(2)</sup> |                           | stics <sup>(2)</sup>                                                                                                                                                                                                                                                                | Min. | Typical <sup>(1)</sup> | Max. | Units   | Conditions |