Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K × 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f128ht-v-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

|                             | LE 19-1:                 | UAI       |        | ROUGE   | UARTS  |       |           |       |       | (ש.         |             |         |       |          |          |      |        |       |            |

|-----------------------------|--------------------------|-----------|--------|---------|--------|-------|-----------|-------|-------|-------------|-------------|---------|-------|----------|----------|------|--------|-------|------------|

| ess                         |                          | đ         |        |         |        |       |           |       |       | Bi          | ts          |         |       |          |          |      |        |       | s          |

| Virtual Address<br>(BF80_#) | Register<br>Name         | Bit Range | 31/15  | 30/14   | 29/13  | 28/12 | 27/11     | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6440                        |                          | 31:16     | _      | —       | —      |       | —         |       | —     | —           |             | —       | _     |          | _        | _    | _      |       | 0000       |

| 0440                        | USBRG. /                 | 15:0      |        |         |        |       |           |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 6600                        | U4MODE <sup>(1)</sup>    | 31:16     | _      | _       | _      |       | _         |       | _     | _           |             | —       | _     |          | _        | _    | _      |       | 0000       |

| 0000                        | 04IVIODL.                | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD     | —     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6610                        | U4STA <sup>(1)</sup>     | 31:16     | _      | —       | —      | -     | —         | _     | —     | ADM_EN      |             |         |       | ADDF     | R<7:0>   |      | -      |       | 0000       |

| 0010                        | 04017                    | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK    | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6620                        | U4TXREG                  | 31:16     | —      |         | —      | _     | _         | _     |       | —           | _           | —       | —     | _        | —        | —    | —      | —     | 0000       |

| 0020                        | OFINICO                  | 15:0      | —      |         | —      | _     | _         | _     |       | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 6630                        | U4RXREG                  | 31:16     | —      |         | —      | _     | _         | _     |       | _           |             | —       | _     | _        | _        | _    | _      | —     | 0000       |

| 0000                        | OHIVILO                  | 15:0      | —      |         | —      | _     | _         | _     |       | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 6640                        | U4BRG <sup>(1)</sup>     | 31:16     | —      | —       | —      | —     | —         | —     | —     | —           | —           | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0010                        | U IBIKO                  | 15:0      |        |         |        |       |           |       | Bau   | d Rate Gen  | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 6800                        | U5MODE <sup>(1,2)</sup>  | 31:16     |        | —       | —      |       | —         | _     | —     |             |             | —       | —     |          | —        | —    | —      |       | 0000       |

|                             | 00111022                 | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD     | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6810                        | U5STA <sup>(1,2)</sup>   | 31:16     | —      | —       | —      | —     | —         | —     | —     | ADM_EN      |             |         |       | 1        | R<7:0>   | 1    | 1      | 1     | 0000       |

|                             |                          | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK    | UTXEN | UTXBF | TRMT        | URXIS       | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6820                        | U5TXREG <sup>(1,2)</sup> | 31:16     | _      |         | —      | _     | —         |       |       |             | _           | —       | —     | —        |          | —    |        |       | 0000       |

|                             |                          | 15:0      | _      |         | —      | _     | —         |       |       | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 6830                        | U5RXREG <sup>(1,2)</sup> | 31:16     | _      |         | —      | —     | —         |       |       | —           | —           | —       | —     | —        | —        | —    | —      | —     | 0000       |

|                             |                          | 1010      | —      |         | —      | —     | —         |       |       | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 6840                        | U5BRG <sup>(1,2)</sup>   | 31:16     | —      | —       | —      | —     | —         | —     | —     | —           | —           | —       | —     | —        | —        | —    | —      |       | 0000       |

|                             |                          | 15:0      |        |         |        |       | 'o' Booot |       |       | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

## TABLE 19-1: UART1 THROUGH UART5 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register is only available on 100-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 31:24        | U-0                 | U-0                 |

| 31.24        | —                 | —                 | —                 | _                 | —                 | —                 | —                   | —                   |

| 23:16        | U-0                 | U-0                 |

| 23.10        | —                 | —                 | —                 | _                 | —                 | —                 | —                   | —                   |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                 | —                 | FORM<2:0>         |                     |                     |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7.0          |                   | SSRC<2:0>         |                   | CLRASAM           | _                 | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1

#### Legend:

bit 14

| R = Readable bit  | = Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|---------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12-11 Unimplemented: Read as '0'

- bit 10-8 **FORM<2:0>:** Data Output Format bits

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

#### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing SAMP bit ends sampling and starts conversion

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | _                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | —                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

## **REGISTER 23-3: C1INT: CAN INTERRUPT REGISTER**

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | IVRIE: Invalid Message Received Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | <b>WAKIE:</b> CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                            |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | <b>MODIE:</b> Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by cl                                                                                          |

learing or setting the ON bit N (C1CON<15>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | -                 | —                 | -                 | -                 | -                 | _                 | _                | —                |  |  |

| 22:16        | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | _                 | —                 | TXBO              | TXBP              | RXBP              | TXWARN            | RXWARN           | EWARN            |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | TERRCNT<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | RERRC             | NT<7:0>           |                   |                  |                  |  |  |

### REGISTER 23-5: C1TREC: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-22 Unimplemented: Read as '0'

bit 21 **TXBO:** Transmitter in Error State Bus OFF (TERRCNT  $\geq$  256)

- bit 20 **TXBP:** Transmitter in Error State Bus Passive (TERRCNT ≥ 128)

- bit 19 **RXBP:** Receiver in Error State Bus Passive (RERRCNT  $\geq$  128)

bit 18 **TXWARN:** Transmitter in Error State Warning (128 > TERRCNT ≥ 96)

bit 17 **RXWARN:** Receiver in Error State Warning (128 > RERRCNT  $\ge$  96)

bit 16 EWARN: Transmitter or Receiver is in Error State Warning

- bit 15-8 TERRCNT<7:0>: Transmit Error Counter

- bit 7-0 RERRCNT<7:0>: Receive Error Counter

## REGISTER 23-6: C1FSTAT: CAN FIFO STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   |                   | —                 | —                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | _                 | —                 | _                 | _                 | _                | _                |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | FIFOIP15          | FIFOIP14          | FIFOIP13          | FIFOIP12          | FIFOIP11          | FIFOIP10          | FIFOIP9          | FIFOIP8          |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | FIFOIP7           | FIFOIP6           | FIFOIP5           | FIFOIP4           | FIFOIP3           | FIFOIP2           | FIFOIP1          | FIFOIP0          |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 FIFOIP<15:0>: FIFOx Interrupt Pending bits

1 = One or more enabled FIFO interrupts are pending

0 = No FIFO interrupts are pending

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|

| 31:24        | R/W-0              | R/W-0              |  |  |  |

| 31.24        | C1FIFOBA<31:24>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 23:16        | R/W-0              | R/W-0              |  |  |  |

| 23.10        | C1FIFOBA<23:16>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 15:8         | R/W-0              | R/W-0              |  |  |  |

| 10.0         | C1FIFOBA<15:8>    |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |

| 7:0          |                   |                   |                   | C1FIFO            | BA<7:0>           |                   |                    |                    |  |  |  |

#### REGISTER 23-15: C1FIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

#### Legend:

| Logonal           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 C1FIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Bits <1:0> are read-only and read as '0', forcing the messages to be 32-bit word-aligned in device RAM.

**Note 1:** This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                   | —                 | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15.0         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | —                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | _                 | —                 | —                 | -                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | —                 |                   | _                 | _                 | _                 | -                | _                |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | SIDL              | —                 | —                 | —                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 | —                 | _                 |                   | _                 | C3OUT             | C2OUT            | C10UT            |

## REGISTER 24-2: CMSTAT: COMPARATOR STATUS REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

bit 13 **SIDL:** Stop in IDLE Control bit

1 = All Comparator modules are disabled in IDLE mode

0 = All Comparator modules continue to operate in the IDLE mode

#### bit 12-3 Unimplemented: Read as '0'

- bit 2 C3OUT: Comparator Output bit

- 1 = Output of Comparator 3 is a '1'

- 0 = Output of Comparator 3 is a '0'

#### bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

#### bit 0 **C1OUT:** Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

| bit 24    | EDG1STAT: Edge 1 Status bit                                                                                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Indicates the status of Edge 1 and can be written to control edge source                                                                                                                                                                                                                                         |

|           | 1 = Edge 1 has occurred                                                                                                                                                                                                                                                                                          |

|           | 0 = Edge 1 has not occurred                                                                                                                                                                                                                                                                                      |

| bit 23    | EDG2MOD: Edge 2 Edge Sampling Select bit                                                                                                                                                                                                                                                                         |

|           | 1 = Input is edge-sensitive                                                                                                                                                                                                                                                                                      |

|           | 0 = Input is level-sensitive                                                                                                                                                                                                                                                                                     |

| bit 22    | EDG2POL: Edge 2 Polarity Select bit                                                                                                                                                                                                                                                                              |

|           | 1 = Edge 2 programmed for a positive edge response                                                                                                                                                                                                                                                               |

|           | 0 = Edge 2 programmed for a negative edge response                                                                                                                                                                                                                                                               |

| bit 21-18 | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                                                                                                                                                                                                                          |

|           | 1111 = IC4 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1110 = C2OUT pin is selected                                                                                                                                                                                                                                                                                     |

|           | 1101 = C1OUT pin is selected                                                                                                                                                                                                                                                                                     |

|           | 1100 = PBCLK clock is selected                                                                                                                                                                                                                                                                                   |

|           | 1011 = IC3 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1010 = IC2 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1001 = IC1 Capture Event is selected                                                                                                                                                                                                                                                                             |

|           | 1000 = CTED13 pin is selected<br>0111 = CTED12 pin is selected                                                                                                                                                                                                                                                   |

|           | 0110 = CTED12 pin is selected                                                                                                                                                                                                                                                                                    |

|           | 0101 = CTED10 pin is selected                                                                                                                                                                                                                                                                                    |

|           | 0100 = CTED9 pin is selected                                                                                                                                                                                                                                                                                     |

|           | 0011 = CTED1 pin is selected                                                                                                                                                                                                                                                                                     |

|           | 0010 = CTED2 pin is selected                                                                                                                                                                                                                                                                                     |

|           | 0001 = OC1 Compare Event is selected                                                                                                                                                                                                                                                                             |

|           | 0000 = Timer1 Event is selected                                                                                                                                                                                                                                                                                  |

| bit 17-16 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |

| bit 15    | ON: ON Enable bit                                                                                                                                                                                                                                                                                                |

|           | 1 = Module is enabled                                                                                                                                                                                                                                                                                            |

|           | 0 = Module is disabled                                                                                                                                                                                                                                                                                           |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                       |

| bit 13    | CTMUSIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                  |

|           | 1 = Discontinue module operation when device enters Idle mode                                                                                                                                                                                                                                                    |

|           | 0 = Continue module operation in Idle mode                                                                                                                                                                                                                                                                       |

| bit 12    | TGEN: Time Generation Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                  |

|           | 1 = Enables edge delay generation                                                                                                                                                                                                                                                                                |

|           | 0 = Disables edge delay generation                                                                                                                                                                                                                                                                               |

| bit 11    | EDGEN: Edge Enable bit                                                                                                                                                                                                                                                                                           |

|           | 1 = Edges are not blocked                                                                                                                                                                                                                                                                                        |

|           | 0 = Edges are blocked                                                                                                                                                                                                                                                                                            |

| Note 1:   | When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.                                                                                                                                                                                                    |

| 2:        | The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion                                                                                                                                                                                                               |

| -         | cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor |

|           | array.                                                                                                                                                                                                                                                                                                           |

| -         |                                                                                                                                                                                                                                                                                                                  |

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

## 27.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

#### 27.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The peripheral bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

## 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

|               |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                                                                                                                  |                        |            |       |                                                   |

|---------------|--------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------|---------------------------------------------------|

|               |        |                                                                       | $\begin{array}{ll} \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \ 1 \\ -40^\circ C \leq TA \leq +105^\circ C \end{array}$ |                        |            |       |                                                   |

| Param.<br>No. | Symbol | Characteristics                                                       | Min.                                                                                                                                             | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |

|               | VIL    | Input Low Voltage                                                     |                                                                                                                                                  |                        |            |       |                                                   |

| DI10          |        | I/O Pins with PMP                                                     | Vss                                                                                                                                              | —                      | 0.15 Vdd   | V     |                                                   |

|               |        | I/O Pins                                                              | Vss                                                                                                                                              | —                      | 0.2 Vdd    | V     |                                                   |

| DI18          |        | SDAx, SCLx                                                            | Vss                                                                                                                                              | —                      | 0.3 VDD    | V     | SMBus disabled<br>(Note 4)                        |

| DI19          |        | SDAx, SCLx                                                            | Vss                                                                                                                                              | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |

|               | VIH    | Input High Voltage                                                    |                                                                                                                                                  |                        |            |       |                                                   |

| DI20          |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                               | 0.65 VDD                                                                                                                                         | _                      | Vdd        | V     | (Note 4,6)                                        |

|               |        | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>                       | 0.25 VDD + 0.8V                                                                                                                                  | —                      | 5.5        | V     | (Note 4,6)                                        |

|               |        | I/O Pins 5V-tolerant <sup>(5)</sup>                                   | 0.65 VDD                                                                                                                                         | —                      | 5.5        | V     |                                                   |

| DI28          |        | SDAx, SCLx                                                            | 0.65 VDD                                                                                                                                         | —                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |

| DI29          |        | SDAx, SCLx                                                            | 2.1                                                                                                                                              | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |

| DI30          | ICNPU  | Change Notification<br>Pull-up Current                                | _                                                                                                                                                | -200                   | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |

| DI31          | ICNPD  | Change Notification<br>Pull-down Current <sup>(4)</sup>               | 50                                                                                                                                               | 200                    | —          | μA    | VDD = 3.3V, VPIN = VDD                            |

|               | lı∟    | Input Leakage Current<br>(Note 3)                                     |                                                                                                                                                  |                        |            |       |                                                   |

| DI50          |        | I/O Ports                                                             | _                                                                                                                                                | —                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |

| DI51          |        | Analog Input Pins                                                     | _                                                                                                                                                | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |

| DI55          |        | MCLR <sup>(2)</sup>                                                   | _                                                                                                                                                | _                      | <u>+</u> 1 | μA    | $VSS \le VPIN \le VDD$                            |

| DI56          |        | OSC1                                                                  | -                                                                                                                                                | —                      | <u>+</u> 1 | μΑ    | $VSS \le VPIN \le VDD,$ XT and HS modes           |

## TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.

- **6:** The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

#### FIGURE 31-10: SPIx MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS SCKx (CKP = 0) SP11 SP10 SP21 SP20 SCKx (CKP = 1) SP35 SP20 SP21 SDOx MSb Bit 14 -1 LSb **SP31** SP30 SDIx LSb In MSb In Bit 14 SP40 'SP41' Note: Refer to Figure 31-1 for load conditions.

## TABLE 31-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |       |                    |

|--------------------|-----------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>             | Min.                                                                                                                                                                                                                                                                                | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10               | TscL                  | SCKx Output Low Time<br>(Note 3)           | Тѕск/2                                                                                                                                                                                                                                                                              | —                      | _    | ns    | _                  |

| SP11               | TscH                  | SCKx Output High Time (Note 3)             | Тѕск/2                                                                                                                                                                                                                                                                              | —                      | _    | ns    | _                  |

| SP20               | TscF                  | SCKx Output Fall Time (Note 4)             | —                                                                                                                                                                                                                                                                                   | —                      | _    | ns    | See parameter DO32 |

| SP21               | TscR                  | SCKx Output Rise Time (Note 4)             | —                                                                                                                                                                                                                                                                                   | —                      | -    | ns    | See parameter DO31 |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)        | —                                                                                                                                                                                                                                                                                   | —                      | -    | ns    | See parameter DO32 |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)        | —                                                                                                                                                                                                                                                                                   | —                      | _    | ns    | See parameter DO31 |

| SP35               | TscH2doV,             | SDOx Data Output Valid after               | —                                                                                                                                                                                                                                                                                   | —                      | 15   | ns    | VDD > 2.7V         |

|                    | TscL2doV              | SCKx Edge                                  | _                                                                                                                                                                                                                                                                                   | —                      | 20   | ns    | VDD < 2.7V         |

| SP40               | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge | 10                                                                                                                                                                                                                                                                                  | —                      | _    | ns    | _                  |

| SP41               | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 10                                                                                                                                                                                                                                                                                  | —                      |      | ns    | _                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

### TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHARACTERISTICS |             |                            |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |                           |                            |  |

|--------------------|-------------|----------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------|----------------------------|--|

| Param.<br>No.      | Symbol      | Charact                    | eristics                      | Min.                                                                                                                                                                                                                                                                                | Max. | Units                     | Conditions                 |  |

| IS34               | THD:STO     | Stop Condition             | 100 kHz mode                  | 4000                                                                                                                                                                                                                                                                                | _    | ns                        | —                          |  |

|                    |             | Hold Time                  | 400 kHz mode                  | 600                                                                                                                                                                                                                                                                                 | —    | ns                        |                            |  |

|                    |             |                            | 1 MHz mode<br>(Note 1)        | 250                                                                                                                                                                                                                                                                                 |      | ns                        |                            |  |

| IS40               | S40 TAA:SCL | Output Valid from<br>Clock | 100 kHz mode                  | 0                                                                                                                                                                                                                                                                                   | 3500 | ns                        | —                          |  |

|                    |             |                            | 400 kHz mode                  | 0                                                                                                                                                                                                                                                                                   | 1000 | ns                        |                            |  |

|                    |             |                            | 1 MHz mode<br><b>(Note 1)</b> | 0                                                                                                                                                                                                                                                                                   | 350  | ns                        |                            |  |

| IS45               | TBF:SDA     | Bus Free Time              | 100 kHz mode                  | 4.7                                                                                                                                                                                                                                                                                 | —    | μs                        | The amount of time the bus |  |

|                    |             | 400 kHz mode               | 1.3                           | _                                                                                                                                                                                                                                                                                   | μs   | must be free before a new |                            |  |

|                    |             |                            | 1 MHz mode<br><b>(Note 1)</b> | 0.5                                                                                                                                                                                                                                                                                 | _    | μS                        | transmission can start     |  |

| IS50               | Св          | Bus Capacitive Lo          | ading                         |                                                                                                                                                                                                                                                                                     | 400  | pF                        | —                          |  |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

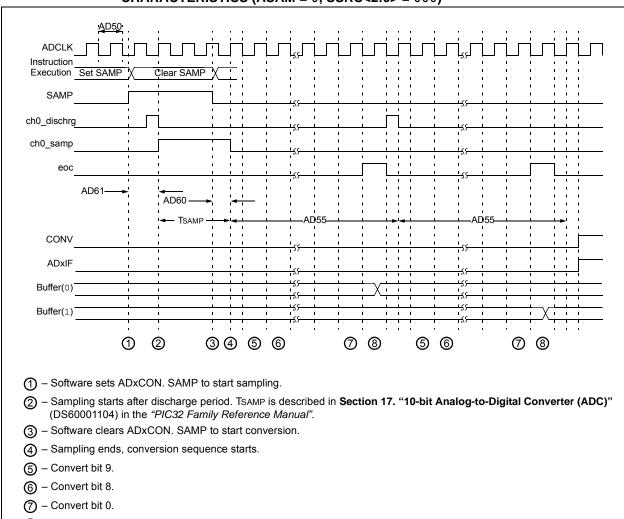

### FIGURE 31-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

(8) – One TAD for end of conversion.

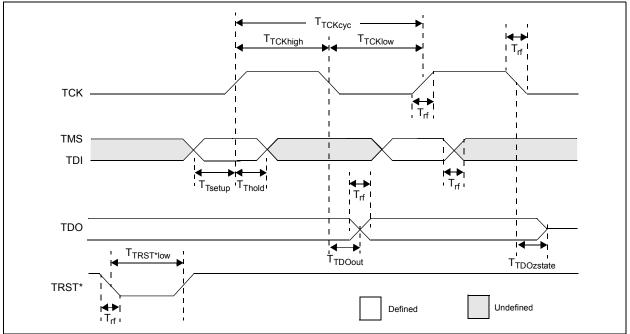

## FIGURE 31-23: EJTAG TIMING CHARACTERISTICS

### TABLE 31-42: EJTAG TIMING REQUIREMENTS

| AC CHARACTERISTICS |            |                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |

|--------------------|------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|

| Param.<br>No.      | Symbol     | Description <sup>(1)</sup>                       | Min.                                                                                                                                                                                                                                                                               | Max. | Units | Conditions |  |

| EJ1                | Ттсксус    | TCK Cycle Time                                   | 25                                                                                                                                                                                                                                                                                 |      | ns    |            |  |

| EJ2                | Ттскнідн   | TCK High Time                                    | 10                                                                                                                                                                                                                                                                                 |      | ns    | _          |  |