Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f128ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

64

1

64

#### TABLE 3: **PIN NAMES FOR 64-PIN USB DEVICES**

64-PIN QFN<sup>(4)</sup> AND TQFP (TOP VIEW)

PIC32MX230F128H PIC32MX530F128H PIC32MX250F256H PIC32MX550F256H PIC32MX270F512H PIC32MX570F512H

|       |                                           | QF | N <sup>(4)</sup> | TQFP                  |

|-------|-------------------------------------------|----|------------------|-----------------------|

| Pin # | Full Pin Name                             | Pi | in #             | Full Pin Name         |

| 1     | AN22/RPE5/PMD5/RE5                        | 3  | 33               | USBID/RPF3/RF3        |

| 2     | AN23/PMD6/RE6                             | 3  | 34               | VBUS                  |

| 3     | AN27/PMD7/RE7                             | 3  | 35               | VUSB3V3               |

| 4     | AN16/C1IND/RPG6/SCK2/PMA5/RG6             | 3  | 36               | D-                    |

| 5     | AN17/C1INC/RPG7/PMA4/RG7                  | 3  | 37               | D+                    |

| 6     | AN18/C2IND/RPG8/PMA3/RG8                  | 3  | 38               | VDD                   |

| 7     | MCLR                                      | 3  | 39               | OSC1/CLKI/RC12        |

| 8     | AN19/C2INC/RPG9/PMA2/RG9                  | 4  | 40               | OSC2/CLKO/RC15        |

| 9     | Vss                                       | 4  | 41               | Vss                   |

| 10    | Vdd                                       | 4  | 42               | RPD8/RTCC/RD8         |

| 11    | AN5/C1INA/RPB5/VBUSON/RB5                 | 4  | 43               | RPD9/SDA1/RD9         |

| 12    | AN4/C1INB/RB4                             | 4  | 44               | RPD10/SCL1/PMA15/RD10 |

| 13    | PGED3/AN3/C2INA/RPB3/RB3                  | 4  | 45               | RPD11/PMA14/RD11      |

| 14    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2     | 4  | 46               | RPD0/INT0/RD0         |

| 15    | PGEC1/VREF-/AN1/RPB1/CTED12/RB1           | 4  | 47               | SOSCI/RPC13/RC13      |

| 16    | PGED1/VREF+/AN0/RPB0/PMA6/RB0             | 4  | 48               | SOSCO/RPC14/T1CK/RC14 |

| 17    | PGEC2/AN6/RPB6/RB6                        | 4  | 49               | AN24/RPD1/RD1         |

| 18    | PGED2/AN7/RPB7/CTED3/RB7                  | 5  | 50               | AN25/RPD2/SCK1/RD2    |

| 19    | AVDD                                      | 5  | 51               | AN26/C3IND/RPD3/RD3   |

| 20    | AVss                                      | 5  | 52               | RPD4/PMWR/RD4         |

| 21    | AN8/RPB8/CTED10/RB8                       | 5  | 53               | RPD5/PMRD/RD5         |

| 22    | AN9/RPB9/CTED4/PMA7/RB9                   | 5  | 54               | C3INC/RD6             |

| 23    | TMS/CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 5  | 55               | C3INB/RD7             |

| 24    | TDO/AN11/PMA12/RB11                       | 5  | 56               | VCAP                  |

| 25    | Vss                                       | 5  | 57               | VDD                   |

| 26    | Vdd                                       | 5  | 58               | C3INA/RPF0/RF0        |

| 27    | TCK/AN12/PMA11/RB12                       | 5  | 59               | RPF1/RF1              |

| 28    | TDI/AN13/PMA10/RB13                       | e  | 60               | PMD0/RE0              |

| 29    | AN14/RPB14/SCK3/CTED5/PMA1/RB14           | 6  | 61               | PMD1/RE1              |

| 30    | AN15/RPB15/OCFB/CTED6/PMA0/RB15           | 6  | 62               | AN20/PMD2/RE2         |

| 31    | RPF4/SDA2/PMA9/RF4                        | 6  | 63               | RPE3/CTPLS/PMD3/RE3   |

| 32    | RPF5/SCL2/PMA8/RF5                        | 6  | 64               | AN21/PMD4/RE4         |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 11.0 "I/O Ports" for more information. 2: 3: Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally. The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

#### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Name        | Function                                                                                                                                                              |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| HWREna                  | Enables access via the RDHWR instruction to selected hardware registers.                                                                                              |

| BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.                                                                                                    |

| Count <sup>(1)</sup>    | Processor cycle count.                                                                                                                                                |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| Compare <sup>(1)</sup>  | Timer interrupt control.                                                                                                                                              |

| Status <sup>(1)</sup>   | Processor status and control.                                                                                                                                         |

| IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                                                                                                                  |

| Cause <sup>(1)</sup>    | Cause of last general exception.                                                                                                                                      |

| EPC <sup>(1)</sup>      | Program counter at last exception.                                                                                                                                    |

| PRId                    | Processor identification and revision.                                                                                                                                |

| EBASE                   | Exception vector base register.                                                                                                                                       |

| Config                  | Configuration register.                                                                                                                                               |

| Config1                 | Configuration register 1.                                                                                                                                             |

| Config2                 | Configuration register 2.                                                                                                                                             |

| Config3                 | Configuration register 3.                                                                                                                                             |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| Debug <sup>(2)</sup>    | Debug control and exception status.                                                                                                                                   |

| DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                                                                                                              |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| ErrorEPC <sup>(1)</sup> | Program counter at last error.                                                                                                                                        |

| DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                                                                                                                    |

|                         | NameReservedHWREnaBadVAddr(1)Count(1)ReservedCompare(1)Status(1)IntCtl(1)Cause(1)EPC(1)PRIdEBASEConfigConfig1Config2Config3ReservedDebug(2)DEPC(2)ReservedErrorEPC(1) |

| TABLE 3-2. COPROCESSOR UREGISTERS | <b>TABLE 3-2:</b> | <b>COPROCESSOR 0 REGISTERS</b> |

|-----------------------------------|-------------------|--------------------------------|

|-----------------------------------|-------------------|--------------------------------|

Note 1: Registers used in exception processing.

**2:** Registers used during debug.

| REGIST  | ER 5-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| bit 9-8 | IS1<1:0>: Interrupt Subpriority bits                                                                                  |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                            |

| bit 4-2 | IP0<2:0>: Interrupt Priority bits                                                                                     |

|         | 111 = Interrupt priority is 7                                                                                         |

|         | •                                                                                                                     |

|         |                                                                                                                       |

|         | 010 = Interrupt priority is 2                                                                                         |

|         | 001 = Interrupt priority is 1                                                                                         |

|         | 000 = Interrupt is disabled                                                                                           |

| bit 1-0 | IS0<1:0>: Interrupt Subpriority bits                                                                                  |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 5-1 for the exact bit definitions. |

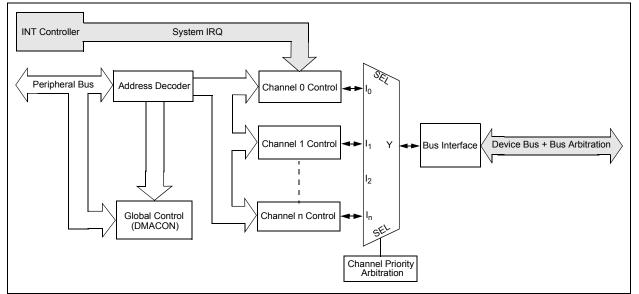

### 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

The following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

#### FIGURE 9-1: DMA BLOCK DIAGRAM

| REGIOTE      |                   |                       |                   |                   |                    |                   |                  |                  |  |  |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |  |  |

| 31:24        | —                 | —                     | BYTO<1:0>         |                   | WBO <sup>(1)</sup> | _                 | _                | BITO             |  |  |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                     | —                 | -                 | —                  | _                 | -                | _                |  |  |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | -                 | —                  | (                 | CRCCH<2:0>       |                  |  |  |

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

#### Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit<sup>(1</sup>

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| REGISTE      | REGISTER 9-8: DCHXECON: DMA CHANNEL 'X' EVENT CONTROL REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|----------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                              | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24        | U-0                                                            | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                                                              | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |

| 22:16        | R/W-1                                                          | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup>                                     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:0         | R/W-1                                                          | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup>                                     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | S-0                                                            | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |

| 7.0          | CFORCE                                                         | CABORT            | PATEN             | SIRQEN            | AIRQEN            | _                 |                  |                  |  |  |

####

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-24 **-** -· ~ '

| bit 31-24 | Unimplemented: Read as '0'                                                       |

|-----------|----------------------------------------------------------------------------------|

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                      |

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag |

|           | •                                                                                |

|           | •                                                                                |

|           | •                                                                                |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag   |

|           | 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag   |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                      |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                            |

|           | •                                                                                |

|           | •                                                                                |

|           | •                                                                                |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer                              |

|           | 0000000 = Interrupt 0 will initiate a DMA transfer                               |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                  |

|           | 1 = A DMA transfer is forced to begin when this bit is written to a '1'          |

|           | 0 = This bit always reads '0'                                                    |

| bit 6     | CABORT: DMA Abort Transfer bit                                                   |

|           | 1 = A DMA transfer is aborted when this bit is written to a '1'                  |

|           | 0 = This bit always reads '0'                                                    |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                    |

|           | 1 = Abort transfer and clear CHEN on pattern match                               |

|           | 2 Dettern weetsk is dischlad                                                     |

- 0 = Pattern match is disabled

- bit 4 SIRQEN: Channel Start IRQ Enable bit

- 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

- 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 5-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| ILCIOID L    | LOISTER 3-10. DCHACGIZ. DMA CHANNEL & CELE-SIZE REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 01.04        | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                                                          | —                 | -                 | -                 | —                 | —                 | -                | —                |  |  |

| 22:16        | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                                                        | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |

| 45.0         | R/W-0                                                    | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHCSIZ<15:8>                                             |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0                                                    | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                                                          |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |  |  |

#### REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

1111111111111111 = 65,535 bytes transferred on an event

#### **REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | -                 | _                 |                   |                  | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7.0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

#### Note: When in Pattern Detect mode, this register is reset on a pattern detect.

### 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The PIC32 USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- · Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | —                 | _                 | —                 | _                 | _                 | _                | -                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   | _                 |                   | _                 | _                 | -                 | -                | -                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         |                   | _                 |                   | _                 | _                 | -                 | -                | -                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |  |  |  |

#### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| 9                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device enabled

- 0 = Direct connection to a low-speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

#### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive enabled

- 0 = Endpoint n receive disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit enabled

- 0 = Endpoint n transmit disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake enabled

- 0 = Endpoint Handshake disabled (typically used for isochronous endpoints)

#### TABLE 11-7: PORTD REGISTER MAP FOR 100-PIN DEVICES ONLY

| ess                         |                                 | 0         |               |               |               |               |               |               |              | Bits         |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | —             | —             | —             | _             | _             | _             | _            | —            | _            | —            | _            | _            | _            | —            | —            | —            | 0000          |

| 0000                        | ANOLLD                          | 15:0      | ANSELD15      | ANSELD14      | ANSELD13      | ANSELD12      | —             | —             | —            | _            | ANSELD7      | ANSELD6      | —            | —            | ANSELD3      | ANSELD2      | ANSELD1      | -            | FOCE          |

| 6310                        | TRISD                           | 31:16     | —             | _             | _             | _             | _             | _             | _            | —            |              | _            | —            | _            | _            | _            |              |              | 0000          |

| 0310                        | INIOD                           | 15:0      | TRISD15       | TRISD14       | TRISD13       | TRISD12       | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | FFFF          |

| 5320                        | PORTD                           | 31:16     | _             | —             | —             | _             | _             | _             | _            | _            | _            | —            | —            | _            | _            | -            | —            | _            | 0000          |

| 5520                        | FORID                           | 15:0      | RD15          | RD14          | RD13          | RD12          | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     | _             | _             | _             |               |               |               |              | _            |              | _            | _            | _            |              |              | _            |              | 0000          |

| 0330                        | LAID                            | 15:0      | LATD15        | LATD14        | LATD13        | LATD12        | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | xxxx          |

| 6340                        | ODCD                            | 31:16     | _             | _             | _             |               |               |               |              | _            |              | _            | _            | _            |              |              | _            |              | 0000          |

| 0340                        | ODCD                            | 15:0      | ODCD15        | ODCD14        | ODCD13        | ODCD12        | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | 0000          |

| 6350                        | CNPUD                           | 31:16     | _             | _             | _             |               |               |               |              | _            |              | _            | _            | _            |              |              | _            |              | 0000          |

| 0000                        |                                 | 15:0      | CNPUD15       | CNPUD14       | CNPUD13       | CNPUD12       | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | 0000          |

| 6360                        | CNPDD                           | 31:16     | _             | —             | —             | _             | _             | _             | _            | _            | _            | —            | —            | _            | _            | -            | —            | _            | 0000          |

| 0300                        |                                 | 15:0      | CNPDD15       | CNPDD14       | CNPDD13       | CNPDD12       | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | 0000          |

| 6370                        | CNCOND                          | 31:16     | _             | —             | —             | _             | _             | _             | _            | _            | _            | —            | —            | _            | _            | -            | —            | _            | 0000          |

| 0370                        | CINCOIND                        | 15:0      | ON            | —             | SIDL          | _             | _             | _             | _            | _            | _            | —            | —            | _            | _            | -            | —            | _            | 0000          |

| 6380                        | CNEND                           | 31:16     | _             | _             | _             |               |               |               |              | _            |              | _            | _            | _            |              |              | _            |              | 0000          |

| 0300                        | CINLIND                         | 15:0      | CNIED15       | CNIED14       | CNIED13       | CNIED12       | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | 0000          |

|                             |                                 | 31:16     | -             | —             | _             | -             |               |               |              | _            |              | —            | —            | —            | _            |              | —            |              | 0000          |

| 6390                        | CNSTATD                         | 15:0      | CNS<br>TATD15 | CN<br>STATD14 | CN<br>STATD13 | CN<br>STATD12 | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | 0000          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | -                 |                   | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 |                   |                   | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | —                 | _                | _                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | _                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

#### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|-------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| 011 31-10 | Unimplemented: Read as 0                                                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Timer On bit <sup>(1)</sup>                                                                                                                                                |

|           | 1 = Timer is enabled                                                                                                                                                           |

|           | 0 = Timer is disabled                                                                                                                                                          |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                    |

|           | 1 = Discontinue operation when device enters Idle mode                                                                                                                         |

|           | 0 = Continue operation even in Idle mode                                                                                                                                       |

| bit 12    | TWDIS: Asynchronous Timer Write Disable bit                                                                                                                                    |

|           | <ul><li>1 = Writes to TMR1 are ignored until pending write operation completes</li><li>0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)</li></ul> |

| bit 11    | TWIP: Asynchronous Timer Write in Progress bit                                                                                                                                 |

|           | In Asynchronous Timer mode:                                                                                                                                                    |

|           | 1 = Asynchronous write to TMR1 register in progress                                                                                                                            |

|           | 0 = Asynchronous write to TMR1 register complete                                                                                                                               |

|           | In Synchronous Timer mode:<br>This bit is read as '0'.                                                                                                                         |

| bit 10-8  | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 7     | TGATE: Timer Gated Time Accumulation Enable bit                                                                                                                                |

|           | When TCS = 1:                                                                                                                                                                  |

|           | This bit is ignored.                                                                                                                                                           |

|           | When TCS = 0:<br>1 = Gated time accumulation is enabled                                                                                                                        |

|           | 0 = Gated time accumulation is enabled                                                                                                                                         |

| bit 6     | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 5-4   | TCKPS<1:0>: Timer Input Clock Prescale Select bits                                                                                                                             |

|           | 11 = 1:256 prescale value                                                                                                                                                      |

|           | 10 = 1:64 prescale value                                                                                                                                                       |

|           | 01 = 1:8 prescale value<br>00 = 1:1 prescale value                                                                                                                             |

| bit 3     | Unimplemented: Read as '0'                                                                                                                                                     |

| DIL J     | ommplemented. Read as 0                                                                                                                                                        |

|           |                                                                                                                                                                                |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

|                             | COSTER 21-4. RTCDATE. RTC DATE VALUE REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |

|-----------------------------|-----------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range                | Bit<br>31/23/15/7                             | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04                       | R/W-x                                         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24                       |                                               | YEAR1             | 0<3:0>            |                   |                   | YEAR0             | 1<3:0>           |                  |  |  |

| 23:16                       | R/W-x                                         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16 MONTH10<3:0>          |                                               |                   |                   |                   | MONTH01<3:0>      |                   |                  |                  |  |  |

| 1= 0                        | R/W-x                                         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8                        |                                               | DAY10             | <3:0>             |                   | DAY01<3:0>        |                   |                  |                  |  |  |

| 7.0                         | U-0                                           | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0                         | _                                             | —                 | _                 | —                 |                   | WDAYO             | 1<3:0>           |                  |  |  |

|                             |                                               |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:                     |                                               |                   |                   |                   |                   |                   |                  |                  |  |  |

| R = Read                    | able bit                                      |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |  |

| -n = Value at POR '1' = Bit |                                               |                   |                   | et                | '0' = Bit is cl   | eared             | x = Bit is un    | known            |  |  |

### REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digits

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1s place digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                 | —                 | —                 | _                 | —                 | —                 | -                | —                |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | -                 | —                 |                   | _                 | _                 | _                 | -                | _                |  |  |  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 10.0         | —                 | —                 | SIDL              | —                 | —                 | —                 | —                | —                |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | _                 | —                 | _                 |                   | _                 | C3OUT             | C2OUT            | C10UT            |  |  |  |

#### REGISTER 24-2: CMSTAT: COMPARATOR STATUS REGISTER

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|-------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

bit 13 **SIDL:** Stop in IDLE Control bit

1 = All Comparator modules are disabled in IDLE mode

0 = All Comparator modules continue to operate in the IDLE mode

#### bit 12-3 Unimplemented: Read as '0'

#### bit 2 C3OUT: Comparator Output bit

- 1 = Output of Comparator 3 is a '1'

- 0 = Output of Comparator 3 is a '0'

#### bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

#### bit 0 **C1OUT:** Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 04.04        | r-0               | r-1               | r-1               | R/P               | r-1               | r-1                   | r-1              | R/P              |

| 31:24        | —                 | —                 | _                 | СР                | —                 | —                     | _                | BWP              |

| 00.40        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P                   | R/P              | R/P              |

| 23:16        | —                 | _                 | _                 | _                 |                   | PWP                   | <9:6>            |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P                   | r-1              | r-1              |

| 15:8         | PWP<5:0>          |                   |                   |                   |                   |                       |                  | —                |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P               | R/P                   | R/P              | R/P              |

| 7:0          |                   | _                 |                   | ICESE             | L<1:0>            | JTAGEN <sup>(1)</sup> | DEBUG<1:0>       |                  |

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | it P = Programmable bit            |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31 Reserved: Write '0'

- bit 30-29 Reserved: Write '1'

- bit 28 **CP:** Code-Protect bit

- Prevents boot and program Flash memory from being read or modified by an external programming device.

- 1 = Protection is disabled

- 0 = Protection is enabled

- bit 27-25 Reserved: Write '1'

- bit 24 **BWP:** Boot Flash Write-Protect bit

- Prevents boot Flash memory from being modified during code execution.

- 1 = Boot Flash is writable

- 0 = Boot Flash is not writable

- bit 23-20 Reserved: Write '1'

- Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

| DC CHARACT                                                         | ERISTICS               |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                 |      |               |  |  |

|--------------------------------------------------------------------|------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|---------------|--|--|

| Parameter<br>No.                                                   | Typical <sup>(2)</sup> | Max. | Units Conditions                                                                                                                                                                                                                                                                      |                 |      |               |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Notes 1, 4) |                        |      |                                                                                                                                                                                                                                                                                       |                 |      |               |  |  |

| DC30a                                                              | 1.5                    | 5    | mA                                                                                                                                                                                                                                                                                    | 4 MHz (Note 3)  |      |               |  |  |

| DC31a                                                              | 3                      | 8    | mA                                                                                                                                                                                                                                                                                    | 10 MHz          |      |               |  |  |

| DC32a                                                              | 5                      | 12   | mA                                                                                                                                                                                                                                                                                    | 20 MHz (Note 3) |      |               |  |  |

| DC33a                                                              | 6.5                    | 15   | mA                                                                                                                                                                                                                                                                                    | 30 MHz (Note 3) |      |               |  |  |

| DC34a                                                              | 8                      | 20   | mA                                                                                                                                                                                                                                                                                    | 40 MHz          |      |               |  |  |

| DC37a                                                              | 75                     | 100  | μA                                                                                                                                                                                                                                                                                    | -40°C           |      | LPRC (31 kHz) |  |  |

| DC37b                                                              | 180                    | 250  | μA                                                                                                                                                                                                                                                                                    | +25°C           | 3.3V | (Note 3)      |  |  |

| DC37c                                                              | 280                    | 380  | μA                                                                                                                                                                                                                                                                                    | +85°C           |      |               |  |  |

#### TABLE 31-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** The test conditions for IIDLE current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1  $\,$

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: IIDLE electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

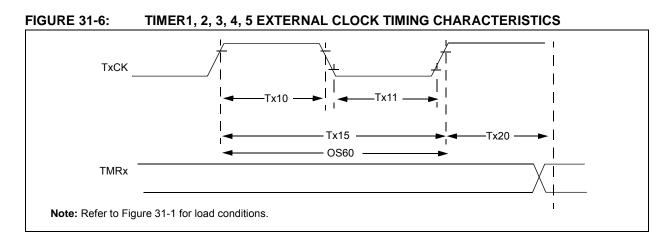

#### TABLE 31-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

|               |           |                                                                                                             |                              |   | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |         |      |       |                               |

|---------------|-----------|-------------------------------------------------------------------------------------------------------------|------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-------------------------------|

| Param.<br>No. | Symbol    | Characteristics <sup>(2)</sup>                                                                              |                              |   | Min.                                                                                                                                                                                                                                                                            | Typical | Max. | Units | Conditions                    |

| TA10          | T⊤xH      | TxCK<br>High Time                                                                                           | Synchronou<br>with presca    |   | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                                                                                               | —       | —    | ns    | Must also meet parameter TA15 |

|               |           |                                                                                                             | Asynchrono<br>with presca    |   | 10                                                                                                                                                                                                                                                                              | —       | _    | ns    | —                             |

| TA11          | T⊤xL      | TxCK<br>Low Time                                                                                            | Synchronous, with prescaler  |   | [(12.5 ns or 1 Трв)/N]<br>+ 25 ns                                                                                                                                                                                                                                               | —       | _    | ns    | Must also meet parameter TA15 |

|               |           |                                                                                                             | Asynchronous, with prescaler |   | 10                                                                                                                                                                                                                                                                              | _       | _    | ns    | —                             |