Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 81                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 48x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

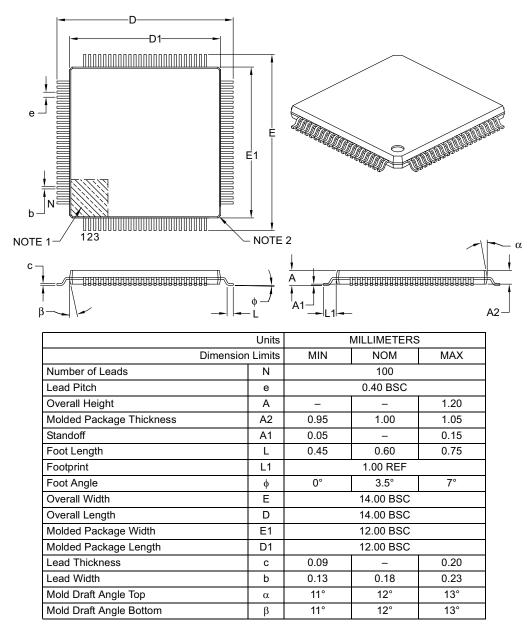

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f128l-v-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Device Pin Tables**

# TABLE 2: PIN NAMES FOR 64-PIN GENERAL PURPOSE DEVICES

| 64·   | PIN QFN <sup>(4)</sup> AND TQFP (TOP VIEW)                                     |                   |                        |

|-------|--------------------------------------------------------------------------------|-------------------|------------------------|

|       | PIC32MX120F064H<br>PIC32MX130F128H<br>PIC32MX150F256H<br>PIC32MX170F512H<br>64 | QFN <sup>(4</sup> | 1<br>64<br><b>TQFP</b> |

| Pin # | Full Pin Name                                                                  | Pin #             | Full Pin Name          |

| 1     | AN22/RPE5/PMD5/RE5                                                             | 33                | RPF3/RF3               |

| 2     | AN23/PMD6/RE6                                                                  | 34                | RPF2/RF2               |

| 3     | AN27/PMD7/RE7                                                                  | 35                | RPF6/SCK1/INT0/RF6     |

| 4     | AN16/C1IND/RPG6/SCK2/PMA5/RG6                                                  | 36                | SDA1/RG3               |

| 5     | AN17/C1INC/RPG7/PMA4/RG7                                                       | 37                | SCL1/RG2               |

| 6     | AN18/C2IND/RPG8/PMA3/RG8                                                       | 38                | VDD                    |

| 7     | MCLR                                                                           | 39                | OSC1/CLKI/RC12         |

| 8     | AN19/C2INC/RPG9/PMA2/RG9                                                       | 40                | OSC2/CLKO/RC15         |

| 9     | Vss                                                                            | 41                | Vss                    |

| 10    | VDD                                                                            | 42                | RPD8/RTCC/RD8          |

| 11    | AN5/C1INA/RPB5/RB5                                                             | 43                | RPD9/RD9               |

| 12    | AN4/C1INB/RB4                                                                  | 44                | RPD10/PMA15/RD10       |

| 13    | PGED3/AN3/C2INA/RPB3/RB3                                                       | 45                | RPD11/PMA14/RD11       |

| 14    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2                                          | 46                | RPD0/RD0               |

| 15    | PGEC1/VREF-/AN1/RPB1/CTED12/RB1                                                | 47                | SOSCI/RPC13/RC13       |

| 16    | PGED1/VREF+/AN0/RPB0/PMA6/RB0                                                  | 48                | SOSCO/RPC14/T1CK/RC14  |

| 17    | PGEC2/AN6/RPB6/RB6                                                             | 49                | AN24/RPD1/RD1          |

| 18    | PGED2/AN7/RPB7/CTED3/RB7                                                       | 50                | AN25/RPD2/RD2          |

| 19    | AVDD                                                                           | 51                | AN26/C3IND/RPD3/RD3    |

| 20    | AVss                                                                           | 52                | RPD4/PMWR/RD4          |

| 21    | AN8/RPB8/CTED10/RB8                                                            | 53                | RPD5/PMRD/RD5          |

| 22    | AN9/RPB9/CTED4/PMA7/RB9                                                        | 54                | C3INC/RD6              |

| 23    | TMS/CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                      | 55                | C3INB/RD7              |

| 24    | TDO/AN11/PMA12/RB11                                                            | 56                | VCAP                   |

| 25    | Vss                                                                            | 57                | Vdd                    |

| 26    | Vdd                                                                            | 58                | C3INA/RPF0/RF0         |

| 27    | TCK/AN12/PMA11/RB12                                                            | 59                | RPF1/RF1               |

| 28    | TDI/AN13/PMA10/RB13                                                            | 60                | PMD0/RE0               |

| 29    | AN14/RPB14/SCK3/CTED5/PMA1/RB14                                                | 61                | PMD1/RE1               |

| 30    | AN15/RPB15/OCFB/CTED6/PMA0/RB15                                                | 62                | AN20/PMD2/RE2          |

| 31    | RPF4/SDA2/PMA9/RF4                                                             | 63                | RPE3/CTPLS/PMD3/RE3    |

| 32    | RPF5/SCL2/PMA8/RF5                                                             | 64                | AN21/PMD4/RE4          |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 11.0 "I/O Ports" for more information.

Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

# 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX/5XX 64/ 100-pin family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of  $0.1 \ \mu F$ (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

# 5.1 Interrupts Control Registers

#### TABLE 5-2: INTERRUPT REGISTER MAP

| sse                         |                                 |               |                 |                |                   |                  |                  |                 |                              |                 | Bits              |                       |                       |                      |                         |                         |                |                 |               |

|-----------------------------|---------------------------------|---------------|-----------------|----------------|-------------------|------------------|------------------|-----------------|------------------------------|-----------------|-------------------|-----------------------|-----------------------|----------------------|-------------------------|-------------------------|----------------|-----------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(3)</sup> | Bit Range     | 31/15           | 30/14          | 29/13             | 28/12            | 27/11            | 26/10           | 25/9                         | 24/8            | 23/7              | 22/6                  | 21/5                  | 20/4                 | 19/3                    | 18/2                    | 17/1           | 16/0            | All<br>Resets |

| 1000                        | INTCON                          | 31:16         | _               |                | _                 | —                | _                |                 | —                            | _               | —                 | —                     | —                     | -                    | -                       | -                       | -              | -               | 0000          |

|                             |                                 | 15:0          |                 |                | —                 | MVEC             | —                |                 | TPC<2:0>                     |                 | _                 | _                     | _                     | INT4EP               | INT3EP                  | INT2EP                  | INT1EP         | INT0EP          | 0000          |

| 1010                        | INTSTAT <sup>(4)</sup>          | 31:16<br>15:0 |                 |                |                   |                  | _                |                 |                              |                 |                   |                       |                       | _                    | <br>VEC<                | 5:0>                    | _              |                 | 0000          |

|                             |                                 | 31:16         |                 |                |                   |                  |                  |                 |                              |                 |                   |                       |                       |                      | VLOV                    | 0.0-                    |                |                 | 0000          |

| 1020                        | IPTMR                           | 15:0          |                 |                |                   |                  | IF               |                 |                              | PTMR<31:0>      | >                 |                       |                       |                      |                         |                         |                | 0000            |               |

| 1030                        | IFS0                            | 31:16         | FCEIF           | RTCCIF         | FSCMIF            | AD1IF            | OC5IF            | IC5IF           | IC5EIF                       | T5IF            | INT4IF            | OC4IF                 | IC4IF                 | IC4EIF               | T4IF                    | INT3IF                  | OC3IF          | IC3IF           | 0000          |

| 1030                        | 150                             | 15:0          | IC3EIF          | T3IF           | INT2IF            | OC2IF            | IC2IF            | IC2EIF          | T2IF                         | INT1IF          | OC1IF             | IC1IF                 | IC1EIF                | T1IF                 | INT0IF                  | CS1IF                   | CS0IF          | CTIF            | 0000          |

| 1040                        | IFS1                            | 31:16         | <b>U3RXIF</b>   | U3EIF          | I2C2MIF           | I2C2SIF          | I2C2BIF          | U2TXIF          | U2RXIF                       | U2EIF           | SPI2TXIF          | SPI2RXIF              | SPI2EIF               | PMPEIF               | PMPIF                   | CNGIF                   | CNFIF          | CNEIF           | 0000          |

| 1010                        |                                 | 15:0          | CNDIF           | CNCIF          | CNBIF             | CNAIF            | I2C1MIF          | I2C1SIF         | I2C1BIF                      | U1TXIF          | U1RXIF            | U1EIF                 | SPI1TXIF              | SPI1RXIF             | SPI1EIF                 | USBIF <sup>(2)</sup>    | CMP2IF         | CMP1IF          | 0000          |

| 1050                        | IFS2                            | 31:16         | —               | —              | —                 |                  | —                | —               | —                            | —               | _                 | (1)                   | (1)                   | —                    | SPI4TXIF <sup>(1)</sup> | SPI4RXIF <sup>(1)</sup> | -              | <b>SPI3TXIF</b> |               |

|                             |                                 | 15:0          | SPI3RXIF        | SPI3EIF        | CANIF             | CMP3IF           | DMA3IF           | DMA2IF          | DMA1IF                       | DMA0IF          | CTMUIF            | U5TXIF <sup>(1)</sup> | U5RXIF <sup>(1)</sup> | U5EIF <sup>(1)</sup> | U4TXIF                  | U4RXIF                  | U4EIF          | U3TXIF          | 0000          |

| 1060                        | IEC0                            | 31:16         | FCEIE<br>IC3EIE | RTCCIE<br>T3IE | FSCMIE<br>INT2IE  | AD1IE            | OC5IE            | IC5IE<br>IC2EIE | IC5EIE<br>T2IE               | T5IE            | INT4IE            | OC4IE                 | IC4IE                 | IC4EIE<br>T1IE       | T4IE<br>INT0IE          | INT3IE                  | OC3IE          | IC3IE<br>CTIE   | 0000          |

|                             |                                 | 15:0<br>31:16 | U3RXIE          | U3EIE          | INTZIE<br>I2C2MIE | OC2IE<br>I2C2SIE | IC2IE<br>I2C2BIE | U2TXIE          | U2RXIE                       | INT1IE<br>U2EIE | OC1IE<br>SPI2TXIE | IC1IE<br>SPI2RXIE     | SPI2EIE               | PMPEIE               | PMPIE                   | CS1IE<br>CNGIE          | CS0IE<br>CNFIE | CITE            | 0000          |

| 1070                        | IEC1                            | 15:0          | CNDIE           | CNCIE          | CNBIE             | CNAIE            | I2C2BIE          | I2C1SIE         | I2C1BIE                      | U1TXIE          | U1RXIE            | U1EIE                 | SPIZEIE               | SPI1RXIE             | SPI1EIE                 | USBIE <sup>(2)</sup>    | CMP2IE         | CMP1IE          | 0000          |

|                             |                                 | 31:16         | _               |                |                   | _                |                  | -               |                              | _               |                   | _                     |                       |                      |                         |                         | _              |                 | 0000          |

| 1080                        | IEC2                            | 15:0          | _               | _              | _                 | _                | DMA3IE           | DMA2IE          | DMA1IE                       | DMA0IE          | CTMUIE            | U5TXIE <sup>(1)</sup> | U5RXIE <sup>(1)</sup> | U5EIE <sup>(1)</sup> | U4TXIE                  | U4RXIE                  | U4EIE          | U3TXIE          | 0000          |

|                             |                                 | 31:16         | _               | _              | _                 | IN               | T0IP<2:0>        |                 | INTOIS                       |                 | _                 | _                     | _                     |                      | CS1IP<2:0>              | ,                       | CS1IS          | 6<1:0>          | 0000          |

| 1090                        | IPC0                            | 15:0          | _               | _              | _                 | CS               | S0IP<2:0>        |                 | CSOIS                        | <1:0>           |                   | _                     | _                     |                      | CTIP<2:0>               |                         | CTIS           | <1:0>           | 0000          |

| 10A0                        | IPC1                            | 31:16         | _               | —              | —                 | IN               | T1IP<2:0>        |                 | INT1IS                       | 6<1:0>          | _                 | _                     | _                     |                      | OC1IP<2:0>              | >                       | OC1IS          | 6<1:0>          | 0000          |

| IUAU                        | IPCT                            | 15:0          | _               | _              | —                 | IC               | 1IP<2:0>         |                 | IC1IS                        | <1:0>           | _                 | _                     | _                     |                      | T1IP<2:0>               |                         | T1IS           | <1:0>           | 0000          |

| 10B0                        | IPC2                            | 31:16         |                 |                | —                 | IN               | T2IP<2:0>        |                 | INT2IS<1:0>                  |                 |                   | -                     | —                     |                      | OC2IP<2:0>              | >                       | OC2IS          | 6<1:0>          | 0000          |

| IUBU                        | 1602                            | 15:0          | _               | _              | —                 | IC               | 2IP<2:0>         |                 | IC2IS<1:0>                   |                 | _                 | —                     | —                     |                      | T2IP<2:0>               |                         | T2IS           | <1:0>           | 0000          |

| 10C0                        | IPC3                            | 31:16         | _               | —              | —                 |                  | T3IP<2:0>        |                 | INT3IS<1:0> — — — OC3IP<2:0> |                 | OC3IS<1:0>        |                       | 0000                  |                      |                         |                         |                |                 |               |

| 1000                        | " 00                            | 15:0          | _               |                | —                 |                  | 3IP<2:0>         |                 | IC3IS<1:0> — — — T3IP<2:0>   |                 | T3IS              | -                     | 0000                  |                      |                         |                         |                |                 |               |

| 10D0                        | IPC4                            | 31:16         | —               | —              | —                 |                  | T4IP<2:0>        |                 |                              |                 | OC4IP<2:0>        |                       |                       | 0000                 |                         |                         |                |                 |               |

| Longer                      |                                 | 15:0          | -               | —              | —                 |                  | 4IP<2:0>         |                 | IC4IS                        |                 |                   | —                     | _                     |                      | T4IP<2:0>               |                         | T4IS           | <1:0>           | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

3: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

4: This register does not have associated CLR, SET, and INV registers.

5: This bit is only implemented on devices with a CAN module.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24 R/W-0  |                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | :24 DCRCDATA<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.10        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | DCRCDATA<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                     |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                     |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |  |  |  |

## REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

# Legend:

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### **REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | DCRCXOR<31:24>                            |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0 R/W-0                               |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | DCRCXOR<23:16>                            |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15:8         |                                           |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                                           |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |  |  |  |  |

| 00.10     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45-0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8      | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |  |  |

# **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

## **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04        | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        |                                           |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | CHDSA<23:16>                              |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15:8         |                                           |                   |                   | CHDSA             | <15:8>            |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                                           |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\text{Note:}}$  This must be the physical address of the destination.

| ess                         |                                 |           |       |       |               |               |       |       |      | Bits         | 5            |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6500                        | ANSELF                          | 31:16     | _     | -     | —             | —             | _     | —     | —    | _            | -            | —            | —            | —            | —            | —            | -            | -            | 0000          |

| 0000                        | ANOLLI                          | 15:0      | —     | _     | ANSELE13      | ANSELE12      | —     | _     | _    | ANSELE8      |              | —            | _            |              |              | ANSELE2      | ANSELE1      | ANSELE0      | 3107          |

| 6510                        | TRISF                           | 31:16     | —     | _     | —             | —             | —     | —     | _    | —            | _            | —            | —            | _            |              |              | _            | _            | 0000          |

| 0010                        | TRIO                            | 15:0      | _     | -     | TRISF13       | TRISF12       | _     | —     | —    | TRISF8       | TRISF7       | TRISF6       | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | 31FF          |

| 6520                        | PORTF                           | 31:16     | _     | -     | —             | —             | _     | —     | —    | —            | -            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 0320                        | 1 OKII                          | 15:0      | _     | -     | RF13          | RF12          | _     | —     | —    | RF8          | RF7          | RF6          | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATE                            | 31:16     | _     | -     | —             | —             | _     | —     | —    | —            | -            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 0000                        | LAII                            | 15:0      | _     | -     | LATF13        | LATF12        | _     | —     | —    | LATF8        | LATF7        | LATF6        | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | _     | -     | —             | —             | _     | —     | —    | —            | -            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 0340                        | ODCI                            | 15:0      | _     |       | ODCF13        | ODCF12        | -     | _     | —    | ODCF8        | ODCF7        | ODCF6        | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | 0000          |

| 6550                        | CNPUF                           | 31:16     | _     |       | _             | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 0330                        | CINFUI                          | 15:0      | _     |       | CNPUF13       | CNPUF12       | -     | _     | —    | CNPUF8       | CNPUF7       | CNPUF6       | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | 0000          |

| 6560                        | CNPDF                           | 31:16     | _     |       | _             | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 0300                        | CINF DI                         | 15:0      | _     |       | CNPDF13       | CNPDF12       | -     | _     | —    | CNPDF8       | CNPDF7       | CNPDF6       | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | 0000          |

| 6570                        | CNCONF                          | 31:16     | _     | _     | —             | —             | —     | _     | _    | —            | _            | —            | _            | _            | —            | _            | -            | -            | 0000          |

| 0370                        | CINCOIN                         | 15:0      | ON    |       | SIDL          | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 6580                        | CNENF                           | 31:16     | _     |       | _             | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 0380                        | CINLINI                         | 15:0      | _     |       | CNIEF13       | CNIEF12       | -     | _     | —    | CNIEF8       | CNIEF7       | CNIEF6       | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | 0000          |

|                             |                                 | 31:16     | _     | _     | —             | —             | —     | _     | —    | _            |              | _            | _            | —            | _            | —            |              |              | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | _     | CN<br>STATF13 | CN<br>STATF12 | _     | _     | _    | CN<br>STATF8 | CN<br>STATF7 | CN<br>STATF6 | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | 0000          |

# TABLE 11-11: PORTF REGISTER MAP FOR PIC32MX130F128L, PIC32MX150F256L, AND PIC32MX170F512L DEVICES ONLY

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

# TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                         |                  |           |       |       |       |       |       |       |      | Bi   | its  |      |      |      |           |      |        |      |            |

|----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|-----------|------|--------|------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3      | 18/2 | 17/1   | 16/0 | All Resets |

| 5004                       | RPG1R            | 31:16     |       | _     |       |       | —     | _     | _    |      | _    |      | —    | _    |           | _    |        | —    | 0000       |

| FC04                       | RPGIR            | 15:0      | —     | —     | _     | _     | _     | —     | —    | —    | —    | _    | _    | —    |           | RPG1 | <3:0>  |      | 0000       |

| 5000                       | DDOOD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | —    | _    | _    | _    | —    | _         | _    | _      | _    | 0000       |

| FC98                       | RPG6R            | 15:0      | —     | —     | _     | _     | —     | —     | —    | —    | _    | —    | —    | —    | RPG6<3:0> |      |        | 0000 |            |

| 5000                       | 00070            | 31:16     | —     | —     | _     | _     | —     | —     | —    | —    | _    | —    | —    | —    | —         | —    | _      | —    | 0000       |

| FC9C                       | RPG7R            | 15:0      | _     | —     | _     | _     | _     | —     | —    | _    | _    | _    | _    | _    |           | RPG7 | /<3:0> |      | 0000       |

| 5040                       | DDOAD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | -    |      | _    | _    | _    | _         | _    | _      | _    | 0000       |

| FCAU                       | RPG8R            | 15:0      | _     | —     | _     | _     | _     | —     | —    |      |      | _    | _    | —    |           | RPG8 | 3<3:0> | •    | 0000       |

| 5044                       | DDOOD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | _    | -    | _    | _    | _    | _         | _    | _      | _    | 0000       |

| FCA4                       | RPG9R            | 15:0      | —     | —     | _     | _     | —     | —     | —    | _    | _    | —    | —    | —    |           | RPG9 | <3:0>  |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | —                 | -                 | _                 | —                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | —                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | e]R<3:0>         |                  |

## REGISTER 11-1: [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-4 Unimplemented: Read as '0'

### bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

#### REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 |                   |                  | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | —                 | —                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | RPnR              | <3:0>            |                  |

# Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

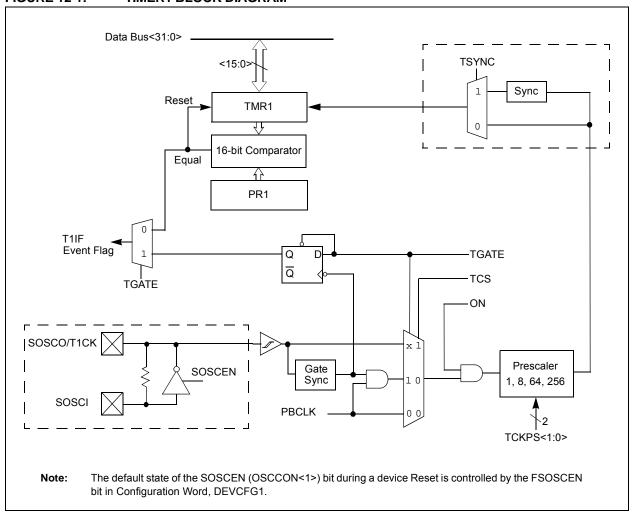

# 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a freerunning interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

# 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

# FIGURE 12-1: TIMER1 BLOCK DIAGRAM

NOTES:

# REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | -                 | -                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | -                 | —                 |                   | _                | —                |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | _                 | _                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

| Legend:           | HS = Set in hardware | HSC = Hardware set/cleared |                   |  |

|-------------------|----------------------|----------------------------|-------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re  | ead as '0'        |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | C = Clearable bit |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 GCSTAT: General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

bit 7 IWCOL: Write Collision Detect bit

1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy 0 = No collision

- Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

- bit 6 **I2COV:** Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        |                   | —                 | _                 | _                 | —                 | —                 | —                | _                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | _                 | _                 | _                 | —                 | -                 | —                | _                |  |  |  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |  |  |  |  |  |

## REGISTER 19-1: UxMODE: UARTx MODE REGISTER

# Legend:

| Legend.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

#### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                       | —                     | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 00.40        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                       | —                     | _                 | _                 | _                 | _                 | —                | —                |  |  |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    | ADDR<13:8>        |                   |                   |                   |                  |                  |  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   |                   | ADDR              | <13.0>            |                  |                  |  |  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                       |                       | ADDR<7:0>         |                   |                   |                   |                  |                  |  |  |

## REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

**Note:** If the DUALBUF bit (PMCON<17>) = 0, the bits in this register control both read and write target addressing. If the DUALBUF bit = 1, the bits in this register are not used. In this instance, use the PMRADDR register for Read operations and the PMWADDR register for Write operations.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

### REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 |                   | —                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | —                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ADRC              | —                 | _                 |                   |                   | SAMC<4:0>(1)      |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W              | R/W-0            |

| 7:0          |                   |                   |                   | ADCS<             | 7:0> <b>(2)</b>   |                   |                  |                  |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB 2 (ADCS<7:0> + 1) = 4 TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- 2: This bit is not used if the ADRC bit (AD1CON3<15>) = 1.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

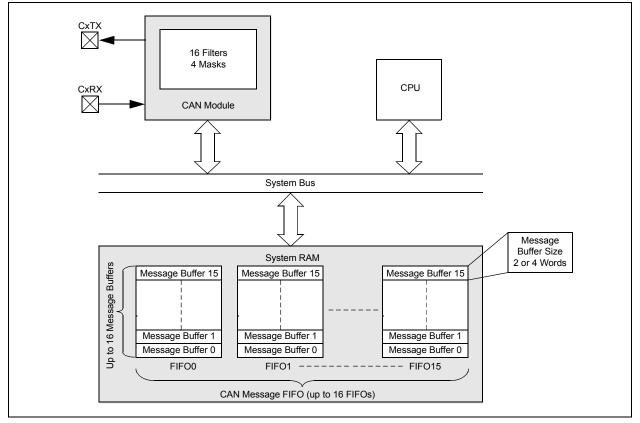

# 23.0 CONTROLLER AREA NETWORK (CAN)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Controller Area Network (CAN)" (DS60001154) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Controller Area Network (CAN) module supports the following key features:

- · Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- Message Reception and Transmission:

- 16 message FIFOs

- Each FIFO can have up to 16 messages for a total of 256 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 16 acceptance filters for message filtering

- Four acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

- DeviceNet<sup>™</sup> addressing support

- Additional Features:

- Loopback, Listen All Messages, and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32 system bus

- Use of DMA is not required

- Dedicated time-stamp timer

- Dedicated DMA channels

- Data-only Message Reception mode

Figure 23-1 illustrates the general structure of the CAN module.

#### FIGURE 23-1: PIC32 CAN MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 51.24        | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15.0         | —                 | —                 | —                 | – FILHIT<4:0>     |                   |                   |                  |                  |  |

| 7:0          | U-0               | R-1               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7.0          | _                 |                   |                   | ICODE<6:0>(1)     |                   |                   |                  |                  |  |

# REGISTER 23-4: C1VEC: CAN INTERRUPT CODE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-13 Unimplemented: Read as '0'

```

bit 12-8 FILHIT<4:0>: Filter Hit Number bit

11111 = Reserved

10000 = Reserved

01111 = Filter 15

00000 = Filter 0

bit 7

Unimplemented: Read as '0'

ICODE<6:0>: Interrupt Flag Code bits<sup>(1)</sup>

bit 6-0

1111111 = Reserved

1001001 = Reserved

1001000 = Invalid message received (IVRIF)

1000111 = CAN module mode change (MODIF)

1000110 = CAN timestamp timer (CTMRIF)

1000101 = Bus bandwidth error (SERRIF)

1000100 = Address error interrupt (SERRIF)

1000011 = Receive FIFO overflow interrupt (RBOVIF)

1000010 = Wake-up interrupt (WAKIF)

1000001 = Error Interrupt (CERRIF)

1000000 = No interrupt

0111111 = Reserved

0010000 = Reserved

0001111 = FIFO15 Interrupt (C1FSTAT<15> set)

0000000 = FIFO0 Interrupt (C1FSTAT<0> set)

```

| DC CHARACTERISTICS |         |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |                    |          |                                                                  |  |

|--------------------|---------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|----------|------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol  | Characteristics                                              | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max.               | Comments |                                                                  |  |

| D312               | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time. | _                                                                                                                                                                                                                                                                                     | _    | 10                 | μs       | See Note 1                                                       |  |

| D313 DACREFH       | DACREFH | CVREF Input Voltage<br>Reference Range                       | AVss                                                                                                                                                                                                                                                                                  | _    | AVDD               | V        | CVRSRC with CVRSS = 0                                            |  |

|                    |         |                                                              | VREF-                                                                                                                                                                                                                                                                                 |      | VREF+              | V        | CVRSRC with CVRSS = 1                                            |  |

| D314               | DVREF   | CVREF Programmable<br>Output Range                           | 0                                                                                                                                                                                                                                                                                     | _    | 0.625 x<br>DACREFH | V        | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                  |  |

|                    |         |                                                              | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                     | —    | 0.719 x<br>DACREFH | V        | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/<br>32 step size |  |

| D315               | DACRES  | Resolution                                                   | —                                                                                                                                                                                                                                                                                     | _    | DACREFH/24         |          | CVRCON <cvrr> = 1</cvrr>                                         |  |

|                    |         |                                                              | _                                                                                                                                                                                                                                                                                     |      | DACREFH/32         |          | CVRCON <cvrr> = 0</cvrr>                                         |  |

| D316 DACACC        |         | Absolute Accuracy <sup>(2)</sup>                             | —                                                                                                                                                                                                                                                                                     | _    | 1/4                | LSB      | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                          |  |