Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f128lt-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX1XX/2XX/5XX 64/100-pin devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX1XX/2XX/5XX 64/100-pin devices, the Flash page size is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

| KE013TE      | .K 3-10. D        | CHACOLL. D        |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 01.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | -                 | -                 | —                 | —                 | -                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHCSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |

#### REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

1111111111111111 = 65,535 bytes transferred on an event

#### **REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | —                 | -                 | _                 |                   |                  | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                   |                   |                   | CHCPTR            | <15:8>            |                   |                  |                  |  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7.0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

#### Note: When in Pattern Detect mode, this register is reset on a pattern detect.

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 6         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |              |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3         | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | _     | —        | _     | —        | _            | —      | —         |          | 0000       |

| 5260                        |                                 | 15:0      |       |       | _     |       | —     | —     | —    | —    |       |          |       | FRML<    | 7:0>         |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | -     | _     | -     | _     | _     | _     | _    | _    | _     | —        | —     | —        | _            | -      | —         |          | 0000       |

| 5290                        |                                 | 15:0      | _     | —     | _     | —     | —     | —     | _    | —    | —     | —        | —     | —        | —            |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     |          | —            |        | -         | —        | 0000       |

| 5270                        | UTION                           | 15:0      | _     | —     |       | —     | —     | —     | —    | —    |       | PID      | <3:0> |          |              | EP     | ><3:0>    |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _     | —        | _     | —        | _            | _      | —         |          | 0000       |

| 52BU                        | 0130F                           | 15:0      |       | _     |       | _     | _     | _     | _    | _    |       |          |       | CNT<7    | <b>'</b> :0> | -      | •         |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     |       | _     |       | _     | _     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     |       | _     |       | _     | _     | _    |      |       |          |       | BDTPTRH  | <23:16>      |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     |       | _     |       | _     | _     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 5200                        | OIBDIF5                         | 15:0      | _     |       | _     |       | _     | _     | _    |      |       |          |       | BDTPTRU  | <31:24>      |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | _     |       | _     |       | _     | _     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 52L0                        | UICNIGI                         | 15:0      | _     |       | _     |       | —     | —     | _    |      | UTEYE | —        | _     | USBSIDL  | LSDEV        | _      | —         | UASUSPND | 0000       |

| 5300                        | U1EP0                           | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 5500                        | UILFU                           | 15:0      | _     |       | _     |       | —     | —     | _    |      | LSPD  | RETRYDIS | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —            | _      | —         |          | 0000       |

| 5510                        | UILFI                           | 15:0      | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | _     |       | _     |       | —     | —     | —    |      | _     | —        | —     | —        | —            | _      | —         |          | 0000       |

| 5520                        | UILFZ                           | 15:0      |       |       |       |       | _     | _     | _    | _    | _     | _        | —     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —     | _     | —     | —     | —     | _    | —    | —     | —        | —     | —        | —            | —      | —         | _        | 0000       |

| 0000                        | 01EI 3                          | 15:0      |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | _     | _     | —     | —     | —    | _    | —     | —        | —     | _        | —            | —      | —         | _        | 0000       |

| 0040                        | 01214                           | 15:0      |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | _     | _     | —     | —     | —    | _    | —     | —        | —     | _        | —            | —      | —         | _        | 0000       |

| 5550                        | 01EI 5                          | 15:0      |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | _     | —     |       | —     | —     | —     | —    | —    | —     | —        | _     | _        | —            | —      | —         | —        | 0000       |

| 5500                        | 01L10                           | 15:0      | -     | _     | -     | —     | _     | —     | —    |      | _     | —        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | _     | —     | _     | —     | —     | —     | —    | —    | —     | -        | _     | —        | —            | —      | -         | —        | 0000       |

| 5570                        |                                 | 15:0      | -     | —     | -     | —     | _     | _     | —    | —    | —     | —        | _     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —     | _     | —     | —     | —     | —    | —    | —     | —        | _     | —        | —            | —      | -         | —        | 0000       |

| 5500                        |                                 | 15:0      | -     | _     | -     | _     | —     | —     | _    | —    | _     | —        | —     | EPCONDIS | EPRXEN       | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

DS60001290D-page 108

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | -                 |                   |                   | _                 |                  | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 |                   |                   | _                 |                  | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | —                 | _                 | -                 | -                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          | —                | VBUSVDIE         |

#### REGISTER 10-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt enabled

- 0 = ID interrupt disabled

- bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt enabled

- 0 = 1 millisecond timer interrupt disabled

- bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt enabled

- 0 = Line state interrupt disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = ACTIVITY interrupt enabled

- 0 = ACTIVITY interrupt disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt enabled

- 0 = Session valid interrupt disabled

- bit 2 SESENDIE: B-Session End Interrupt Enable bit

- 1 = B-session end interrupt enabled

- 0 = B-session end interrupt disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-VBUS Valid Interrupt Enable bit

- 1 = A-VBUS valid interrupt enabled

- 0 = A-VBUS valid interrupt disabled

|              |                   | • • • • • • • • • •     |                         |                   |                      |                   |                       |                         |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | —                 | —                       | _                       |                   | —                    | —                 | —                     | —                       |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | —                 | —                       | _                       |                   | —                    | _                 | _                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.6         | —                 | —                       | _                       |                   | —                    | —                 | —                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | UIALLII           |                         |                         | IULLII            |                      | 00111             |                       | DETACHIF <sup>(6)</sup> |

|              | •                 | •                       |                         |                   |                      |                   |                       |                         |

#### REGISTER 10-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settal | ble bit            |

|-------------------|-------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented b  | vit, read as '0'   |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 |    | STALLIF: STALL Handshake Interrupt bit                                                                                                                                                 |

|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |    | 1 = In Host mode, a STALL handshake was received during the handshake phase of the transaction                                                                                         |

|       |    | In Device mode, a STALL handshake was transmitted during the handshake phase of the transaction                                                                                        |

|       |    | 0 = STALL handshake has not been sent                                                                                                                                                  |

| bit 6 |    | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup>                                                                                                                               |

|       |    | 1 = Peripheral attachment was detected by the USB module                                                                                                                               |

|       |    | 0 = Peripheral attachment was not detected                                                                                                                                             |

| bit 5 |    | RESUMEIF: Resume Interrupt bit <sup>(2)</sup>                                                                                                                                          |

|       |    | 1 = K-State is observed on the D+ or D- pin for 2.5 $\mu$ s                                                                                                                            |

|       |    | 0 = K-State is not observed                                                                                                                                                            |

| bit 4 |    | IDLEIF: Idle Detect Interrupt bit                                                                                                                                                      |

|       |    | 1 = Idle condition detected (constant Idle state of 3 ms or more)                                                                                                                      |

|       |    | 0 = No Idle condition detected                                                                                                                                                         |

| bit 3 |    | <b>TRNIF:</b> Token Processing Complete Interrupt bit <sup>(3)</sup>                                                                                                                   |

|       |    | <ul> <li>1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information</li> <li>0 = Processing of current token not complete</li> </ul> |

| h:+ 0 |    |                                                                                                                                                                                        |

| bit 2 |    | <b>SOFIF:</b> SOF Token Interrupt bit<br>1 = SOF token received by the peripheral or the SOF threshold reached by the host                                                             |

|       |    | 0 = SOF token was not received nor threshold reached                                                                                                                                   |

| bit 1 |    | <b>UERRIF:</b> USB Error Condition Interrupt bit <sup>(4)</sup>                                                                                                                        |

| DICT  |    | 1 = Unmasked error condition has occurred                                                                                                                                              |

|       |    | 0 = Unmasked error condition has not occurred                                                                                                                                          |

| bit 0 |    | URSTIF: USB Reset Interrupt bit (Device mode) <sup>(5)</sup>                                                                                                                           |

| 2.00  |    | 1 = Valid USB Reset has occurred                                                                                                                                                       |

|       |    | 0 = No USB Reset has occurred                                                                                                                                                          |

| bit 0 |    | DETACHIF: USB Detach Interrupt bit (Host mode) <sup>(6)</sup>                                                                                                                          |

|       |    | 1 = Peripheral detachment was detected by the USB module                                                                                                                               |

|       |    | 0 = Peripheral detachment was not detected                                                                                                                                             |

| Note  | 1. | This bit is valid only if the HOSTEN bit is set (see Register 10-11), there is no activity on the USB for                                                                              |

| noto  | •• | $2.5 \mu$ s, and the current bus state is not SE0.                                                                                                                                     |

|       | 2: | When not in Suspend mode, this interrupt should be disabled.                                                                                                                           |

|       | 3: | Clearing this bit will cause the STAT FIFO to advance.                                                                                                                                 |

|       | 4: | Only error conditions enabled through the U1EIE register will set this bit.                                                                                                            |

|       | 5: | Device mode.                                                                                                                                                                           |

|       | 6: | Host mode.                                                                                                                                                                             |

#### TABLE 11-9: PORTE REGISTER MAP FOR 100-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |              | E            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6400                        | ANSELE                          | 31:16     | _     | _     | _     |       | _     | _     | —            | -            |              | _            | —            | _            | —            | —            | —            | _            | 0000          |

| 0400                        | ANOLLL                          | 15:0      | _     | _     | —     | _     | _     | _     | ANSELE9      | ANSELE8      | ANSELE7      | ANSELE6      | ANSELE5      | ANSELE4      | —            | ANSELE2      | ANSELE1      | ANSELE0      | 03F7          |

| 6410                        | TRISE                           | 31:16     | _     | —     | _     | —     | _     | _     | _            | _            | _            | _            |              | _            | —            | _            | —            | —            | 0000          |

| 0410                        | INICE                           | 15:0      | _     | _     | —     | _     | _     | _     | TRISE9       | TRISE8       | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | 03FF          |

| 6420                        | PORTE                           | 31:16     | —     | —     | —     | —     | —     | _     | —            | _            | _            |              |              |              | —            | —            | —            | —            | 0000          |

| 0420                        | TORTE                           | 15:0      | —     | —     | —     | —     | —     | _     | RE9          | RE8          | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 6440                        | LATE                            | 31:16     | —     | —     | —     | —     | —     |       | —            | _            |              |              |              |              |              |              | —            | —            | 0000          |

| 0440                        | L/ (1 L                         | 15:0      | —     | —     | —     | —     | —     |       | LATE9        | LATE8        | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | xxxx          |

| 6440                        | ODCE                            | 31:16     | —     | —     | —     | —     | —     |       | —            | _            |              |              |              |              |              |              | —            | —            | 0000          |

| 0440                        | ODOL                            | 15:0      | —     | —     | —     | —     | —     |       | ODCE9        | ODCE8        | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 6450                        | CNPUE                           | 31:16     | —     | —     | —     | —     | —     |       | —            | _            |              |              |              |              |              |              | —            | —            | 0000          |

| 0100                        |                                 | 15:0      | —     | —     | —     | —     | —     | —     | CNPUE9       | CNPUE8       | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPDE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 6460                        | CNPDE                           | 31:16     | —     | —     | —     | —     | —     | —     | —            | —            | —            | —            |              | —            | —            | —            | —            | —            | 0000          |

| 0100                        | ON DE                           | 15:0      | —     | —     | —     | —     | —     | —     | CNPDE9       | CNPDE8       | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

| 6470                        | CNCONE                          | 31:16     | —     | —     | —     | —     | —     | —     | —            | —            | —            | _            |              | _            | —            | —            | —            | —            | 0000          |

| 0110                        | ONCOME                          | 15:0      | ON    | —     | SIDL  | —     | —     | —     | —            | —            | —            | _            |              | _            | —            | —            | —            | —            | 0000          |

| 6480                        | CNENE                           | 31:16     | —     | —     | —     | —     | —     | —     | —            | —            | —            | —            |              | —            | —            | —            | —            | —            | 0000          |

| 0400                        | ONLINE                          | 15:0      | —     | —     | —     | —     | —     |       | CNIEE9       | CNIEE8       | CNIEE7       | CNIEE6       | CNIEE5       | CNIEE4       | CNIEE3       | CNIEE2       | CNIEE1       | CNIEE0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | —     | —     | _     | —            | —            | _            | _            |              | _            |              |              | —            | —            | 0000          |

| 6490                        | CNSTATE                         | 15:0      | —     | —     | —     | —     | —     | -     | CN<br>STATE9 | CN<br>STATE8 | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 31.24        | _                    | —                 | —                 | —                 | —                        | _                 | -                | _                |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 23.10        | —                    | _                 | —                 | —                 | —                        | —                 | _                | —                |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | SPISGNEXT            | _                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR           |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0            |

| 7:0          | AUDEN <sup>(1)</sup> |                   |                   |                   | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | )<1:0>(1,2)      |

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| ı' |

|----|

| ļ  |

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extened

#### bit 14-13 Unimplemented: Read as '0'

- bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit 1 = Frame Error overflow generates error events 0 = Frame Error does not generate error events bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit 1 = Receive overflow generates error events 0 = Receive overflow does not generate error events bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit 1 = Transmit Underrun Generates Error Events 0 = Transmit Underrun Does Not Generates Error Events bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions) 1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data 0 = A ROV is a critical error which stop SPI operation bit 8 IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions) 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty 0 = A TUR is a critical error which stop SPI operation AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup> bit 7 1 = Audio protocol enabled 0 = Audio protocol disabled bit 6-5 Unimplemented: Read as '0' AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup> bit 3 1 = Audio data is mono (Each data word is transmitted on both left and right channels) 0 = Audio data is stereo bit 2 Unimplemented: Read as '0' AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup> bit 1-0 11 = PCM/DSP mode 10 = Right Justified mode 01 = Left Justified mode  $00 = I^2 S \mod I$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

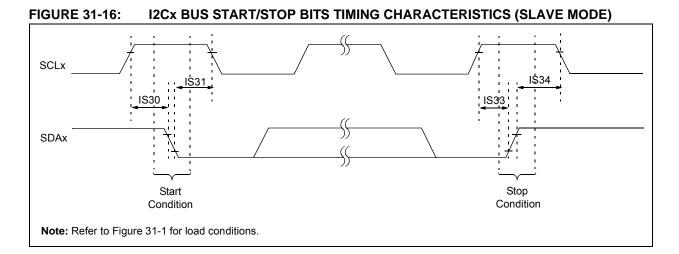

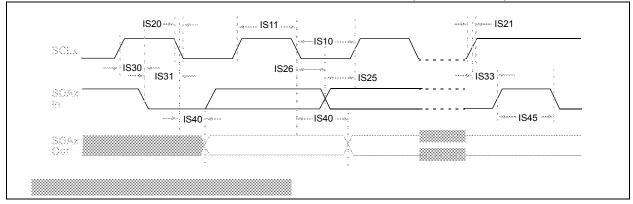

#### 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard. Figure 18-1 illustrates the  $l^2C$  module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

| Bit<br>31/23/15/7      | Bit<br>30/22/14/6                                                                 | Bit<br>29/21/13/5                                                                                                                                                                                                                                             | Bit<br>28/20/12/4                                                                                                                                                                                                                                                                                                                   | Bit<br>27/19/11/3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit<br>26/18/10/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| U-0                    | U-0                                                                               | U-0                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                        | _                                                                                 |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| U-0                    | U-0                                                                               | U-0                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                        | _                                                                                 | _                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| R/W-0                  | R/W-0                                                                             | R/W-0                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RCS2 <sup>(1)</sup>    | RCS1 <sup>(3)</sup>                                                               |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| RADDR15 <sup>(2)</sup> | RADDR14 <sup>(4)</sup>                                                            | RADDR<13:8>                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| R/W-0                  | R/W-0                                                                             | R/W-0                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |