Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

| Core Processor            | MIPS32® M4K™                                                                    |

| Core Size                 | 32-Bit Single-Core                                                              |

| Speed                     | 40MHz                                                                           |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O             | 81                                                                              |

| Program Memory Size       | 128KB (128K x 8)                                                                |

| Program Memory Type       | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| RAM Size                  | 16K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters           | A/D 48x10b                                                                      |

| Oscillator Type           | Internal                                                                        |

| Operating Temperature     | -40°C ~ 85°C (TA)                                                               |

| Mounting Type             | Surface Mount                                                                   |

| ackage / Case             | 100-TQFP                                                                        |

| Supplier Device Package   | 100-TQFP (12x12)                                                                |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx230f128lt-i-pt |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin N                  | umber           |             |                |                                                                                           |

|----------|------------------------|-----------------|-------------|----------------|-------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                               |

| RTCC     | 42                     | 68              | 0           | _              | Real-Time Clock Alarm Output                                                              |

| CVREFOUT | 23                     | 34              | 0           | Analog         | Comparator Voltage Reference (Output)                                                     |

| C1INA    | 11                     | 20              | I           | Analog         |                                                                                           |

| C1INB    | 12                     | 21              | I           | Analog         | Composition 4 Imputs                                                                      |

| C1INC    | 5                      | 11              | I           | Analog         | Comparator 1 Inputs                                                                       |

| C1IND    | 4                      | 10              | I           | Analog         |                                                                                           |

| C2INA    | 13                     | 22              | I           | Analog         |                                                                                           |

| C2INB    | 14                     | 23              | I           | Analog         | Compositor 3 Invite                                                                       |

| C2INC    | 8                      | 14              | I           | Analog         | Comparator 2 Inputs                                                                       |

| C2IND    | 6                      | 12              | I           | Analog         |                                                                                           |

| C3INA    | 58                     | 87              | I           | Analog         |                                                                                           |

| C3INB    | 55                     | 84              | I           | Analog         | Comparator 3 Inputs                                                                       |

| C3INC    | 54                     | 83              | I           | Analog         | Comparator 3 inputs                                                                       |

| C3IND    | 51                     | 78              | I           | Analog         |                                                                                           |

| C1OUT    | PPS                    | PPS             | 0           | _              | Comparator 1 Output                                                                       |

| C2OUT    | PPS                    | PPS             | 0           | _              | Comparator 2 Output                                                                       |

| C3OUT    | PPS                    | PPS             | 0           | _              | Comparator 3 Output                                                                       |

| PMALL    | 30                     | 44              | 0           | TTL/ST         | Parallel Master Port Address Latch Enable Low Byte                                        |

| PMALH    | 29                     | 43              | 0           | TTL/ST         | Parallel Master Port Address Latch Enable High Byte                                       |

| PMA0     | 30                     | 44              | 0           | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |

| PMA1     | 29                     | 43              | 0           | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |

**Legend:** CMOS = CMOS compatible input or output Analog = ST = Schmitt Trigger input with CMOS levels TTL = T

Analog = Analog input I = Input TTL = TTL input buffer P = Power

O = Output

Note 1: This pin is only available on devices without a USB module.

- 2: This pin is only available on devices with a USB module.

- 3: This pin is not available on 64-pin devices with a USB module.

- **4:** This pin is only available on 100-pin devices without a USB module.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

### 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX/5XX 64/ 100-pin family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP™) and debugging purposes (see 2.5 "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

Note:

The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 µF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended that

the capacitors be placed on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within onequarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### REGISTER 5-4: IFSx: INTERRUPT FLAG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS9             | IFS8             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1             | IFS0             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

1 = Interrupt request has occurred

0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 5-1 for the exact bit definitions.

#### REGISTER 5-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 00.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IEC31-IEC0: Interrupt Enable bits

1 = Interrupt is enabled0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 5-1 for the exact bit definitions.

#### REGISTER 9-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | CHSSIZ<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

111111111111111 = 65,535 byte source size

:

•

0000000000000010 = 2 byte source size

00000000000000001 = 1 byte source size

0000000000000000 = 65,536 byte source size

#### REGISTER 9-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | CHDSIZ<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDSIZ<15:0>: Channel Destination Size bits

111111111111111 = 65,535 byte destination size

•

00000000000000001 = 1 byte destination size

0000000000000000 = 65,536 byte destination size

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 PPBRST: Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN BD banks

- 0 = Even/Odd buffer pointers not being Reset

- bit 0 USBEN: USB Module Enable bit(4)

- 1 = USB module and supporting circuitry enabled0 = USB module and supporting circuitry disabled

- **SOFEN:** SOF Enable bit<sup>(5)</sup>

1 = SOF token sent every 1 ms

0 = SOF token disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- **3:** Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

**TABLE 11-2: OUTPUT PIN SELECTION**

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection      |

|----------------------|----------|-------------|--------------------------------------------|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                          |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = <u>U3TX</u>                         |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved            |

| RPD10                | RPD10R   | RPD10R<3:0> | 0111 = Reserved                            |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                            |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                                |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved<br>1000 = Reserved         |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 - Reserved                            |

| RPB5 <sup>(7)</sup>  | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                            |

| RPC1 <sup>(3)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 = OC3                                 |

| RPD14 <sup>(3)</sup> | RPD14R   | RPD14R<3:0> | 1100 = C1TX <sup>(5)</sup><br>1101 = C2OUT |

| RPG1 <sup>(3)</sup>  | RPG1R    | RPG1R<3:0>  | 11101 = C2001<br>1110 = SDO3               |

| RPA14 <sup>(3)</sup> | RPA14R   | RPA14R<3:0> | 1111 = SDO4 <sup>(3)</sup>                 |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                          |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 = U2TX                                |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                            |

| RPD11                | RPD11R   | RPD11R<3:0> | 0011 = U1TX<br>0100 = U5RTS <sup>(3)</sup> |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0100 = 05RTS(*)<br>0101 = Reserved         |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = NCSCIVED                            |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                            |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 = SDO1                                |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                            |

| RPF3 <sup>(4)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved                            |

| RPC4 <sup>(3)</sup>  | RPC4R    | RPC4R<3:0>  | 1011 = OC4<br>1100 = Reserved              |

| RPD15 <sup>(3)</sup> | RPD15R   | RPD15R<3:0> | 1100 = Reserved<br>1101 = C3OUT            |

| RPG0 <sup>(3)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 = SDO3                                |

| RPA15 <sup>(3)</sup> | RPA15R   | RPA15R<3:0> | 1111 = SDO4 <sup>(3)</sup>                 |

Note 1: This selection is not available on 64-pin USB devices.

<sup>2:</sup> This selection is only available on 100-pin General Purpose devices.

<sup>3:</sup> This selection is not available on 64-pin devices.

<sup>4:</sup> This selection is not available when USBID functionality is used on USB devices.

<sup>5:</sup> This selection is not available on devices without a CAN module.

<sup>6:</sup> This selection is not available on USB devices.

<sup>7:</sup> This selection is not available when VBUSON functionality is used on USB devices.

**TABLE 11-5:** PORTC REGISTER MAP FOR 100-PIN DEVICES ONLY

| ess                         |                                 | •         |           | Bits      |           |           |       |       |      |      |      |      |      |          |          |          |          |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|----------|----------|----------|----------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0 | All<br>Resets |

| 6200                        | ANSELC                          | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | ANSLLO                          | 15:0      | _         | _         |           |           | _     | _     | _    | _    | _    | _    | _    | _        | ANSELC3  | ANSELC2  | ANSELC1  | _    | 000E          |

| 6210                        | TRISC                           | 31:16     |           | _         |           |           | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0210                        | TKISC                           | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | _     | _     | _    | _    | _    | _    | _    | TRISC4   | TRISC3   | TRISC2   | TRISC1   | _    | FFFF          |

| 6220                        | PORTC                           | 31:16     | 1         | _         | 1         | 1         | -     | _     | -    |      |      | _    | _    | -        | _        | _        | _        | _    | 0000          |

| 0220                        | FORTO                           | 15:0      | RC15      | RC14      | RC13      | RC12      | -     | _     | -    |      |      | _    | _    | RC4      | RC3      | RC2      | RC1      | _    | xxxx          |

| 6230                        | LATC                            | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0230                        | LAIC                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    |       | _     |      |      |      | _    | _    | LATC4    | LATC3    | LATC2    | LATC1    | _    | xxxx          |

| 6240                        | ODCC                            | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0240                        | 0000                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | _     | _     | _    | _    | _    | _    | _    | ODCC4    | ODCC3    | ODCC2    | ODCC1    | _    | 0000          |

| 6250                        | CNPUC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | 0111 00                         | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | _     | _     | _    | _    | _    | _    | _    | CNPUC4   | CNPUC3   | CNPUC2   | CNPUC1   | _    | 0000          |

| 6260                        | CNPDC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | ON DO                           | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | _     | _     | _    | _    | _    | _    | _    | CNPDC4   | CNPDC3   | CNPDC2   | CNPDC1   | _    | 0000          |

| 6270                        | CNCONC                          | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 02.0                        | 01100110                        | 15:0      | ON        | _         | SIDL      | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 6280                        | CNENC                           | 31:16     | _         | _         |           | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | ONLINO                          | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | _     | _     | _    | _    | _    | _    | _    | CNIEC4   | CNIEC3   | CNIEC2   | CNIEC1   | _    | 0000          |

| 6290                        | CNSTATC                         | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0200                        | 51,517,10                       | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     | _     | _    | _    |      | _    | _    | CNSTATC4 | CNSTATC3 | CNSTATC2 | CNSTATC1 | _    | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

PORTC REGISTER MAP FOR 64-PIN DEVICES ONLY **TABLE 11-6:**

| ess                         |                                 | •         |           |           |           |           |       |       |      | Bits |      |      |      |      |         |         |         |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|------|---------|---------|---------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3    | 18/2    | 17/1    | 16/0 | All<br>Resets |

| 6200                        | ANSELC                          | 31:16     | _         |           |           | _         |       | _     |      | _    | _    | _    | _    |      | _       | _       | _       | _    | 0000          |

| 0200                        | ANSLLO                          | 15:0      | _         |           |           | _         |       | _     |      | _    | _    | _    | _    | _    | ANSELC3 | ANSELC2 | ANSELC1 | _    | 000E          |

| 6210                        | TRISC                           | 31:16     | _         |           |           | _         |       | _     |      | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0210                        | TRISC                           | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | -     | _     | -    | _    | _    | _    | _    | -    | _       | _       | _       | _    | F000          |

| 6220                        | PORTC                           | 31:16     | _         | _         | _         | _         |       |       |      |      | _    |      | _    | _    | _       | _       | _       |      | 0000          |

| 0220                        | 10110                           | 15:0      | RC15      | RC14      | RC13      | RC12      | -     | _     | -    | _    | _    | _    | _    | -    | _       | _       | _       | _    | xxxx          |

| 6230                        | LATC                            | 31:16     | _         | _         | _         | _         | _     |       |      |      | _    |      | _    |      | _       | _       | _       |      | 0000          |

| 0200                        | Dilo                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       |      | xxxx          |

| 6240                        | ODCC                            | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       |      | 0000          |

| 0240                        | 0000                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       |      | 0000          |

| 6250                        | CNPUC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0200                        | 0141 00                         | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 6260                        | CNPDC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0200                        | ON BO                           | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 6270                        | CNCONC                          | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0270                        | 01100110                        | 15:0      | ON        | _         | SIDL      | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 6280                        | CNENC                           | 31:16     | _         | _         |           | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       |      | 0000          |

| 0200                        | CHENO                           | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 6290                        | CNSTATC                         | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0200                        | 5.1017110                       | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

## REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)('x' = 1 THROUGH 5)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 24.** "InterIntegrated Circuit (I<sup>2</sup>C)" (DS60001116) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The  $\rm I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $\rm I^2C$  serial communication standard. Figure 18-1 illustrates the  $\rm I^2C$  module block diagram.

Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

### REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

- bit 4 **P:** Stop bit

- 1 = Indicates that a Stop bit has been detected last

- 0 = Stop bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

- bit 3 S: Start bit

- 1 = Indicates that a Start (or Repeated Start) bit has been detected last

- 0 = Start bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

- bit 2  $R_W$ : Read/Write Information bit (when operating as  $I^2C$  slave)

- 1 = Read indicates data transfer is output from slave

- 0 = Write indicates data transfer is input to slave

Hardware set or clear after reception of I<sup>2</sup>C device address byte.

- bit 1 RBF: Receive Buffer Full Status bit

- 1 = Receive complete, I2CxRCV is full

- 0 = Receive not complete, I2CxRCV is empty

Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.

- bit 0 TBF: Transmit Buffer Full Status bit

- 1 = Transmit in progress, I2CxTRN is full

- 0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

#### REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED) bit 8 PTRDEN: Read/Write Strobe Port Enable bit 1 = PMRD/PMWR port enabled 0 = PMRD/PMWR port disabled CSF<1:0>: Chip Select Function bits(2) bit 7-6 11 = Reserved 10 = PMCS1 and PMCS2 function as Chip Select 01 = PMCS1 functions as address bit 14; PMCS2 functions as Chip Select 00 = PMCS1 and PMCS2 function as address bits 14 and 15, respectively **ALP:** Address Latch Polarity bit<sup>(2)</sup> bit 5 1 = Active-high (PMALL and PMALH) $0 = Active-low (\overline{PMALL} \text{ and } \overline{PMALH})$ CS2P: Chip Select 0 Polarity bit(2) bit 4 1 = Active-high (PMCS2) 0 = Active-low (PMCS2) CS1P: Chip Select 0 Polarity bit<sup>(2)</sup> bit 3 1 = Active-high (PMCS1) $0 = Active-low (\overline{PMCS1})$ bit 2 Unimplemented: Read as '0' bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10): 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

- For Master mode 1 (MODE<1:0> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- 0 = Read Strobe active-low (PMRD)

For Master mode 1 (MODE<1:0> = 11):

- 1 = Read/write strobe active-high (PMRD/PMWR)

- 0 = Read/write strobe active-low (PMRD/PMWR)

- Note 1: When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

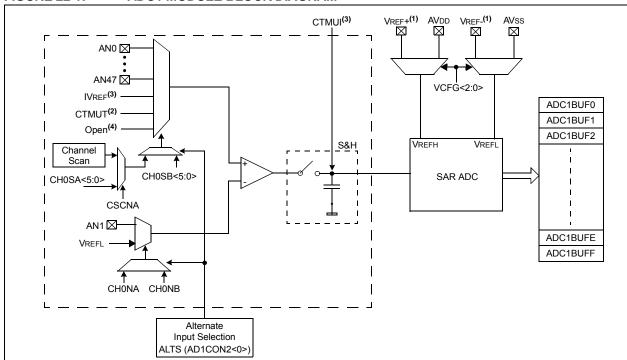

## 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 17.** "10-bit **Analog-to-Digital Converter (ADC)**" (DS60001104) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

- Up to 48 analog input pins

- · External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- · Eight conversion result format options

- · Operation during CPU Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. The 10-bit ADC has up to 28 analog input pins, designated AN0-AN27. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

#### FIGURE 22-1: ADC1 MODULE BLOCK DIAGRAM

- Note 1: VREF+ and VREF- inputs can be multiplexed with other analog inputs.

- 2: Connected to the CTMU temperature reference diode. See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: Internal precision 1.2V reference. See Section 24.0 "Comparator" for more information.

- 4: This selection is only used with CTMU capacitive and time measurement.

#### REGISTER 23-11: C1FLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED)

```

bit 20-16 FSEL6<4:0>: FIFO Selection bits

11111 = Reserved

10000 = Reserved

01111 = Message matching filter is stored in FIFO buffer 15

00000 = Message matching filter is stored in FIFO buffer 0

FLTEN5: Filter 17 Enable bit

bit 15

1 = Filter is enabled

0 = Filter is disabled

bit 14-13 MSEL5<1:0>: Filter 5 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 12-8 FSEL5<4:0>: FIFO Selection bits

11111 = Reserved

10000 = Reserved

01111 = Message matching filter is stored in FIFO buffer 15

00000 = Message matching filter is stored in FIFO buffer 0

bit 7

FLTEN4: Filter 4 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 6-5

MSEL4<1:0>: Filter 4 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

FSEL4<4:0>: FIFO Selection bits

bit 4-0

11111 = Reserved

10000 = Reserved

01111 = Message matching filter is stored in FIFO buffer 15

00000 = Message matching filter is stored in FIFO buffer 0

```

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 23-15: C1FIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|

| 31:24        | R/W-0              | R/W-0              |  |  |  |

| 31.24        | C1FIFOBA<31:24>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 23:16        | R/W-0              | R/W-0              |  |  |  |

| 23.10        | C1FIFOBA<23:16>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 15:8         | R/W-0              | R/W-0              |  |  |  |

| 15.6         | C1FIFOBA<15:8>    |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |

| 7.0          | C1FIFOBA<7:0>     |                   |                   |                   |                   |                   |                    |                    |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 C1FIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Bits <1:0> are read-only and read as '0', forcing the messages to be 32-bit word-aligned in device RAM.

Note 1: This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

| PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY |  |  |  |  |  |  |  |  |  |  |

|--------------------------------------|--|--|--|--|--|--|--|--|--|--|

| NOTES:                               |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

|                                      |  |  |  |  |  |  |  |  |  |  |

**TABLE 31-17: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHA        | RACTER        | ISTICS                                                                                                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Indust $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-ter |                        |             |            |                                         |  |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|-----------------------------------------|--|--|

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                      | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                              |  |  |

| OS10 Fosc     |               | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                                                                   | _                      | 40<br>40    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)           |  |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                                                                         | _                      | 10          | MHz        | XT (Note 4)                             |  |  |

| OS12          |               |                                                                                                                  | 4                                                                                                                                                                                                                                         | _                      | 10          | MHz        | XTPLL<br>(Notes 3,4)                    |  |  |

| OS13          |               |                                                                                                                  | 10                                                                                                                                                                                                                                        | _                      | 25          | MHz        | HS (Note 5)                             |  |  |

| OS14          |               |                                                                                                                  | 10                                                                                                                                                                                                                                        | _                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                    |  |  |

| OS15          |               |                                                                                                                  | 32                                                                                                                                                                                                                                        | 32.768                 | 100         | kHz        | Sosc (Note 4)                           |  |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                                                                                                                                                                                                         | _                      | _           | _          | See parameter<br>OS10 for Fosc<br>value |  |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                                                                               | _                      | _           | ns         | EC (Note 4)                             |  |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | _                                                                                                                                                                                                                                         | _                      | 0.05 x Tosc | ns         | EC (Note 4)                             |  |  |

| OS40          | Tost          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                                                                         | 1024                   | _           | Tosc       | (Note 4)                                |  |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | _                                                                                                                                                                                                                                         | 2                      | _           | ms         | (Note 4)                                |  |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | _                                                                                                                                                                                                                                         | 12                     | _           | mA/V       | VDD = 3.3V,<br>TA = +25°C<br>(Note 4)   |  |  |

- Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

- 2: Instruction cycle period (TcY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- 3: PLL input requirements:  $4 \text{ MHz} \le \text{FPLLIN} \le 5 \text{ MHz}$  (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

- 4: This parameter is characterized, but not tested in manufacturing.

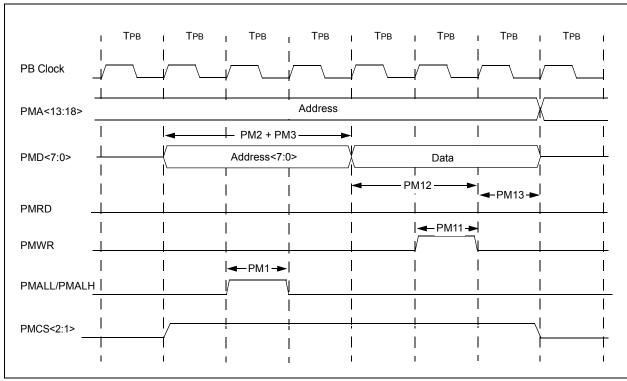

TABLE 31-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +105^{\circ}\text{C}$ for V-temp |       |      |       |            |  |

|--------------------|---------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                               | Тур.  | Max. | Units | Conditions |  |

| PM1                | TLAT    | PMALL/PMALH Pulse Width                                              | _                                                                                                                                                                                                                                                  | 1 Трв |      | _     | _          |  |

| PM2                | TADSU   | Address Out Valid to PMALL/<br>PMALH Invalid (address setup<br>time) | _                                                                                                                                                                                                                                                  | 2 Трв | _    | _     | _          |  |

| РМ3                | TADHOLD | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | _                                                                                                                                                                                                                                                  | 1 Трв | _    | _     | _          |  |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                  | _     | _    | ns    | _          |  |

| PM5                | TRD     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                  | 1 Трв |      | _     | _          |  |

| PM6                | TDSU    | PMRD or PMENB Active to Data In Valid (data setup time)              | 15                                                                                                                                                                                                                                                 | _     | _    | ns    | _          |  |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | _                                                                                                                                                                                                                                                  | 80    | _    | ns    | _          |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

FIGURE 31-22: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

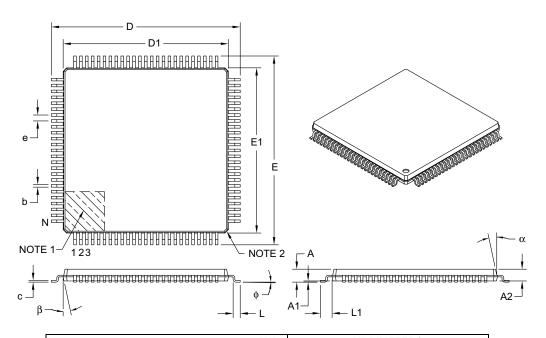

### 100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |           |      |  |  |

|--------------------------|-------------|-----------|-----------|------|--|--|

| Dimension                | Limits      | MIN       | NOM       | MAX  |  |  |

| Number of Leads          | N           | 100       |           |      |  |  |

| Lead Pitch               | е           | 0.50 BSC  |           |      |  |  |

| Overall Height           | Α           | _         | _         | 1.20 |  |  |

| Molded Package Thickness | A2          | 0.95      | 1.00      | 1.05 |  |  |

| Standoff                 | A1          | 0.05      | _         | 0.15 |  |  |

| Foot Length              | L           | 0.45      | 0.60      | 0.75 |  |  |

| Footprint                | L1          | 1.00 REF  |           |      |  |  |

| Foot Angle               | ф           | 0°        | 3.5°      | 7°   |  |  |

| Overall Width            | Е           |           | 16.00 BSC |      |  |  |

| Overall Length           | D           | 16.00 BSC |           |      |  |  |

| Molded Package Width     | E1          | 14.00 BSC |           |      |  |  |

| Molded Package Length    | D1          | 14.00 BSC |           |      |  |  |

| Lead Thickness           | С           | 0.09      | _         | 0.20 |  |  |

| Lead Width               | b           | 0.17      | 0.22      | 0.27 |  |  |

| Mold Draft Angle Top     | α           | 11°       | 12°       | 13°  |  |  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°       | 13°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

### **Revision D (April 2016)**

This revision includes the following major changes, which are referenced by their respective chapter in Table A-2.

**TABLE A-3: MAJOR SECTION UPDATES**

| Section Name                             | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1.0 "Device Overview"                    | Removed the USBOEN pin and all trace-related pins from the Pinout I/O Descriptions (see Table 1-1).                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 2.0 "Guidelines for Getting Started      | Section 2.7 "Trace" was removed.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| with 32-bit MCUs"                        | Section 2.10 "Sosc Design Recommendation" was removed.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 3.0 "CPU"                                | References to the Shadow Register Set (SRS), which is not supported by PIC32MX1XX/2XX/5XX 64/100-pin Family devices, were removed from <b>3.1</b> "Features", <b>3.2.1</b> "Execution Unit", and Coprocessor 0 Registers (Table 3-2).                                                                                                                                                                                                                  |  |  |  |  |

| 4.0 "Memory Organization"                | The SFR Memory Map was added (see Table 4-1).                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 5.0 "Interrupt Controller"               | The Single Vector Shadow Register Set (SSO) bit (INTCON<16>) was removed (see Register 5-1).                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 10.0 "USB On-The-Go (OTG)"               | The UOEMON bit (U1CNFG1<6>) was removed (see Register 10-20).                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 23.0 "Controller Area Network (CAN)"     | The CAN features (number of messages and FIFOs) were updated. The PIC32 CAN Block Diagram was updated (see Figure 23-1). The following registers were updated: • C1FSTAT (see Register 23-6) • C1RXOVF (see Register 23-7) • C1RXFn (see Register 23-14) • C1FIFOCONn (see Register 23-16) • C1FIFOINTn (see Register 23-17) • C1FIFOUAn (see Register 23-18) • C1FIFOCIn (see Register 23-19) The C1FLTCON4 through C1FLTCON7 registers were removed. |  |  |  |  |

| 28.0 "Special Features"                  | The virtual addresses for the Device Configuration Word registers were updated (see Table 28-1).                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 31.0 "40 MHz Electrical Characteristics" | The EJTAG Timing Characteristics diagram was updated (see Figure 31-23).                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |