Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 256КВ (256К х 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f256h-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Interment Course (1)                       | 100 # | Vector |               | Interru      | pt Bit Location |              | Persistent |

|--------------------------------------------|-------|--------|---------------|--------------|-----------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>            | IRQ # | #      | Flag          | Enable       | Priority        | Sub-priority | Interrupt  |

| CNA – PORTA Input Change Interrupt         | 44    | 33     | IFS1<12>      | IEC1<12>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNB – PORTB Input Change Interrupt         | 45    | 33     | IFS1<13>      | IEC1<13>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNC – PORTC Input Change Interrupt         | 46    | 33     | IFS1<14>      | IEC1<14>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CND – PORTD Input Change Interrupt         | 47    | 33     | IFS1<15>      | IEC1<15>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNE – PORTE Input Change Interrupt         | 48    | 33     | IFS1<16>      | IEC1<16>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNF – PORTF Input Change Interrupt         | 49    | 33     | IFS1<17>      | IEC1<17>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNG – PORTG Input Change Interrupt         | 50    | 33     | IFS1<18>      | IEC1<18>     | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| PMP – Parallel Master Port                 | 51    | 34     | IFS1<19>      | IEC1<19>     | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| PMPE – Parallel Master Port Error          | 52    | 34     | IFS1<20>      | IEC1<20>     | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| SPI2E – SPI2 Fault                         | 53    | 35     | IFS1<21>      | IEC1<21>     | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2RX – SPI2 Receive Done                 | 54    | 35     | IFS1<22>      | IEC1<22>     | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2TX – SPI2 Transfer Done                | 55    | 35     | IFS1<23>      | IEC1<23>     | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| U2E – UART2 Error                          | 56    | 36     | IFS1<24>      | IEC1<24>     | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2RX – UART2 Receiver                      | 57    | 36     | IFS1<25>      | IEC1<25>     | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2TX – UART2 Transmitter                   | 58    | 36     | IFS1<26>      | IEC1<26>     | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| I2C2B – I2C2 Bus Collision Event           | 59    | 37     | IFS1<27>      | IEC1<27>     | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2S – I2C2 Slave Event                   | 60    | 37     | IFS1<28>      | IEC1<28>     | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2M – I2C2 Master Event                  | 61    | 37     | IFS1<29>      | IEC1<29>     | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U3E – UART3 Error                          | 62    | 38     | IFS1<30>      | IEC1<30>     | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| U3RX – UART3 Receiver                      | 63    | 38     | IFS1<31>      | IEC1<31>     | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| U3TX – UART3 Transmitter                   | 64    | 38     | IFS2<0>       | IEC2<0>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| U4E – UART4 Error                          | 65    | 39     | IFS2<1>       | IEC2<1>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| U4RX – UART4 Receiver                      | 66    | 39     | IFS2<2>       | IEC2<2>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| U4TX – UART4 Transmitter                   | 67    | 39     | IFS2<3>       | IEC2<3>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| U5E – UART5 Error <sup>(2)</sup>           | 68    | 40     | IFS2<4>       | IEC2<4>      | IPC10<4:2>      | IPC10<1:0>   | Yes        |

| U5RX – UART5 Receiver <sup>(2)</sup>       | 69    | 40     | IFS2<5>       | IEC2<5>      | IPC10<4:2>      | IPC10<1:0>   | Yes        |

| U5TX – UART5 Transmitter <sup>(2)</sup>    | 70    | 40     | IFS2<6>       | IEC2<6>      | IPC10<4:2>      | IPC10<1:0>   | Yes        |

| CTMU – CTMU Event <sup>(2)</sup>           | 71    | 41     | IFS2<7>       | IEC2<7>      | IPC10<12:10>    | IPC10<9:8>   | Yes        |

| DMA0 – DMA Channel 0                       | 72    | 42     | IFS2<8>       | IEC2<8>      | IPC10<20:18>    | IPC10<17:16> | No         |

| DMA1 – DMA Channel 1                       | 73    | 43     | IFS2<9>       | IEC2<9>      | IPC10<28:26>    | IPC10<25:24> | No         |

| DMA2 – DMA Channel 2                       | 74    | 44     | IFS2<10>      | IEC2<10>     | IPC11<4:2>      | IPC11<1:0>   | No         |

| DMA3 – DMA Channel 3                       | 75    | 45     | IFS2<11>      | IEC2<11>     | IPC11<12:10>    | IPC11<9:8>   | No         |

| CMP3 – Comparator 3 Interrupt              | 76    | 46     | IFS2<12>      | IEC2<12>     | IPC11<20:18>    | IPC11<17:16> | No         |

| CAN1 – CAN1 Event                          | 77    | 47     | IFS2<13>      | IEC2<13>     | IPC11<28:26>    | IPC11<25:24> | Yes        |

| SPI3E – SPI3 Fault                         | 78    | 48     | IFS2<14>      | IEC2<14>     | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| SPI3RX – SPI3 Receive Done                 | 79    | 48     | IFS2<15>      | IEC2<15>     | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| SPI3TX – SPI3 Transfer Done                | 80    | 48     | IFS2<16>      | IEC2<16>     | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| SPI4E – SPI4 Fault <sup>(2)</sup>          | 81    | 49     | IFS2<17>      | IEC2<17>     | IPC12<12:10>    | IPC12<9:8>   | Yes        |

| SPI4RX – SPI4 Receive Done <sup>(2)</sup>  | 82    | 49     | IFS2<18>      | IEC2<18>     | IPC12<12:10>    | IPC12<9:8>   | Yes        |

| SPI4TX – SPI4 Transfer Done <sup>(2)</sup> | 83    | 49     | IFS2<19>      | IEC2<19>     | IPC12<12:10>    | IPC12<9:8>   | Yes        |

|                                            | •     | Lowe   | st Natural Or | der Priority |                 |              |            |

## TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0 |

|--------------|-----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|------------------|

| 24.04        | U-0                         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0              |

| 31:24        | —                           | —                 | —                 | _                 | _                 | —                 |                          | _                |

| 00.40        | U-0                         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0              |

| 23:16        | —                           | —                 | —                 | —                 | —                 | —                 |                          | —                |

| 45.0         | U-0                         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0            |

| 15:8         | _                           | —                 |                   | _                 | _                 | S                 | RIPL<2:0> <sup>(1)</sup> |                  |

| 7.0          | U-0                         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0            |

| 7:0          | — — VEC<5:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                          |                  |

#### REGISTER 5-2: INTSTAT: INTERRUPT STATUS REGISTER

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-11 Unimplemented: Read as '0'

- bit 10-8 **SRIPL<2:0>:** Requested Priority Level bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 **Unimplemented:** Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | IPTMR<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        |                   |                   |                   | IPTMF             | ?<23:16>          |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | IPTM              | R<15:8>           |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | IPTMR<7:0>        |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 5-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

## 6.1 Control Registers

## TABLE 6-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | a         |       |                                                                                                                                  |       |       |       |       |      | Bi        | ts        |      |      |      |      |      |      |      | 6          |

|-----------------------------|------------------------|-----------|-------|----------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|------|-----------|-----------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14                                                                                                                            | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8      | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     | _     | —                                                                                                                                | —     | —     | _     |       | —    |           | —         | —    | —    | —    |      |      | —    | —    | 0000       |

| 1400                        |                        | 15:0      | WR    | WR         WRER         LVDERR         LVDSTAT         -         -         -         -         -         NVMOP<3:0>         0000 |       |       |       |       |      |           |           |      |      |      |      |      |      |      |            |

| F410                        | NVMKEY                 | 31:16     |       |                                                                                                                                  |       |       |       |       |      | NVMKE     | /<31.0>   |      |      |      |      |      |      |      | 0000       |

|                             |                        | 15:0      |       |                                                                                                                                  |       |       |       |       |      |           | 1501.02   |      |      |      |      |      |      |      | 0000       |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                                                                                                                                  |       |       |       |       |      | NVMADE    | P<31.05   |      |      |      |      |      |      |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |       |                                                                                                                                  |       |       |       |       |      | INVIVIADE | K~51.02   |      |      |      |      |      |      |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       |                                                                                                                                  |       |       |       |       |      |           | A-31.0>   |      |      |      |      |      |      |      | 0000       |

| 1430                        | NVINDAIA               | 15:0      |       | NVMDATA<31:0>                                                                                                                    |       |       |       |       |      |           |           |      | 0000 |      |      |      |      |      |            |

| F440                        | NVMSRC                 | 31:16     |       | NVMSRCADDR<31:0>                                                                                                                 |       |       |       |       |      |           |           |      | 0000 |      |      |      |      |      |            |

| F440                        | ADDR                   | 15:0      |       |                                                                                                                                  |       |       |       |       | I    | VIVISRUAI | JUR-31.02 | •    |      |      |      |      |      |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

|              |                   |                   |                   | -                 | -                 |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   | DCRCDATA<31:24>   |                   |                   |                   |                   |                  |                  |  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        |                   |                   |                   | DCRCDAT           | 4<23:16>          |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | DCRCDATA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

# Legend:

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### **REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | DCRCXOR<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                                                     |                    |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

## 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The PIC32 USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- · Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 | _                 | —                 |                   | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | —                 | —                 | —                 |                   | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | —                 | —                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

## REGISTER 10-4: U1OTGCON: USB OTG CONTROL REGISTER

## Legend:

bit

| Logona            |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| 7 | DPI | PUL | UP: | D+ I | Pull-Up | Enable | e bit |  |

|---|-----|-----|-----|------|---------|--------|-------|--|

|   |     | -   |     |      |         |        |       |  |

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

# bit 6 **DMPULUP:** D- Pull-Up Enable bit

- to **DMPOLOP:** D- Pull-Op Enable bit

- 1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

#### bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

1 = D+ data line pull-down resistor is enabled

0 = D+ data line pull-down resistor is disabled

## bit 4 **DMPULDWN:** D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

- bit 3 **VBUSON:** VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 **OTGEN:** OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

#### bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

- bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

## TABLE 11-8: PORTD REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |               |               |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | _     | _     | —     | _     |               | —             | —            |              | _            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0000                        | THOLLD                          | 15:0      | —     | —     | —     | —     |               |               | —            | _            | _            | —            | _            |              | ANSELD3      | ANSELD2      | ANSELD1      | —            | 000E          |

| 6310                        | TRISD                           | 31:16     | —     | —     | —     | —     | —             |               | —            | —            | _            |              | _            | _            |              | —            |              |              | 0000          |

| 0310                        | TRIOD                           | 15:0      | —     | —     | —     | _     | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | OFFF          |

| 5320                        | PORTD                           | 31:16     | —     | _     | _     | _     | _             | _             | —            | _            | _            | _            | _            |              | _            | —            |              |              | 0000          |

| 3320                        | TORID                           | 15:0      | —     | —     | —     | _     | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     | —     | —     | —     | _     | —             | —             | _            | _            | _            | —            | _            | -            | —            | —            | _            | _            | 0000          |

| 0330                        | LAID                            | 15:0      | -     | _     | _     | _     | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | xxxx          |

| 6340                        | ODCD                            | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0340                        | ODCD                            | 15:0      | Ι     |       |       |       | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | 0000          |

| 6350                        | CNPUD                           | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0330                        | CINFUD                          | 15:0      | -     | _     | _     | _     | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | 0000          |

| 6360                        | CNPDD                           | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0300                        | CNFDD                           | 15:0      |       | _     | -     |       | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | 0000          |

| 6270                        | CNCOND                          | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0370                        | CINCOIND                        | 15:0      | ON    | _     | SIDL  |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 6380                        | CNEND                           | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0300                        | CNEND                           | 15:0      | Ι     | -     | -     | Ι     | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | _     | _             | _             | _            | —            | _            | _            | _            | _            | _            | _            |              | _            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | _     | _     | _     | -     | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

## TABLE 11-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SS                          |                  |               |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16         |       | —     | —     | -     | -     | —     | -    | -    | -    | —    | -    | -    | —    | —     | -      | _    | 0000       |

| 1 A04                       |                  | 15:0          | _     | —     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16         | _     | _     |       |       | _     | _     | _    | —    | _    | _    | _    | _    | —    | _     | —      | _    | 0000       |

| 17.00                       | 1111211          | 15:0          |       |       |       |       |       |       | —    |      | _    | _    |      |      |      | INT2F | <3:0>  |      | 0000       |

| FA0C                        | INT3R            | 31:16         | _     | —     | _     |       | _     |       | _    | _    | _    | —    | _    | _    |      |       | _      |      | 0000       |

|                             |                  | 15:0          | —     | —     | —     | —     | _     | —     | —    | —    | —    | —    | —    | _    |      | INT3F | <3:0>  |      | 0000       |

| FA10                        | INT4R            | 31:16         | —     | —     | _     | —     | _     | —     | —    | —    | —    | _    | —    | _    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0          |       |       | _     | _     | _     |       | _    | _    | _    | _    | _    | _    |      | INT4F | <3:0>  |      | 0000       |

| FA18                        | T2CKR            | 31:16         | _     |       |       |       |       |       |      |      |      |      | —    |      |      | -     | —      | _    | 0000       |

|                             |                  | 15:0          |       |       | _     | _     |       |       |      | _    | _    | _    |      | _    |      | T2CK  | <<3:0> | _    | 0000       |

| FA1C                        | T3CKR            | 31:16         | _     | —     |       |       |       |       | _    |      |      | —    |      |      | _    | —<br> | -      | —    | 0000       |

|                             |                  | 15:0          | _     |       |       |       |       |       |      |      |      |      |      |      |      | T3CKF | <<3:0> |      | 0000       |

| FA20                        | T4CKR            | 31:16<br>15:0 |       | _     |       |       |       |       |      |      |      |      |      |      |      | T4CKF |        | —    | 0000       |

|                             |                  |               |       |       | _     |       |       |       |      |      |      | _    |      |      |      | 1400  | (<3.0> |      | 0000       |

| FA24                        | T5CKR            | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      |      |      | T5CKF |        | _    | 0000       |

|                             |                  | 31:16         |       |       |       |       |       |       |      |      |      |      | _    |      | _    |       | (<3.0> | _    | 0000       |

| FA28                        | IC1R             | 15:0          | _     | _     |       | _     |       |       |      |      | _    | _    |      |      |      | IC1R  | <3:0>  |      | 0000       |

|                             |                  | 31:16         | _     | _     | _     | _     |       |       |      |      |      | _    |      |      | _    | _     |        | _    | 0000       |

| FA2C                        | IC2R             | 15:0          | _     | _     | _     |       |       | _     | _    | _    | _    | _    | _    |      |      |       | <3:0>  |      | 0000       |

|                             |                  | 31:16         |       |       |       |       | _     |       |      | _    | _    |      |      | _    |      | _     | _      |      | 0000       |

| FA30                        | IC3R             | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC3R  | <3:0>  |      | 0000       |

|                             |                  | 31:16         | _     |       | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       | _      | _    | 0000       |

| FA34                        | IC4R             | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC4R  | <3:0>  |      | 0000       |

| -                           | 10.55            | 31:16         | _     | —     | —     | —     | _     | —     | _    | _    | -    | _    | _    | _    | —    | —     | —      | —    | 0000       |

| FA38                        | IC5R             | 15:0          | _     | _     | _     | _     |       | _     | _    | _    | -    | _    |      |      |      | IC5R  | <3:0>  | •    | 0000       |

| FA 40                       |                  | 31:16         |       |       |       | —     |       |       |      | _    |      |      |      |      | —    | —     | —      | —    | 0000       |

| FA48                        | OCFAR            | 15:0          |       | —     | _     | —     | _     | —     |      | -    | _    | _    | -    | _    |      | OCFA  | R<3:0> |      | 0000       |

| FA50                        | U1RXR            | 31:16         | _     | _     | —     | —     | _     | —     | _    |      | _    | _    |      | -    | _    | _     | _      | _    | 0000       |

| FAGU                        | UIKAR            | 15:0          | _     | —     |       | —     |       |       | _    |      | -    | —    |      |      |      | U1RXI | R<3:0> |      | 0000       |

| FA54                        | U1CTSR           | 31:16         | _     | —     | —     | —     |       | —     |      |      |      | —    |      |      | —    | _     | —      | _    | 0000       |

| 1704                        | UTUTUR           | 15:0          | _     | —     | —     | _     | _     | —     |      | _    | _    | —    | _    | _    |      | U1CTS | R<3:0> |      | 0000       |

| FA58                        | U2RXR            | 31:16         | _     | —     | —     | —     | _     | —     | _    | _    | _    | —    | _    | —    | —    | —     | —      | —    | 0000       |

| 1,100                       | <b>U</b> LIVIN   | 15:0          |       | —     | —     | —     |       | —     | —    | —    | —    | —    | —    | —    |      | U2RXI | R<3:0> |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

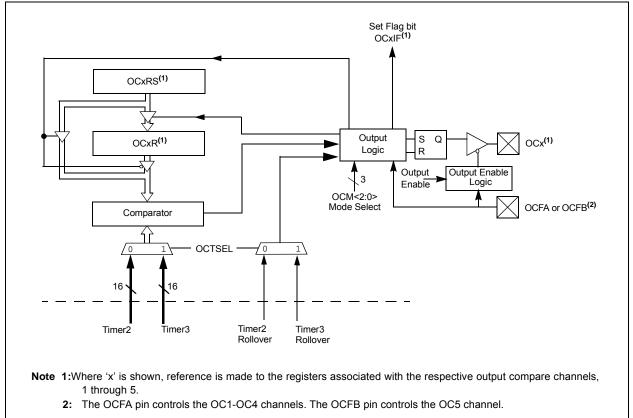

## 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are the key features of this module:

- · Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- · Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

## FIGURE 16-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

## TABLE 17-1: SPI1 THROUGH SPI4 REGISTER MAP (CONTINUED)

| ess                         |                                 | 6             |               |         |        |              |              |              |           | Bit    | ts      |        |        |          |             |          |        |         | \$         |

|-----------------------------|---------------------------------|---------------|---------------|---------|--------|--------------|--------------|--------------|-----------|--------|---------|--------|--------|----------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6   | 21/5   | 20/4     | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

|                             |                                 | 31:16         | -             | —       | —      | _            | _            | _            | —         | _      | —       | _      | —      | _        | _           | —        | —      | —       | 0000       |

| 5C40                        | SPI3CON2                        | 15:0          | SPI<br>SGNEXT | -       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | -      |        |          | AUD<br>MONO | -        | AUDMC  | )D<1:0> | 0000       |

|                             | SPI4CON <sup>(2)</sup>          | 31:16         | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:0 | )>     | MCLKSEL |        | —      | —        | —           |          | SPIFE  | ENHBUF  | 0000       |

| 5E00                        | SPI4COIN-                       | 15:0          | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | L<1:0>   | SRXISE | L<1:0>  | 0000       |

|                             | SPI4STAT <sup>(2)</sup>         | 31:16         | _             | _       | _      |              | RXB          | UFELM<4:     | )>        |        | —       | —      | —      |          | TXE         | BUFELM<4 | :0>    |         | 0000       |

| 5E10                        | 5P1451A1                        | 15:0          | _             | —       | —      | FRMERR       | SPIBUSY      | —            |           | SPITUR | SRMT    | SPIROV | SPIRBE | —        | SPITBE      | —        | SPITBF | SPIRBF  | 19EB       |

| 5E20                        | SPI4BUF <sup>(2)</sup>          | 31:16<br>15:0 |               |         |        |              |              |              |           | DATA<  | 31:0>   |        |        |          |             |          |        |         | 0000       |

|                             | SPI4BRG <sup>(2)</sup>          | 31:16         | _             |         |        | —            | —            | —            | _         | —      | —       | —      | —      | —        | —           | —        | —      | —       | 0000       |

| 5E30                        | SPI4BRG-                        | 15:0          | _             | _       | _      | _            | _            | _            | _         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         |               | —       | —      | —            | —            | —            |           |        | —       | —      | —      | —        | —           | —        | —      | —       | 0000       |

| 5E40                        | SPI4CON2 <sup>(2)</sup>         | 15:0          | SPI<br>SGNEXT | _       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | _      | _      | _        | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register is only available on 100-pin devices.

## TABLE 23-1: CAN1 REGISTER SUMMARY (CONTINUED)

| ess                        |                                 | 6             |       |                |                 |       |       | ,         |          | Bits      | ;      |        |        |       |          |            |          |                |            |

|----------------------------|---------------------------------|---------------|-------|----------------|-----------------|-------|-------|-----------|----------|-----------|--------|--------|--------|-------|----------|------------|----------|----------------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14          | 29/13           | 28/12 | 27/11 | 26/10     | 25/9     | 24/8      | 23/7   | 22/6   | 21/5   | 20/4  | 19/3     | 18/2       | 17/1     | 16/0           | All Resets |

| B340                       | C1FIFOBA                        | 31:16<br>15:0 |       |                |                 |       |       |           |          | C1FIFOBA  | <31:0> |        |        |       |          |            |          |                | 0000       |

| B350                       | C1FIFOCONn                      | 31:16         |       | _              | FSIZE<4:0> 0000 |       |       |           |          |           |        |        |        |       |          |            |          |                |            |

| D330                       | (n = 0-15)                      | 15:0          | —     | FRESET         | UINC            | DONLY | _     | —         | _        | —         | TXEN   | TXABAT | TXLARB | TXERR | TXREQ    | RTREN      | TXPRI    | <1:0>          | 0000       |

| B360                       | C1FIFOINTn                      | 31:16         | -     | -              | —               | —     | —     | TXNFULLIE | TXHALFIE | TXEMPTYIE | —      | —      | -      | —     | RXOVFLIE | RXFULLIE   | RXHALFIE | RXN<br>EMPTYIE | 0000       |

| D300                       | (n = 0-15)                      | 15:0          | _     | -              |                 | -     | _     | TXNFULLIF | TXHALFIF | TXEMPTYIF | _      | —      | -      | _     | RXOVFLIF | RXFULLIF   | RXHALFIF | RXN<br>EMPTYIF | 0000       |

| B370                       | C1FIFOUAn                       | 31:16         |       | C1FIFOUA<31:0> |                 |       |       |           |          |           |        |        |        |       |          |            |          |                |            |

| B370                       | (n = 0-15)                      | 15:0          |       |                |                 |       |       |           |          | CIFIFUUA  | ~31.02 |        |        |       |          |            |          |                | 0000       |

| B380                       | C1FIFOCIn                       | 31:16         | _     | _              | _               | _     | -     | _         | -        | _         | _      | _      | _      |       | _        | _          | _        | -              | 0000       |

| 6300                       | (n = 0-15)                      | 15:0          | —     | —              | _               | _     | _     | _         | _        | _         | _      | —      | _      |       | C1       | FIFOCIn<4: | 0>       |                | 0000       |

Legend: Note 1 x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more 1: information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | —                 | —                 | ABAT              | F                 | REQOP<2:0>       | •                |

| 22:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23:16        | C                 | OPMOD<2:0>        |                   | CANCAP            | —                 | —                 | —                | -                |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDLE             | —                 | CANBUSY           | —                 | —                | _                |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   | _                 |                   | I                 | DNCNT<4:0>        |                  |                  |

## **REGISTER 23-1: C1CON: CAN MODULE CONTROL REGISTER**

| Legend:           | HC = Hardware Clear | S = Settable bit          |                    |

|-------------------|---------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-28 Unimplemented: Read as '0'

- bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

### bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 ON: CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

## REGISTER 23-16: C1FIFOCONn: CAN FIFO CONTROL REGISTER 'n' ('n' = 0 THROUGH 15) (CONTINUED)

- bit 7 TXEN: TX/RX Buffer Selection bit 1 = FIFO is a Transmit FIFO 0 = FIFO is a Receive FIFO TXABAT: Message Aborted bit<sup>(2)</sup> bit 6 1 = Message was aborted 0 = Message completed successfully TXLARB: Message Lost Arbitration bit<sup>(3)</sup> bit 5 1 = Message lost arbitration while being sent 0 = Message did not lose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent. Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received. TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest message priority 10 = High intermediate message priority 01 = Low intermediate message priority

- 01 Low Internetiate message

- 00 = Lowest message priority

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (C1CON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                   | —                 | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 10.0         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | —                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

## 27.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 27-1 for more information.

Note: Disabling a peripheral module while it's ON bit is set, may result in undefined behavior. The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

| Peripheral <sup>(1)</sup>    | PMDx bit Name <sup>(1)</sup> | Register Name and Bit Location |

|------------------------------|------------------------------|--------------------------------|

| ADC1                         | AD1MD                        | PMD1<0>                        |

| СТМИ                         | CTMUMD                       | PMD1<8>                        |

| Comparator Voltage Reference | CVRMD                        | PMD1<12>                       |

| Comparator 1                 | CMP1MD                       | PMD2<0>                        |

| Comparator 2                 | CMP2MD                       | PMD2<1>                        |

| Comparator 3                 | CMP3MD                       | PMD2<2>                        |

| Input Capture 1              | IC1MD                        | PMD3<0>                        |

| Input Capture 2              | IC2MD                        | PMD3<1>                        |

| Input Capture 3              | IC3MD                        | PMD3<2>                        |

| Input Capture 4              | IC4MD                        | PMD3<3>                        |

| Input Capture 5              | IC5MD                        | PMD3<4>                        |

| Output Compare 1             | OC1MD                        | PMD3<16>                       |

| Output Compare 2             | OC2MD                        | PMD3<17>                       |

| Output Compare 3             | OC3MD                        | PMD3<18>                       |

| Output Compare 4             | OC4MD                        | PMD3<19>                       |

| Output Compare 5             | OC5MD                        | PMD3<20>                       |

| Timer1                       | T1MD                         | PMD4<0>                        |

| Timer2                       | T2MD                         | PMD4<1>                        |

| Timer3                       | T3MD                         | PMD4<2>                        |

| Timer4                       | T4MD                         | PMD4<3>                        |

| Timer5                       | T5MD                         | PMD4<4>                        |

| UART1                        | U1MD                         | PMD5<0>                        |

| UART2                        | U2MD                         | PMD5<1>                        |

| UART3                        | U3MD                         | PMD5<2>                        |

| UART4                        | U4MD                         | PMD5<3>                        |

| UART5                        | U5MD                         | PMD5<4>                        |

| SPI1                         | SPI1MD                       | PMD5<8>                        |

| SPI2                         | SPI2MD                       | PMD5<9>                        |

| SPI3                         | SPI3MD                       | PMD5<10>                       |

| SPI4                         | SPI4MD                       | PMD5<11>                       |

| 2C1                          | I2C1MD                       | PMD5<16>                       |

| 2C2                          | I2C2MD                       | PMD5<17>                       |

| USB <sup>(2)</sup>           | USBMD                        | PMD5<24>                       |

| CAN                          | CAN1MD                       | PMD5<28>                       |

| RTCC                         | RTCCMD                       | PMD6<0>                        |

| Reference Clock Output       | REFOMD                       | PMD6<1>                        |

| PMP                          | PMPMD                        | PMD6<16>                       |

Note 1:

Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

## REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 19-10 **PWP<9:0>:** Program Flash Write-Protect bits

| DIT 19-1      | <b>PWP&lt;9:0&gt;:</b> Program Flash Write-Protect bits                                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages. |

|               | 111111111 = Disabled                                                                                                                                                                             |

|               | 1111111110 = Memory below 0x0400 address is write-protected<br>1111111101 = Memory below 0x0800 address is write-protected                                                                       |

|               | 1111111100 = Memory below 0x0000 address is write-protected                                                                                                                                      |

|               | 1111111011 = Memory below 0x1000 (4K) address is write-protected                                                                                                                                 |

|               | 1111111010 = Memory below 0x1400 address is write-protected                                                                                                                                      |

|               | 1111111001 = Memory below 0x1800 address is write-protected                                                                                                                                      |

|               | 1111111000 = Memory below 0x1C00 address is write-protected<br>1111110111 = Memory below 0x2000 (8K) address is write-protected                                                                  |

|               | 1111110110 = Memory below 0x2400 address is write-protected                                                                                                                                      |

|               | 1111110101 = Memory below 0x2800 address is write-protected                                                                                                                                      |

|               | 1111110100 = Memory below 0x2C00 address is write-protected                                                                                                                                      |

|               | 1111110011 = Memory below 0x3000 address is write-protected                                                                                                                                      |

|               | 1111110010 = Memory below 0x3400 address is write-protected<br>1111110001 = Memory below 0x3800 address is write-protected                                                                       |

|               | 1111110000 = Memory below 0x3C00 address is write-protected                                                                                                                                      |

|               | 1111101111 = Memory below 0x4000 (16K) address is write-protected                                                                                                                                |

|               |                                                                                                                                                                                                  |

|               | •<br>1110111111 = Memory below 0x10000 (64K) address is write-protected                                                                                                                          |

|               | •                                                                                                                                                                                                |

|               |                                                                                                                                                                                                  |

|               | 1101111111 = Memory below 0x20000 (128K) address is write-protected                                                                                                                              |

|               |                                                                                                                                                                                                  |

|               | •<br>1011111111 = Memory below 0x40000 (256K) address is write-protected                                                                                                                         |

|               | •                                                                                                                                                                                                |

|               | •                                                                                                                                                                                                |

|               | •<br>0111111111 = Memory below 0x80000 (512K) address is write-protected                                                                                                                         |

|               | •                                                                                                                                                                                                |

|               |                                                                                                                                                                                                  |

|               | 000000000 = All possible memory is write-protected                                                                                                                                               |