Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f256h-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |            |                         |                                    |                  | Ren             | nappabl                               | e Per | iphera               | als                                |                              |                    |                     |     |      |                  |     |      | (þé                                   |          |      |

|-----------------|------------|-------------------------|------------------------------------|------------------|-----------------|---------------------------------------|-------|----------------------|------------------------------------|------------------------------|--------------------|---------------------|-----|------|------------------|-----|------|---------------------------------------|----------|------|

| Device          | Pins       | Packages <sup>(4)</sup> | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers/Capture/Compare <sup>(2)</sup> | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Analog Comparators | USB On-The-Go (OTG) | CAN | CTMU | 1 <sup>2</sup> C | AMP | RTCC | DMA Channels (Programmable/Dedicated) | I/O Pins | JTAG |

| PIC32MX120F064H | 64         | QFN,<br>TQFP            | 64+3                               | 8                | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Ν                   | 0   | Y    | 2                | Y   | Y    | 4/0                                   | 53       | Y    |

| PIC32MX130F128H | 64         | QFN,<br>TQFP            | 128+3                              | 16               | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Ν                   | 0   | Y    | 2                | Y   | Y    | 4/0                                   | 53       | Y    |

| PIC32MX130F128L | 100<br>100 | TQFP<br>TFBGA           | 128+3                              | 16               | 54              | 5/5/5                                 | 5     | 4                    | 5                                  | 48                           | 3                  | N                   | 0   | Y    | 2                | Y   | Y    | 4/0                                   | 85       | Y    |

| PIC32MX230F128H | 64         | QFN,<br>TQFP            | 128+3                              | 16               | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Y                   | 0   | Y    | 2                | Y   | Y    | 4/2                                   | 49       | Y    |

| PIC32MX230F128L | 100<br>100 | TQFP<br>TFBGA           | 128+3                              | 16               | 54              | 5/5/5                                 | 5     | 4                    | 5                                  | 48                           | 3                  | Y                   | 0   | Y    | 2                | Y   | Y    | 4/2                                   | 81       | Y    |

| PIC32MX530F128H | 64         | QFN,<br>TQFP            | 128+3                              | 16               | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Y                   | 1   | Y    | 2                | Y   | Y    | 4/4                                   | 49       | Y    |

| PIC32MX530F128L | 100<br>100 | TQFP<br>TFBGA           | 128+3                              | 16               | 54              | 5/5/5                                 | 5     | 4                    | 5                                  | 48                           | 3                  | Y                   | 1   | Y    | 2                | Y   | Y    | 4/4                                   | 81       | Y    |

| PIC32MX150F256H | 64         | QFN,<br>TQFP            | 256+3                              | 32               | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Ν                   | 0   | Y    | 2                | Y   | Y    | 4/0                                   | 53       | Y    |

| PIC32MX150F256L | 100<br>100 | TQFP<br>TFBGA           | 256+3                              | 32               | 54              | 5/5/5                                 | 5     | 4                    | 5                                  | 48                           | 3                  | Ν                   | 0   | Y    | 2                | Y   | Y    | 4/0                                   | 85       | Y    |

| PIC32MX250F256H | 64         | QFN,<br>TQFP            | 256+3                              | 32               | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Y                   | 0   | Y    | 2                | Y   | Y    | 4/2                                   | 49       | Y    |

| PIC32MX250F256L | 100<br>100 | TQFP<br>TFBGA           | 256+3                              | 32               | 54              | 5/5/5                                 | 5     | 4                    | 5                                  | 48                           | 3                  | Y                   | 0   | Y    | 2                | Y   | Y    | 4/2                                   | 81       | Y    |

| PIC32MX550F256H | 64         | QFN,<br>TQFP            | 256+3                              | 32               | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Y                   | 1   | Y    | 2                | Y   | Y    | 4/4                                   | 49       | Y    |

| PIC32MX550F256L | 100<br>100 | TQFP<br>TFBGA           | 256+3                              | 32               | 54              | 5/5/5                                 | 5     | 4                    | 5                                  | 48                           | 3                  | Y                   | 1   | Y    | 2                | Y   | Y    | 4/4                                   | 81       | Y    |

| PIC32MX170F512H | 64         | QFN,<br>TQFP            | 512+3                              | 64               | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Ν                   | 0   | Y    | 2                | Y   | Y    | 4/0                                   | 53       | Y    |

| PIC32MX170F512L | 100<br>100 | TQFP<br>TFBGA           | 512+3                              | 64               | 54              | 5/5/5                                 | 5     | 4                    | 5                                  | 48                           | 3                  | N                   | 0   | Y    | 2                | Y   | Y    | 4/0                                   | 85       | Y    |

| PIC32MX270F512H | 64         | QFN,<br>TQFP            | 512+3                              | 64               | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Y                   | 0   | Y    | 2                | Y   | Y    | 4/2                                   | 49       | Y    |

| PIC32MX270F512L | 100<br>100 | TQFP<br>TFBGA           | 512+3                              | 64               | 54              | 5/5/5                                 | 5     | 4                    | 5                                  | 48                           | 3                  | Y                   | 0   | Y    | 2                | Y   | Y    | 4/2                                   | 81       | Y    |

| PIC32MX570F512H | 64         | QFN,<br>TQFP            | 512+3                              | 64               | 37              | 5/5/5                                 | 4     | 3                    | 5                                  | 28                           | 3                  | Y                   | 1   | Y    | 2                | Y   | Y    | 4/4                                   | 49       | Y    |

| PIC32MX570F512L | 100<br>100 | TQFP<br>TFBGA           | 512+3                              | 64               | 54              | 5/5/5                                 | 5     | 4                    | 5                                  | 48                           | 3                  | Y                   | 1   | Y    | 2                | Y   | Y    | 4/4                                   | 81       | Y    |

#### TABLE 1: PIC32MX1XX/2XX/5XX 64/100-PIN CONTROLLER FAMILY FEATURES

Note 1: All devices feature 3 KB of Boot Flash memory.

**2:** Four out of five timers are remappable.

Four out of five external interrupts are remappable.

Please contact your local Microchip Sales Office for information regarding the availability of devices in the 100-pin TFBGA package.

| Bit<br>Range | Bit<br>31/23/15/7         | Bit<br>30/22/14/6          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|---------------------------|----------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0                       | R/W-0                      | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                           | RODIV<14:8> <sup>(1)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |

| 00.40        | R/W-0                     | R/W-0                      | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | RODIV<7:0> <sup>(3)</sup> |                            |                   |                   |                     |                   |                  |                  |  |  |  |

| 45.0         | R/W-0                     | U-0                        | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |

| 15:8         | ON                        | _                          | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |

|              | U-0                       | U-0                        | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                           | _                          | _                 | _                 |                     | ROSEL             | _<3:0>(1)        |                  |  |  |  |

### **REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER**

| Legend: HC = Hardware Clearable |                  | HS = Hardware Settable   |                    |  |  |

|---------------------------------|------------------|--------------------------|--------------------|--|--|

| R = Readable bit                | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |  |

| -n = Value at POR               | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |  |

### bit 31 Unimplemented: Read as '0'

### bit 30-16 RODIV<14:0>: Reference Clock Divider bits<sup>(1)</sup>

This value selects the Reference Clock Divider bits. See Figure 8-1 for more information.

- bit 15 **ON:** Output Enable bit

- 1 = Reference Oscillator Module enabled

- 0 = Reference Oscillator Module disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Peripheral Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 **RSLP:** Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator Module output continues to run in Sleep

- 0 = Reference Oscillator Module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

| REGIOTE      |                   |                       |                   |                   |                    |                   |                  |                  |  |  |  |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |  |  |  |

| 31:24        | —                 | —                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO             |  |  |  |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                     | —                 | -                 | —                  | _                 | -                | _                |  |  |  |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | —                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | -                 | —                  | (                 | CRCCH<2:0>       |                  |  |  |  |

### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

### Legend:

| Legena.           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | V = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit<sup>(1</sup>

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | -                 | _                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | —                 | _                 | _                 | -                 | _                 | -                 |                  | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | CHSPTF            | R<7:0>            |                   |                  |                  |  |  |  |

### REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   | _                 | _                 | _                 | —                 |                   | —                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   | —                 | _                 | _                 | —                 |                   | —                | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                    | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:10        | —                 | _                 | _                 | —                    | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

### **REGISTER 16-1:** OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER ('x' = 1 THROUGH 5)

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

### bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

### **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

### 20.1 Control Registers

### TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | ē                           |               |               |       |            |         |        |        | Bi     | its        |         |      |       |        |      |         |      |            |

|-----------------------------|---------------------------------|-----------------------------|---------------|---------------|-------|------------|---------|--------|--------|--------|------------|---------|------|-------|--------|------|---------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range                   | 31/15         | 30/14         | 29/13 | 28/12      | 27/11   | 26/10  | 25/9   | 24/8   | 23/7       | 22/6    | 21/5 | 20/4  | 19/3   | 18/2 | 17/1    | 16/0 | All Resets |

| 7000                        | PMCON                           | 31:16                       | —             | _             | _     | _          | -       | —      | -      |        | RDSTART    | —       | -    | —     | _      | _    | DUALBUF | _    | 0000       |

| 1000                        |                                 | 15:0                        | ON            | —             | SIDL  | ADRML      | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF∢       | <1:0>   | ALP  | CS2P  | CS1P   | —    | WRSP    | RDSP | 0000       |

| 7010                        | PMMODE                          | 31:16                       | —             | —             | —     | —          | —       | _      | —      | —      | —          | _       | —    | —     | —      | —    | -       | _    | 0000       |

|                             |                                 | 15:0                        | BUSY          | IRQM          | <1:0> | INCM       | <1:0>   | MODE16 | MODE   | <1:0>  | WAITE      | 3<1:0>  |      | WAITN | 1<3:0> |      | WAITE   |      | 0000       |

|                             |                                 | 31:16                       | —             | —             | _     | —          | —       | —      | —      | —      | —          | —       | —    | —     | —      | —    | —       | _    | 0000       |

| 7020                        | PMADDR                          | 15:0                        | CS2<br>ADDR15 | CS1<br>ADDR14 |       | ADDR<13:0> |         |        |        |        |            |         |      |       | 0000   |      |         |      |            |

|                             |                                 | 31:16                       | ADDR15        | ADDR 14       | _     |            | _       |        | _      | _      | _          |         | _    |       |        | _    | _       | _    | 0000       |

| 7030                        | PMDOUT                          | 15:0                        |               |               |       |            |         |        |        |        |            | 0000    |      |       |        |      |         |      |            |

|                             |                                 | 31:16                       |               |               |       |            |         |        |        |        |            |         | _    |       |        |      | _       | _    | 0000       |

| 7040                        | PMDIN                           | 15:0                        |               |               |       |            |         |        |        | DATAIN | l<15:0>    |         |      |       |        |      |         |      | 0000       |

|                             |                                 | 31:16                       | _             | _             | _     | _          | _       | _      | _      | _      | _          | —       | _    | _     | _      | _    | _       | _    | 0000       |

| 7050                        | PMAEN                           | 15:0                        |               |               |       |            |         |        |        | PTEN   | <15:0>     |         |      |       |        |      |         |      | 0000       |

| 7060                        | PMSTAT                          | 31:16                       | —             | —             | _     | —          | _       | _      | _      | —      | —          | _       | _    | —     | —      | —    | —       | _    | 0000       |

| 7000                        | FINISTAT                        | 15:0                        | IBF           | IBOV          |       | _          | IB3F    | IB2F   | IB1F   | IB0F   | OBE        | OBUF    |      | _     | OB3E   | OB2E | OB1E    | OB0E | BFBF       |

|                             |                                 | 31:16                       | —             | _             |       | —          |         | —      | 1      | -      | -          | —       | 1    | —     | _      | -    | -       |      | 0000       |

| 7070                        | PMWADDR                         | 15:0                        | WCS2          | WCS1          | _     | —          | _       | _      | _      | —      | —          |         | _    | —     | —      | _    | -       | _    | 0000       |

|                             |                                 | 15.0                        | WADDR15       | WADDR14       |       |            |         |        |        |        | WADDF      | R<13:0> |      |       |        |      |         |      | 0000       |

|                             |                                 | 31:16                       | —             | —             | _     | —          |         | —      | _      | _      | _          |         | _    | —     | —      | _    | —       |      | 0000       |

| 7080                        | PMRADDR                         | 15:0                        | RCS2          | RCS1          | _     | —          | _       |        | —      | —      | —          | _       | —    | —     | —      | _    | —       | _    | 0000       |

|                             |                                 | RADDR15 RADDR14 RADDR<13:0> |               |               |       |            |         |        |        | 0000   |            |         |      |       |        |      |         |      |            |

| 7090                        | PMRDIN                          | 31:16                       | 31:16         | —             | —     | —          | _       | _      | —      | —      | —          | —       | —    | —     | —      | _    | —       | _    | 0000       |

| 1030                        |                                 | 15:0                        | 15:0          |               |       |            |         |        |        | R      | DATAIN<15: | 0>      |      |       |        |      |         |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                       | —                     | _                 | _                 | _                 | _                 | _                | —                |  |

| 00.40        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                       | —                     | _                 | _                 | _                 | _                 | —                | —                |  |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    |                   |                   |                   | ~12.05            |                  |                  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   |                   | ADDR              | <13.0>            |                  |                  |  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                       |                       | ADDR<7:0>         |                   |                   |                   |                  |                  |  |

### REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

**Note:** If the DUALBUF bit (PMCON<17>) = 0, the bits in this register control both read and write target addressing. If the DUALBUF bit = 1, the bits in this register are not used. In this instance, use the PMRADDR register for Read operations and the PMWADDR register for Write operations.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|------------------------|------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                      | _                      | _                 |                   |                   | _                 | -                | —                |

| 22:16        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                      | —                      | _                 | _                 | _                 | _                 | _                | —                |

|              | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | WCS2 <sup>(1)</sup>    | WCS1 <sup>(3)</sup>    |                   |                   |                   | 2 < 1 2 . 0 >     |                  |                  |

|              | WADDR15 <sup>(2)</sup> | WADDR14 <sup>(4)</sup> |                   |                   | WADDF             | <<13:8>           |                  |                  |

| 7:0          | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                        |                        |                   | WADDR<            | 7:0>              |                   |                  |                  |

### REGISTER 20-8: PMWADDR: PARALLEL PORT WRITE ADDRESS REGISTER

### Legend:

| Logonal           |                  |                        |                    |  |  |

|-------------------|------------------|------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | bit, read as '0'   |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |  |

- bit 31-16 Unimplemented: Read as '0'

- bit 15 WCS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 WADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 WCS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 WADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 WADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

### REGISTER 23-16: C1FIFOCONn: CAN FIFO CONTROL REGISTER 'n' ('n' = 0 THROUGH 15) (CONTINUED)

- bit 7 TXEN: TX/RX Buffer Selection bit 1 = FIFO is a Transmit FIFO 0 = FIFO is a Receive FIFO TXABAT: Message Aborted bit<sup>(2)</sup> bit 6 1 = Message was aborted 0 = Message completed successfully TXLARB: Message Lost Arbitration bit<sup>(3)</sup> bit 5 1 = Message lost arbitration while being sent 0 = Message did not lose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent. Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received. TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest message priority 10 = High intermediate message priority 01 = Low intermediate message priority

- 00 = Lowest message priority

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (C1CON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 | —                 | —                 | _                 | —                 | —                 | -                | —                |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | -                 | —                 |                   | _                 | _                 | _                 | -                | _                |  |  |  |  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 10.0         | —                 | —                 | SIDL              | —                 | —                 | —                 | —                | —                |  |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          | _                 | —                 | _                 |                   | _                 | C3OUT             | C2OUT            | C10UT            |  |  |  |  |

### REGISTER 24-2: CMSTAT: COMPARATOR STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-14 Unimplemented: Read as '0'

bit 13 **SIDL:** Stop in IDLE Control bit

1 = All Comparator modules are disabled in IDLE mode

0 = All Comparator modules continue to operate in the IDLE mode

### bit 12-3 Unimplemented: Read as '0'

- bit 2 C3OUT: Comparator Output bit

- 1 = Output of Comparator 3 is a '1'

- 0 = Output of Comparator 3 is a '0'

### bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

### bit 0 **C1OUT:** Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

| REGIST  | ER 26-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)                                          |

|---------|----------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                           |

|         | 1 = Edge 1 must occur before Edge 2 can occur                                                |

|         | 0 = No edge sequence is needed                                                               |

| bit 9   | <b>IDISSEN:</b> Analog Current Source Control bit <sup>(2)</sup>                             |

|         | 1 = Analog current source output is grounded                                                 |

|         | 0 = Analog current source output is not grounded                                             |

| bit 8   | CTTRIG: Trigger Control bit                                                                  |

|         | 1 = Trigger output is enabled                                                                |

|         | 0 = Trigger output is disabled                                                               |

| bit 7-2 | ITRIM<5:0>: Current Source Trim bits                                                         |

|         | 011111 = Maximum positive change from nominal current                                        |

|         | 011110                                                                                       |

|         |                                                                                              |

|         |                                                                                              |

|         | 000001 = Minimum positive change from nominal current                                        |

|         | 000000 = Nominal current output specified by IRNG<1:0>                                       |

|         | 111111 = Minimum negative change from nominal current                                        |

|         |                                                                                              |

|         | •                                                                                            |

|         | 100010                                                                                       |

|         | 100001 = Maximum negative change from nominal current                                        |

| bit 1-0 | IRNG<1:0>: Current Range Select bits <sup>(3)</sup>                                          |

|         | 11 = 100 times base current                                                                  |

|         | 10 = 10 times base current                                                                   |

|         | 01 = Base current level                                                                      |

|         | 00 = 1000 times base current <sup>(4)</sup>                                                  |

| Nets 4  | When this bit is set for Dules Delay Operation, the EDOOOEL (0.0), bits must be act to (1.1) |

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3            | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------|-------------------|------------------|------------------|--|

| 04.04        | r-0               | r-1               | r-1               | R/P               | r-1                          | r-1               | r-1              | R/P              |  |

| 31:24        | —                 | —                 | _                 | СР                | —                            | —                 | _                | BWP              |  |

| 00.40        | r-1               | r-1               | r-1               | r-1               | R/P                          | R/P               | R/P              | R/P              |  |

| 23:16        | —                 | _                 | _                 | _                 |                              | PWP               | <9:6>            |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P                          | R/P               | r-1              | r-1              |  |

| 15:8         |                   |                   | PWP<              | :5:0>             |                              |                   | _                | —                |  |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P                          | R/P               | R/P              | R/P              |  |

| 7:0          |                   | _                 |                   | ICESE             | _<1:0> JTAGEN <sup>(1)</sup> |                   | DEBUG<1:0>       |                  |  |

### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:         r = Reserved bit         P = Programmable bit |                  |                                    |                    |  |  |

|---------------------------------------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit                                              | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                                             | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31 Reserved: Write '0'

- bit 30-29 Reserved: Write '1'

- bit 28 **CP:** Code-Protect bit

- Prevents boot and program Flash memory from being read or modified by an external programming device.

- 1 = Protection is disabled

- 0 = Protection is enabled

- bit 27-25 Reserved: Write '1'

- bit 24 **BWP:** Boot Flash Write-Protect bit

- Prevents boot Flash memory from being modified during code execution.

- 1 = Boot Flash is writable

- 0 = Boot Flash is not writable

- bit 23-20 Reserved: Write '1'

- Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

### REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

### bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

#### bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator disabled

- 10 = HS Oscillator mode selected

- 01 = XT Oscillator mode selected

- 00 = External Clock mode selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

### 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

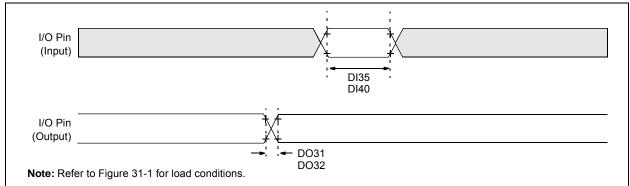

### FIGURE 31-3: I/O TIMING CHARACTERISTICS

### TABLE 31-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                       |                           | (unless other | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                        |      |         |            |  |  |

|--------------------|---------------------------------------|---------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|---------|------------|--|--|

| Param.<br>No.      | Symbol Characteristics <sup>(2)</sup> |                           |               | Min.                                                                                                                                                                                               | Typical <sup>(1)</sup> | Max. | Units   | Conditions |  |  |

| DO31               | TIOR                                  | Port Output Rise Time     |               |                                                                                                                                                                                                    | 5                      | 15   | ns      | Vdd < 2.5V |  |  |

|                    |                                       |                           |               |                                                                                                                                                                                                    | 5                      | 10   | ns      | Vdd > 2.5V |  |  |

| DO32               | TIOF                                  | Port Output Fall Tim      | е             | _                                                                                                                                                                                                  | 5                      | 15   | ns      | Vdd < 2.5V |  |  |

|                    |                                       |                           |               |                                                                                                                                                                                                    | 5                      | 10   | ns      | VDD > 2.5V |  |  |

| DI35               | Tinp                                  | INTx Pin High or Low Time |               | 10                                                                                                                                                                                                 | _                      | _    | ns      | _          |  |  |

| DI40               | Trbp                                  | CNx High or Low Tir       | me (input)    | 2                                                                                                                                                                                                  | _                      | _    | TSYSCLK |            |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

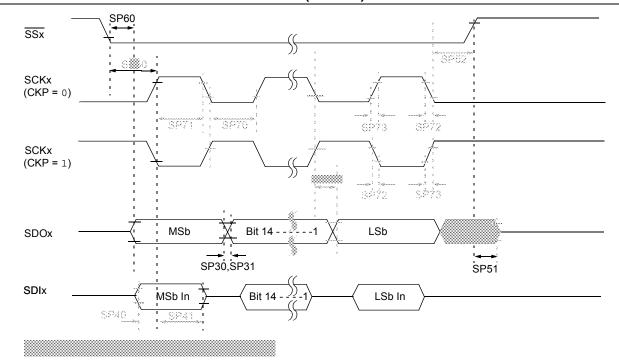

### FIGURE 31-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

### TABLE 31-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                           |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                    |  |

|--------------------|-----------------------|---------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.   | Typical <sup>(2)</sup>                                                                                                                                                                                                                                                             | Max. | Units | Conditions         |  |

| SP70               | TscL                  | SCKx Input Low Time (Note 3)                                              | Тѕск/2 | _                                                                                                                                                                                                                                                                                  |      | ns    | _                  |  |

| SP71               | TscH                  | SCKx Input High Time (Note 3)                                             | Tsck/2 | —                                                                                                                                                                                                                                                                                  | _    | ns    | —                  |  |

| SP72               | TscF                  | SCKx Input Fall Time                                                      | —      | 5                                                                                                                                                                                                                                                                                  | 10   | ns    | —                  |  |

| SP73               | TscR                  | SCKx Input Rise Time                                                      | —      | 5                                                                                                                                                                                                                                                                                  | 10   | ns    | —                  |  |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)                                       | —      | —                                                                                                                                                                                                                                                                                  | _    | ns    | See parameter DO32 |  |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)                                       | —      | —                                                                                                                                                                                                                                                                                  | _    | ns    | See parameter DO31 |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                 |        | _                                                                                                                                                                                                                                                                                  | 20   | ns    | VDD > 2.7V         |  |

|                    |                       |                                                                           |        | _                                                                                                                                                                                                                                                                                  | 30   | ns    | VDD < 2.7V         |  |

| SP40               | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                | 10     | —                                                                                                                                                                                                                                                                                  | _    | ns    | —                  |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                 | 10     | —                                                                                                                                                                                                                                                                                  |      | ns    | —                  |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175    | —                                                                                                                                                                                                                                                                                  |      | ns    | —                  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

NOTES:

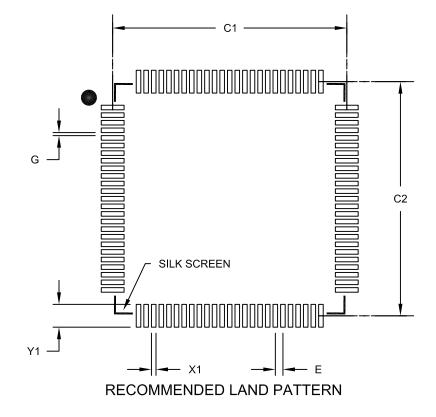

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |          |       |      |  |

|---------------------------|-------------|----------|-------|------|--|

| Dimension Limits          |             | MIN      | NOM   | MAX  |  |

| Contact Pitch             | E           | 0.50 BSC |       |      |  |

| Contact Pad Spacing       | C1          |          | 15.40 |      |  |

| Contact Pad Spacing       | C2          |          | 15.40 |      |  |

| Contact Pad Width (X100)  | X1          |          |       | 0.30 |  |

| Contact Pad Length (X100) | Y1          |          |       | 1.50 |  |

| Distance Between Pads     | G           | 0.20     |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

### w

| WWW Address          | 377 |

|----------------------|-----|

| WWW, On-Line Support | 9   |