Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 49                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 28x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

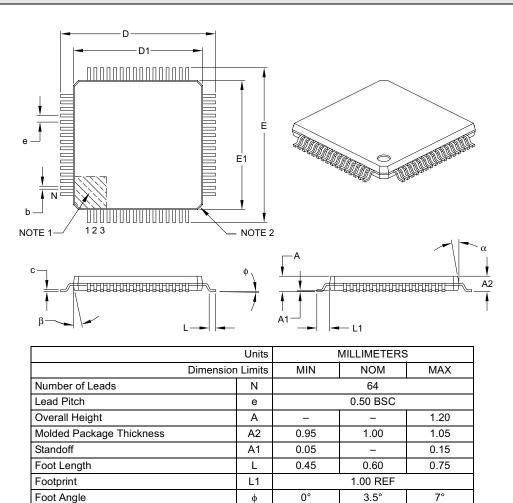

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-QFN (9x9)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f256ht-50i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Name        | Function                                                                                                                                                              |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| HWREna                  | Enables access via the RDHWR instruction to selected hardware registers.                                                                                              |

| BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.                                                                                                    |

| Count <sup>(1)</sup>    | Processor cycle count.                                                                                                                                                |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| Compare <sup>(1)</sup>  | Timer interrupt control.                                                                                                                                              |

| Status <sup>(1)</sup>   | Processor status and control.                                                                                                                                         |

| IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                                                                                                                  |

| Cause <sup>(1)</sup>    | Cause of last general exception.                                                                                                                                      |

| EPC <sup>(1)</sup>      | Program counter at last exception.                                                                                                                                    |

| PRId                    | Processor identification and revision.                                                                                                                                |

| EBASE                   | Exception vector base register.                                                                                                                                       |

| Config                  | Configuration register.                                                                                                                                               |

| Config1                 | Configuration register 1.                                                                                                                                             |

| Config2                 | Configuration register 2.                                                                                                                                             |

| Config3                 | Configuration register 3.                                                                                                                                             |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| Debug <sup>(2)</sup>    | Debug control and exception status.                                                                                                                                   |

| DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                                                                                                              |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| ErrorEPC <sup>(1)</sup> | Program counter at last error.                                                                                                                                        |

| DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                                                                                                                    |

|                         | NameReservedHWREnaBadVAddr(1)Count(1)ReservedCompare(1)Status(1)IntCtl(1)Cause(1)EPC(1)PRIdEBASEConfigConfig1Config2Config3ReservedDebug(2)DEPC(2)ReservedErrorEPC(1) |

| TABLE 3-2. COPROCESSOR UREGISTERS | <b>TABLE 3-2:</b> | <b>COPROCESSOR 0 REGISTERS</b> |

|-----------------------------------|-------------------|--------------------------------|

|-----------------------------------|-------------------|--------------------------------|

Note 1: Registers used in exception processing.

**2:** Registers used during debug.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | _                 | _                 | _                 | —                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         | BMXDUDBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |  |  |

# REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

# 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX1XX/2XX/5XX 64/100-pin devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX1XX/2XX/5XX 64/100-pin devices, the Flash page size is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|----------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | U-0               | R/W-0                      | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        |                   | RODIV<14:8> <sup>(1)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0                      | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        |                   | RODIV<7:0> <sup>(3)</sup>  |                   |                   |                     |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | U-0                        | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |  |  |

| 15:8         | ON                | _                          | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |  |  |

|              | U-0               | U-0                        | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   | _                          |                   | _                 |                     | ROSEL             | _<3:0>(1)        |                  |  |  |  |  |  |

#### **REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER**

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31 Unimplemented: Read as '0'

#### bit 30-16 RODIV<14:0>: Reference Clock Divider bits<sup>(1)</sup>

This value selects the Reference Clock Divider bits. See Figure 8-1 for more information.

- bit 15 **ON:** Output Enable bit

- 1 = Reference Oscillator Module enabled

- 0 = Reference Oscillator Module disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Peripheral Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 **RSLP:** Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator Module output continues to run in Sleep

- 0 = Reference Oscillator Module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# 9.1 Control Registers

### TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 |           |       | Bits          |       |         |         |       |      |          |      |      |      |      | 6    |      |          |      |            |

|-----------------------------|---------------------------------|-----------|-------|---------------|-------|---------|---------|-------|------|----------|------|------|------|------|------|------|----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 2000                        | DMACON                          | 31:16     | _     | _             | —     | _       | —       | _     | —    | _        | _    | _    | _    | _    | _    | _    | _        |      | 0000       |

| 3000                        | DMACON                          | 15:0      | ON    | —             | _     | SUSPEND | DMABUSY | _     | —    | _        | —    | —    | —    | _    | —    | _    | —        | —    | 0000       |

| 2010                        | DMASTAT                         | 31:16     | _     | —             | _     | _       |         | _     | —    | _        | —    | —    | —    | _    | —    | _    | —        | —    | 0000       |

| 3010                        | DIVIASTAT                       | 15:0      |       | -             | _     | _       | —       | _     | _    | —        | -    | —    | _    | —    | RDWR | C    | MACH<2:0 | >    | 0000       |

| 2020                        | DMAADDR                         | 31:16     |       | DMAADDR<31:0> |       |         |         |       |      |          |      |      |      | 0000 |      |      |          |      |            |

| 3020                        | DIVIAADDR                       | 15:0      |       |               |       |         |         |       |      | DIVIAADD | 1.02 |      |      |      |      |      |          |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### TABLE 9-2: DMA CRC REGISTER MAP

| ess                              |                                 | â         |                | Bits  |       |                               |       |       |      |       |           |      |      |            |      |      |      |      |            |

|----------------------------------|---------------------------------|-----------|----------------|-------|-------|-------------------------------|-------|-------|------|-------|-----------|------|------|------------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#)      | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15          | 30/14 | 29/13 | 28/12                         | 27/11 | 26/10 | 25/9 | 24/8  | 23/7      | 22/6 | 21/5 | 20/4       | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 2020                             | DCRCCON                         | 31:16     | _              | _     | BYTO  | <1:0>                         | WBO   | —     | _    | BITO  | —         | —    | _    | _          | _    | _    | —    | _    | 0000       |

| 3030                             | DURUUUN                         | 15:0      | _              |       | —     | PLEN<4:0> CRCEN CRCAPP CRCTYP |       |       |      |       |           |      | _    | CRCCH<2:0> |      |      | 0000 |      |            |

| 3040                             | DCRCDATA                        | 31:16     |                |       |       |                               |       |       |      |       | TA-21:05  |      |      |            |      |      |      |      | 0000       |

| 3040                             | DCRODAIA                        | 15:0      | DCRCDATA<31:0> |       |       |                               |       |       |      |       |           | 0000 |      |            |      |      |      |      |            |

| 3050 DCRCXOR 31:16 DCRCXOR<31:0> |                                 |           |                |       |       |                               |       |       |      |       | 0000      |      |      |            |      |      |      |      |            |

| 3030                             | DONOXON                         | 15:0      |                |       |       |                               |       |       |      | DOROX | JIX-51.02 |      |      |            |      |      |      |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

# REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected</li> <li>Either the source or the destination address is invalid.</li> </ul>                                                        |

0 = No interrupt is pending

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     | CHSSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.10     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45-0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8      | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |

# **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | CHDSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | CHDSA<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\text{Note:}}$  This must be the physical address of the destination.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | —                 | -                 |                   | _                 | -                 | -                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        |                   | —                 | -                 |                   | _                 | -                 | -                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         |                   | _                 | -                 |                   | _                 | -                 |                  | _                |  |  |

| 7.0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |  |  |

| 7:0          | ID                | —                 | LSTATE            | _                 | SESVD             | SESEND            |                  | VBUSVD           |  |  |

# REGISTER 10-3: U1OTGSTAT: USB OTG STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a Type-B cable has been plugged into the USB receptacle

- 0 = A Type-A cable has been plugged into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has been stable for the previous 1 ms

- 0 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has not been stable for the previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 **SESEND:** B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   |                   |                   |                   |                  | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | -                 | -                 | -                 | -                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | -                 | -                 | -                 | -                 |                  | —                |

| 7:0          | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | _                 | _                 | USBSIDL           | USBSIDL           |                   | _                | UASUSPND         |

### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test enabled

- 0 = Eye-Pattern Test disabled

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 3 LSDEV: Low-Speed Device Enable bit

- 1 = USB module operates in Low-Speed Device mode only

- 0 = USB module operates in OTG, Host, or Full-Speed Device mode

- bit 2-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock

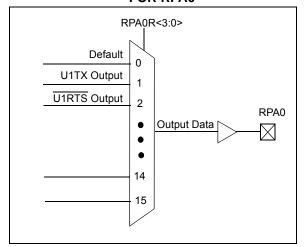

### 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

# 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

# 11.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

### 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

#### **Control Registers** 18.1

# TABLE 18-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |            |                        |           |              |             |              |             | Bi         | ts        |             |             |              |            |          |           |      |              |

|-----------------------------|---------------------------------|---------------|------------|------------------------|-----------|--------------|-------------|--------------|-------------|------------|-----------|-------------|-------------|--------------|------------|----------|-----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15      | 30/14                  | 29/13     | 28/12        | 27/11       | 26/10        | 25/9        | 24/8       | 23/7      | 22/6        | 21/5        | 20/4         | 19/3       | 18/2     | 17/1      | 16/0 | All Resets   |

| 5000                        | I2C1CON                         | 31:16<br>15:0 | —<br>ON    |                        | —<br>SIDL | —<br>SCLREL  | —<br>STRICT | —<br>A10M    | —<br>DISSLW | —<br>SMEN  | —<br>GCEN | —<br>STREN  | —<br>ACKDT  | —<br>ACKEN   | —<br>RCEN  | —<br>PEN | —<br>RSEN |      | 0000<br>BFFF |

| 5040                        | 10040747                        | 31:16         | _          | _                      | _         | _            | _           | -            | _           | _          | _         | _           | _           | _            | -          | _        | _         | _    | 0000         |

| 5010                        | I2C1STAT                        | 15:0          | ACKSTAT    | TRSTAT                 | _         | _            | _           | BCL          | GCSTAT      | ADD10      | IWCOL     | I2COV       | D_A         | Р            | S          | R_W      | RBF       | TBF  | 0000         |

| 5000                        | 1001400                         | 31:16         | _          | —                      | -         | _            | —           | _            | —           | _          | —         | —           | —           | _            | _          | _        | —         | _    | 0000         |

| 5020                        | I2C1ADD                         | 15:0          | _          | _                      |           | _            | _           |              |             |            |           | •           | Address     | Register     |            |          |           |      | 0000         |

| 5030                        | I2C1MSK                         | 31:16         | —          | —                      | _         | —            | —           | _            | —           | —          | —         | —           | _           | _            | —          | —        | —         | —    | 0000         |

| 5030                        | 12C TIVISK                      | 15:0          | _          | _                      |           | _            | —           | _            |             |            |           |             | Address Ma  | ask Register | •          |          |           |      | 0000         |

| 5040                        | I2C1BRG                         | 31:16         | _          | —                      | 1         | —            | —           |              | —           | _          | _         | —           | —           | —            |            | -        | —         |      | 0000         |

| 5040                        | 120 IDIXO                       | 15:0          | _          | —                      |           |              |             |              |             |            | Βαι       | ud Rate Ger | erator Reg  | ister        |            |          | -         |      | 0000         |

| 5050                        | I2C1TRN                         | 31:16         | —          | —                      | _         |              | —           | —            | —           | —          | —         | —           |             | —            | —          | —        | —         | —    | 0000         |

| 0000                        |                                 | 15:0          | —          | —                      | _         |              |             | _            | —           | —          |           |             |             | Transmit     | Register   |          |           |      | 0000         |

| 5060                        | I2C1RCV                         | 31:16         | —          | —                      | —         | —            | —           | _            | —           | —          | _         | —           | —           | —            | —          | —        | —         | —    | 0000         |

|                             |                                 | 15:0          | _          | —                      | _         | —            | —           | _            | —           | _          |           |             |             | Receive      | Register   |          |           |      | 0000         |

| 5100                        | I2C2CON                         | 31:16         | —          | _                      | _         |              |             | _            | _           | _          | _         | —           |             | —            | —          | —        |           |      | 0000         |

|                             |                                 | 15:0          | ON         | _                      | SIDL      | SCLREL       | STRICT      | A10M         | DISSLW      | SMEN       | GCEN      | STREN       | ACKDT       | ACKEN        | RCEN       | PEN      | RSEN      | SEN  | BFFF         |

| 5110                        | I2C2STAT                        | 31:16         | _          | —                      | _         | _            | —           | —            | _           | _          | _         | _           | —           | _            | —          | —        | —         | —    | 0000         |

|                             |                                 | 15:0          | ACKSTAT    | TRSTAT                 | _         |              | _           | BCL          | GCSTAT      | ADD10      | IWCOL     | I2COV       | D_A         | Р            | S          | R_W      | RBF       | TBF  | 0000         |

| 5120                        | I2C2ADD                         | 31:16         | _          | _                      |           |              |             |              |             | _          |           | _           |             |              | _          | _        | —         | _    | 0000         |

|                             |                                 | 15:0          | _          | _                      |           |              |             |              |             |            |           | 1           | Address     | Register     |            |          |           |      | 0000         |

| 5130                        | I2C2MSK                         | 31:16<br>15:0 | _          | _                      | _         | _            |             |              | —           |            | _         | _           | —           | _            | _          | _        | —         | _    | 0000         |

|                             |                                 | 15:0<br>31:16 |            |                        |           |              |             |              |             |            |           | _           | Address Ma  | ask Register |            |          |           |      | 0000         |

| 5140                        | I2C2BRG                         | 15:0          |            |                        |           |              |             |              | —           | _          |           | ud Rate Ger |             |              |            | _        |           |      | 0000         |

|                             |                                 | 31:16         |            |                        |           |              | _           | _            | _           | _          | Dal       |             | leialui Rey | ISIEI        |            |          |           | _    | 0000         |

| 5150                        | I2C2TRN                         | 15:0          |            |                        | _         |              |             |              | _           |            |           |             |             | Transmit     | Register   |          |           |      | 0000         |

|                             |                                 | 31:16         |            |                        |           |              |             |              |             |            |           |             |             |              |            |          |           | _    | 0000         |

| 5160                        | I2C2RCV                         | 15:0          | _          | _                      | _         | _            | _           | _            | _           | _          |           |             | 1           | Receive      | Register   |          | 1         |      | 0000         |

| Legen                       | d: x=u                          |               | n value on | Reset <sup>.</sup> — = | unimpleme | ented read a | as '0' Rese | t values are | shown in h  | exadecimal |           |             |             | 1000110      | . togiotoi |          |           |      | 3000         |

© 2014-2016 Microchip Technology Inc.

All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information. Note 1:

| 31:24         U-0         U-0         U-0         U-0         U-0         U-0         R/W-0         R/W-0 |       |                         |          |       |       |                        |         |                        |                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------|----------|-------|-------|------------------------|---------|------------------------|------------------|

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _     | -                       |          |       |       |                        |         |                        | Bit<br>24/16/8/0 |

| -         -         -         -         -         CAL<9:8>           23:16         RW-0         U-0                                                                       | 21.24 | U-0                     | U-0      | U-0   | U-0   | U-0                    | U-0     | R/W-0                  | R/W-0            |

| 23:16         CAL<7:0>           15:8         R/W-0         U-0         R/W-0         U-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R-0         R/W-0         R/W-0         R/W-0         R-0         R/W-0         R/W-0         R/W-0         R-0         R/W-0                                                       | 31.24 | —                       | —        | _     | —     | —                      | —       | CAL<9                  | ):8>             |

| CAL<7:0>           15:8         R/W-0         U-0         R/W-0         U-0         U-0         U-0         U-0         U-0           15:8         R/W-0         R-0         SIDL         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <td>22.16</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td> <td>R/W-0</td>                        | 22.16 | R/W-0                   | R/W-0    | R/W-0 | R/W-0 | R/W-0                  | R/W-0   | R/W-0                  | R/W-0            |

| 15:8         ON <sup>(1,2)</sup> —         SIDL         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         #         #         #         #         #         #         #         #                                                                                                                                                               | 23.10 |                         |          |       | CAL<  | :7:0>                  |         |                        |                  |

| ON(1,2)         —         SIDL         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         … <th…< td=""><td>15.0</td><td>R/W-0</td><td>U-0</td><td>R/W-0</td><td>U-0</td><td>U-0</td><td>U-0</td><td>U-0</td><td>U-0</td></th…<>                                 | 15.0  | R/W-0                   | U-0      | R/W-0 | U-0   | U-0                    | U-0     | U-0                    | U-0              |

| 7.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10.0  | ON <sup>(1,2)</sup>     | —        | SIDL  | —     | —                      | —       | —                      | -                |

| <sup>7.0</sup> RTSECSEL <sup>(3)</sup> RTCCLKON — RTCWREN <sup>(4)</sup> RTCSYNC HALFSEC <sup>(5)</sup> RTCOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7.0   |                         | -        | U-0   |       | -                      | R-0     | R-0                    | R/W-0            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7:0   | RTSECSEL <sup>(3)</sup> | RTCCLKON | _     | _     | RTCWREN <sup>(4)</sup> | RTCSYNC | HALFSEC <sup>(5)</sup> | RTCOE            |

#### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          | l |

|-------------------|------------------|---------------------------|--------------------|---|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |   |

#### bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: RTC Drift Calibration bits, which contain a signed 10-bit integer value 0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute 000000000 = No adjustment 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute 100000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute ON: RTCC On bit<sup>(1,2)</sup> bit 15 1 = RTCC module is enabled 0 = RTCC module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Stop in Idle Mode bit 1 = Disables the PBCLK to the RTCC when CPU enters in Idle mode 0 = Continue normal operation in Idle mode Unimplemented: Read as '0' bit 12-8 bit 7 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(3)</sup> 1 = RTCC Seconds Clock is selected for the RTCC pin 0 = RTCC Alarm Pulse is selected for the RTCC pin bit 6 RTCCLKON: RTCC Clock Enable Status bit 1 = RTCC Clock is actively running 0 = RTCC Clock is not running bit 5-4 Unimplemented: Read as '0' **Note 1:** The ON bit is only writable when RTCWREN = 1. 2: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active. 4: The RTCWREN bit can be set only when the write sequence is enabled. 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>). Note: This register is reset only on a Power-on Reset (POR).

| ILE OIOTE    |       |       |          |       |             |       |                  |                  |  |  |

|--------------|-------|-------|----------|-------|-------------|-------|------------------|------------------|--|--|

| Bit<br>Range |       |       |          |       |             |       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04        | U-0   | U-0   | U-0      | U-0   | U-0         | U-0   | U-0              | U-0              |  |  |

| 31:24        | —     | _     | _        | —     | _           | _     | _                | —                |  |  |

| 00.40        | R/W-x | R/W-x | R/W-x    | R/W-x | R/W-x       | R/W-x | R/W-x            | R/W-x            |  |  |

| 23:16        |       | MONT  | H10<3:0> |       |             | MONTH | 01<3:0>          |                  |  |  |

| 45.0         | R/W-x | R/W-x | R/W-x    | R/W-x | R/W-x       | R/W-x | R/W-x            | R/W-x            |  |  |

| 15:8         |       | DAY   | 10<1:0>  |       | DAY01<3:0>  |       |                  |                  |  |  |

| 7.0          | U-0   | U-0   | U-0      | U-0   | R/W-x       | R/W-x | R/W-x            | R/W-x            |  |  |

| 7:0          | _     | —     | —        | _     | WDAY01<3:0> |       |                  |                  |  |  |

# REGISTER 21-6: ALRMDATE: ALARM DATE VALUE REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 **DAY10<3:0>:** Binary Coded Decimal value of days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9 bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1s place digit; contains a value from 0 to 6

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | CSSL31 <sup>(2)</sup> | CSSL30 <sup>(1)</sup> | CSSL29 <sup>(1)</sup> | CSSL28 <sup>(1)</sup> | CSSL27            | CSSL26            | CSSL25           | CSSL24           |

| 22:16        | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CSSL23                | CSSL21                | CSSL21                | CSSL20                | CSSL19            | CSSL18            | CSSL17           | CSSL16           |

| 15.0         | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15                | CSSL14                | CSSL13                | CSSL12                | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7                 | CSSL6                 | CSSL5                 | CSSL4                 | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

#### REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

## Legend:

| •                 |                  |                           |                    |  |  |  |

|-------------------|------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | it, read as '0'    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

bit 31-0 CSSL<31:0>: ADC Input Pin Scan Selection bits

- 1 = Select ANx for input scan; CSSLx = ANx, where 'x' = 0-31

- 0 = Skip ANx for input scan; CSSLx = ANx, where 'x' = 0-31

- Note 1: For devices with 64 pins, CSSL28 selects IVREF (Band Gap) for scan; CSSL29 selects CTMU temperature diode for scan; and CSSL30 selects CTMU input for scan

- 2: On devices with less than 32 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

| REGISTER 22-0. ADTOUGE2. ADD INT OT GOAN DELEDT REGISTER 2 |                   |                   |                   |                   |                   |                       |                       |                       |  |

|------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-----------------------|-----------------------|--|

| Bit<br>Range                                               | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |  |

| 31:24                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0                   | U-0                   |  |

| 31.24                                                      | —                 | —                 | —                 | —                 | —                 | —                     | —                     | _                     |  |

| 22:16                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                 | R/W-0                 | R/W-0                 |  |

| 23:16                                                      | _                 | —                 | —                 | —                 | —                 | CSSL50 <sup>(1)</sup> | CSSL49 <sup>(1)</sup> | CSSL48 <sup>(1)</sup> |  |

| 15.0                                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0                 | R/W-0                 |  |

| 15:8                                                       | CSSL47            | CSSL46            | CSSL45            | CSSL44            | CSSL43            | CSSL42                | CSSL41                | CSSL40                |  |

| 7:0                                                        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0                 | R/W-0                 |  |

| 7:0                                                        | CSSL39            | CSSL38            | CSSL37            | CSSL36            | CSSL35            | CSSL34                | CSSL33                | CSSL32                |  |

#### REGISTER 22-6: AD1CSSL2: ADC INPUT SCAN SELECT REGISTER 2

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-19 Unimplemented: Read as '0'

- bit 18-0 CSSL<50:32>: ADC Input Pin Scan Selection bits

- 1 = Select ANx for input scan; CSSLx = ANx, where 'x' = 32-50

- 0 =Skip ANx for input scan; CSSLx = ANx, where 'x' = 32-50

- Note 1: For devices with 100 or more pins, CSSL48 selects IVREF (Band Gap) for scan; CSSL49 selects CTMU temperature diode for scan; and CSSL50 selects CTMU input for scan

**Note:** The ANx inputs in this register only support devices with 100 or more pins.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                   | —                 | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 10.0         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | —                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.