Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

| roduct Status            | Active                                                                         |

| ore Processor            | MIPS32® M4K™                                                                   |

| ore Size                 | 32-Bit Single-Core                                                             |

| peed                     | 40MHz                                                                          |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| ripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                |

| umber of I/O             | 81                                                                             |

| ogram Memory Size        | 256KB (256K x 8)                                                               |

| ogram Memory Type        | FLASH                                                                          |

| PROM Size                | -                                                                              |

| M Size                   | 32K x 8                                                                        |

| ltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ta Converters            | A/D 48x10b                                                                     |

| cillator Type            | Internal                                                                       |

| erating Temperature      | -40°C ~ 85°C (TA)                                                              |

| ounting Type             | Surface Mount                                                                  |

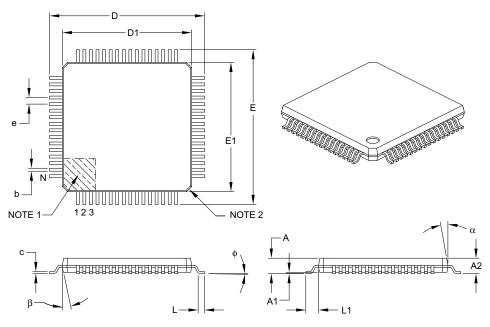

| ckage / Case             | 100-TQFP                                                                       |

| ipplier Device Package   | 100-TQFP (14x14)                                                               |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f256l-i-pf |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin N                  | umber             |             |                |                                   |

|----------|------------------------|-------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP   | Pin<br>Type | Buffer<br>Type | Description                       |

| RF0      | 58                     | 87                | I/O         | ST             |                                   |

| RF1      | 59                     | 88                | I/O         | ST             |                                   |

| RF2      | 34(3)                  | 52                | I/O         | ST             |                                   |

| RF3      | 33                     | 51                | I/O         | ST             |                                   |

| RF4      | 31                     | 49                | I/O         | ST             |                                   |

| RF5      | 32                     | 50                | I/O         | ST             | PORTF is a bidirectional I/O port |

| RF6      | 35 <sup>(1)</sup>      | 55 <sup>(1)</sup> | I/O         | ST             |                                   |

| RF7      | _                      | 54(4)             | I/O         | ST             |                                   |

| RF8      | _                      | 53                | I/O         | ST             |                                   |

| RF12     | _                      | 40                | I/O         | ST             |                                   |

| RF13     | _                      | 39                | I/O         | ST             |                                   |

| RG0      | _                      | 90                | I/O         | ST             |                                   |

| RG1      | _                      | 89                | I/O         | ST             |                                   |

| RG2      | 37(1)                  | 57 <sup>(1)</sup> | I/O         | ST             |                                   |

| RG3      | 36 <sup>(1)</sup>      | 56 <sup>(1)</sup> | I/O         | ST             |                                   |

| RG6      | 4                      | 10                | I/O         | ST             |                                   |

| RG7      | 5                      | 11                | I/O         | ST             | DODTO : hidira eti l 1/O et       |

| RG8      | 6                      | 12                | I/O         | ST             | PORTG is a bidirectional I/O port |

| RG9      | 8                      | 14                | I/O         | ST             |                                   |

| RG12     |                        | 96                | I/O         | ST             |                                   |

| RG13     | _                      | 97                | I/O         | ST             |                                   |

| RG14     | _                      | 95                | I/O         | ST             |                                   |

| RG15     | _                      | 1                 | I/O         | ST             |                                   |

| T1CK     | 48                     | 74                | ı           | ST             | Timer1 External Clock Input       |

| T2CK     | PPS                    | PPS               | I           | ST             | Timer2 External Clock Input       |

| T3CK     | PPS                    | PPS               | I           | ST             | Timer3 External Clock Input       |

| T4CK     | PPS                    | PPS               | I           | ST             | Timer4 External Clock Input       |

| T5CK     | PPS                    | PPS               | I           | ST             | Timer5 External Clock Input       |

| U1CTS    | PPS                    | PPS               | I           | ST             | UART1 Clear to Send               |

| U1RTS    | PPS                    | PPS               | 0           |                | UART1 Ready to Send               |

| U1RX     | PPS                    | PPS               | I           | ST             | UART1 Receive                     |

| U1TX     | PPS                    | PPS               | 0           | _              | UART1 Transmit                    |

| U2CTS    | PPS                    | PPS               | I           | ST             | UART2 Clear to Send               |

| U2RTS    | PPS                    | PPS               | 0           |                | UART2 Ready to Send               |

| U2RX     | PPS                    | PPS               | I           | ST             | UART2 Receive                     |

| U2TX     | PPS                    | PPS               | 0           | _              | UART2 Transmit                    |

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levelsAnalog = Analog input<br/>TTL = TTL input bufferI = Input<br/>P = Power

Note 1: This pin is only available on devices without a USB module.

- 2: This pin is only available on devices with a USB module.

- 3: This pin is not available on 64-pin devices with a USB module.

- **4:** This pin is only available on 100-pin devices without a USB module.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32  $^{\otimes}$  architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

TABLE 3-2: COPROCESSOR 0 REGISTERS

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.               |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.               |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration register 1.                                                |

| 16                 | Config2                 | Configuration register 2.                                                |

| 16                 | Config3                 | Configuration register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.               |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.               |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

**Note 1:** Registers used in exception processing.

2: Registers used during debug.

TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Intermed Course (1)                 | 100 # | Vector |               | Interru      | ıpt Bit Location |              | Persistent |

|-------------------------------------|-------|--------|---------------|--------------|------------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>     | IRQ#  | #      | Flag          | Enable       | Priority         | Sub-priority | Interrupt  |

|                                     | •     | Highe  | st Natural Or | der Priority |                  | <u> </u>     |            |

| CT – Core Timer Interrupt           | 0     | 0      | IFS0<0>       | IEC0<0>      | IPC0<4:2>        | IPC0<1:0>    | No         |

| CS0 – Core Software Interrupt 0     | 1     | 1      | IFS0<1>       | IEC0<1>      | IPC0<12:10>      | IPC0<9:8>    | No         |

| CS1 – Core Software Interrupt 1     | 2     | 2      | IFS0<2>       | IEC0<2>      | IPC0<20:18>      | IPC0<17:16>  | No         |

| INT0 – External Interrupt           | 3     | 3      | IFS0<3>       | IEC0<3>      | IPC0<28:26>      | IPC0<25:24>  | No         |

| T1 – Timer1                         | 4     | 4      | IFS0<4>       | IEC0<4>      | IPC1<4:2>        | IPC1<1:0>    | No         |

| IC1E – Input Capture 1 Error        | 5     | 5      | IFS0<5>       | IEC0<5>      | IPC1<12:10>      | IPC1<9:8>    | Yes        |

| IC1 – Input Capture 1               | 6     | 5      | IFS0<6>       | IEC0<6>      | IPC1<12:10>      | IPC1<9:8>    | Yes        |

| OC1 – Output Compare 1              | 7     | 6      | IFS0<7>       | IEC0<7>      | IPC1<20:18>      | IPC1<17:16>  | No         |

| INT1 – External Interrupt 1         | 8     | 7      | IFS0<8>       | IEC0<8>      | IPC1<28:26>      | IPC1<25:24>  | No         |

| T2 – Timer2                         | 9     | 8      | IFS0<9>       | IEC0<9>      | IPC2<4:2>        | IPC2<1:0>    | No         |

| IC2E – Input Capture 2              | 10    | 9      | IFS0<10>      | IEC0<10>     | IPC2<12:10>      | IPC2<9:8>    | Yes        |

| IC2 – Input Capture 2               | 11    | 9      | IFS0<11>      | IEC0<11>     | IPC2<12:10>      | IPC2<9:8>    | Yes        |

| OC2 – Output Compare 2              | 12    | 10     | IFS0<12>      | IEC0<12>     | IPC2<20:18>      | IPC2<17:16>  | No         |

| INT2 – External Interrupt 2         | 13    | 11     | IFS0<13>      | IEC0<13>     | IPC2<28:26>      | IPC2<25:24>  | No         |

| T3 – Timer3                         | 14    | 12     | IFS0<14>      | IEC0<14>     | IPC3<4:2>        | IPC3<1:0>    | No         |

| IC3E – Input Capture 3              | 15    | 13     | IFS0<15>      | IEC0<15>     | IPC3<12:10>      | IPC3<9:8>    | Yes        |

| IC3 – Input Capture 3               | 16    | 13     | IFS0<16>      | IEC0<16>     | IPC3<12:10>      | IPC3<9:8>    | Yes        |

| OC3 – Output Compare 3              | 17    | 14     | IFS0<17>      | IEC0<17>     | IPC3<20:18>      | IPC3<17:16>  | No         |

| INT3 – External Interrupt 3         | 18    | 15     | IFS0<18>      | IEC0<18>     | IPC3<28:26>      | IPC3<25:24>  | No         |

| T4 – Timer4                         | 19    | 16     | IFS0<19>      | IEC0<19>     | IPC4<4:2>        | IPC4<1:0>    | No         |

| IC4E – Input Capture 4 Error        | 20    | 17     | IFS0<20>      | IEC0<20>     | IPC4<12:10>      | IPC4<9:8>    | Yes        |

| IC4 – Input Capture 4               | 21    | 17     | IFS0<21>      | IEC0<21>     | IPC4<12:10>      | IPC4<9:8>    | Yes        |

| OC4 – Output Compare 4              | 22    | 18     | IFS0<22>      | IEC0<22>     | IPC4<20:18>      | IPC4<17:16>  | No         |

| INT4 – External Interrupt 4         | 23    | 19     | IFS0<23>      | IEC0<23>     | IPC4<28:26>      | IPC4<25:24>  | No         |

| T5 – Timer5                         | 24    | 20     | IFS0<24>      | IEC0<24>     | IPC5<4:2>        | IPC5<1:0>    | No         |

| IC5E – Input Capture 5 Error        | 25    | 21     | IFS0<25>      | IEC0<25>     | IPC5<12:10>      | IPC5<9:8>    | Yes        |

| IC5 – Input Capture 5               | 26    | 21     | IFS0<26>      | IEC0<26>     | IPC5<12:10>      | IPC5<9:8>    | Yes        |

| OC5 – Output Compare 5              | 27    | 22     | IFS0<27>      | IEC0<27>     | IPC5<20:18>      | IPC5<17:16>  | No         |

| AD1 – ADC1 Convert done             | 28    | 23     | IFS0<28>      | IEC0<28>     | IPC5<28:26>      | IPC5<25:24>  | Yes        |

| FSCM – Fail-Safe Clock Monitor      | 29    | 24     | IFS0<29>      | IEC0<29>     | IPC6<4:2>        | IPC6<1:0>    | No         |

| RTCC – Real-Time Clock and Calendar | 30    | 25     | IFS0<30>      | IEC0<30>     | IPC6<12:10>      | IPC6<9:8>    | No         |

| FCE – Flash Control Event           | 31    | 26     | IFS0<31>      | IEC0<31>     | IPC6<20:18>      | IPC6<17:16>  | No         |

| CMP1 – Comparator Interrupt         | 32    | 27     | IFS1<0>       | IEC1<0>      | IPC6<28:26>      | IPC6<25:24>  | No         |

| CMP2 – Comparator Interrupt         | 33    | 28     | IFS1<1>       | IEC1<1>      | IPC7<4:2>        | IPC7<1:0>    | No         |

| USB – USB Interrupts                | 34    | 29     | IFS1<2>       | IEC1<2>      | IPC7<12:10>      | IPC7<9:8>    | Yes        |

| SPI1E – SPI1 Fault                  | 35    | 30     | IFS1<3>       | IEC1<3>      | IPC7<20:18>      | IPC7<17:16>  | Yes        |

| SPI1RX – SPI1 Receive Done          | 36    | 30     | IFS1<4>       | IEC1<4>      | IPC7<20:18>      | IPC7<17:16>  | Yes        |

| SPI1TX – SPI1 Transfer Done         | 37    | 30     | IFS1<5>       | IEC1<5>      | IPC7<20:18>      | IPC7<17:16>  | Yes        |

| U1E – UART1 Fault                   | 38    | 31     | IFS1<6>       | IEC1<6>      | IPC7<28:26>      | IPC7<25:24>  | Yes        |

| U1RX – UART1 Receive Done           | 39    | 31     | IFS1<7>       | IEC1<7>      | IPC7<28:26>      | IPC7<25:24>  | Yes        |

| U1TX – UART1 Transfer Done          | 40    | 31     | IFS1<8>       | IEC1<8>      | IPC7<28:26>      | IPC7<25:24>  | Yes        |

| I2C1B – I2C1 Bus Collision Event    | 41    | 32     | IFS1<9>       | IEC1<9>      | IPC8<4:2>        | IPC8<1:0>    | Yes        |

| I2C1S - I2C1 Slave Event            | 42    | 32     | IFS1<10>      | IEC1<10>     | IPC8<4:2>        | IPC8<1:0>    | Yes        |

| I2C1M - I2C1 Master Event           | 43    | 32     | IFS1<11>      | IEC1<11>     | IPC8<4:2>        | IPC8<1:0>    | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

<sup>2:</sup> This interrupt source is not available on 64-pin devices.

REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | SUSPEND           | DMABUSY <sup>(1)</sup> | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: DMA On bit<sup>(1)</sup>

1 = DMA module is enabled0 = DMA module is disabled

bit 14-13 **Unimplemented:** Read as '0' bit 12 **SUSPEND:** DMA Suspend bit

1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

0 = DMA operates normally

bit 11 **DMABUSY:** DMA Module Busy bit<sup>(1)</sup>

1 = DMA module is active

0 = DMA module is disabled and not actively transferring data

bit 10-0 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

TABLE 11-14: PORTF REGISTER MAP FOR PIC32MX230F128H, PIC32MX530F128H, PIC32MX250F256H, PIC32MX550F256H, PIC32MX570F512H, AND PIC32MX570F512H DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |      | Bi   | ts   |      |              |              |              |      |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|--------------|--------------|--------------|------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5         | 20/4         | 19/3         | 18/2 | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | _     | l     | _     |       | _     |       | I    | 1    | _    |      | _            | I            |              | I    | _            | I            | 0000          |

| 0010                        | 114101                          | 15:0      | _     |       | _     | _     | _     | _     | _    |      | _    | _    | TRISF5       | TRISF4       | TRISF3       | _    | TRISF1       | TRISF0       | 003B          |

| 6520                        | PORTF                           | 31:16     | _     | _     | _     |       | _     | _     |      | _    |      | _    | _            | _            | _            |      | _            | _            | 0000          |

| 0020                        |                                 | 15:0      | _     | -     | _     | _     | _     | _     | -    | -    | _    | _    | RF5          | RF4          | RF3          | -    | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | _     | -     | _     | _     | _     | _     | -    | -    | _    | _    | _            | 1            | _            | -    | _            | ı            | 0000          |

| -                           |                                 | 15:0      | _     | -     | _     | _     | _     | _     | -    | -    | _    | _    | LATF5        | LATF4        | LATF3        | -    | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _            | _            | _            | _    | _            | _            | 0000          |

| 0010                        | 0001                            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | ODCF5        | ODCF4        | ODCF3        | _    | ODCF1        | ODCF0        | 0000          |

| 6550                        | CNPUF                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _            | _            | _            | _    | _            | _            | 0000          |

| 0000                        | 0111 01                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | CNPUF5       | CNPUF4       | CNPUF3       | _    | CNPUF1       | CNPUF0       | 0000          |

| 6560                        | CNPDF                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _            | _            | _            | _    | _            | _            | 0000          |

| 0000                        |                                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | CNPDF5       | CNPDF4       | CNPDF3       | _    | CNPDF1       | CNPDF0       | 0000          |

| 6570                        | CNCONF                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _            | _            | _            | _    | _            | _            | 0000          |

| 00.0                        |                                 | 15:0      | ON    | -     | SIDL  | _     | _     | _     | -    | -    | _    | _    | _            | -            | _            | -    | _            | -            | 0000          |

| 6580                        | CNENF                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _            | _            | _            | _    | _            | _            | 0000          |

| 0000                        |                                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | CNIEF5       | CNIEF4       | CNIEF3       | _    | CNIEF1       | CNIEF0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _            | _            | _            | _    | _            | _            | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | 1     | _     | 1     | _     | -     | 1    | -    | _    | 1    | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | -    | CN<br>STATF1 | CN<br>STATF0 | 0000          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

TABLE 11-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SS                          |                  |           |       | Bits  |       |       |       |       |      |      |      |      |      |      |      |       |          |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1     | 16/0 | All Resets |

| FAFC                        | U2CTSR           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| FA5C                        | 02C15R           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2CTS | R<3:0>   |      | 0000       |

| FA60                        | U3RXR            | 31:16     | -     | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | _    | -    | _     | _        | _    | 0000       |

| 1 A00                       | USINAN           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | U3RX  | R<3:0>   |      | 0000       |

| FA64                        | U3CTSR           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 1 A04                       | USCISK           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | U3CTS | R<3:0>   |      | 0000       |

| FA68                        | U4RXR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 1700                        | 0410/11          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U4RX  | R<3:0>   |      | 0000       |

| FA6C                        | U4CTSR           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 17.00                       | 0401010          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U4CTS | R<3:0>   |      | 0000       |

| FA70                        | U5RXR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 17170                       | COLOUIT          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U5RX  | R<3:0>   |      | 0000       |

| FA74                        | U5CTSR           | 31:16     | -     | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | _    | -    | _     | _        | _    | 0000       |

| 1707                        | 0001010          | 15:0      |       | _     |       |       | _     | _     |      | _    |      | _    | _    | _    |      | U5CTS | R<3:0>   | 1    | 0000       |

| FA84                        | SDI1R            | 31:16     |       | _     |       |       | _     | _     |      | _    |      | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 17101                       | OBITIC           | 15:0      | -     | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | _    |      | SDI1F | R<3:0>   |      | 0000       |

| FA88                        | SS1R             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 17100                       | OOTIV            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | SS1F  | R<3:0>   | 1    | 0000       |

| FA90                        | SDI2R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 17100                       | OBILIT           | 15:0      |       | _     |       |       | _     | _     |      | _    |      | _    | _    | _    |      | SDI2F | R<3:0>   | 1    | 0000       |

| FA94                        | SS2R             | 31:16     |       | _     |       |       | _     | _     |      | _    |      | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 17.01                       | OOLIK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | SS2F  | <3:0>    | 1    | 0000       |

| FA9C                        | SDI3R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _        | _    | 0000       |

|                             | 02.011           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | SDI3F | R<3:0>   | 1    | 0000       |

| FAA0                        | SS3R             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 17010                       | COURT            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | SS3F  | !<3:0>   | 1    | 0000       |

| FAA8                        | SDI4R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 17010                       | OBITIK           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | SDI4F | R<3:0>   | 1    | 0000       |

| FAAC                        | SS4R             | 31:16     | -     | _     | _     | -     | _     | _     | _    | _    | _    | _    | _    | _    | -    | _     | _        | _    | 0000       |

| 1,010                       | 004IX            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | SS4F  | <3:0>    |      | 0000       |

| FAC8                        | C1RXR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| 1 700                       | OHAN             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | C1RX  | R<3:0>   |      | 0000       |

| FAD0                        | REFCLKIR         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| ו אסט                       | INLI OLININ      | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | REFCL | (IR<3:0> |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                          |                  |           |       |       |       |       |       |       |      | Ві   | its  |      |      |      |      |      |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| FC04                        | RPG1R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FC84                        | RPGIR            | 15:0      | -     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPG1 | <3:0>  |      | 0000       |

| F000                        | DDOOD            | 31:16     | 1     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FC98                        | RPG6R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPG6 | <3:0>  |      | 0000       |

| FC0C                        | RPG7R            | 31:16     | -     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FC9C                        | RPG/R            | 15:0      | 1     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPG7 | '<3:0> |      | 0000       |

| F0.40                       | DDCOD            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FCAU                        | RPG8R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPG8 | 3:0>   |      | 0000       |

| FO.4.4                      | DDCCD            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FCA4                        | RPG9R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPG9 | <3:0>  |      | 0000       |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

### REGISTER 18-1: I2CxCON: I<sup>2</sup>C 'x' CONTROL REGISTER (CONTINUED)('x' = 1 AND 2)

- bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

- 1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)

- 0 = General call address disabled

- bit 6 **STREN:** SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with SCLREL bit.

- 1 = Enable software or receive clock stretching

- 0 = Disable software or receive clock stretching

- bit 5 **ACKDT:** Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive)

Value that is transmitted when the software initiates an Acknowledge sequence.

- 1 = Send NACK during Acknowledge

- 0 = Send ACK during Acknowledge

- bit 4 ACKEN: Acknowledge Sequence Enable bit

(when operating as I<sup>2</sup>C master, applicable during master receive)

- 1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence.

- 0 = Acknowledge sequence not in progress

- bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.

- 0 = Receive sequence not in progress

- bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.

- 0 = Stop condition not in progress

- bit 1 **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.

- 0 = Repeated Start condition not in progress

- bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.

- 0 = Start condition not in progress

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

```

WAITM<3:0>: Data Read/Write Strobe Wait States bits(1)

1111 = Wait of 16 TPB

0001 = Wait of 2 TPB

0000 = Wait of 1 TPB (default)

WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits(1)

bit 1-0

11 = Wait of 4 TPB

10 = Wait of 3 TPB

01 = Wait of 2 TPB

00 = Wait of 1 TPB (default)

For Read operations:

```

- 11 = Wait of 3 TPB

- 10 = Wait of 2 TPB

- 01 = Wait of 1 TPB

- 00 = Wait of 0 TPB (default)

- Note 1: Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

#### REGISTER 20-4: PMDOUT: PARALLEL PORT OUTPUT DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         |                   | DATAOUT<15:8>     |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | DATAOUT<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **DATAOUT<15:0>:** Port Data Output bits

This register is used for Read operations in the Enhanced Parallel Slave mode and Write operations for Dual Buffer Master mode.

In Dual Buffer Master mode, the DUALBUF bit (PMPCON<17>) = 1, a write to the MSB triggers the transaction on the PMP port. When MODE16 = 1, MSB = DATAOUT<15:8>. When MODE16 = 0, MSB = DATAOUT<7:0>.

**Note:** In Master mode, a read will return the last value written to the register. In Slave mode, a read will return indeterminate results.

#### REGISTER 20-5: PMDIN: PARALLEL PORT INPUT DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 |                  | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 13.6         |                   | DATAIN<15:8>      |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | DATAIN<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 DATAIN<15:0>: Port Data Input bits

This register is used for both Parallel Master Port mode and Enhanced Parallel Slave mode.

In Parallel Master mode, a write to the MSB triggers the write transaction on the PMP port. Similarly, a read to the MSB triggers the read transaction on the PMP port.

When MODE16 = 1, MSB = DATAIN<15:8>. When MODE16 = 0, MSB = DATAIN<7:0>.

Note: This register is not used in Dual Buffer Master mode (i.e., DUALBUF bit (PMPCON<17>) = 1).

#### **REGISTER 22-2:** AD1CON2: ADC CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 13.6         |                   | VCFG<2:0>         |                   | OFFCAL            | _                 | CSCNA             | _                | _                |

| 7:0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| BUFS —       |                   |                   |                   | SMP               | I<3:0>            |                   | BUFM             | ALTS             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVDD               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

bit 11 Unimplemented: Read as '0'

bit 10 **CSCNA:** Input Scan Select bit

1 = Scan inputs

0 = Do not scan inputs

bit 9-8 Unimplemented: Read as '0'

bit 7 BUFS: Buffer Fill Status bit Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

bit 6 Unimplemented: Read as '0'

bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence 1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

bit 1 BUFM: ADC Result Buffer Mode Select bit

1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

bit 0 **ALTS:** Alternate Input Sample Mode Select bit

> 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

0 = Always use Sample A input multiplexer settings

### 26.1 Control Registers

### TABLE 26-1: CTMU REGISTER MAP

| ess                      | _                               | ø         |         |         |          |       |         |          |          | Bits     |         |                             |        |       |      |      |      |       | S         |

|--------------------------|---------------------------------|-----------|---------|---------|----------|-------|---------|----------|----------|----------|---------|-----------------------------|--------|-------|------|------|------|-------|-----------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11   | 26/10    | 25/9     | 24/8     | 23/7    | 22/6                        | 21/5   | 20/4  | 19/3 | 18/2 | 17/1 | 16/0  | All Reset |

| A 200                    | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | EL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | DG2MOD EDG2POL EDG2SEL<3:0> |        |       |      | _    | _    | 0000  |           |

| A200                     | CTWOCON                         | 15:0      | ON      | _       | CTMUSIDL | TGEN  | EDGEN   | EDGSEQEN | IDISSEN  | CTTRIG   |         |                             | ITRIM: | <5:0> |      |      | IRNG | <1:0> | 0000      |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Bit<br>Range | Bit<br>31/23/15/7                     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|---------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | r-0                                   | r-1               | r-1               | R/P               | r-1               | r-1               | r-1              | R/P              |  |

| 31:24        | _                                     | _                 | -                 | CP                | _                 | _                 | _                | BWP              |  |

| 00:40        | r-1                                   | r-1               | r-1               | r-1               | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | _                                     | _                 | _                 | _                 |                   | PWP               | :9:6>            |                  |  |

| 45.0         | R/P                                   | R/P               | R/P               | R/P               | R/P               | R/P               | r-1              | r-1              |  |

| 15:8         |                                       | _                 | _                 |                   |                   |                   |                  |                  |  |

| 7.0          | r-1                                   | r-1               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 7:0          | — — ICESEL<1:0> JTAGEN <sup>(1)</sup> |                   |                   |                   |                   |                   | DEBU             | G<1:0>           |  |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 Reserved: Write '0' bit 30-29 Reserved: Write '1' bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external pro-

gramming device.

1 = Protection is disabled0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable0 = Boot Flash is not writable

bit 23-20 Reserved: Write '1'

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

### REGISTER 28-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

FPLLIDIV<2:0>: PLL Input Divider bits

111 = 12x divider

110 = 10x divider

101 = 6x divider

100 **= 5x divider**

011 = 4x divider

010 = 3x divider

001 = 2x divider

000 = 1x divider

Note 1: This bit is available on PIC32MX2XX/5XX devices only.

TABLE 31-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                                                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |      |         |                                                                                                          |                                                      |  |  |

|--------------------|--------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|---------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| DO 0117            |        |                                                                                                                |                                                                       |      | erature | $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                                                      |  |  |

| Param.             | Symbol | Characteristic                                                                                                 | Min.                                                                  | Тур. | Max.    | Units                                                                                                    | Conditions                                           |  |  |

| DO10               | Vol    | Output Low Voltage I/O Pins: 4x Sink Driver Pins - All I/O output pins not defined as 8x Sink Driver pins      | _                                                                     | _    | 0.4     | ٧                                                                                                        | IoL ≤ 9 mA, VDD = 3.3V                               |  |  |

| DO 10              | VOL    | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - RB14,<br>RC15, RD2, RD10, RD15, RF6,<br>RF13, RG6     | ı                                                                     | _    | 0.4     | >                                                                                                        | $IOL \le 15$ mA, $VDD = 3.3V$                        |  |  |

| DO20               | Vон    | Output High Voltage I/O Pins: 4x Source Driver Pins - All I/O output pins not defined as 8x Source Driver pins | 2.4                                                                   | _    | _       | >                                                                                                        | IOH ≥ -10 mA, VDD = 3.3V                             |  |  |

| DO20               | VOH    | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - RB14,<br>RC15, RD2, RD10, RD15, RF6,<br>RF13, RG6  | 2.4                                                                   |      |         | >                                                                                                        | IOH ≥ -15 mA, VDD = 3.3V                             |  |  |

|                    |        | Output High Voltage I/O Pins:                                                                                  | 1.5 <sup>(1)</sup>                                                    | _    | _       |                                                                                                          | IOH ≥ -14 mA, VDD = 3.3V                             |  |  |

|                    |        | 4x Source Driver Pins - All I/O                                                                                | 2.0 <sup>(1)</sup>                                                    | _    | _       | V                                                                                                        | IOH $\geq$ -12 mA, VDD = 3.3V                        |  |  |

| DO20A              | Voud   | output pins not defined as 8x Sink Driver pins                                                                 | 3.0 <sup>(1)</sup>                                                    |      | _       |                                                                                                          | $IOH \ge -7 \text{ mA}, VDD = 3.3V$                  |  |  |

| DOZUA              | VOHI   | Output High Voltage I/O Pins:                                                                                  | 1.5 <sup>(1)</sup>                                                    | _    | _       |                                                                                                          | IOH ≥ -22 mA, VDD = 3.3V                             |  |  |

|                    |        | 8x Source Driver Pins - RB14,                                                                                  | 2.0 <sup>(1)</sup>                                                    | _    | _       | V                                                                                                        | IOH ≥ -18 mA, VDD = 3.3V                             |  |  |

|                    |        | RC15, RD2, RD10, RD15, RF6,<br>RF13, RG6                                                                       | 3.0 <sup>(1)</sup>                                                    | _    | _       |                                                                                                          | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |  |  |

Note 1: Parameters are characterized, but not tested.

DS60001290D-page 316

**TABLE 31-17: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHA        | RACTER        | ISTICS                                                                                                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |             |            |                                         |  |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|-----------------------------------------|--|--|

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                           | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                              |  |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                                                                        | _                      | 40<br>40    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)           |  |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                                                                              | _                      | 10          | MHz        | XT (Note 4)                             |  |  |

| OS12          |               |                                                                                                                  | 4                                                                                                                                                                                                                                              | _                      | 10          | MHz        | XTPLL<br>(Notes 3,4)                    |  |  |

| OS13          |               |                                                                                                                  | 10                                                                                                                                                                                                                                             | _                      | 25          | MHz        | HS (Note 5)                             |  |  |

| OS14          |               |                                                                                                                  | 10                                                                                                                                                                                                                                             | _                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                    |  |  |

| OS15          |               |                                                                                                                  | 32                                                                                                                                                                                                                                             | 32.768                 | 100         | kHz        | Sosc (Note 4)                           |  |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                                                                                                                                                                                                              | _                      | _           | _          | See parameter<br>OS10 for Fosc<br>value |  |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                                                                                    | _                      | _           | ns         | EC (Note 4)                             |  |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | _                                                                                                                                                                                                                                              | _                      | 0.05 x Tosc | ns         | EC (Note 4)                             |  |  |

| OS40          | Tost          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                                                                              | 1024                   | _           | Tosc       | (Note 4)                                |  |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | _                                                                                                                                                                                                                                              | 2                      | _           | ms         | (Note 4)                                |  |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | _                                                                                                                                                                                                                                              | 12                     | _           | mA/V       | VDD = 3.3V,<br>TA = +25°C<br>(Note 4)   |  |  |

- Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

- 2: Instruction cycle period (TcY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- 3: PLL input requirements:  $4 \text{ MHz} \le \text{FPLLIN} \le 5 \text{ MHz}$  (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

- 4: This parameter is characterized, but not tested in manufacturing.

TABLE 31-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        | RACTER  | ISTICS          |                        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |        |                                |  |  |

|---------------|---------|-----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------------------------------|--|--|

| Param.<br>No. | Symbol  | Charact         | eristics               | Min. <sup>(1)</sup>                                                                                                                                                                                                                            | Max. | Units  | Conditions                     |  |  |

| IM10          | TLO:SCL | Clock Low Time  | 100 kHz mode           | TPB * (BRG + 2)                                                                                                                                                                                                                                | _    | — μs — |                                |  |  |

|               |         |                 | 400 kHz mode           | Трв * (BRG + 2)                                                                                                                                                                                                                                | _    | μS     | _                              |  |  |

|               |         |                 | 1 MHz mode (Note 2)    | Трв * (BRG + 2)                                                                                                                                                                                                                                | _    | μS     | _                              |  |  |

| IM11          | THI:SCL | Clock High Time | 100 kHz mode           | Трв * (BRG + 2)                                                                                                                                                                                                                                | _    | μS     | _                              |  |  |

|               |         |                 | 400 kHz mode           | Трв * (BRG + 2)                                                                                                                                                                                                                                | _    | μS     | _                              |  |  |

|               |         |                 | 1 MHz mode<br>(Note 2) | Трв * (BRG + 2)                                                                                                                                                                                                                                | _    | μS     | _                              |  |  |

| IM20          | TF:SCL  | SDAx and SCLx   | 100 kHz mode           | _                                                                                                                                                                                                                                              | 300  | ns     | CB is specified to be          |  |  |

|               |         | Fall Time       | 400 kHz mode           | 20 + 0.1 CB                                                                                                                                                                                                                                    | 300  | ns     | from 10 to 400 pF              |  |  |

|               |         |                 | 1 MHz mode<br>(Note 2) | _                                                                                                                                                                                                                                              | 100  | ns     |                                |  |  |

| IM21          | TR:SCL  | SDAx and SCLx   | 100 kHz mode           | _                                                                                                                                                                                                                                              | 1000 | ns     | CB is specified to be          |  |  |

|               |         | Rise Time       | 400 kHz mode           | 20 + 0.1 Св                                                                                                                                                                                                                                    | 300  | ns     | from 10 to 400 pF              |  |  |

|               |         |                 | 1 MHz mode (Note 2)    | _                                                                                                                                                                                                                                              | 300  | ns     |                                |  |  |

| IM25          | TSU:DAT | Data Input      | 100 kHz mode           | 250                                                                                                                                                                                                                                            | _    | ns     | _                              |  |  |

|               |         | Setup Time      | 400 kHz mode           | 100                                                                                                                                                                                                                                            | _    | ns     |                                |  |  |

|               |         |                 | 1 MHz mode (Note 2)    | 100                                                                                                                                                                                                                                            | _    | ns     |                                |  |  |

| IM26          | THD:DAT | Data Input      | 100 kHz mode           | 0                                                                                                                                                                                                                                              | _    | μS     | _                              |  |  |