Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f256lt-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

64

1

64

#### TABLE 3: **PIN NAMES FOR 64-PIN USB DEVICES**

64-PIN QFN<sup>(4)</sup> AND TQFP (TOP VIEW)

PIC32MX230F128H PIC32MX530F128H PIC32MX250F256H PIC32MX550F256H PIC32MX270F512H PIC32MX570F512H

|       |                                           | QF | N <sup>(4)</sup> | TQFP                  |

|-------|-------------------------------------------|----|------------------|-----------------------|

| Pin # | Full Pin Name                             | Pi | in #             | Full Pin Name         |

| 1     | AN22/RPE5/PMD5/RE5                        | 3  | 33               | USBID/RPF3/RF3        |

| 2     | AN23/PMD6/RE6                             | 3  | 34               | VBUS                  |

| 3     | AN27/PMD7/RE7                             | 3  | 35               | VUSB3V3               |

| 4     | AN16/C1IND/RPG6/SCK2/PMA5/RG6             | 3  | 36               | D-                    |

| 5     | AN17/C1INC/RPG7/PMA4/RG7                  | 3  | 37               | D+                    |

| 6     | AN18/C2IND/RPG8/PMA3/RG8                  | 3  | 38               | VDD                   |

| 7     | MCLR                                      | 3  | 39               | OSC1/CLKI/RC12        |

| 8     | AN19/C2INC/RPG9/PMA2/RG9                  | 4  | 40               | OSC2/CLKO/RC15        |

| 9     | Vss                                       | 4  | 41               | Vss                   |

| 10    | Vdd                                       | 4  | 42               | RPD8/RTCC/RD8         |

| 11    | AN5/C1INA/RPB5/VBUSON/RB5                 | 4  | 43               | RPD9/SDA1/RD9         |

| 12    | AN4/C1INB/RB4                             | 4  | 44               | RPD10/SCL1/PMA15/RD10 |

| 13    | PGED3/AN3/C2INA/RPB3/RB3                  | 4  | 45               | RPD11/PMA14/RD11      |

| 14    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2     | 4  | 46               | RPD0/INT0/RD0         |

| 15    | PGEC1/VREF-/AN1/RPB1/CTED12/RB1           | 4  | 47               | SOSCI/RPC13/RC13      |

| 16    | PGED1/VREF+/AN0/RPB0/PMA6/RB0             | 4  | 48               | SOSCO/RPC14/T1CK/RC14 |

| 17    | PGEC2/AN6/RPB6/RB6                        | 4  | 49               | AN24/RPD1/RD1         |

| 18    | PGED2/AN7/RPB7/CTED3/RB7                  | 5  | 50               | AN25/RPD2/SCK1/RD2    |

| 19    | AVDD                                      | 5  | 51               | AN26/C3IND/RPD3/RD3   |

| 20    | AVss                                      | 5  | 52               | RPD4/PMWR/RD4         |

| 21    | AN8/RPB8/CTED10/RB8                       | 5  | 53               | RPD5/PMRD/RD5         |

| 22    | AN9/RPB9/CTED4/PMA7/RB9                   | 5  | 54               | C3INC/RD6             |

| 23    | TMS/CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 5  | 55               | C3INB/RD7             |

| 24    | TDO/AN11/PMA12/RB11                       | 5  | 56               | VCAP                  |

| 25    | Vss                                       | 5  | 57               | VDD                   |

| 26    | Vdd                                       | 5  | 58               | C3INA/RPF0/RF0        |

| 27    | TCK/AN12/PMA11/RB12                       | 5  | 59               | RPF1/RF1              |

| 28    | TDI/AN13/PMA10/RB13                       | e  | 60               | PMD0/RE0              |

| 29    | AN14/RPB14/SCK3/CTED5/PMA1/RB14           | 6  | 61               | PMD1/RE1              |

| 30    | AN15/RPB15/OCFB/CTED6/PMA0/RB15           | 6  | 62               | AN20/PMD2/RE2         |

| 31    | RPF4/SDA2/PMA9/RF4                        | 6  | 63               | RPE3/CTPLS/PMD3/RE3   |

| 32    | RPF5/SCL2/PMA8/RF5                        | 6  | 64               | AN21/PMD4/RE4         |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 11.0 "I/O Ports" for more information. 2: 3: Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

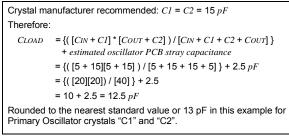

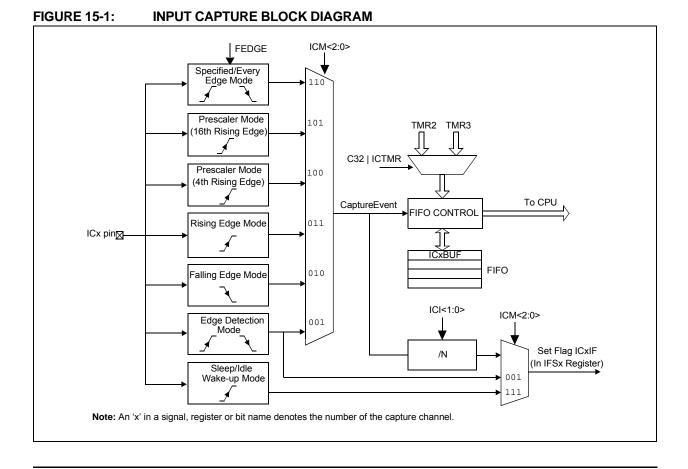

### 2.7.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following examples are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

### EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to  $\sim$ VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with  $\leq$  1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

2.7.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | ROTRIN            | √<8:1>            |                   |                  |                  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 |                   | —                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 | _                 | _                 | _                 | _                 |                  | —                |

### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

| Legend:           | y = Value set from Config | uration bits on POR      |                    |

|-------------------|---------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

**Note:** While the ON bit (REFOCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

| KE0131       | EK 10-1.          |                   |                   | ILKNUFI           | JIATUS KE         | GIGTER            |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | —                 |                   | -                 | _                 | -                | —                |

| 7.0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |

## REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable   | bit                |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIF: ID State Change Indicator bit

- 1 = Change in ID state detected

- 0 = No change in ID state detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1millisecond, but different from last time

- 0 = USB line state has not been stable for 1 millisecond

#### bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = Change on the session valid input detected

- 0 = No change on the session valid input detected

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | -                 |                   | _                 | -                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | -                 |                   | _                 | -                 | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | _                 | -                 |                   | _                 | -                 |                  | _                |

| 7.0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7:0          | ID                | —                 | LSTATE            | _                 | SESVD             | SESEND            |                  | VBUSVD           |

## REGISTER 10-3: U1OTGSTAT: USB OTG STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a Type-B cable has been plugged into the USB receptacle

- 0 = A Type-A cable has been plugged into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has been stable for the previous 1 ms

- 0 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has not been stable for the previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 **SESEND:** B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet rejected due to CRC5 error

- 0 = Token packet accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = EOF error condition detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check failed

- 0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

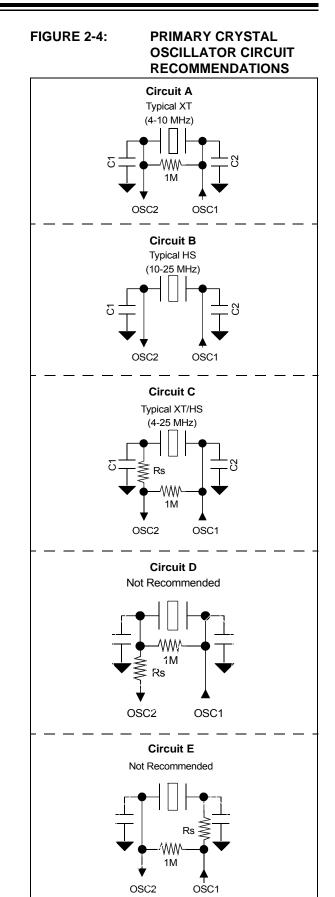

## 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a freerunning interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

## FIGURE 12-1: TIMER1 BLOCK DIAGRAM

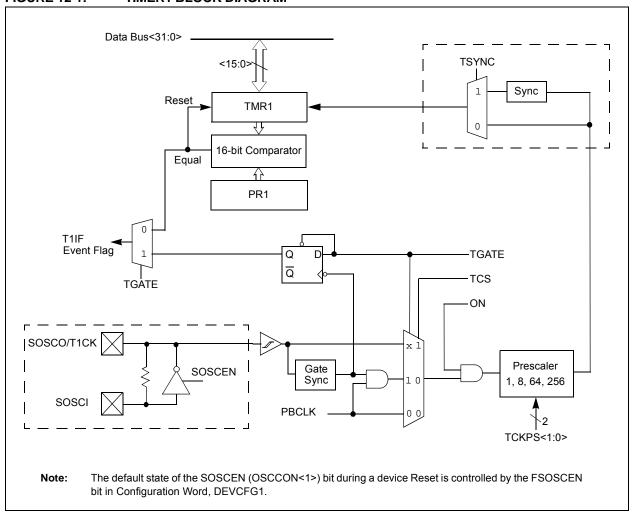

## 15.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 15. "Input Capture"** (DS60001122) of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

The other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

## 16.1 Control Registers

## TABLE 16-1: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |       |       |       |       |       |       |      | Bi    | its     |      |      |       |        |      |          |      |              |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|-------|-------|------|-------|---------|------|------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7    | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16         | —     | —     | —     | —     | —     | —     | —    | —     | —       | _    | _    | —     | —      | _    | —        |      | 0000         |

| 3000                        |                                 | 15:0          | ON    | —     | SIDL  | —     | —     | —     | —    | —     | —       | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3010                        | OC1R                            | 31:16<br>15:0 |       |       |       |       |       |       |      | OC1R  | <31:0>  |      |      |       |        |      |          |      | xxxx<br>xxxx |

| 3020                        | OC1RS                           | 31:16<br>15:0 |       |       |       |       |       |       |      | OC1RS | 6<31:0> |      |      |       |        |      |          |      | xxxx<br>xxxx |

|                             |                                 | 31:16         | _     | _     | _     | _     | _     | —     | —    | —     | _       | _    | _    | _     | _      | _    | _        | _    | 0000         |

| 3200                        | OC2CON                          | 15:0          | ON    | _     | SIDL  | _     | _     | _     | _    | _     | _       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

|                             |                                 | 31:16         |       |       |       |       |       |       |      |       |         |      |      |       |        |      |          |      | xxxx         |

| 3210                        | OC2R                            | 15:0          |       |       |       |       |       |       |      | OC2R  | <31:0>  |      |      |       |        |      |          |      | xxxx         |

|                             |                                 | 31:16         |       |       |       |       |       |       |      |       |         |      |      |       |        |      |          |      | xxxx         |

| 3220                        | OC2RS                           | 15:0          |       |       |       |       |       |       |      | OC2RS | 6<31:0> |      |      |       |        |      |          |      | xxxx         |

|                             |                                 | 31:16         |       | _     | _     | _     | _     | _     |      | _     | _       |      |      | _     | _      | _    | _        | _    | 0000         |

| 3400                        | OC3CON                          | 15:0          | ON    | _     | SIDL  | _     | _     | _     | _    | _     | _       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 0.440                       | 0.000                           | 31:16         |       |       |       |       |       |       |      | 0.000 | -0.1.0: |      |      |       |        |      |          |      | xxxx         |

| 3410                        | OC3R                            | 15:0          |       |       |       |       |       |       |      | OC3R  | <31:0>  |      |      |       |        |      |          |      | xxxx         |

| 3420                        | OC3RS                           | 31:16         |       |       |       |       |       |       |      | OC3R5 | 221.05  |      |      |       |        |      |          |      | xxxx         |

| 3420                        | UCSRS                           | 15:0          |       |       |       |       |       |       |      | UCSRE | 5<31.0> |      |      |       |        |      |          |      | xxxx         |

| 3600                        | OC4CON                          | 31:16         | _     | —     | _     | —     | —     | —     | —    | —     | _       | —    | —    | —     | —      |      | —        |      | 0000         |

| 3000                        | 004001                          | 15:0          | ON    | _     | SIDL  | _     | _     | _     | -    | _     | _       | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3610                        | OC4R                            | 31:16         |       |       |       |       |       |       |      | OC4R  | ~31.0>  |      |      |       |        |      |          |      | xxxx         |

| 3010                        | 0040                            | 15:0          |       |       |       |       |       |       |      | 0040  | <31.02  |      |      |       |        |      |          |      | xxxx         |

| 3620                        | OC4RS                           | 31:16         |       |       |       |       |       |       |      | OC4RS | 2<31.05 |      |      |       |        |      |          |      | xxxx         |

| 3020                        | 00403                           | 15:0          |       | -     |       | -     | -     | -     | -    | 00400 | 5-51.0- | -    |      |       | -      |      |          |      | xxxx         |

| 3800                        | OC5CON                          | 31:16         | —     | —     | —     | —     | —     |       |      |       | —       | —    | —    |       | —      |      | —        | —    | 0000         |

| 5000                        | 00000                           | 15:0          | ON    | —     | SIDL  | _     | —     | _     | —    | _     | —       |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3810                        | OC5R                            | 31:16         |       |       |       |       |       |       |      | OC5R  | <31.0>  |      |      |       |        |      |          |      | xxxx         |

| 3010                        | 0001                            | 15:0          |       |       |       |       |       |       |      | 0000  | -01.04  |      |      |       |        |      |          |      | xxxx         |

| 3820                        | OC5RS                           | 31:16         |       |       |       |       |       |       |      | 00589 | S<31:0> |      |      |       |        |      |          |      | xxxx         |

| 0020                        | 000100                          | 15:0          |       |       |       |       |       |       |      | OUSKE | -01.0-  |      |      |       |        |      |          |      | xxxx         |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

NOTES:

## 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

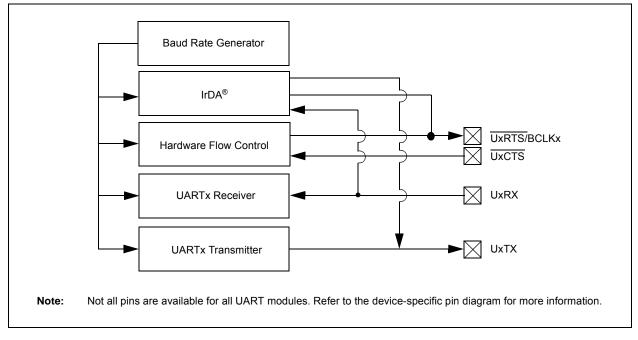

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX/5XX 64/100-pin family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, odd or no parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9<sup>th</sup> bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART.

#### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | FLTEN11           | MSEL1             | 1<1:0>            | FSEL11<4:0>       |                   |                   |                  |                  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN10           | MSEL1             | 0<1:0>            | FSEL10<4:0>       |                   |                   |                  |                  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN9            | MSEL              | 9<1:0>            | FSEL9<4:0>        |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN8            | MSEL              | 8<1:0>            | FSEL8<4:0>        |                   |                   |                  |                  |  |

### REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN11: Filter 11 Enable bit                                      |

|-----------|--------------------------------------------------------------------|

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 30-29 | MSEL11<1:0>: Filter 11 Mask Select bits                            |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| h:+ 00 04 |                                                                    |

| bit 28-24 |                                                                    |

|           | 11111 = Reserved                                                   |

|           | •                                                                  |

|           | •                                                                  |

|           | 10000 = Reserved                                                   |

|           | 01111 = Message matching filter is stored in FIFO buffer 15        |

|           | •                                                                  |

|           |                                                                    |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

| bit 23    | FLTEN10: Filter 10 Enable bit                                      |

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 22-21 | MSEL10<1:0>: Filter 10 Mask Select bits                            |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected                                    |

|           | 00 = Acceptance Mask 0 selected                                    |

|           |                                                                    |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

NOTES:

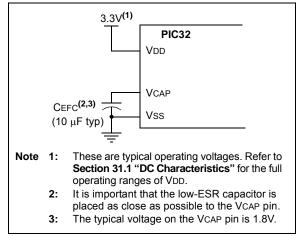

## 28.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX/5XX 64/100-pin devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX/5XX 64/100-pin family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 28-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 31.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

### 28.3.1 HIGH VOLTAGE DETECT (HVD)

The HVD module monitors the core voltage at the VCAP pin. If a voltage above the required level is detected on VCAP, the I/O pins are disabled and the device is held in Reset as long as the HVD condition persists. See parameter HV10 (VHVD) in Table 31-11 in **Section 31.1** "**DC Characteristics**" for more information.

#### 28.3.2 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

#### 28.3.3 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX/5XX 64/100-pin devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 31.1 "DC Characteristics"**.

## FIGURE 28-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

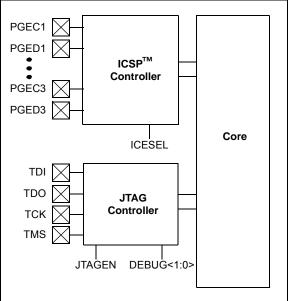

## 28.4 Programming and Diagnostics

PIC32MX1XX/2XX/5XX 64/100-pin devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- · Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules that provide a range of functions to the application developer.

#### BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE PORTS

## 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

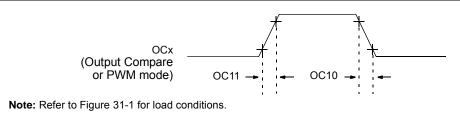

## FIGURE 31-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

## TABLE 31-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |                        |      |       |                    |

|--------------------|--------|-------------------------------------------------------|------|------------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>                        | Min. | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| OC10               | TccF   | OCx Output Fall Time                                  | —    | —                      | _    | ns    | See parameter DO32 |

| OC11               | TccR   | OCx Output Rise Time                                  | —    | —                      | —    | ns    | See parameter DO31 |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

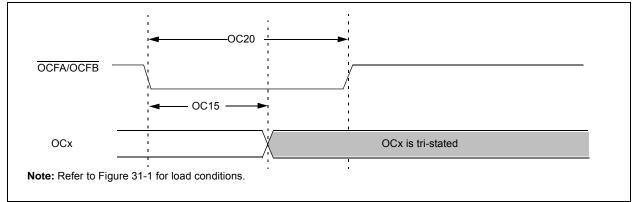

#### FIGURE 31-9: OCx/PWM MODULE TIMING CHARACTERISTICS

### TABLE 31-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |     |                        |     |       |            |

|--------------------|--------|----------------------------------------------------------|-----|------------------------|-----|-------|------------|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup>                           | Min | Typical <sup>(2)</sup> | Max | Units | Conditions |

| OC15               | Tfd    | Fault Input to PWM I/O Change                            | —   | —                      | 50  | ns    | _          |

| OC20               | TFLT   | Fault Input Pulse Width                                  | 50  | —                      |     | ns    | —          |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHARACTERISTICS |         |                            |                               |      |       |            |                           |  |

|--------------------|---------|----------------------------|-------------------------------|------|-------|------------|---------------------------|--|

| Param.<br>No.      | Symbol  | Charact                    | Min.                          | Max. | Units | Conditions |                           |  |

| IS34               | THD:STO | Stop Condition             | 100 kHz mode                  | 4000 | _     | ns         | —                         |  |

|                    |         | Hold Time                  | 400 kHz mode                  | 600  | —     | ns         |                           |  |

|                    |         |                            | 1 MHz mode<br>(Note 1)        | 250  |       | ns         |                           |  |

| IS40               | TAA:SCL | Output Valid from<br>Clock | 100 kHz mode                  | 0    | 3500  | ns         | —                         |  |

|                    |         |                            | 400 kHz mode                  | 0    | 1000  | ns         |                           |  |

|                    |         |                            | 1 MHz mode<br><b>(Note 1)</b> | 0    | 350   | ns         |                           |  |

| IS45               | Tbf:sda | A Bus Free Time            | 100 kHz mode                  | 4.7  | —     | μs         | The amount of time the bu |  |

|                    |         |                            | 400 kHz mode                  | 1.3  |       | μS         | must be free before a new |  |

|                    |         |                            | 1 MHz mode<br><b>(Note 1)</b> | 0.5  | -     | μS         | transmission can start    |  |

| IS50               | Св      | Bus Capacitive Loading     |                               |      | 400   | pF         | —                         |  |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

#### TABLE 31-34: ADC MODULE SPECIFICATIONS

|               |            | ACTERISTICS                                          | (unless oth                       | erwise sta  | ted)                              |          | e 5): 2.5V to 3.6V                                                                            |

|---------------|------------|------------------------------------------------------|-----------------------------------|-------------|-----------------------------------|----------|-----------------------------------------------------------------------------------------------|

|               |            | ACTERISTICS                                          | Operating te                      | emperature  | C for Industrial<br>°C for V-temp |          |                                                                                               |

| Param.<br>No. | Symbol     | Characteristics                                      | Min.                              | Typical     | Max.                              | Units    | Conditions                                                                                    |

| Device        | Supply     |                                                      |                                   |             |                                   |          |                                                                                               |

| AD01          | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5 | —           | Lesser of<br>VDD + 0.3 or<br>3.6  | V        | _                                                                                             |

| AD02          | AVss       | Module Vss Supply                                    | Vss                               | _           | AVdd                              | V        | (Note 1)                                                                                      |

| Referen       | ce Inputs  |                                                      |                                   |             |                                   |          |                                                                                               |

| AD05<br>AD05a | Vrefh      | Reference Voltage High                               | AVss + 2.0<br>2.5                 | _           | AVDD<br>3.6                       | V<br>V   | (Note 1)<br>VREFH = AVDD (Note 3)                                                             |

| AD06          | Vrefl      | Reference Voltage Low                                | AVss                              | —           | Vrefh – 2.0                       | V        | (Note 1)                                                                                      |

| AD07          | Vref       | Absolute Reference<br>Voltage (VREFH – VREFL)        | 2.0                               | —           | AVDD                              | V        | (Note 3)                                                                                      |

| AD08<br>AD08a | IREF       | Current Drain                                        |                                   | 250<br>—    | 400<br>3                          | μΑ<br>μΑ | ADC operating<br>ADC off                                                                      |

| Analog        | Input      |                                                      |                                   |             |                                   |          | ·                                                                                             |

| AD12          | VINH-VINL  | Full-Scale Input Span                                | VREFL                             | —           | Vrefh                             | V        | —                                                                                             |

| AD13          | VINL       | Absolute VINL Input<br>Voltage                       | AVss – 0.3                        | —           | AVDD/2                            | V        | _                                                                                             |

| AD14          | Vin        | Absolute Input Voltage                               | AVss - 0.3                        | _           | AVDD + 0.3                        | V        | —                                                                                             |

| AD15          | _          | Leakage Current                                      | —                                 | ±0.001      | ±0.610                            | μA       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = $3.3V$<br>Source Impedance = $10 \text{ k}\Omega$ |

| AD17          | RIN        | Recommended<br>Impedance of Analog<br>Voltage Source | —                                 | _           | 5k                                | Ω        | (Note 1)                                                                                      |

| ADC Ac        | curacy – N | leasurements with Exte                               | rnal VREF+/V                      | REF-        |                                   |          |                                                                                               |

| AD20c         | Nr         | Resolution                                           |                                   | 10 data bit | S                                 | bits     | _                                                                                             |

| AD21c         | INL        | Integral Non-linearity                               | > -1                              | —           | < 1                               | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |

| AD22c         | DNL        | Differential Non-linearity                           | > -1                              | _           | < 1                               | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V<br>(Note 2)                                  |

| AD23c         | Gerr       | Gain Error                                           | > -1                              | _           | < 1                               | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.3V                                              |

| AD24c         | Eoff       | Offset Error                                         | > -1                              | _           | < 1                               | Lsb      | VINL = AVSS = 0V,<br>AVDD = 3.3V                                                              |

| AD25c         | _          | Monotonicity                                         | _                                 | _           | _                                 | _        | Guaranteed                                                                                    |

Note 1: These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

**3:** These parameters are characterized, but not tested in manufacturing.

4: Characterized with a 1 kHz sine wave.

**5:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

#### w

| WWW Address          | 377 |

|----------------------|-----|

| WWW, On-Line Support | 9   |