Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

| Core Processor            | MIPS32® M4K™                                                                    |

| Core Size                 | 32-Bit Single-Core                                                              |

| Speed                     | 40MHz                                                                           |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O             | 81                                                                              |

| Program Memory Size       | 256KB (256K x 8)                                                                |

| rogram Memory Type        | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| AM Size                   | 32K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| ata Converters            | A/D 48x10b                                                                      |

| scillator Type            | Internal                                                                        |

| perating Temperature      | -40°C ~ 105°C (TA)                                                              |

| lounting Type             | Surface Mount                                                                   |

| ackage / Case             | 100-TQFP                                                                        |

| upplier Device Package    | 100-TQFP (14x14)                                                                |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx250f256lt-v-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 5: PIN NAMES FOR 100-PIN USB DEVICES

100-PIN TQFP (TOP VIEW)

PIC32MX230F128L PIC32MX530F128L PIC32MX250F256L PIC32MX550F256L PIC32MX270F512L PIC32MX570F512L

100

1

| Pin# | Full Pin Name                         |

|------|---------------------------------------|

| 1    | AN28/RG15                             |

| 2    | VDD                                   |

| 3    | AN22/RPE5/PMD5/RE5                    |

| 4    | AN23/PMD6/RE6                         |

| 5    | AN27/PMD7/RE7                         |

| 6    | AN29/RPC1/RC1                         |

| 7    | AN30/RPC2/RC2                         |

| 8    | AN31/RPC3/RC3                         |

| 9    | RPC4/CTED7/RC4                        |

| 10   | AN16/C1IND/RPG6/SCK2/PMA5/RG6         |

| 11   | AN17/C1INC/RPG7/PMA4/RG7              |

| 12   | AN18/C2IND/RPG8/PMA3/RG8              |

| 13   | MCLR                                  |

| 14   | AN19/C2INC/RPG9/PMA2/RG9              |

| 15   | Vss                                   |

| 16   | VDD                                   |

| 17   | TMS/CTED1/RA0                         |

| 18   | AN32/RPE8/RE8                         |

| 19   | AN33/RPE9/RE9                         |

| 20   | AN5/C1INA/RPB5/VBuson/RB5             |

| 21   | AN4/C1INB/RB4                         |

| 22   | PGED3/AN3/C2INA/RPB3/RB3              |

| 23   | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 |

| 24   | PGEC1/AN1/RPB1/CTED12/RB1             |

| 25   | PGED1/AN0/RPB0/RB0                    |

| 26   | PGEC2/AN6/RPB6/RB6                    |

| 27   | PGED2/AN7/RPB7/CTED3/RB7              |

| 28   | VREF-/PMA7/RA9                        |

| 29   | VREF+/PMA6/RA10                       |

| 30   | AVDD                                  |

| 31   | AVss                                  |

| 32   | AN8/RPB8/CTED10/RB8                   |

| 33   | AN9/RPB9/CTED4/RB9                    |

| 34   | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| 35   | AN11/PMA12/RB11                       |

| Pin # | Full Bin Name                   |

|-------|---------------------------------|

|       | Full Pin Name                   |

| 36    | Vss                             |

| 37    | VDD                             |

| 38    | TCK/CTED2/RA1                   |

| 39    | AN34/RPF13/SCK3/RF13            |

| 40    | AN35/RPF12/RF12                 |

| 41    | AN12/PMA11/RB12                 |

| 42    | AN13/PMA10/RB13                 |

| 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 45    | Vss                             |

| 46    | VDD                             |

| 47    | AN36/RPD14/RD14                 |

| 48    | AN37/RPD15/SCK4/RD15            |

| 49    | RPF4/PMA9/RF4                   |

| 50    | RPF5/PMA8/RF5                   |

| 51    | USBID/RPF3/RF3                  |

| 52    | AN38/RPF2/RF2                   |

| 53    | AN39/RPF8/RF8                   |

| 54    | VBUS                            |

| 55    | VUSB3V3                         |

| 56    | D-                              |

| 57    | D+                              |

| 58    | SCL2/RA2                        |

| 59    | SDA2/RA3                        |

| 60    | TDI/CTED9/RA4                   |

| 61    | TDO/RA5                         |

| 62    | VDD                             |

| 63    | OSC1/CLKI/RC12                  |

| 64    | OSC2/CLKO/RC15                  |

| 65    | Vss                             |

| 66    | RPA14/SCL1/RA14                 |

| 67    | RPA15/SDA1/RA15                 |

| 68    | RPD8/RTCC/RD8                   |

| 69    | RPD9/RD9                        |

| 70    | RPD10/SCK1/PMA15/RD10           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS

|          | Pin N                  | umber           |             |                |                        |

|----------|------------------------|-----------------|-------------|----------------|------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description            |

| AN0      | 16                     | 25              | Ι           | Analog         |                        |

| AN1      | 15                     | 24              | I           | Analog         |                        |

| AN2      | 14                     | 23              | I           | Analog         |                        |

| AN3      | 13                     | 22              | I           | Analog         |                        |

| AN4      | 12                     | 21              | I           | Analog         |                        |

| AN5      | 11                     | 20              | I           | Analog         |                        |

| AN6      | 17                     | 26              | I           | Analog         |                        |

| AN7      | 18                     | 27              | I           | Analog         |                        |

| AN8      | 21                     | 32              | I           | Analog         |                        |

| AN9      | 22                     | 33              | I           | Analog         |                        |

| AN10     | 23                     | 34              | I           | Analog         |                        |

| AN11     | 24                     | 35              | I           | Analog         |                        |

| AN12     | 27                     | 41              | I           | Analog         |                        |

| AN13     | 28                     | 42              | I           | Analog         |                        |

| AN14     | 29                     | 43              | I           | Analog         |                        |

| AN15     | 30                     | 44              | I           | Analog         |                        |

| AN16     | 4                      | 10              | I           | Analog         |                        |

| AN17     | 5                      | 11              | I           | Analog         | Analas innut shannala  |

| AN18     | 6                      | 12              | I           | Analog         | Analog input channels. |

| AN19     | 8                      | 14              | I           | Analog         |                        |

| AN20     | 62                     | 98              | I           | Analog         |                        |

| AN21     | 64                     | 100             | I           | Analog         |                        |

| AN22     | 1                      | 3               | I           | Analog         |                        |

| AN23     | 2                      | 4               | I           | Analog         |                        |

| AN24     | 49                     | 76              | I           | Analog         |                        |

| AN25     | 50                     | 77              | I           | Analog         |                        |

| AN26     | 51                     | 78              | I           | Analog         |                        |

| AN27     | 3                      | 5               | I           | Analog         |                        |

| AN28     |                        | 1               | I           | Analog         |                        |

| AN29     | _                      | 6               | I           | Analog         |                        |

| AN30     |                        | 7               | I           | Analog         |                        |

| AN31     |                        | 8               | I           | Analog         |                        |

| AN32     |                        | 18              | I           | Analog         |                        |

| AN33     |                        | 19              | I           | Analog         |                        |

| AN34     |                        | 39              | I           | Analog         |                        |

| AN35     | _                      | 40              | I           | Analog         |                        |

Legend: CMOS = CMOS compatible input or output Analog = Analog input I = Input O = Output ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = Power

Note 1: This pin is only available on devices without a USB module.

- 2: This pin is only available on devices with a USB module.

- 3: This pin is not available on 64-pin devices with a USB module.

- **4:** This pin is only available on 100-pin devices without a USB module.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin N                                 | umber                                 |             |                |                                   |

|----------|---------------------------------------|---------------------------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP                | 100-pin<br>TQFP                       | Pin<br>Type | Buffer<br>Type | Description                       |

| INT0     | 35 <sup>(1)</sup> , 46 <sup>(2)</sup> | 55 <sup>(1)</sup> , 72 <sup>(2)</sup> | I           | ST             | External Interrupt 0              |

| INT1     | PPS                                   | PPS                                   | - 1         | ST             | External Interrupt 1              |

| INT2     | PPS                                   | PPS                                   | I           | ST             | External Interrupt 2              |

| INT3     | PPS                                   | PPS                                   | - 1         | ST             | External Interrupt 3              |

| INT4     | PPS                                   | PPS                                   | - 1         | ST             | External Interrupt 4              |

| RA0      | _                                     | 17                                    | I/O         | ST             |                                   |

| RA1      | _                                     | 38                                    | I/O         | ST             |                                   |

| RA2      | _                                     | 58                                    | I/O         | ST             |                                   |

| RA3      | _                                     | 59                                    | I/O         | ST             |                                   |

| RA4      | _                                     | 60                                    | I/O         | ST             |                                   |

| RA5      | _                                     | 61                                    | I/O         | ST             | DODTA is a little discussion of   |

| RA6      | _                                     | 91                                    | I/O         | ST             | PORTA is a bidirectional I/O port |

| RA7      | _                                     | 92                                    | I/O         | ST             |                                   |

| RA9      | _                                     | 28                                    | I/O         | ST             |                                   |

| RA10     | _                                     | 29                                    | I/O         | ST             |                                   |

| RA14     | _                                     | 66                                    | I/O         | ST             |                                   |

| RA15     | _                                     | 67                                    | I/O         | ST             |                                   |

| RB0      | 16                                    | 25                                    | I/O         | ST             |                                   |

| RB1      | 15                                    | 24                                    | I/O         | ST             |                                   |

| RB2      | 14                                    | 23                                    | I/O         | ST             |                                   |

| RB3      | 13                                    | 22                                    | I/O         | ST             |                                   |

| RB4      | 12                                    | 21                                    | I/O         | ST             |                                   |

| RB5      | 11                                    | 20                                    | I/O         | ST             |                                   |

| RB6      | 17                                    | 26                                    | I/O         | ST             |                                   |

| RB7      | 18                                    | 27                                    | I/O         | ST             | DODTE: 1 : i' i' 1 / O 1          |

| RB8      | 21                                    | 32                                    | I/O         | ST             | PORTB is a bidirectional I/O port |

| RB9      | 22                                    | 33                                    | I/O         | ST             |                                   |

| RB10     | 23                                    | 34                                    | I/O         | ST             |                                   |

| RB11     | 24                                    | 35                                    | I/O         | ST             |                                   |

| RB12     | 27                                    | 41                                    | I/O         | ST             |                                   |

| RB13     | 28                                    | 42                                    | I/O         | ST             |                                   |

| RB14     | 29                                    | 43                                    | I/O         | ST             |                                   |

| RB15     | 30                                    | 44                                    | I/O         | ST             |                                   |

| Legend:  | CMOS = CM                             | IOS compati                           | hla inni    | it or output   | Analog = Analog input             |

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

I = Input

O = Output

ST = Schmitt Trigger input with CMOS levels

TTL = TTL input buffer

P = Power

Note 1: This pin is only available on devices without a USB module.

- 2: This pin is only available on devices with a USB module.

- 3: This pin is not available on 64-pin devices with a USB module.

- **4:** This pin is only available on 100-pin devices without a USB module.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

### 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX/5XX 64/ 100-pin family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP™) and debugging purposes (see 2.5 "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

Note:

The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 µF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended that

the capacitors be placed on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within onequarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

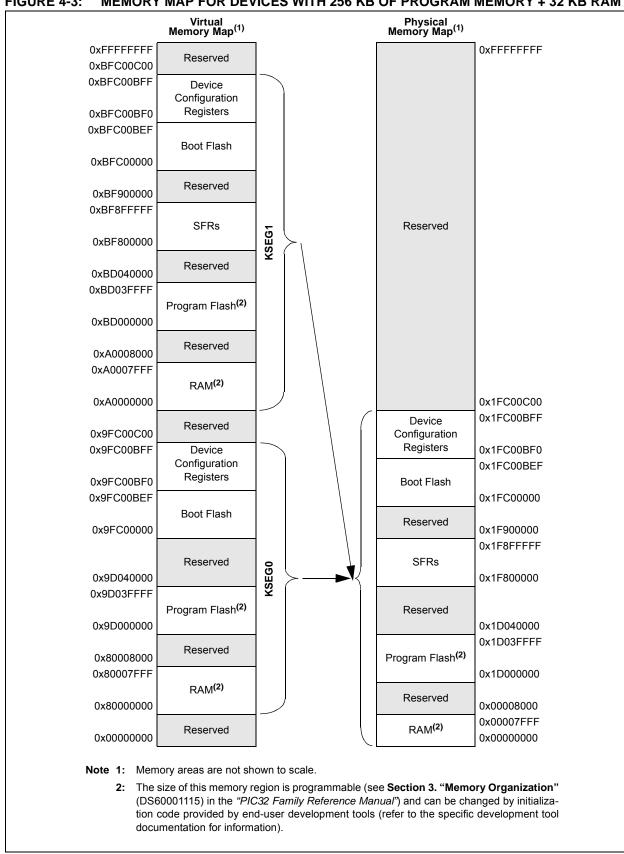

FIGURE 4-3: MEMORY MAP FOR DEVICES WITH 256 KB OF PROGRAM MEMORY + 32 KB RAM

TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

| Intonum (0 (1)                             | IDC " | Vector |               | Interru      | ıpt Bit Location |              | Persistent |

|--------------------------------------------|-------|--------|---------------|--------------|------------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>            | IRQ#  | #      | Flag          | Enable       | Priority         | Sub-priority | Interrupt  |

| CNA – PORTA Input Change Interrupt         | 44    | 33     | IFS1<12>      | IEC1<12>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CNB – PORTB Input Change Interrupt         | 45    | 33     | IFS1<13>      | IEC1<13>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CNC - PORTC Input Change Interrupt         | 46    | 33     | IFS1<14>      | IEC1<14>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CND – PORTD Input Change Interrupt         | 47    | 33     | IFS1<15>      | IEC1<15>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CNE – PORTE Input Change Interrupt         | 48    | 33     | IFS1<16>      | IEC1<16>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CNF - PORTF Input Change Interrupt         | 49    | 33     | IFS1<17>      | IEC1<17>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CNG – PORTG Input Change Interrupt         | 50    | 33     | IFS1<18>      | IEC1<18>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| PMP – Parallel Master Port                 | 51    | 34     | IFS1<19>      | IEC1<19>     | IPC8<20:18>      | IPC8<17:16>  | Yes        |

| PMPE – Parallel Master Port Error          | 52    | 34     | IFS1<20>      | IEC1<20>     | IPC8<20:18>      | IPC8<17:16>  | Yes        |

| SPI2E – SPI2 Fault                         | 53    | 35     | IFS1<21>      | IEC1<21>     | IPC8<28:26>      | IPC8<25:24>  | Yes        |

| SPI2RX – SPI2 Receive Done                 | 54    | 35     | IFS1<22>      | IEC1<22>     | IPC8<28:26>      | IPC8<25:24>  | Yes        |

| SPI2TX – SPI2 Transfer Done                | 55    | 35     | IFS1<23>      | IEC1<23>     | IPC8<28:26>      | IPC8<25:24>  | Yes        |

| U2E – UART2 Error                          | 56    | 36     | IFS1<24>      | IEC1<24>     | IPC9<4:2>        | IPC9<1:0>    | Yes        |

| U2RX – UART2 Receiver                      | 57    | 36     | IFS1<25>      | IEC1<25>     | IPC9<4:2>        | IPC9<1:0>    | Yes        |

| U2TX – UART2 Transmitter                   | 58    | 36     | IFS1<26>      | IEC1<26>     | IPC9<4:2>        | IPC9<1:0>    | Yes        |

| I2C2B – I2C2 Bus Collision Event           | 59    | 37     | IFS1<27>      | IEC1<27>     | IPC9<12:10>      | IPC9<9:8>    | Yes        |

| I2C2S – I2C2 Slave Event                   | 60    | 37     | IFS1<28>      | IEC1<28>     | IPC9<12:10>      | IPC9<9:8>    | Yes        |

| I2C2M – I2C2 Master Event                  | 61    | 37     | IFS1<29>      | IEC1<29>     | IPC9<12:10>      | IPC9<9:8>    | Yes        |

| U3E – UART3 Error                          | 62    | 38     | IFS1<30>      | IEC1<30>     | IPC9<20:18>      | IPC9<17:16>  | Yes        |

| U3RX – UART3 Receiver                      | 63    | 38     | IFS1<31>      | IEC1<31>     | IPC9<20:18>      | IPC9<17:16>  | Yes        |

| U3TX – UART3 Transmitter                   | 64    | 38     | IFS2<0>       | IEC2<0>      | IPC9<20:18>      | IPC9<17:16>  | Yes        |

| U4E – UART4 Error                          | 65    | 39     | IFS2<1>       | IEC2<1>      | IPC9<28:26>      | IPC9<25:24>  | Yes        |

| U4RX – UART4 Receiver                      | 66    | 39     | IFS2<2>       | IEC2<2>      | IPC9<28:26>      | IPC9<25:24>  | Yes        |

| U4TX – UART4 Transmitter                   | 67    | 39     | IFS2<3>       | IEC2<3>      | IPC9<28:26>      | IPC9<25:24>  | Yes        |

| U5E – UART5 Error <sup>(2)</sup>           | 68    | 40     | IFS2<4>       | IEC2<4>      | IPC10<4:2>       | IPC10<1:0>   | Yes        |

| U5RX – UART5 Receiver <sup>(2)</sup>       | 69    | 40     | IFS2<5>       | IEC2<5>      | IPC10<4:2>       | IPC10<1:0>   | Yes        |

| U5TX – UART5 Transmitter <sup>(2)</sup>    | 70    | 40     | IFS2<6>       | IEC2<6>      | IPC10<4:2>       | IPC10<1:0>   | Yes        |

| CTMU - CTMU Event <sup>(2)</sup>           | 71    | 41     | IFS2<7>       | IEC2<7>      | IPC10<12:10>     | IPC10<9:8>   | Yes        |

| DMA0 - DMA Channel 0                       | 72    | 42     | IFS2<8>       | IEC2<8>      | IPC10<20:18>     | IPC10<17:16> | No         |

| DMA1 – DMA Channel 1                       | 73    | 43     | IFS2<9>       | IEC2<9>      | IPC10<28:26>     | IPC10<25:24> | No         |

| DMA2 – DMA Channel 2                       | 74    | 44     | IFS2<10>      | IEC2<10>     | IPC11<4:2>       | IPC11<1:0>   | No         |

| DMA3 – DMA Channel 3                       | 75    | 45     | IFS2<11>      | IEC2<11>     | IPC11<12:10>     | IPC11<9:8>   | No         |

| CMP3 – Comparator 3 Interrupt              | 76    | 46     | IFS2<12>      | IEC2<12>     | IPC11<20:18>     | IPC11<17:16> | No         |

| CAN1 – CAN1 Event                          | 77    | 47     | IFS2<13>      | IEC2<13>     | IPC11<28:26>     | IPC11<25:24> | Yes        |

| SPI3E – SPI3 Fault                         | 78    | 48     | IFS2<14>      | IEC2<14>     | IPC12<4:2>       | IPC12<1:0>   | Yes        |

| SPI3RX – SPI3 Receive Done                 | 79    | 48     | IFS2<15>      | IEC2<15>     | IPC12<4:2>       | IPC12<1:0>   | Yes        |

| SPI3TX – SPI3 Transfer Done                | 80    | 48     | IFS2<16>      | IEC2<16>     | IPC12<4:2>       | IPC12<1:0>   | Yes        |

| SPI4E – SPI4 Fault <sup>(2)</sup>          | 81    | 49     | IFS2<17>      | IEC2<17>     | IPC12<12:10>     | IPC12<9:8>   | Yes        |

| SPI4RX – SPI4 Receive Done <sup>(2)</sup>  | 82    | 49     | IFS2<18>      | IEC2<18>     | IPC12<12:10>     | IPC12<9:8>   | Yes        |

| SPI4TX – SPI4 Transfer Done <sup>(2)</sup> | 83    | 49     | IFS2<19>      | IEC2<19>     | IPC12<12:10>     | IPC12<9:8>   | Yes        |

|                                            |       | Lowe   | st Natural Or | der Priority |                  |              |            |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

<sup>2:</sup> This interrupt source is not available on 64-pin devices.

#### REGISTER 5-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | _                 | _                 | _                 | IP3<2:0>          |                   |                   | IS3<1:0>         |                  |  |

| 22:46        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | _                 | _                 | _                 | IP2<2:0>          |                   |                   | IS2<1:0>         |                  |  |

| 15.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | _                 | _                 |                   | IP1<2:0>          |                   | IS1<             | 1:0>             |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                 | _                 | _                 |                   | IP0<2:0>          |                   | IS0<             | 1:0>             |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-26 IP3<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 25-24 IS3<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 23-21 Unimplemented: Read as '0'

bit 20-18 IP2<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

.

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 17-16 IS2<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 15-13 Unimplemented: Read as '0'

bit 12-10 IP1<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

.

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 5-1 for the exact bit definitions.

#### REGISTER 6-4: NVMDATA: FLASH PROGRAM DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | NVMDATA<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 22.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        |                   |                   |                   | NVMDA             | TA<23:16>         |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | NVMDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | NVMD              | ATA<7:0>          | _                 |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

**Note:** The bits in this register are only reset by a Power-on Reset (POR).

### REGISTER 6-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | NVMSRCA           | DDR<31:24>        | •                 |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

#### DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER **REGISTER 9-14:**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | _                 | _                 | _                 | _                 | _                 | _                | -                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHSPTF            | R<7:0>            |                   |                  |                  |  |  |

Legend:

R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit

-n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

111111111111111 = Points to byte 65,535 of the source

0000000000000000 = Points to byte 1 of the source 0000000000000000 = Points to byte 0 of the source

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15.6         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7.0          | CHDPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

111111111111111 = Points to byte 65,535 of the destination

0000000000000001 = Points to byte 1 of the destination

0000000000000000 = Points to byte 0 of the destination

#### REGISTER 10-3: U10TGSTAT: USB OTG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | -                 | -                 | -                 | -                 | _                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 13.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7:0          | ID                | _                 | LSTATE            | _                 | SESVD             | SESEND            | _                | VBUSVD           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **ID:** ID Pin State Indicator bit

1 = No cable is attached or a Type-B cable has been plugged into the USB receptacle

0 = A Type-A cable has been plugged into the USB receptacle

bit 6 Unimplemented: Read as '0'

bit 5 LSTATE: Line State Stable Indicator bit

1 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has been stable for the previous 1 ms

0 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has not been stable for the previous 1 ms

bit 4 Unimplemented: Read as '0'

bit 3 SESVD: Session Valid Indicator bit

1 = VBUS voltage is above Session Valid on the A or B device

0 = VBUS voltage is below Session Valid on the A or B device

bit 2 SESEND: B-Device Session End Indicator bit

1 = VBUS voltage is below Session Valid on the B device

0 = VBUS voltage is above Session Valid on the B device

bit 1 **Unimplemented:** Read as '0'

bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

1 = VBUS voltage is above Session Valid on the A device

0 = VBUS voltage is below Session Valid on the A device

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 31:24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31.24        | _                 | _                 | _                        | _                 | _                     | -                     | _                | _                    |

| 22.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | _                 | _                 | _                        | _                 | _                     | -                     | _                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         | _                 | _                 | _                        | _                 | _                     | -                     | _                | _                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | ICTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | DDDDOT           | USBEN <sup>(4)</sup> |

|              | JSTATE            |                   | TOKBUSY <sup>(1,5)</sup> |                   | HOSTEN                | RESUME                | PPBRST           | SOFEN <sup>(5)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

1 = JSTATE detected on the USB

0 = No JSTATE detected

bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single Ended Zero detected on the USB

0 = No Single Ended Zero detected

bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

1 = Token and packet processing disabled (set upon SETUP token received)

0 = Token and packet processing enabled

**TOKBUSY:** Token Busy Indicator bit (1,5)

1 = Token being executed by the USB module

0 = No token being executed

bit 4 USBRST: Module Reset bit (5)

1 = USB reset generated

0 = USB reset terminated

bit 3 **HOSTEN:** Host Mode Enable bit<sup>(2)</sup>

1 = USB host capability enabled

0 = USB host capability disabled

bit 2 **RESUME**: RESUME Signaling Enable bit<sup>(3)</sup>

1 = RESUME signaling activated

0 = RESUME signaling disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- **3:** Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit

When TCS = 1:

1 = External clock input is synchronized0 = External clock input is not synchronized

When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit

1 = External clock from TxCKI pin

0 = Internal peripheral clock

bit 0 **Unimplemented:** Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# REGISTER 13-1: TxCON: TYPE B TIMER 'x' CONTROL REGISTER (CONTINUED)('x' = 2 THROUGH 5)

bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

1 = Odd numbered and even numbered timers form a 32-bit timer

0 = Odd numbered and even numbered timers form a separate 16-bit timer

bit 2 Unimplemented: Read as '0'

bit 1 TCS: Timer Clock Source Select bit<sup>(3)</sup>

1 = External clock from TxCK pin

0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- **4:** While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 15.0         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 15:8         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

|              | AUDEN <sup>(1)</sup> | _                 | _                 | _                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | <1:0> <sup>(1,2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

1 = Data from RX FIFO is sign extended

0 = Data from RX FIFO is not sign extened

bit 14-13 Unimplemented: Read as '0'

bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit

1 = Frame Error overflow generates error events

0 = Frame Error does not generate error events

bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = Receive overflow generates error events

0 = Receive overflow does not generate error events

bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

1 = Transmit Underrun Generates Error Events

0 = Transmit Underrun Does Not Generates Error Events

bit 9 **IGNROV:** Ignore Receive Overflow bit (for Audio Data Transmissions)

1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data

0 = A ROV is a critical error which stop SPI operation

bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

0 = A TUR is a critical error which stop SPI operation

bit 7 AUDEN: Enable Audio CODEC Support bit(1)

1 = Audio protocol enabled

0 = Audio protocol disabled

bit 6-5 Unimplemented: Read as '0'

bit 3 **AUDMONO:** Transmit Audio Data Format bit<sup>(1,2)</sup>

1 = Audio data is mono (Each data word is transmitted on both left and right channels)

0 = Audio data is stereo

bit 2 **Unimplemented:** Read as '0'

bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit(1,2)

11 = PCM/DSP mode

10 = Right Justified mode

01 = Left Justified mode

$00 = I^2S \text{ mode}$

**Note 1:** This bit can only be written when the ON bit = 0.

2: This bit is only valid for AUDEN = 1.

#### REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4   | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|---------------------|---------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0                 | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                   | _                  | _                   | _                   |                   | _                | _                |

| 22:46        | R/W-0, HC         | U-0                 | U-0                | U-0                 | U-0                 | U-0               | R/W-0            | U-0              |

| 23:16        | RDSTART           | _                   | _                  | _                   | _                   | _                 | DUALBUF          | _                |

| 15:0         | R/W-0             | U-0                 | R/W-0              | R/W-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                   | SIDL               | ADRMU               | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7:0          | R/W-0             | R/W-0               | R/W-0              | R/W-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

|              | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | CS2P <sup>(2)</sup> | CS1P <sup>(2)</sup> |                   | WRSP             | RDSP             |

Legend:HC = Hardware clearedR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23 RDSTART: Start a Read on the PMP Bus bit (3)

1 = Start a read cycle on the PMP bus

0 = No effect

This bit is cleared by hardware at the end of the read cycle when the BUSY bit (PMMODE<15>) = 0.

bit 22-18 Unimplemented: Read as '0'

bit 17 **DUALBUF:** Parallel Master Port Dual Read/Write Buffer Enable bit

This bit is only valid in Master mode.

1 = PMP uses separate registers for reads and writes

Reads: PMRADDR and PMRDIN Writes: PMRWADDR and PMDOUT

0 = PMP uses legacy registers for reads and writes

Reads/Writes: PMADDR and PMRDIN

bit 16 Unimplemented: Read as '0'

bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

1 = PMP enabled

0 = PMP disabled, no off-chip access performed

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

11 = Lower 8 bits of address are multiplexed on PMD<15:0> pins

10 = All 16 bits of address are multiplexed on PMD<7:0> pins

01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

00 = Address and data appear on separate pins

bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

1 = PMP module uses TTL input buffers

0 = PMP module uses Schmitt Trigger input buffer

bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

1 = PMWR/PMENB port enabled

0 = PMWR/PMENB port disabled

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

2: These bits have no effect when their corresponding pins are used as address lines.

#### **REGISTER 23-13: C1FLTCON3: CAN FILTER CONTROL REGISTER 3**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | FLTEN15           | MSEL1               | 5<1:0>            | FSEL15<4:0>       |                   |                   |                  |                  |

| 00.46        | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN14           | MSEL1               | 4<1:0>            | FSEL14<4:0>       |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 13.6         | FLTEN13           | MSEL13<1:0>         |                   | FSEL13<4:0>       |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FLTEN12           | FLTEN12 MSEL12<1:0> |                   | FSEL12<4:0>       |                   |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FLTEN15: Filter 15 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 30-29 MSEL15<1:0>: Filter 15 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 28-24 FSEL15<4:0>: FIFO Selection bits

11111 = Reserved

•

•

10000 = Reserved

01111 = Message matching filter is stored in FIFO buffer 15

•

•

DS60001290D-page 262

00000 = Message matching filter is stored in FIFO buffer 0

bit 23 FLTEN14: Filter 14 Enable bit

1 = Filter is enabled0 = Filter is disabled

bit 22-21 MSEL14<1:0>: Filter 14 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-0               | r-1                                   | r-1               | R/P               | r-1               | r-1               | r-1              | R/P              |

| 31:24        | _                 | _                                     | _                 | CP                | _                 | _                 | _                | BWP              |

| 00:40        | r-1               | r-1                                   | r-1               | r-1               | R/P               | R/P               | R/P              | R/P              |

| 23:16        | _                 | _                                     | _                 | _                 | PWP<9:6>          |                   |                  |                  |

| 45.0         | R/P               | R/P                                   | R/P               | R/P               | R/P               | R/P               | r-1              | r-1              |

| 15:8         | PWP<5:0>          |                                       |                   |                   |                   |                   |                  | _                |

| 7:0          | r-1               | r-1                                   | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |

|              | _                 | — — ICESEL<1:0> JTAGEN <sup>(1)</sup> |                   |                   |                   |                   |                  | G<1:0>           |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 Reserved: Write '0' bit 30-29 Reserved: Write '1' bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external pro-

gramming device.

1 = Protection is disabled0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable0 = Boot Flash is not writable

bit 23-20 Reserved: Write '1'

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 19-10 PWP<9:0>: Program Flash Write-Protect bits

```

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits

represent the one's compliment of the number of write protected program Flash memory pages.

1111111111 = Disabled

1111111110 = Memory below 0x0400 address is write-protected

1111111101 = Memory below 0x0800 address is write-protected

1111111100 = Memory below 0x0C00 address is write-protected

1111111011 = Memory below 0x1000 (4K) address is write-protected

1111111010 = Memory below 0x1400 address is write-protected

1111111001 = Memory below 0x1800 address is write-protected

1111111000 = Memory below 0x1C00 address is write-protected

1111110111 = Memory below 0x2000 (8K) address is write-protected

1111110110 = Memory below 0x2400 address is write-protected

1111110101 = Memory below 0x2800 address is write-protected

1111110100 = Memory below 0x2C00 address is write-protected

1111110011 = Memory below 0x3000 address is write-protected

1111110010 = Memory below 0x3400 address is write-protected

1111110001 = Memory below 0x3800 address is write-protected

1111110000 = Memory below 0x3C00 address is write-protected

1111101111 = Memory below 0x4000 (16K) address is write-protected

1110111111 = Memory below 0x10000 (64K) address is write-protected

1101111111 = Memory below 0x20000 (128K) address is write-protected

1011111111 = Memory below 0x40000 (256K) address is write-protected

0111111111 = Memory below 0x80000 (512K) address is write-protected

000000000 = All possible memory is write-protected

These bits are effective only if Boot Flash is also protected by clearing the BWP bit

Note:

(DEVCFG0<24>).

bit 9-5

Reserved: Write '1'

bit 4-3

ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits

11 = PGEC1/PGED1 pair is used

10 = PGEC2/PGED2 pair is used

01 = PGEC3/PGED3 pair is used

00 = Reserved

bit 2

JTAGEN: JTAG Enable bit(1)

1 = JTAG is enabled

0 = JTAG is disabled

bit 1-0

DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled)

1x = Debugger is disabled

0x = Debugger is enabled

```

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

TABLE 31-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

AC CHARACTERISTICS Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature  $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$  for V-temp

| Param.<br>No. | Symbol    | Characteristics <sup>(1)</sup>                            |                             | Min.                                      | Max. | Units | Condit                        | ions                  |

|---------------|-----------|-----------------------------------------------------------|-----------------------------|-------------------------------------------|------|-------|-------------------------------|-----------------------|

| TB10          | ТтхН      | TxCK<br>High Time                                         | Synchronous, with prescaler | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns         | _    | ns    | Must also meet parameter TB15 | value<br>(1, 2, 4, 8, |

| TB11          | TTXL      | TxCK<br>Low Time                                          | Synchronous, with prescaler | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns         | _    | ns    | Must also meet parameter TB15 | 16, 32, 64,<br>256)   |

| TB15          | TTXP      | TxCK<br>Input                                             | Synchronous, with prescaler | [(Greater of [(25 ns or 2 TPB)/N] + 30 ns | _    | ns    | VDD > 2.7V                    |                       |

|               |           | Period                                                    |                             | [(Greater of [(25 ns or 2 TPB)/N] + 50 ns | _    | ns    | VDD < 2.7V                    |                       |

| TB20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer Increment |                             | _                                         | 1    | Трв   |                               |                       |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

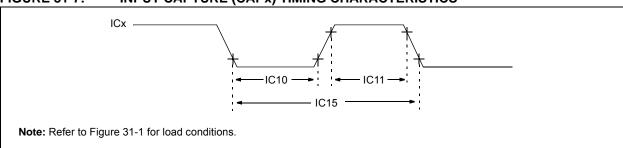

### FIGURE 31-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

**TABLE 31-25: INPUT CAPTURE MODULE TIMING REQUIREMENTS**

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                                   |   |      |                                         |                                  |     |          |

|--------------------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---|------|-----------------------------------------|----------------------------------|-----|----------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> |                                                                                                                                                                                                                                                | Characteristics <sup>(1)</sup>    |   | Min. | Max.                                    | Units                            | Cor | nditions |

| IC10               | TccL   | ICx Input Low Time             |                                                                                                                                                                                                                                                | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns | _ | ns   | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |     |          |

| IC11               | TccH   | ICx Input                      | t High Time                                                                                                                                                                                                                                    | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns | _ | ns   | Must also<br>meet<br>parameter<br>IC15. |                                  |     |          |

| IC15               | TCCP   | ICx Input                      |                                                                                                                                                                                                                                                | [(25 ns or 2 TPB)/N]<br>+ 50 ns   | _ | ns   | _                                       |                                  |     |          |

Note 1: These parameters are characterized, but not tested in manufacturing.