Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 49                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 28x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f512h-50i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)**

|                       | Pin N                       | umber |             |                |                                                                                                    |  |  |  |

|-----------------------|-----------------------------|-------|-------------|----------------|----------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name              | 64-pin<br>QFN/<br>TQFP TQFP |       | Pin<br>Type | Buffer<br>Type | Description                                                                                        |  |  |  |

| VUSB3V3 <b>(2)</b>    | 35                          | 55    | Р           | —              | USB internal transceiver supply. If the USB module is not used, this pin must be connected to VDD. |  |  |  |

| VBUSON <sup>(2)</sup> | 11                          | 20    | 0           | —              | USB Host and OTG bus power control Output                                                          |  |  |  |

| D+ <sup>(2)</sup>     | 37                          | 57    | I/O         | Analog         | USB D+                                                                                             |  |  |  |

| D-(2)                 | 36                          | 56    | I/O         | Analog         | USB D-                                                                                             |  |  |  |

| USBID <sup>(2)</sup>  | 33                          | 51    | Ι           | ST             | USB OTG ID Detect                                                                                  |  |  |  |

| PGED1                 | 16                          | 25    | I/O         | ST             | Data I/O pin for Programming/Debugging Communication<br>Channel 1                                  |  |  |  |

| PGEC1                 | 15                          | 24    | I           | ST             | Clock Input pin for Programming/Debugging Communication Channel 1                                  |  |  |  |

| PGED2                 | 18                          | 27    | I/O         | ST             | Data I/O Pin for Programming/Debugging Communication<br>Channel 2                                  |  |  |  |

| PGEC2                 | 17                          | 26    | I           | ST             | Clock Input Pin for Programming/Debugging Communication Channel 2                                  |  |  |  |

| PGED3                 | 13                          | 22    | I/O         | ST             | Data I/O Pin for Programming/Debugging Communication<br>Channel 3                                  |  |  |  |

| PGEC3                 | 14                          | 23    | I           | ST             | Clock Input Pin for Programming/Debugging Communication<br>Channel 3                               |  |  |  |

| CTED1                 | _                           | 17    | Ι           | ST             | CTMU External Edge Input 1                                                                         |  |  |  |

| CTED2                 |                             | 38    | I           | ST             | CTMU External Edge Input 2                                                                         |  |  |  |

| CTED3                 | 18                          | 27    | I           | ST             | CTMU External Edge Input 3                                                                         |  |  |  |

| CTED4                 | 22                          | 33    | Ι           | ST             | CTMU External Edge Input 4                                                                         |  |  |  |

| CTED5                 | 29                          | 43    | Ι           | ST             | CTMU External Edge Input 5                                                                         |  |  |  |

| CTED6                 | 30                          | 44    | Ι           | ST             | CTMU External Edge Input 6                                                                         |  |  |  |

| CTED7                 | _                           | 9     | Ι           | ST             | CTMU External Edge Input 7                                                                         |  |  |  |

| CTED8                 |                             | 92    | Ι           | ST             | CTMU External Edge Input 8                                                                         |  |  |  |

| CTED9                 |                             | 60    | Ι           | ST             | CTMU External Edge Input 9                                                                         |  |  |  |

| CTED10                | 21                          | 32    | Ι           | ST             | CTMU External Edge Input 10                                                                        |  |  |  |

| CTED11                | 23                          | 34    | Ι           | ST             | CTMU External Edge Input 11                                                                        |  |  |  |

| CTED12                | 15                          | 24    | Ι           | ST             | CTMU External Edge Input 12                                                                        |  |  |  |

| CTED13                | 14                          | 23    | Ι           | ST             | CTMU External Edge Input 13                                                                        |  |  |  |

| C1RX                  | PPS                         | PPS   | Ι           | ST             | Enhanced CAN Receive                                                                               |  |  |  |

| C1TX                  | PPS                         | PPS   | 0           | ST             | Enhanced CAN Transmit                                                                              |  |  |  |

**Legend:** CMOS = CMOS compatible input or output

P = Power

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer **Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module. 4: This pin is only available on 100-pin devices without a USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 31:24        |                   |                   |                   | BMXPFN            | ISZ<31:24>        |                   |                  |                  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7:0          | BMXPFMSZ<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

### Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00010000 = Device has 64 KB Flash 0x00020000 = Device has 128 KB Flash 0x00040000 = Device has 256 KB Flash 0x00080000 = Device has 512 KB Flash

#### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

|              |                   |                   |                   | . ,               |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 31:24        |                   |                   |                   | BMXBOO            | TSZ<31:24>        |                   |                  |                  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15:8         |                   |                   |                   | BMXBOC            | )TSZ<15:8>        |                   |                  |                  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7:0          |                   |                   |                   | BMXBO             | OTSZ<7:0>         |                   |                  |                  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00000C00 = Device has 3 KB Boot Flash

© 2014-2016 Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | NVMDA             | TA<31:24>         |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | NVMDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | NVMDATA<7:0>      |                   |                   |                   |                   |                  |                  |  |  |  |

#### **REGISTER 6-4:** NVMDATA: FLASH PROGRAM DATA REGISTER

I edend.

| Logonal           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

Note: The bits in this register are only reset by a Power-on Reset (POR).

#### NVMSRCADDR: SOURCE DATA ADDRESS REGISTER **REGISTER 6-5:**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   | NVMSRCA           | DDR<31:24>        | •                 |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

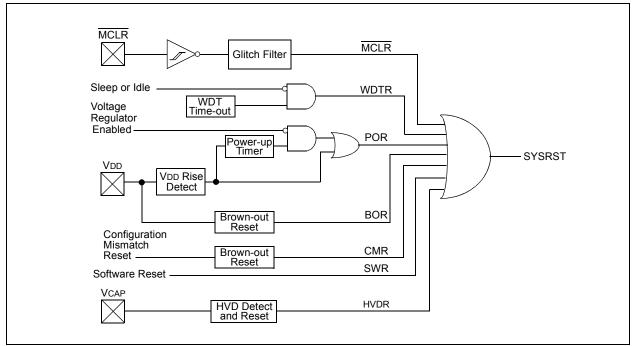

### 7.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Reset pin

- · SWR: Software Reset

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CMR: Configuration Mismatch Reset

- HVDR: High Voltage Detect Reset

A simplified block diagram of the Reset module is illustrated in Figure 7-1.

#### FIGURE 7-1: SYSTEM RESET BLOCK DIAGRAM

| KE0131       | EGISTER 10-1: 0101GIR: 03B 01G INTERROFT STATUS REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24        | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                                                        | —                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 23:16        | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                                                        | —                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 15:8         | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                                                        | —                 | —                 |                   | -                 | _                 | -                | —                |  |  |

|              | R/WC-0, HS                                               | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | U-0              | R/WC-0, HS       |  |  |

| 7:0          | IDIF                                                     | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |  |  |

#### REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable   | bit                |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIF: ID State Change Indicator bit

- 1 = Change in ID state detected

- 0 = No change in ID state detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1millisecond, but different from last time

- 0 = USB line state has not been stable for 1 millisecond

#### bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = Change on the session valid input detected

- 0 = No change on the session valid input detected

|              | $\Box R 10=10.$   |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | —                 | —                 | —                 | -                 | -                 | —                | -                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | —                 | —                 | -                 |                   | —                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | _                 | —                 | —                 | —                 | _                 | _                 | —                | -                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |

#### REGISTER 10-18: U1BDTP2: USB BDT PAGE 2 REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** BDT Base Address bits This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        |                   | —                 | —                 |                   | _                 | _                 |                  | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | -                 | —                 | —                 | -                 | —                 | _                 | -                | —                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.0         | -                 | —                 | —                 | -                 | —                 | _                 | -                | —                |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | BDTPTRU<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

#### REGISTER 10-19: U1BDTP3: USB BDT PAGE 3 REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

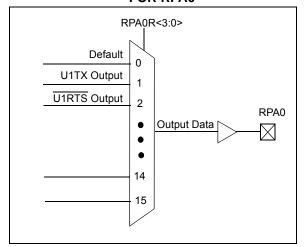

#### 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

### 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

#### 11.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

#### 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

#### 11.4 Control Registers

#### TABLE 11-3: PORTA REGISTER MAP 100-PIN DEVICES ONLY

| -                           |                                 |           |               |               |       |       | -     |               |              |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ress<br>)                   | <b>N</b> .                      | Ð         |               |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | ANSELA                          | 31:16     | _             | _             | _     | _     | —     | —             | —            | _    | —            | —            | —            |              | —            |              | I            | —            | 0000          |

| 0000                        | ANGELA                          | 15:0      | _             | —             | _     | —     | —     | ANSELA10      | ANSELA9      | —    | —            | _            | _            |              | _            | _            |              | _            | 0060          |

| 6010                        | TRISA                           | 31:16     | _             | —             | _     | —     | —     | —             | —            | —    | —            | _            | _            |              | _            | _            |              | _            | 0000          |

| 0010                        | INISA                           | 15:0      | TRISA15       | TRISA14       | —     | —     | —     | TRISA10       | TRISA9       | —    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | C6FF          |

| 6020                        | PORTA                           | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 0020                        | FURIA                           | 15:0      | RA15          | RA14          | —     | —     | —     | RA10          | RA9          | —    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                            | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 0030                        | LAIA                            | 15:0      | LATA15        | LATA14        | —     | —     | —     | LATA10        | LATA9        | —    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                            | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 0040                        | ODCA                            | 15:0      | ODCA15        | ODCA14        | —     | —     | —     | ODCA10        | ODCA9        | —    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | 0000          |

| 6050                        | CNPUA                           | 31:16     | _             | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | -            | —            | _            | _            | —            | 0000          |

| 0000                        |                                 | 15:0      | CNPUA15       | CNPUA14       | —     | —     | _     | CNPUA10       | CNPUA9       | —    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | 0000          |

| 6060                        | CNPDA                           | 31:16     | _             | —             | _     | _     | _     | _             | —            | _    | _            |              |              | _            |              | _            |              |              | 0000          |

| 0000                        |                                 | 15:0      | CNPDA15       | CNPDA14       | _     | _     | _     | CNPDA10       | CNPDA9       | _    | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       | 0000          |

| 6070                        | CNCONA                          | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | _            | —            | 0000          |

| 0010                        |                                 | 15:0      | ON            | —             | SIDL  | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 6080                        | CNENA                           | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0000                        | ONEN                            | 15:0      | CNIEA15       | CNIEA14       | _     | _     | _     | CNIEA10       | CNIEA9       | _    | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | 0000          |

|                             |                                 | 31:16     | _             | —             | _     | —     | —     | —             | —            | _    | —            | —            | —            | _            | —            | —            | _            | —            | 0000          |

| 6090                        | CNSTATA                         | 15:0      | CN<br>STATA15 | CN<br>STATA14 | _     | _     | _     | CN<br>STATA10 | CN<br>STATA9 | _    | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | 0000          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| ess                         |                                 |           |       |       |               |               |       |       |      | Bits         | 5            |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6500                        | ANSELF                          | 31:16     | _     | -     | —             | —             | _     | —     | —    | _            | -            | —            | —            | —            | —            | —            | -            | -            | 0000          |

| 0000                        | ANOLLI                          | 15:0      | —     | _     | ANSELE13      | ANSELE12      | —     | _     | _    | ANSELE8      |              | —            | _            |              |              | ANSELE2      | ANSELE1      | ANSELE0      | 3107          |

| 6510                        | TRISF                           | 31:16     | —     | _     | —             | —             | —     | —     | _    | —            | _            | —            | —            | _            |              |              | _            | _            | 0000          |

| 0010                        | TRIO                            | 15:0      | _     | -     | TRISF13       | TRISF12       | _     | —     | —    | TRISF8       | TRISF7       | TRISF6       | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | 31FF          |

| 6520                        | PORTF                           | 31:16     | _     | -     | —             | —             | _     | —     | —    | —            | -            | —            | —            | _            | —            | —            | _            | _            | 0000          |

| 0020                        | 1 OKII                          | 15:0      | _     | -     | RF13          | RF12          | _     | —     | —    | RF8          | RF7          | RF6          | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATE                            | 31:16     | _     | -     | —             | —             | _     | —     | —    | —            | -            | —            | —            | _            | —            | —            | _            | _            | 0000          |

| 0000                        | LAII                            | 15:0      | _     | -     | LATF13        | LATF12        | _     | —     | —    | LATF8        | LATF7        | LATF6        | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | _     | -     | —             | —             | _     | —     | —    | —            | -            | —            | —            | _            | —            | —            | _            | _            | 0000          |

| 0340                        | ODCI                            | 15:0      | _     |       | ODCF13        | ODCF12        | -     | _     | —    | ODCF8        | ODCF7        | ODCF6        | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | 0000          |

| 6550                        | CNPUF                           | 31:16     | _     |       | _             | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 0330                        | CINFUI                          | 15:0      | _     |       | CNPUF13       | CNPUF12       | -     | _     | —    | CNPUF8       | CNPUF7       | CNPUF6       | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | 0000          |

| 6560                        | CNPDF                           | 31:16     | _     |       | _             | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 0300                        | CINF DI                         | 15:0      | _     |       | CNPDF13       | CNPDF12       | -     | _     | —    | CNPDF8       | CNPDF7       | CNPDF6       | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | 0000          |

| 6570                        | CNCONF                          | 31:16     | _     | _     | —             | —             | —     | _     | _    | —            | _            | —            | _            | _            | —            | _            | -            | -            | 0000          |

| 0370                        | CINCOIN                         | 15:0      | ON    |       | SIDL          | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 6580                        | CNENF                           | 31:16     | _     |       | _             | _             | -     | _     | —    | _            |              | _            | _            | _            | _            | _            |              |              | 0000          |

| 0380                        | CINLINI                         | 15:0      | _     |       | CNIEF13       | CNIEF12       | -     | _     | —    | CNIEF8       | CNIEF7       | CNIEF6       | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | 0000          |

|                             |                                 | 31:16     | _     | _     | —             | —             | —     | _     | —    | _            |              | _            | _            | —            | _            | —            |              |              | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | _     | CN<br>STATF13 | CN<br>STATF12 | _     | _     | _    | CN<br>STATF8 | CN<br>STATF7 | CN<br>STATF6 | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | 0000          |

### TABLE 11-11: PORTF REGISTER MAP FOR PIC32MX130F128L, PIC32MX150F256L, AND PIC32MX170F512L DEVICES ONLY

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

#### TABLE 11-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SS                          |                  |               |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16         |       | —     | —     | -     | -     | —     | -    | -    | -    | —    | -    | -    | —    | —     | -      | _    | 0000       |

| 1 A04                       |                  | 15:0          | _     | —     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | INT1F | <3:0>  |      | 0000       |

| FA08                        | INT2R            | 31:16         | _     | _     |       |       | _     | _     | _    | —    | _    | _    | _    | _    | —    | _     | —      | _    | 0000       |

| 17.00                       | 1111211          | 15:0          |       |       |       |       |       |       | —    |      | _    | _    |      |      |      | INT2F | <3:0>  |      | 0000       |

| FA0C                        | INT3R            | 31:16         | _     | —     |       |       | _     |       | _    | _    | _    | _    | _    | _    |      |       | _      |      | 0000       |

|                             |                  | 15:0          | —     | —     | —     | —     | _     | —     | —    | —    | —    | —    | —    | _    |      | INT3F | <3:0>  |      | 0000       |

| FA10                        | INT4R            | 31:16         | —     | —     | _     | —     | _     | —     | —    | —    | —    | _    | —    | _    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0          |       |       | _     | _     | _     |       | _    | _    | _    | _    | _    | _    |      | INT4F | <3:0>  |      | 0000       |

| FA18                        | T2CKR            | 31:16         | _     |       |       |       |       |       |      |      |      |      | —    |      |      | -     | —      | _    | 0000       |

|                             |                  | 15:0          |       |       | _     | _     |       |       |      | _    | _    | _    |      | _    |      | T2CK  | <<3:0> | _    | 0000       |

| FA1C                        | T3CKR            | 31:16         | _     | —     |       |       |       |       | _    |      |      | —    |      |      | _    | —<br> | -      | —    | 0000       |

|                             |                  | 15:0          | _     |       |       |       |       |       |      |      |      |      |      |      |      | T3CKF | <<3:0> |      | 0000       |

| FA20                        | T4CKR            | 31:16<br>15:0 |       | _     |       |       |       |       |      |      |      |      |      |      |      | T4CKF |        | —    | 0000       |

|                             |                  |               |       |       | _     |       |       |       |      |      |      | _    |      |      |      | 1400  | (<3.0> |      | 0000       |

| FA24                        | T5CKR            | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      |      |      | T5CKF |        | _    | 0000       |

|                             |                  | 31:16         |       |       |       |       |       |       |      |      |      |      | _    |      | _    |       | (<3.0> | _    | 0000       |

| FA28                        | IC1R             | 15:0          | _     | _     |       | _     |       |       |      |      | _    | _    |      |      |      | IC1R  | <3:0>  |      | 0000       |

|                             |                  | 31:16         | _     | _     | _     | _     |       |       |      |      |      | _    |      |      | _    | _     |        | _    | 0000       |

| FA2C                        | IC2R             | 15:0          | _     | _     |       |       |       | _     | _    | _    | _    | _    | _    |      |      |       | <3:0>  |      | 0000       |

|                             |                  | 31:16         |       |       |       |       | _     |       |      | _    | _    |      |      | _    |      | _     | _      |      | 0000       |

| FA30                        | IC3R             | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC3R  | <3:0>  |      | 0000       |

|                             |                  | 31:16         | _     |       | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       | _      | _    | 0000       |

| FA34                        | IC4R             | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC4R  | <3:0>  |      | 0000       |

| -                           | 10.55            | 31:16         | _     | —     | —     | —     | _     | —     | _    | _    | _    | _    | _    | _    | —    | —     | —      | —    | 0000       |

| FA38                        | IC5R             | 15:0          | _     | _     | _     | _     |       | _     | _    | _    | -    | _    |      |      |      | IC5R  | <3:0>  | •    | 0000       |

| FA 40                       |                  | 31:16         |       |       |       | —     |       |       |      | _    |      |      |      |      | —    | —     | —      | —    | 0000       |

| FA48                        | OCFAR            | 15:0          |       | —     | _     | —     | _     | —     |      | -    | _    | _    | -    | _    |      | OCFA  | R<3:0> |      | 0000       |

| FA50                        | U1RXR            | 31:16         | _     | _     | —     | —     | _     | —     | _    |      | _    | _    |      | -    | _    | _     | _      | _    | 0000       |

| FAGU                        | UIKAR            | 15:0          | _     | —     |       | _     |       |       | _    |      | -    | —    |      |      |      | U1RXI | R<3:0> |      | 0000       |

| FA54                        | U1CTSR           | 31:16         | _     | —     | —     | —     |       | —     |      |      |      | —    |      |      | —    | —     | —      | _    | 0000       |

| 1704                        | UTUTUR           | 15:0          | _     | —     | —     | _     | _     | —     |      | _    | _    | —    | _    | _    |      | U1CTS | R<3:0> |      | 0000       |

| FA58                        | U2RXR            | 31:16         | _     | —     | —     | —     | _     | —     | _    | _    | _    | —    | _    | —    | —    | —     | —      | —    | 0000       |

| 1,100                       | <b>U</b> LIVIN   | 15:0          |       | —     | —     | —     |       | —     | —    | —    | —    | —    | —    | —    |      | U2RXI | R<3:0> |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                         |                  |           |       |       |       |       |       |       |      | Bi   | its  |      |      |      |      |      |        |      |            |

|----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| 5004                       | RPG1R            | 31:16     |       | _     | _     | _     | —     | _     | _    |      | _    |      | —    | _    |      | _    | _      | —    | 0000       |

| FC04                       | RPGIR            | 15:0      | —     | —     | _     | _     | _     | —     | —    | —    | —    | _    | _    | —    |      | RPG1 | <3:0>  |      | 0000       |

| 5000                       | DDOOD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | —    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FC98                       | RPG6R            | 15:0      | —     | —     | _     | _     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPG  | 6<3:0> |      | 0000       |

| 5000                       | 00070            | 31:16     | —     | —     | _     | _     | —     | —     | —    | —    | _    | —    | —    | —    | —    | —    | _      | —    | 0000       |

| FC9C                       | RPG7R            | 15:0      | _     | —     | _     | _     | _     | —     | —    | —    | _    | _    | _    | _    |      | RPG7 | /<3:0> |      | 0000       |

| 5040                       | DDOAD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | -    |      | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FCAU                       | RPG8R            | 15:0      | _     | —     | _     | _     | _     | —     | —    |      |      | _    | _    | —    |      | RPG8 | 3<3:0> | •    | 0000       |

| 5044                       | DDOOD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | _    | -    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FCA4                       | RPG9R            | 15:0      | —     | —     | _     | _     | —     | —     | —    | _    | _    | —    | —    | —    |      | RPG9 | <3:0>  |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

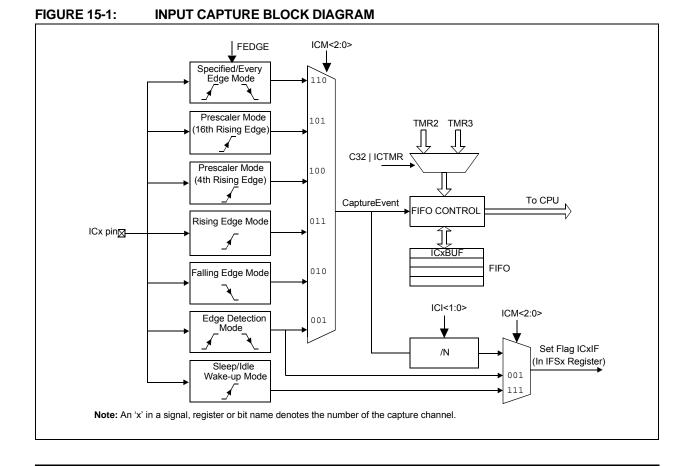

### 15.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 15. "Input Capture"** (DS60001122) of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

The other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

### TABLE 22-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | đ             |       |                                                   |       |       |       |       |         | Bi          | ts       |          |      |      |      |      |      |      | s            |

|-----------------------------|------------------|---------------|-------|---------------------------------------------------|-------|-------|-------|-------|---------|-------------|----------|----------|------|------|------|------|------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                                             | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    | 24/8        | 23/7     | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets   |

| 9100                        | ADC1BUF9         | 31:16<br>15:0 |       |                                                   |       |       |       |       | ADC Res | sult Word 9 | (ADC1BUF | 9<31:0>) |      |      |      |      |      |      | 0000<br>0000 |

| 9110                        | ADC1BUFA         | 31:16<br>15:0 |       | ADC Result Word A (ADC1BUFA<31:0>) 0000 0000 0000 |       |       |       |       |         |             |          |          |      |      |      |      |      |      |              |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |       | ADC Result Word B (ADC1BUFB<31:0>)                |       |       |       |       |         |             |          |          |      |      |      |      |      |      |              |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |       |                                                   |       |       |       |       | ADC Res | ult Word C  | (ADC1BUF | C<31:0>) |      |      |      |      |      |      | 0000<br>0000 |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |       | ADC Result Word D (ADC1BUFD<31:0>)                |       |       |       |       |         |             |          |          |      |      |      |      |      |      |              |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 |       | ADC Result Word E (ADC1BUFE<31:0>) 0000           |       |       |       |       |         |             |          |          |      |      |      |      |      |      |              |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |       | ADC Result Word F (ADC1BUFF<31:0>)                |       |       |       |       |         |             |          |          |      |      |      |      |      |      |              |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for details.

2: For 64-pin devices, the MSB of these bits is not available.

3: For 64-pin devices, only the CSSL30:CSSL0 bits are available.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5         | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|---------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        | —                 | _                 | _                         | _                 | —                 | _                 | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | —                         | —                 | —                 | —                 | —                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0                       | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15.0         | —                 | FILHIT<4:0>       |                           |                   |                   |                   |                  |                  |  |  |

| 7:0          | U-0               | R-1               | R-0                       | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7.0          | _                 |                   | ICODE<6:0> <sup>(1)</sup> |                   |                   |                   |                  |                  |  |  |

#### REGISTER 23-4: C1VEC: CAN INTERRUPT CODE REGISTER

#### Legend:

| R = Rea   | dable bit | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-----------|-----------|------------------|--------------------------|--------------------|--|

| -n = Valu | le at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-13 Unimplemented: Read as '0'

```

bit 12-8 FILHIT<4:0>: Filter Hit Number bit

11111 = Reserved

10000 = Reserved

01111 = Filter 15

00000 = Filter 0

bit 7

Unimplemented: Read as '0'

ICODE<6:0>: Interrupt Flag Code bits<sup>(1)</sup>

bit 6-0

1111111 = Reserved

1001001 = Reserved

1001000 = Invalid message received (IVRIF)

1000111 = CAN module mode change (MODIF)

1000110 = CAN timestamp timer (CTMRIF)

1000101 = Bus bandwidth error (SERRIF)

1000100 = Address error interrupt (SERRIF)

1000011 = Receive FIFO overflow interrupt (RBOVIF)

1000010 = Wake-up interrupt (WAKIF)

1000001 = Error Interrupt (CERRIF)

1000000 = No interrupt

0111111 = Reserved

0010000 = Reserved

0001111 = FIFO15 Interrupt (C1FSTAT<15> set)

0000000 = FIFO0 Interrupt (C1FSTAT<0> set)

```

| REGIST  | TER 23-17: C1FIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' ('n' = 0 THROUGH 15)<br>(CONTINUED)                                                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9   | <b>TXHALFIF:</b> FIFO Transmit FIFO Half Empty Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is $\leq$ half full<br>0 = FIFO is > half full<br><u>TXEN = 0:</u> (FIFO configured as a receive buffer) |

| bit 8   | Unused, reads '0'<br><b>TXEMPTYIF:</b> Transmit FIFO Empty Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is empty<br>0 = FIFO is not empty, at least 1 message queued to be transmitted               |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>Unused, reads '0'                                                                                                                                                                                      |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                       |

| bit 3   | <b>RXOVFLIF:</b> Receive FIFO Overflow Interrupt Flag bit<br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                                                                        |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = Overflow event has occurred<br>0 = No overflow event occured                                                                                                                                       |

| bit 2   | RXFULLIF: Receive FIFO Full Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                                                                    |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = FIFO is full<br>0 = FIFO is not full                                                                                                                                                               |

| bit 1   | <b>RXHALFIF:</b> Receive FIFO Half Full Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                                                        |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = FIFO is ≥ half full<br>0 = FIFO is < half full                                                                                                                                                     |

| bit 0   | RXNEMPTYIF: Receive Buffer Not Empty Interrupt Flag bit <sup>(1)</sup><br><u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>Unused, reads '0'                                                                                                           |

|         | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>1 = FIFO is not empty, has at least 1 message<br>0 = FIFO is empty                                                                                                                                     |

| Note 1  | This bit is read-only and reflects the status of the EIEO                                                                                                                                                                                                        |

Note 1: This bit is read-only and reflects the status of the FIFO.

### 25.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

This data sheet summarizes the features Note: of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

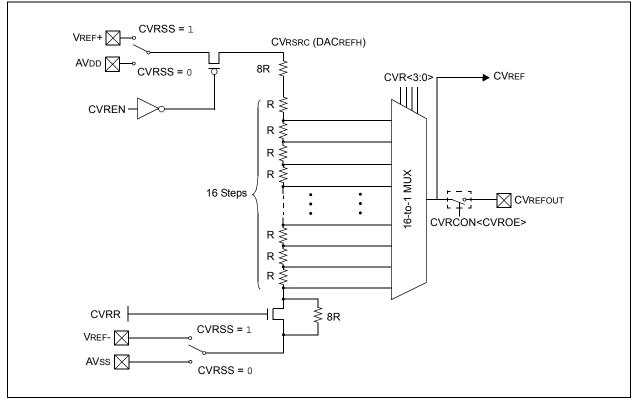

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 25-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The CVREF module has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

#### FIGURE 25-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

| REGIST  | ER 26-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)                                          |

|---------|----------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                           |

|         | 1 = Edge 1 must occur before Edge 2 can occur                                                |

|         | 0 = No edge sequence is needed                                                               |

| bit 9   | <b>IDISSEN:</b> Analog Current Source Control bit <sup>(2)</sup>                             |

|         | 1 = Analog current source output is grounded                                                 |

|         | 0 = Analog current source output is not grounded                                             |

| bit 8   | CTTRIG: Trigger Control bit                                                                  |

|         | 1 = Trigger output is enabled                                                                |

|         | 0 = Trigger output is disabled                                                               |

| bit 7-2 | ITRIM<5:0>: Current Source Trim bits                                                         |

|         | 011111 = Maximum positive change from nominal current                                        |

|         | 011110                                                                                       |

|         |                                                                                              |

|         |                                                                                              |

|         | 000001 = Minimum positive change from nominal current                                        |

|         | 000000 = Nominal current output specified by IRNG<1:0>                                       |

|         | 111111 = Minimum negative change from nominal current                                        |

|         |                                                                                              |

|         | •                                                                                            |

|         | 100010                                                                                       |

|         | 100001 = Maximum negative change from nominal current                                        |

| bit 1-0 | IRNG<1:0>: Current Range Select bits <sup>(3)</sup>                                          |

|         | 11 = 100 times base current                                                                  |

|         | 10 = 10 times base current                                                                   |

|         | 01 = Base current level                                                                      |

|         | 00 = 1000 times base current <sup>(4)</sup>                                                  |

| Nets 4  | When this bit is set for Dules Delay Operation, the EDOOOEL (0.0), bits must be act to (1.1) |

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

#### 32.1 DC Characteristics

#### TABLE 32-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | Voo Bango                              | Temp. Range    | Max. Frequency                          |  |

|----------------|----------------------------------------|----------------|-----------------------------------------|--|

|                | VDD Range<br>(in Volts) <sup>(1)</sup> | (in °C)        | PIC32MX1XX/2XX/5XX 64/100-pin<br>Family |  |

| MDC5           | VBOR-3.6V                              | -40°C to +85°C | 50 MHz                                  |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for BOR values.

#### TABLE 32-2: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS                  |                        |      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |  |  |

|-------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Parameter<br>No.                    | Typical <sup>(3)</sup> | Max. | Units                                                                                                                                           | Conditions |  |  |

| Operating Current (IDD) (Note 1, 2) |                        |      |                                                                                                                                                 |            |  |  |

| MDC24                               | 25                     | 40   | mA                                                                                                                                              | 50 MHz     |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

2: The test conditions for IDD measurements are as follows: