Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 49                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 28x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

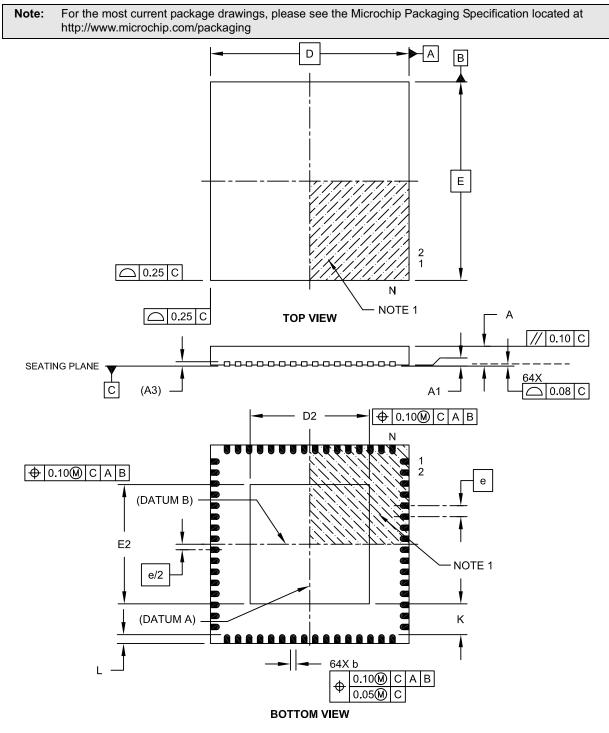

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f512h-50i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 31:24        |                   |                   |                   | NVMKE             | Y<31:24>          |                   |                  |                  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 23:16        |                   |                   |                   | NVMKE             | Y<23:16>          |                   |                  |                  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 15:8         |                   |                   |                   | NVMK              | EY<15:8>          |                   |                  |                  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |

| 7:0          |                   |                   |                   | NVMK              | EY<7:0>           |                   |                  |                  |

# REGISTER 6-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

# Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **NVMKEY<31:0>:** Unlock Register bits These bits are write-only, and read as '0' on any read.

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

## REGISTER 6-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | NVMADI            | DR<31:24>         |                   |                  |                  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | NVMADI            | DR<23:16>         |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | NVMAD             | DR<15:8>          |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | NVMAE             | )DR<7:0>          |                   |                  |                  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMADDR<31:0>: Flash Address bits Bulk/Chip/PFM Erase: Address is ignored Page Erase: Address identifies the page to erase Row Program: Address identifies the row to program Word Program: Address identifies the word to program

# 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The PIC32 USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- · Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | -                 |                   | _                 | -                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | -                 |                   | _                 | -                 | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | _                 | -                 |                   | _                 | -                 |                  | _                |

| 7.0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7:0          | ID                | —                 | LSTATE            | _                 | SESVD             | SESEND            |                  | VBUSVD           |

# REGISTER 10-3: U1OTGSTAT: USB OTG STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a Type-B cable has been plugged into the USB receptacle

- 0 = A Type-A cable has been plugged into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has been stable for the previous 1 ms

- 0 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has not been stable for the previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 **SESEND:** B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 | _                 | —                 |                   | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | —                 | —                 | —                 |                   | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | —                 | —                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

# REGISTER 10-4: U1OTGCON: USB OTG CONTROL REGISTER

# Legend:

bit

| Logona            |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| 7 | DPI | PUL | UP: | D+ I | Pull-Up | Enable | e bit |  |

|---|-----|-----|-----|------|---------|--------|-------|--|

|   |     | -   |     |      |         |        |       |  |

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

# bit 6 **DMPULUP:** D- Pull-Up Enable bit

- to **DMPOLOP:** D- Pull-Op Enable bit

- 1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

#### bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

1 = D+ data line pull-down resistor is enabled

0 = D+ data line pull-down resistor is disabled

## bit 4 **DMPULDWN:** D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

- bit 3 **VBUSON:** VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 **OTGEN:** OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

#### bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

- bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|

| 24.24        | U-0                   | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | -                 | —                     | —                |

| 23:16        | U-0                   | U-0              |

| 23.10        | _                 | _                 | _                 | _                 |                   |                   |                       | —                |

| 15:8         | U-0                   | U-0              |

| 10.0         | _                 | _                 | _                 | _                 | _                 | _                 | _                     | —                |

|              | R/W-0                 | R/W-0            |

| 7:0          | DTOFF             |                   |                   | DTOFE             | DENIGEE           | 0001055           | CRC5EE <sup>(1)</sup> | DIDEE            |

|              | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | EOFEE <sup>(2)</sup>  | PIDEE            |

|              |                   |                   |                   |                   |                   |                   |                       |                  |

#### REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEE: Bit Stuff Error Interrupt Enable bit

- 1 = BTSEF interrupt enabled

- 0 = BTSEF interrupt disabled

- bit 6 **BMXEE:** Bus Matrix Error Interrupt Enable bit

- 1 = BMXEF interrupt enabled

- 0 = BMXEF interrupt disabled

- bit 5 **DMAEE:** DMA Error Interrupt Enable bit

- 1 = DMAEF interrupt enabled

- 0 = DMAEF interrupt disabled

- bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

- 1 = BTOEF interrupt enabled

- 0 = BTOEF interrupt disabled

- bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt enabled

- 0 = DFN8EF interrupt disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt enabled

- 0 = CRC16EF interrupt disabled

- bit 1 **CRC5EE:** CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt enabled

- 0 = CRC5EF interrupt disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt enabled

- 0 = EOF interrupt disabled

- bit 0 **PIDEE:** PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt enabled

- 0 = PIDEF interrupt disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | —                 | —                 | -                 | -                 | —                | -                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | —                 | —                 | —                 | -                 |                   | —                | -                |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | _                 | —                 | —                 | —                 | _                 | _                 | —                | -                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | BDTPTRH<23:16>    |                   |                   |                   |                   |                  |                  |  |  |  |

# REGISTER 10-18: U1BDTP2: USB BDT PAGE 2 REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** BDT Base Address bits This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

| ILE OIO II   | CONTER 10-13. OTBUTF3. OSB BUT FAGE 3 REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                              | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 21.24        | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                                                | —                 | —                 |                   | _                 | _                 |                  | —                |  |  |  |

| 00.40        | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | -                                              | _                 | —                 | -                 | —                 | _                 | -                | —                |  |  |  |

| 15:8         | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | -                                              | _                 | —                 | -                 | —                 | _                 | -                | —                |  |  |  |

| 7:0          | R/W-0                                          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                                                | BDTPTRU<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |

# REGISTER 10-19: U1BDTP3: USB BDT PAGE 3 REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | _                 | —                 | _                 | _                 | _                | -                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   | _                 |                   | _                 | _                 | -                 | -                | -                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         |                   | _                 |                   | _                 | _                 | -                 | -                | -                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |  |  |  |

# REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| 9                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device enabled

- 0 = Direct connection to a low-speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

#### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive enabled

- 0 = Endpoint n receive disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit enabled

- 0 = Endpoint n transmit disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake enabled

- 0 = Endpoint Handshake disabled (typically used for isochronous endpoints)

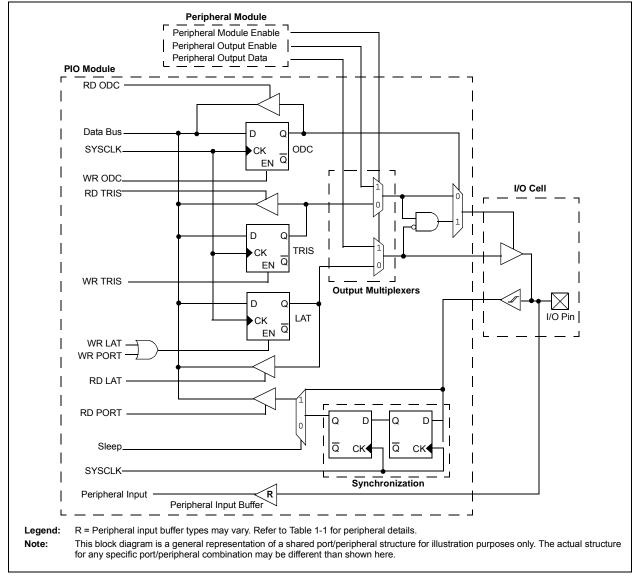

# 11.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate functions. These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

The following are the key features of this module:

- · Individual output pin open-drain enable or disable

- Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt

when change in pin state is detected

- Operation during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

Figure 11-1 illustrates a block diagram of a typical multiplexed I/O port.

# TABLE 11-16: PORTG REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |              | В            | its          |              |      |      |                    |                    |      |      |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|------|------|--------------------|--------------------|------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3               | 18/2               | 17/1 | 16/0 | All<br>Resets |

| 6600                        | ANSELG                          | 31:16     | _     | _     | —     | _     | _     | —     | —            | _            | —            | —            | _    | —    | —                  | —                  |      | —    | 0000          |

| 0000                        | ANOLLO                          | 15:0      | —     | —     | —     | —     | —     | —     | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      | —    | —    | —                  | —                  | —    | —    | 03C0          |

| 6610                        | TRISG                           | 31:16     | —     | _     | —     | —     | _     | _     | _            | —            | _            | —            | _    | _    | _                  | —                  | _    | _    | 0000          |

| 0010                        | TRIBG                           | 15:0      | _     | _     | _     | _     | _     | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | —    | TRISG3             | TRISG2             | _    | —    | 03CC          |

| 6620                        | PORTG                           | 31:16     | -     |       |       | _     |       |       | _            | _            |              | —            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0020                        | FURIG                           | 15:0      | _     | _     | _     | _     | _     | _     | RG9          | RG8          | RG7          | RG6          | _    | —    | RG3 <sup>(2)</sup> | RG2 <sup>(2)</sup> | _    | —    | xxxx          |

| 6630                        | LATG                            | 31:16     | -     | -     | -     | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 0030 LAIG                   | LAIG                            | 15:0      | Ι     | -     | -     |       |       |       | LATG9        | LATG8        | LATG7        | LATG6        | —    | —    | LATG3              | LATG2              | —    | —    | xxxx          |

| 6640                        | ODCG                            | 31:16     | Ι     | -     | -     |       |       |       | —            | —            | -            | —            | —    | —    | —                  | —                  | —    | —    | 0000          |

| 0040                        | ODCG                            | 15:0      | -     | -     | -     | -     |       |       | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | _    | ODCG3              | ODCG2              | _    | _    | 0000          |

| 6650                        | CNPUG                           | 31:16     | -     | -     | -     | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 0030                        | CINFUG                          | 15:0      | -     | -     | -     | -     |       |       | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _    | _    | CNPUG3             | CNPUG2             | _    | _    | 0000          |

| 6660                        | CNPDG                           | 31:16     | -     | -     | -     | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 0000                        | CINF DG                         | 15:0      | -     | -     | -     | -     |       |       | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | _    | _    | CNPDG3             | CNPDG2             | _    | _    | 0000          |

| 6670                        | CNCONG                          | 31:16     | -     | -     | -     | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 0070                        | CINCOING                        | 15:0      | ON    | -     | SIDL  | -     |       |       | _            | _            |              | —            | _    | _    | —                  | _                  | _    | _    | 0000          |

| 6680                        | CNENG                           | 31:16     | —     | _     | _     | _     | _     |       | —            | —            |              | —            | —    | _    | —                  | —                  | —    | _    | 0000          |

| 0000                        | GNEING                          | 15:0      | —     | _     | _     | _     |       | -     | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       | —    | —    | CNIEG3             | CNIEG2             |      | —    | 0000          |

|                             |                                 | 31:16     | —     | _     | —     | —     | _     | _     | _            | _            | _            | —            | _    | —    | _                  | _                  | —    | —    | 0000          |

| 6690                        | CNSTATG                         | 15:0      | _     | _     | _     | _     | _     | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | _    | _    | CN<br>STATG3       | CN<br>STATG2       | _    | _    | 0000          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This bit is only available on devices without a USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | —                 | _                 | _                 | —                 | —                 | —                | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                 | _                 | _                 | —                 | -                 | —                | _                |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |  |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |  |

## REGISTER 19-1: UxMODE: UARTx MODE REGISTER

# Legend:

| Legend.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

#### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                  | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 00:16        | U-0                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                  | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 45.0         | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | 15:8 DATAOUT<15:8> |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | DATAOUT<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

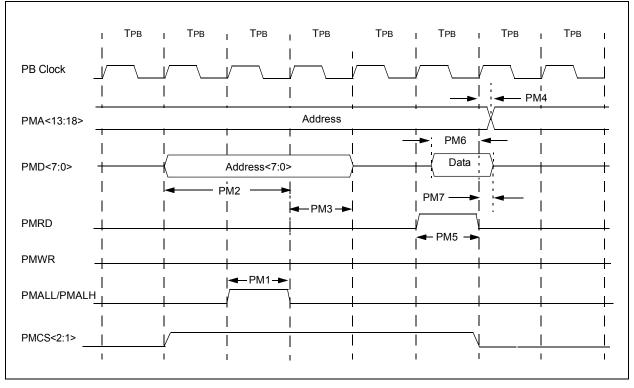

## REGISTER 20-4: PMDOUT: PARALLEL PORT OUTPUT DATA REGISTER

# Legend:

| 9                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-0 DATAOUT<15:0>: Port Data Output bits

This register is used for Read operations in the Enhanced Parallel Slave mode and Write operations for Dual Buffer Master mode.

In Dual Buffer Master mode, the DUALBUF bit (PMPCON<17>) = 1, a write to the MSB triggers the transaction on the PMP port. When MODE16 = 1, MSB = DATAOUT<15:8>. When MODE16 = 0, MSB = DATAOUT<7:0>.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | 15:8 DATAIN<15:8> |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | DATAIN            | <7:0>             |                   |                  |                  |  |  |

#### REGISTER 20-5: PMDIN: PARALLEL PORT INPUT DATA REGISTER

# Legend:

| 9                 |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 DATAIN<15:0>: Port Data Input bits

This register is used for both Parallel Master Port mode and Enhanced Parallel Slave mode. In Parallel Master mode, a write to the MSB triggers the write transaction on the PMP port. Similarly, a read to the MSB triggers the read transaction on the PMP port. When MODE16 = 1, MSB = DATAIN<15:8>. When MODE16 = 0, MSB = DATAIN<7:0>.

Note: This register is not used in Dual Buffer Master mode (i.e., DUALBUF bit (PMPCON<17>) = 1).

**Note:** In Master mode, a read will return the last value written to the register. In Slave mode, a read will return indeterminate results.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |  |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-------------------|------------------|--------------------------|--|

| 31:24        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                      |  |

| 31.24        | _                 | _                    |                   | _                 | _                 |                   | —                | —                        |  |

| 22:16        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                      |  |

| 23:16        | _                 | _                    | _                 | _                 | _                 | -                 | _                | —                        |  |

| 45.0         | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                    |  |

| 15:8         | PTEN<1            | 5:14> <sup>(1)</sup> | PTEN<13:8>        |                   |                   |                   |                  |                          |  |

| 7.0          | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                    |  |

| 7:0          | PTEN<7:2>         |                      |                   |                   |                   |                   |                  | PTEN<1:0> <sup>(2)</sup> |  |

# REGISTER 20-6: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

# Legend:

| Legend.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Write '0'; ignore read

- bit 15-14 **PTEN<15:14>:** PMCSx Address Port Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS2 and PMCS1<sup>(1)</sup>

- 0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits

- 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15/PMA14 or CS2/CS1 is selected by the CSF<1:0> bits (PMCON<7:6>).

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by the ADRMUX<1:0> bits in the PMCON register.

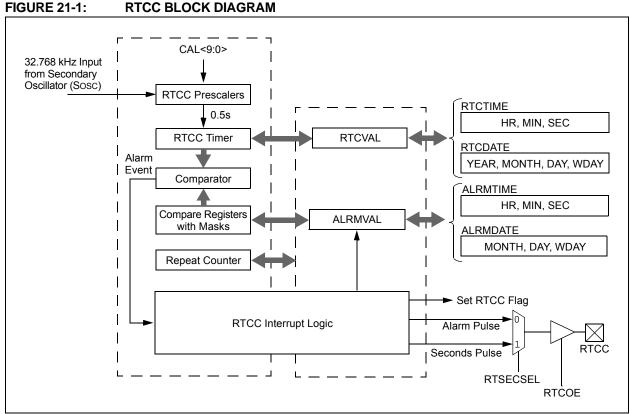

#### 21.0 **REAL-TIME CLOCK AND** CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available the Microchip web from site (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time.

The following are the key features of this module:

- · Time: hours. minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- · Provides calendar: Weekday, date, month and year

- · Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- · User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- · Requirements: External 32.768 kHz clock crystal

- · Alarm pulse or seconds clock output on RTCC pin

# RTCC BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | _                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        | —                 | —                 | TXBO              | TXBP              | RXBP              | TXWARN            | RXWARN           | EWARN            |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | TERRCI            | NT<7:0>           |                   |                  |                  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | RERRC             | NT<7:0>           |                   |                  |                  |

## REGISTER 23-5: C1TREC: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-22 Unimplemented: Read as '0'

bit 21 **TXBO:** Transmitter in Error State Bus OFF (TERRCNT  $\geq$  256)

- bit 20 **TXBP:** Transmitter in Error State Bus Passive (TERRCNT ≥ 128)

- bit 19 **RXBP:** Receiver in Error State Bus Passive (RERRCNT  $\geq$  128)

bit 18 **TXWARN:** Transmitter in Error State Warning (128 > TERRCNT ≥ 96)

bit 17 **RXWARN:** Receiver in Error State Warning (128 > RERRCNT  $\ge$  96)

bit 16 EWARN: Transmitter or Receiver is in Error State Warning

- bit 15-8 TERRCNT<7:0>: Transmit Error Counter

- bit 7-0 RERRCNT<7:0>: Receive Error Counter

# REGISTER 23-6: C1FSTAT: CAN FIFO STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | —                 |                   | _                 | _                 | _                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | FIFOIP15          | FIFOIP14          | FIFOIP13          | FIFOIP12          | FIFOIP11          | FIFOIP10          | FIFOIP9          | FIFOIP8          |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | FIFOIP7           | FIFOIP6           | FIFOIP5           | FIFOIP4           | FIFOIP3           | FIFOIP2           | FIFOIP1          | FIFOIP0          |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 FIFOIP<15:0>: FIFOx Interrupt Pending bits

1 = One or more enabled FIFO interrupts are pending

0 = No FIFO interrupts are pending

# TABLE 27-2: PERIPHERAL MODULE DISABLE REGISTER SUMMARY

| ess                         |                  | e         |       | Bits  |       |        |        |        |        |                      |      |      |      |       |       |        |        |        |                           |

|-----------------------------|------------------|-----------|-------|-------|-------|--------|--------|--------|--------|----------------------|------|------|------|-------|-------|--------|--------|--------|---------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12  | 27/11  | 26/10  | 25/9   | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets <sup>(1)</sup> |

|                             | PMD1             | 31:16     | _     | —     | —     | —      | —      |        |        | —                    | _    | —    | _    | —     |       | —      | —      |        | 0000                      |

| F240                        | FINDT            | 15:0      |       |       | —     | CVRMD  | Ι      |        |        | CTMUMD               | Ι    | —    |      | —     |       | —      | —      | AD1MD  | 0000                      |

| 5050                        | PMD2             | 31:16     | _     | -     | —     | —      | _      | -      |        | —                    | _    | _    |      | _     | -     | _      | —      |        | 0000                      |

| F250                        | FINDZ            | 15:0      |       |       | —     | —      | Ι      |        |        | _                    | Ι    | —    |      | —     |       | CMP3MD | CMP2MD | CMP1MD | 0000                      |

| 5000                        | PMD3             | 31:16     | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | —    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000                      |

| F260                        | FINDS            | 15:0      | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | —    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000                      |

| F270                        | PMD4             | 31:16     | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | —    | _     | —     | _      | —      | _      | 0000                      |

| F270                        | FIVID4           | 15:0      | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | —    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000                      |

| 5000                        | PMD5             | 31:16     | -     |       | _     | CAN1MD | -      | —      | —      | USBMD <sup>(1)</sup> |      | _    | _    | _     | —     | _      | I2C1MD | I2C1MD | 0000                      |

| F280                        | FINDS            | 15:0      | -     |       | _     | —      | SPI4MD | SPI3MD | SPI2MD | SPI1MD               |      | _    | _    | U5MD  | U4MD  | U3MD   | U2MD   | U1MD   | 0000                      |

| 5000                        | PMD6             | 31:16     | -     |       | _     | —      | -      | —      | —      | —                    |      | _    | _    | _     | —     | _      | —      | PMPMD  | 0000                      |

| F290                        | FIVIDO           | 15:0      | —     | _     | —     | —      | _      | _      | -      | —                    | _    | —    | _    | _     | _     | —      | REFOMD | RTCCMD | 0000                      |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on devices with a USB module.

© 2014-2016 Microchip Technology Inc.

| DC CHARACT                                                         | ERISTICS               |      | (unless oth | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                 |               |  |  |  |

|--------------------------------------------------------------------|------------------------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--|--|--|

| Parameter<br>No.                                                   | Typical <sup>(2)</sup> | Max. | Units       | Units Conditions                                                                                                                                                                                   |                 |               |  |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Notes 1, 4) |                        |      |             |                                                                                                                                                                                                    |                 |               |  |  |  |

| DC30a                                                              | 1.5                    | 5    | mA          | 4 MHz (Note 3)                                                                                                                                                                                     |                 |               |  |  |  |

| DC31a                                                              | 3                      | 8    | mA          |                                                                                                                                                                                                    | 10 MHz          |               |  |  |  |

| DC32a                                                              | 5                      | 12   | mA          |                                                                                                                                                                                                    | 20 MHz (Note 3) |               |  |  |  |

| DC33a                                                              | 6.5                    | 15   | mA          |                                                                                                                                                                                                    | 30 MHz (Note 3) |               |  |  |  |

| DC34a                                                              | 8                      | 20   | mA          |                                                                                                                                                                                                    | 40 MHz          |               |  |  |  |

| DC37a                                                              | 75                     | 100  | μA          | -40°C                                                                                                                                                                                              |                 | LPRC (31 kHz) |  |  |  |

| DC37b                                                              | 180                    | 250  | μA          | +25°C                                                                                                                                                                                              | 3.3V            | (Note 3)      |  |  |  |

| DC37c                                                              | 280                    | 380  | μA          | +85°C                                                                                                                                                                                              |                 |               |  |  |  |

#### TABLE 31-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** The test conditions for IIDLE current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1  $\,$

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: IIDLE electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

| AC CHA        | RACTERI       | ISTICS                                                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |             |            |                                              |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|----------------------------------------------|--|

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                                   |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                                                                                                               |                        | 40<br>40    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)                |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                                                                                                                     | —                      | 10          | MHz        | XT (Note 4)                                  |  |

| OS12          |               |                                                                                                                  | 4                                                                                                                                                                                                                                                                                     | —                      | 10          | MHz        | XTPLL<br>(Notes 3,4)                         |  |

| OS13          |               |                                                                                                                  | 10                                                                                                                                                                                                                                                                                    | —                      | 25          | MHz        | HS (Note 5)                                  |  |

| OS14          |               |                                                                                                                  | 10                                                                                                                                                                                                                                                                                    | —                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                         |  |

| OS15          |               |                                                                                                                  | 32                                                                                                                                                                                                                                                                                    | 32.768                 | 100         | kHz        | Sosc (Note 4)                                |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                                                                                                                                                                                                                                                     | _                      | _           | —          | See parameter<br>OS10 for Fosc<br>value      |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                                                                                                                           | —                      | —           | ns         | EC (Note 4)                                  |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | _                                                                                                                                                                                                                                                                                     | —                      | 0.05 x Tosc | ns         | EC (Note 4)                                  |  |

| OS40          | Tost          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                                                                                                                     | 1024                   | _           | Tosc       | (Note 4)                                     |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | —                                                                                                                                                                                                                                                                                     | 2                      | —           | ms         | (Note 4)                                     |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             |                                                                                                                                                                                                                                                                                       | 12                     |             | mA/V       | VDD = 3.3V,<br>TA = +25°C<br><b>(Note 4)</b> |  |

# TABLE 31-17: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

2: Instruction cycle period (TcY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

**3:** PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

4: This parameter is characterized, but not tested in manufacturing.

# TABLE 31-37: PARALLEL SLAVE PORT REQUIREMENTS

| AC CH         | ARACTE       | RISTICS                                                                          | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |            |  |

|---------------|--------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|

| Para<br>m.No. | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                                | Тур. | Max. | Units | Conditions |  |

| PS1           | TdtV2wr<br>H | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                                  |      |      | ns    | _          |  |