Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f512h-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                     | Pin N                    | umber           |             |                |                                                          |  |  |  |  |

|---------------------|--------------------------|-----------------|-------------|----------------|----------------------------------------------------------|--|--|--|--|

| Pin Name            | 64-pin<br>QFN/<br>TQFP   | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                              |  |  |  |  |

| PMA2                | 8                        | 14              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA3                | 6                        | 12              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA4                | 5                        | 11              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA5                | 4                        | 10              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA6                | 16                       | 29              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA7                | 22                       | 28              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA8                | 32                       | 50              | 0           | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) or |  |  |  |  |

| PMA9                | 31                       | 49              | 0           | TTL/ST         | Address/Data (Multiplexed Master modes)                  |  |  |  |  |

| PMA10               | 28                       | 42              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA11               | 27                       | 41              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA12               | 24                       | 35              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA13               | 23                       | 34              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA14               | 45                       | 71              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMA15               | 44                       | 70              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMCS1               | 45                       | 71              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMCS2               | 44                       | 70              | 0           | TTL/ST         |                                                          |  |  |  |  |

| PMD0                | 60                       | 93              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD1                | 61                       | 94              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD2                | 62                       | 98              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD3                | 63                       | 99              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD4                | 64                       | 100             | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD5                | 1                        | 3               | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD6                | 2                        | 4               | I/O         | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) o  |  |  |  |  |

| PMD7                | 3                        | 5               | I/O         | TTL/ST         | Address/Data (Multiplexed Master modes)                  |  |  |  |  |

| PMD8                | _                        | 90              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD9                |                          | 89              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD10               | _                        | 88              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD11               | _                        | 87              | I/O         | TTL/ST         |                                                          |  |  |  |  |

| PMD12               | —                        | 79              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |

| PMD13               | —                        | 80              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |

| PMD14               | —                        | 83              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |

| PMD15               | —                        | 84              | I/O         | TTL/ST         | 1                                                        |  |  |  |  |

| PMRD                | 53                       | 82              | 0           | —              | Parallel Master Port Read Strobe                         |  |  |  |  |

| PMWR                | 52                       | 81              | 0           | —              | Parallel Master Port Write Strobe                        |  |  |  |  |

| VBUS <sup>(2)</sup> | 34                       | 54              | Ι           | Analog         | USB Bus Power Monitor                                    |  |  |  |  |

| •                   | CMOS = CM<br>ST = Schmit | t Trigger inp   | ut with (   | CMOS level     | ls TTL = TTL input buffer P = Power                      |  |  |  |  |

|                     | -                        | -               |             |                | t a USB module.<br>USB module.                           |  |  |  |  |

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

## 2.9 Considerations When Interfacing to Remotely Powered Circuits

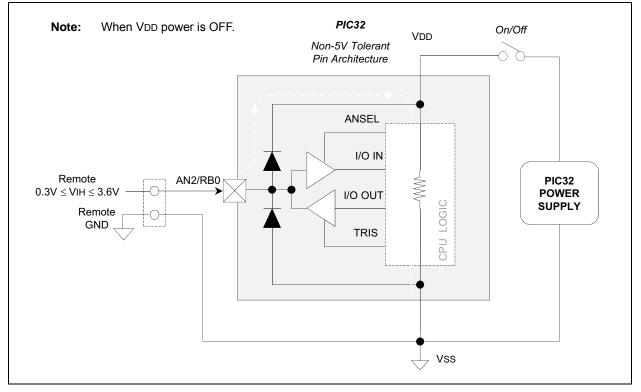

#### 2.9.1 NON-5V TOLERANT INPUT PINS

A quick review of the absolute maximum rating section in **31.0** "**40 MHz Electrical Characteristics**" will indicate that the voltage on any non-5v tolerant pin may not exceed AVDD/VDD + 0.3V. Figure 2-5 shows an example of a remote circuit using an independent power source, which is powered while connected to a PIC32 non-5V tolerant circuit that is not powered.

#### FIGURE 2-5: PIC32 NON-5V TOLERANT CIRCUIT EXAMPLE

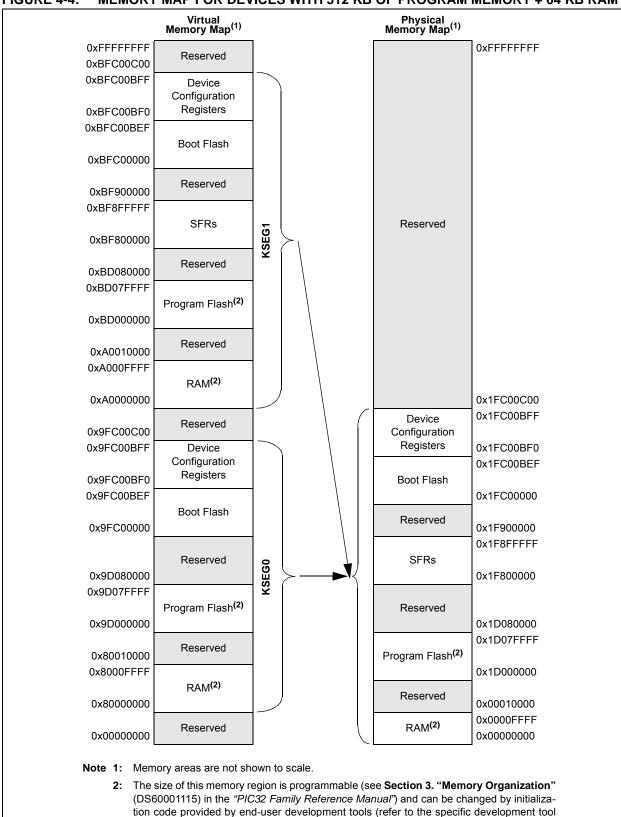

#### FIGURE 4-4: MEMORY MAP FOR DEVICES WITH 512 KB OF PROGRAM MEMORY + 64 KB RAM

© 2014-2016 Microchip Technology Inc.

documentation for information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 | —                 | _                 |                   | IP3<2:0>          |                   | IS3<             | :1:0>            |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | —                 | —                 | _                 | IP2<2:0>          |                   |                   | IS2<             | 1:0>             |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | —                 | —                 | —                 |                   | IP1<2:0>          |                   | IS1<             | :1:0>            |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 |                   | IP0<2:0>          |                   | IS0<             | :1:0>            |

#### REGISTER 5-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-29 Unimplemented: Read as '0'

000 = Interrupt is disabled

bit 25-24 **IS3<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 23-21 **Unimplemented:** Read as '0'

bit 20-18 IP2<2:0>: Interrupt Priority bits

```

111 = Interrupt priority is 7

```

```

•

•

• 010 - Interrupt priority

```

- 010 = Interrupt priority is 2

- 001 = Interrupt priority is 1 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

- bit 12-10 IP1<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

- 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

Note: This register represents a generic definition of the IPCx register. Refer to Table 5-1 for the exact bit definitions.

NOTES:

| LEGISTER 5-10. DETREGIZE DWA CHANNEL & CELE-SIZE REGISTER |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

|-----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range                                              | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 01.04                                                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24                                                     |                   | —                 | _                 | _                 | —                 | —                 | -                | —                |  |  |

| 22:16                                                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16                                                     | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |

| 45.0                                                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8                                                      | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0                                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0                                                       |                   |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |  |  |

#### REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

1111111111111111 = 65,535 bytes transferred on an event

#### **REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | -                 | _                 |                   |                  | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

#### Note: When in Pattern Detect mode, this register is reset on a pattern detect.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | —                 | —                 | —                 | -                 | -                 | —                | -                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | —                 | —                 | -                 |                   | —                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | _                 | —                 | —                 | —                 | _                 | _                 | —                | -                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |

#### REGISTER 10-18: U1BDTP2: USB BDT PAGE 2 REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** BDT Base Address bits This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

| ILE OIO II   |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   | —                 | —                 |                   | _                 | _                 |                  | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | -                 | _                 | —                 | -                 | —                 | _                 | -                | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | -                 | _                 | —                 | -                 | —                 | _                 | -                | —                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | BDTPTRU<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 10-19: U1BDTP3: USB BDT PAGE 3 REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

#### TABLE 11-1: INPUT PIN SELECTION

| [pin name]R SFR      | [pin name]R bits                                                                                                                                                                                                                                                                                                                                                                                                                               | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT3R                | INT3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0000 = RPD2<br>0001 = RPG8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| T2CKR                | T2CKR<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0010 = RPF4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IC3R                 | IC3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| U1RXR                | U1RXR<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0101 = RPB9<br>0110 = RPB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| U2RXR                | U2RXR<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0111 = RPC14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| U5CTSR               | U5CTSR<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1000 = RPB5 <sup>(7)</sup><br>1001 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SDI3R                | SDI3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1010 = RPC1 <sup>(3)</sup><br>1011 = RPD14 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDI4R                | SDI4R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1100 = RPG1 <sup>(3)</sup><br>1101 = RPA14 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| REFCLKIR             | REFCLKIR<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1110 = Reserved<br>1111 = RPF2 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INT4R                | INT4R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0000 <b>= RPD3</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| T5CKR                | T5CKR<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0001 = RPG7<br>0010 = RPF5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0011 = RPD11<br>0100 = RPF0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0101 = RPB1<br>0110 = RPE5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0111 = RPC13<br>1000 = RPB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1001 = RPF12 <sup>(3)</sup><br>1010 = RPC4 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1011 = RPD15 <sup>(3)</sup><br>1100 = RPG0 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1101 = RPA15 <sup>(3)</sup><br>1110 = RPF2 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| C1RXR <sup>(5)</sup> | C1RXR<3:0> <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                      | 1110 = R(F2(2)<br>1111 = RPF7 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INT2R                | INT2R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0000 = RPD9<br>0001 = RPG6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| T4CKR                | T4CKR<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0010 = RPB8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IC2R                 | IC2R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IC5R                 | IC5R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0101 = RPB0<br>0110 = RPE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| U1CTSR               | U1CTSR<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0111 = RPB7<br>1000 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| U2CTSR               | U2CTSR<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1001 = RPF12 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SS1R                 | SS1R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1010 = RPD12 <sup>(3)</sup><br>1011 = RPF8 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SS3R                 | SS1R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1100 = RPC3 <sup>(3)</sup><br>1101 = RPE9 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SS3R                 | SS3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1110 = RPD14 <sup>(3)</sup><br>1111 = RPB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                      | INT3R           T2CKR           IC3R           U1RXR           U2RXR           U5CTSR           SDI3R           SDI4R           REFCLKIR           INT4R           U3RXR           U3RXR           U4CTSR           SDI1R           SDI2R           U4CTSR           SDI2R           U1RXR <sup>(5)</sup> INT2R           IC2R           U2RXR           U2RXR           SDI2R           U1CTSR           U2CTSR           SS1R           SS3R | INT3R         INT3R           IZCKR         T2CKR           IC3R         IC3R           IC3R         IC3R           U1RXR         U1RXR           U2RXR         U2RXR           U5CTSR         U5CTSR           SDI3R         SDI3R           SDI3R         SDI3R           SDI4R         SDI4R           SDI4R         SDI4R           SDI4R         SDI4R           INT4R         INT4R           INT4R         INT4R           INT4R         INT4R           INT4R         INT4R           INT4R         IAT4           INT4R         IAT4           IV3RXR         U3RXR           U3RXR         U3RXR           U4CTSR         U4CTSR           U4CTSR         SDI1R           U4CTSR         SDI2R           SDI2R         SDI2R           SDI2R         SDI2R           SDI2R         SDI2R           INT2R         INT2R           INT2R         IC2R           IC2R         IC2R           IC2R         IC2R           IC5R         IC5R           IV1CTSR |

Note 1: This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

**3:** This selection is not available on 64-pin devices.

4: This selection is not available when USBID functionality is used on USB devices.

5: This selection is not available on devices without a CAN module.

6: This selection is not available on USB devices.

7: This selection is not available when VBUSON functionality is used on USB devices.

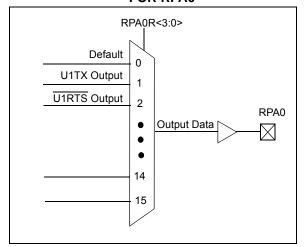

#### 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

### 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

#### 11.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

#### 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

NOTES:

#### REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 17 SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)

- 1 = Frame synchronization pulse coincides with the first bit clock

- 0 = Frame synchronization pulse precedes the first bit clock

- bit 16 **ENHBUF:** Enhanced Buffer Enable bit<sup>(2)</sup>

- 1 = Enhanced Buffer mode is enabled

- 0 = Enhanced Buffer mode is disabled

- bit 15 **ON:** SPI Peripheral On bit<sup>(1)</sup>

- 1 = SPI Peripheral is enabled

- 0 = SPI Peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters in Idle mode

- 0 = Continue operation in Idle mode

- bit 12 **DISSDO:** Disable SDOx pin bit

- 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register

- 0 = SDOx pin is controlled by the module

- bit 11-10 MODE<32,16>: 32/16-Bit Communication Select bits

When AUDEN = 1:

- MODE32 MODE16 Communication

- 11 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame

- 10 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame

- 01 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame

- 00 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame

When AUDEN = 0:

MODE32 MODE16 Communication

- 1x **32-bit**

- 01 **16-bit**

- 00 **8-bit**

- bit 9 SMP: SPI Data Input Sample Phase bit

Master mode (MSTEN = 1):

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time

- Slave mode (MSTEN = 0):

- SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.

- bit 8 CKE: SPI Clock Edge Select bit<sup>(3)</sup>

- 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)

0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)

- SSEN: Slave Select Enable (Slave mode) bit

- 1 = SSx pin used for Slave mode

- $0 = \overline{SSx}$  pin not used for Slave mode, pin controlled by port function.

- bit 6 **CKP:** Clock Polarity Select bit<sup>(4)</sup>

bit 7

- 1 = Idle state for clock is a high level; active state is a low level

- 0 = Idle state for clock is a low level; active state is a high level

- bit 5 MSTEN: Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

#### 19.2 Timing Diagrams

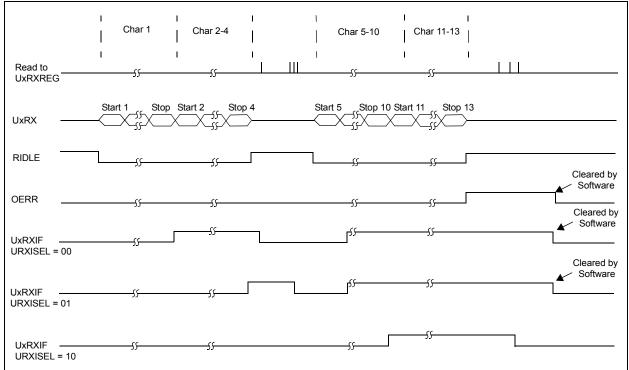

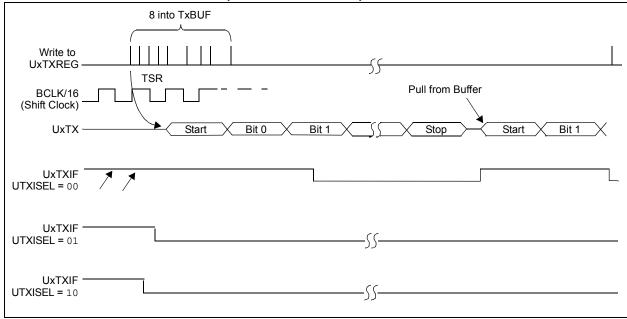

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

#### FIGURE 19-2: UART RECEPTION

#### FIGURE 19-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

| REGISTE  | R 23-3:        | C1INT: CAN INTERRUPT REGISTER (CONTINUED)                                                                                                 |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | 1 = A bus      | CAN Bus Activity Wake-up Interrupt Flag bit<br>s wake-up activity interrupt has occurred<br>s wake-up activity interrupt has not occurred |

| bit 13   | 1 = A CAI      | CAN Bus Error Interrupt Flag bit<br>N bus error has occurred<br>N bus error has not occurred                                              |

| bit 12   | SERRIF:        | System Error Interrupt Flag bit <sup>(1)</sup>                                                                                            |

|          |                | tem error occurred (typically an illegal address was presented to the system bus) tem error has not occurred                              |

| bit 11   | <b>RBOVIF:</b> | Receive Buffer Overflow Interrupt Flag bit                                                                                                |

|          |                | eive buffer overflow has occurred<br>eive buffer overflow has not occurred                                                                |

| bit 10-4 | Unimpler       | mented: Read as '0'                                                                                                                       |

| bit 3    | MODIF: 0       | CAN Mode Change Interrupt Flag bit                                                                                                        |

|          |                | N module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP)<br>N module mode change has not occurred                      |

| bit 2    | CTMRIF:        | CAN Timer Overflow Interrupt Flag bit                                                                                                     |

|          |                | N timer (CANTMR) overflow has occurred<br>N timer (CANTMR) overflow has not occurred                                                      |

| bit 1    | RBIF: Re       | ceive Buffer Interrupt Flag bit                                                                                                           |

|          |                | eive buffer interrupt is pending<br>eive buffer interrupt is not pending                                                                  |

| bit 0    | TBIF: Tra      | nsmit Buffer Interrupt Flag bit                                                                                                           |

|          | 1 = A tran     | nsmit buffer interrupt is pending                                                                                                         |

- 0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (C1CON<15>).

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     | FLTEN3            | MSEL:             | 3<1:0>            | FSEL3<4:0>        |                   |                   |                  |                  |

| 22:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     | FLTEN2            | MSEL              | 2<1:0>            | FSEL2<4:0>        |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0      | FLTEN1            | MSEL              | MSEL1<1:0>        |                   | F                 | SEL1<4:0>         |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | FLTEN0            | MSEL              | 0<1:0>            |                   | F                 | SEL0<4:0>         |                  |                  |

#### REGISTER 23-10: C1FLTCON0: CAN FILTER CONTROL REGISTER 0

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN3: Filter 3 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL3<1:0>: Filter 3 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                    |