Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 81                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 48x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f512l-i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

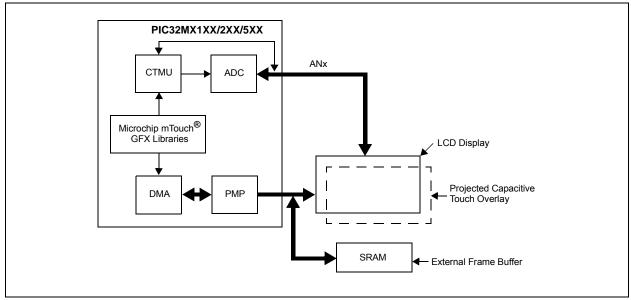

# FIGURE 2-10: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

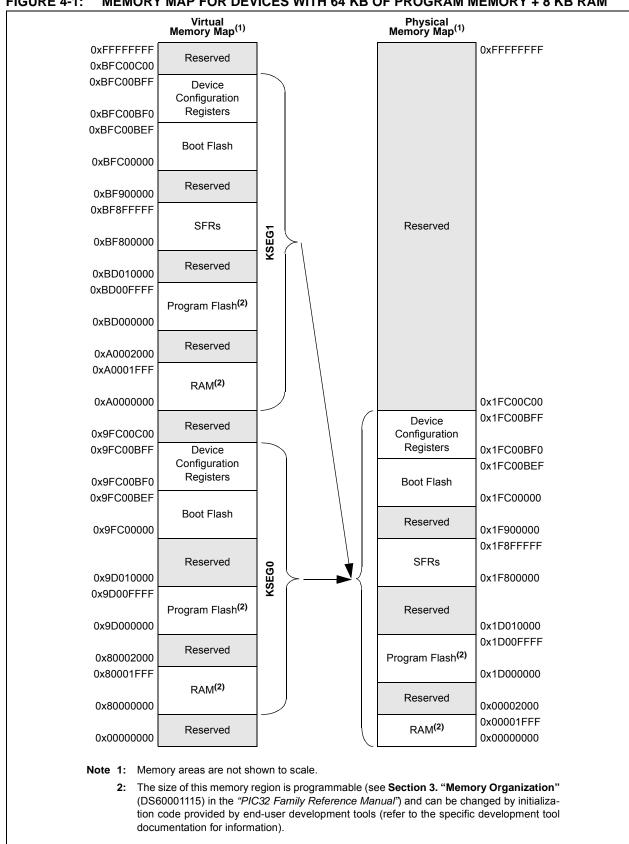

### FIGURE 4-1: MEMORY MAP FOR DEVICES WITH 64 KB OF PROGRAM MEMORY + 8 KB RAM

### TABLE 4-1: SFR MEMORY MAP

| Devinheral             | Virtual | Address      |

|------------------------|---------|--------------|

| Peripheral             | Base    | Offset Start |

| Interrupt Controller   |         | 0x1000       |

| Bus Matrix             |         | 0x2000       |

| DMA                    | 0       | 0x3000       |

| USB                    | 0xBF88  | 0x5000       |

| PORTA-PORTG            |         | 0x6000       |

| CAN1                   |         | 0xB000       |

| Watchdog Timer         |         | 0x0000       |

| RTCC                   |         | 0x0200       |

| Timer1-Timer5          |         | 0x0600       |

| IC1-IC5                |         | 0x2000       |

| OC1-OC5                |         | 0x3000       |

| I2C1-I2C2              |         | 0x5000       |

| SPI1-SPI4              |         | 0x5800       |

| UART1-UART5            | 0xBF80  | 0x6000       |

| PMP                    | UXBF80  | 0x7000       |

| ADC1                   |         | 0x9000       |

| DAC                    |         | 0x9800       |

| Comparator 1, 2, 3     |         | 0xA000       |

| Oscillator             |         | 0xF000       |

| Device and Revision ID |         | 0xF200       |

| Flash Controller       |         | 0xF400       |

| PPS                    |         | 0xFA00       |

| Configuration          | 0xBFC0  | 0x0BF0       |

### 6.1 Control Registers

### TABLE 6-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | a         |       |                  |       |        |         |       |      | Bi        | ts        |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|-------|------------------|-------|--------|---------|-------|------|-----------|-----------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14            | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8      | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     | _     | —                | —     | —      | _       |       | —    |           | —         | —    | —    | —    |      |      | —      | —    | 0000       |

| 1400                        |                        | 15:0      | WR    | WREN             | WRERR | LVDERR | LVDSTAT |       | _    | -         | _         | _    | _    | _    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     |       |                  |       |        |         |       |      | NVMKE     | /<31.0>   |      |      |      |      |      |        |      | 0000       |

|                             |                        | 15:0      |       |                  |       |        |         |       |      |           | 1501.02   |      |      |      |      |      |        |      | 0000       |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                  |       |        |         |       |      | NVMADE    | P<31.05   |      |      |      |      |      |        |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |       |                  |       |        |         |       |      | INVIVIADE | K~51.02   |      |      |      |      |      |        |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       |                  |       |        |         |       |      | NVMDAT    | A-31.0>   |      |      |      |      |      |        |      | 0000       |

| 1430                        | NVINDAIA               | 15:0      |       |                  |       |        |         |       |      | NVIVIDAI  | A-31.02   |      |      |      |      |      |        |      | 0000       |

| F440                        | NVMSRC                 | 31:16     |       | NVMSRCADDR<31:0> |       |        |         |       |      |           |           |      |      |      |      |      |        |      |            |

| F440                        | ADDR                   | 15:0      |       |                  |       |        |         |       | I    | VIVISRUAI | JUR-31.02 | •    |      |      |      |      |        |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| ess                         |                                 |                                                          |             |       |       |       |        |       |      | Bi          | ts        |            |            |            |         |             |        |             |            |

|-----------------------------|---------------------------------|----------------------------------------------------------|-------------|-------|-------|-------|--------|-------|------|-------------|-----------|------------|------------|------------|---------|-------------|--------|-------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                                | 31/15       | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8        | 23/7      | 22/6       | 21/5       | 20/4       | 19/3    | 18/2        | 17/1   | 16/0        | All Resets |

| 3060                        | DCH0CON                         | 31:16<br>15:0                                            | —<br>CHBUSY | _     |       |       | -      | -     |      | —<br>CHCHNS | —<br>CHEN | —<br>CHAED | —<br>CHCHN | —<br>CHAEN |         | —<br>CHEDET |        | —<br>I<1:0> | 00         |

|                             |                                 |                                                          |             |       |       |       |        |       |      |             |           |            |            |            |         |             |        |             |            |

| 3070                        | DCH0ECON                        | 0ECON 15:0 CHSIRQ<7:0> CFORCE CABORT PATEN SIRQEN AIRQEN |             |       |       |       |        |       |      |             |           | FF         |            |            |         |             |        |             |            |

|                             |                                 |                                                          |             |       |       |       |        |       |      |             |           |            | CHERIE     | 00         |         |             |        |             |            |

| 3080                        | DCH0INT                         | 15:0                                                     | _           | _     | _     | _     | _      | _     |      |             | CHSDIF    | CHSHIF     | CHDDIF     | CHDHIF     | CHBCIF  | CHCCIF      | CHTAIF | CHERIF      | 00         |

| 3090                        | DCH0SSA                         | 31:16         0000           15:0         0000           |             |       |       |       |        |       |      |             |           |            |            |            |         |             |        |             |            |

| 30A0                        | DCH0DSA                         | 31:16<br>15:0                                            | 11:16 0000  |       |       |       |        |       |      |             |           |            |            |            |         |             |        |             |            |

|                             | D.0110.0017                     | 31:16                                                    | _           | _     | _     | _     | _      | _     | _    | _           | _         | _          | _          | _          | _       | _           | _      | _           | 00         |

| 30B0                        | DCH0SSIZ                        | 15:0                                                     |             |       |       |       |        |       |      | CHSSIZ      | Z<15:0>   |            |            |            |         |             |        |             | 0.0        |

| 2000                        | DCH0DSIZ                        | 31:16                                                    | _           | _     | _     | —     | _      | _     |      | _           | _         | _          | _          | _          | _       | _           | —      | _           | 00         |

| 5000                        | DCHUD3IZ                        | 15:0                                                     |             |       |       |       |        |       |      | CHDSIZ      | Z<15:0>   |            |            |            |         |             |        |             | 00         |

| 3000                        | DCH0SPTR                        | 31:16                                                    | —           | _     | —     | —     | _      | _     | —    | -           | _         | —          |            |            | _       | —           | _      |             | 00         |

| 0000                        | Donioor III                     | 15:0                                                     |             |       |       |       |        |       |      | CHSPTI      | R<15:0>   |            |            |            |         |             |        |             | 00         |

| 30E0                        | DCH0DPTR                        | 31:16                                                    | —           | _     | —     | —     | —      | —     | —    |             | _         | —          |            | —          | —       | —           | _      | _           | 00         |

|                             |                                 | 15:0                                                     |             |       |       |       |        |       |      | CHDPTI      | R<15:0>   |            |            |            |         |             |        |             | 00         |

| 30F0                        | DCH0CSIZ                        | 31:16                                                    | —           |       | —     | —     | —      | —     |      |             | -         |            | —          | —          |         | —           | _      | _           | 00         |

|                             |                                 | 15:0                                                     |             |       |       |       | _      |       |      | CHCSIZ      | 2<15:0>   | _          |            | _          |         |             |        |             | 00         |

| 3100                        | DCH0CPTR                        | 31:16<br>15:0                                            | —           |       |       |       | _      |       |      | CHCPTI      |           |            |            |            | _       | —           | _      |             | 00         |

|                             |                                 | 31:16                                                    |             | _     | _     | _     | _      | _     | _    |             |           | _          | _          |            |         | _           | _      | _           | 00         |

| 3110                        | DCH0DAT                         | 15:0                                                     | _           | _     | _     | _     | _      | _     | _    | _           |           |            |            |            | AT<7:0> |             |        |             | 00         |

|                             |                                 | 31:16                                                    | _           | _     | _     |       | _      | _     |      | _           | _         | —          | —          | _          | _       | _           | _      | _           | 00         |

| 3120                        | DCH1CON                         | 15:0                                                     | CHBUSY      | _     | _     | _     | _      | _     | _    | CHCHNS      | CHEN      | CHAED      | CHCHN      | CHAEN      | _       | CHEDET      | CHPR   | <1:0>       | 00         |

| 0400                        | DOLUEDON                        | 31:16                                                    | _           | _     | _     | _     | _      | _     | _    | -           |           |            |            | CHAIR      | Q<7:0>  |             |        |             | 00         |

| 3130                        | DCH1ECON                        | 15:0                                                     |             |       |       | CHSIR | Q<7:0> |       |      |             | CFORCE    | CABORT     | PATEN      | SIRQEN     | AIRQEN  | _           | —      | —           | FF         |

| 3140                        | DCH1INT                         | 31:16                                                    |             | _     |       | _     | _      |       |      | _           | CHSDIE    | CHSHIE     | CHDDIE     | CHDHIE     | CHBCIE  | CHCCIE      | CHTAIE | CHERIE      | 00         |

| 5140                        | DCHIINI                         | 15:0                                                     | —           |       | —     | _     | _      | _     | —    | —           | CHSDIF    | CHSHIF     | CHDDIF     | CHDHIF     | CHBCIF  | CHCCIF      | CHTAIF | CHERIF      | 00         |

| 3150                        | DCH1SSA                         | 31:16<br>15:0                                            |             |       |       |       |        |       |      | CHSSA       | <31:0>    |            |            |            |         |             |        |             | 00         |

| 3160                        | DCH1DSA                         | 31:16<br>15:0 CHDSA<31:0> 0000 0000                      |             |       |       |       |        |       |      |             |           |            |            |            |         |             |        |             |            |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information. Note 1:

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

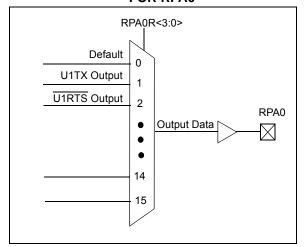

### 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

# 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

### 11.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

### 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

|              | -IN 11-0. C       |                   |                   |                   | NOE I ON          |                   |                  | ,                |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | —                 | _                 | _                 |                   |                  | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 |                   | _                 | _                 | —                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | SIDL              | _                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 |                   |                   |                   | _                |                  |

### **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A – G)

### Legend:

| · J · · ·         |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = CPU Idle Mode halts CN operation

- 0 = CPU Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

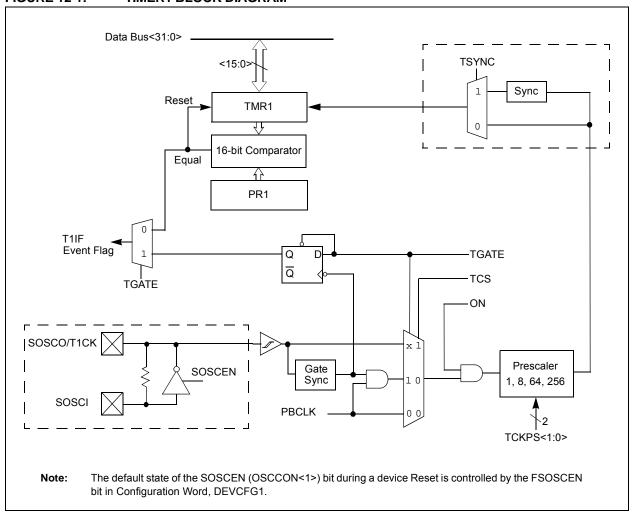

### 12.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a freerunning interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

### 12.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

### FIGURE 12-1: TIMER1 BLOCK DIAGRAM

NOTES:

### REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 17 SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)

- 1 = Frame synchronization pulse coincides with the first bit clock

- 0 = Frame synchronization pulse precedes the first bit clock

- bit 16 **ENHBUF:** Enhanced Buffer Enable bit<sup>(2)</sup>

- 1 = Enhanced Buffer mode is enabled

- 0 = Enhanced Buffer mode is disabled

- bit 15 **ON:** SPI Peripheral On bit<sup>(1)</sup>

- 1 = SPI Peripheral is enabled

- 0 = SPI Peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters in Idle mode

- 0 = Continue operation in Idle mode

- bit 12 **DISSDO:** Disable SDOx pin bit

- 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register

- 0 = SDOx pin is controlled by the module

- bit 11-10 MODE<32,16>: 32/16-Bit Communication Select bits

When AUDEN = 1:

- MODE32 MODE16 Communication

- 11 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame

- 10 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame

- 01 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame

- 00 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame

When AUDEN = 0:

MODE32 MODE16 Communication

- 1x **32-bit**

- 01 **16-bit**

- 00 **8-bit**

- bit 9 SMP: SPI Data Input Sample Phase bit

Master mode (MSTEN = 1):

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time

- Slave mode (MSTEN = 0):

- SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.

- bit 8 CKE: SPI Clock Edge Select bit<sup>(3)</sup>

- 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)

0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)

- SSEN: Slave Select Enable (Slave mode) bit

- 1 = SSx pin used for Slave mode

- $0 = \overline{SSx}$  pin not used for Slave mode, pin controlled by port function.

- bit 6 **CKP:** Clock Polarity Select bit<sup>(4)</sup>

bit 7

- 1 = Idle state for clock is a high level; active state is a low level

- 0 = Idle state for clock is a low level; active state is a high level

- bit 5 MSTEN: Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

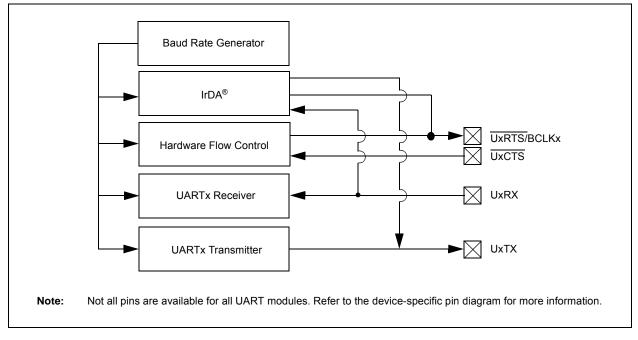

### 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX/5XX 64/100-pin family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, odd or no parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9<sup>th</sup> bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART.

### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

### REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER (CONTINUED)

```

bit 21-16 CH0SA<5:0>: Positive Input Select bits for Sample A Multiplexer Setting

For 64-pin devices:

011110 = Channel 0 positive input is Open<sup>(1)</sup>

011101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

011100 = Channel 0 positive input is IVREF<sup>(3)</sup>

011011 = Channel 0 positive input is AN27

000001 = Channel 0 positive input is AN1

000000 = Channel 0 positive input is AN0

For 100-pin devices:

110010 = Channel 0 positive input is Open<sup>(1)</sup>

110001 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

110000 = Channel 0 positive input is IVREF<sup>(3)</sup>

101111 = Channel 0 positive input is AN47

0000001 = Channel 0 positive input is AN1

0000000 = Channel 0 positive input is AN0

bit 15-0

Unimplemented: Read as '0'

```

- Note 1: This selection is only used with CTMU capacitive and time measurement.

- 2: See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: Internal precision 1.2V reference. See Section 24.0 "Comparator" for more information.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0                     | U-0                | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                       | _                  | _                 | —                 | —                 | —                 | _                | _                |

| 00.40        | U-0                     | R/W-0              | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | —                       | WAKFIL             | _                 | _                 |                   | SEG               | 62PH<2:0>(1      | ,4)              |

| 45.0         | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | SEG2PHTS <sup>(1)</sup> | SAM <sup>(2)</sup> | ę                 | SEG1PH<2:0        | >                 | Р                 | RSEG<2:0>        |                  |

| 7:0          | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | SJW<1:                  | 0> <sup>(3)</sup>  |                   |                   | BRP<              | 5:0>              |                  |                  |

### **REGISTER 23-2: C1CFG: CAN BAUD RATE CONFIGURATION REGISTER**

| Legend:           | HC = Hardware Clear | S = Settable bit          |                    |

|-------------------|---------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-23 Unimplemented: Read as '0'

- bit 22 WAKFIL: CAN Bus Line Filter Enable bit 1 = Use CAN bus line filter for wake-up 0 = CAN bus line filter is not used for wake-up

- bit 21-19 Unimplemented: Read as '0'

| 511 21 15 |                                                                               |

|-----------|-------------------------------------------------------------------------------|

| bit 18-16 | SEG2PH<2:0>: Phase Buffer Segment 2 bits <sup>(1,4)</sup>                     |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x TQ                                                        |

| bit 15    | SEG2PHTS: Phase Segment 2 Time Select bit <sup>(1)</sup>                      |

|           | 1 = Freely programmable                                                       |

|           | 0 = Maximum of SEG1PH or Information Processing Time, whichever is greater    |

| bit 14    | SAM: Sample of the CAN Bus Line bit <sup>(2)</sup>                            |

|           | 1 = Bus line is sampled three times at the sample point                       |

|           | 0 = Bus line is sampled once at the sample point                              |

| bit 13-11 | SEG1PH<2:0>: Phase Buffer Segment 1 bits <sup>(4)</sup>                       |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x TQ                                                        |

|           |                                                                               |

| Note 1:   | SEG2PH $\leq$ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. |

| 2:        | 3 Time bit sampling is not allowed for BRP < 2.                               |

| 3:        | SJW ≤ SEG2PH.                                                                 |

|           |                                                                               |

- 4: The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

- This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> Note: (C1CON < 23:21 >) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|---------------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        | —                 | _                 | _                 | _                         | —                 | _                 | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | —                 | —                         | —                 | —                 | —                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | R-0                       | R-0               | R-0               | R-0              | R-0              |  |  |

| 15.0         | —                 | —                 | —                 |                           |                   | FILHIT<4:0>       |                  |                  |  |  |

| 7:0          | U-0               | R-1               | R-0               | R-0                       | R-0               | R-0               | R-0              | R-0              |  |  |

| 7.0          | _                 |                   |                   | ICODE<6:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |

### REGISTER 23-4: C1VEC: CAN INTERRUPT CODE REGISTER

### Legend:

| R = Rea   | dable bit | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-----------|-----------|------------------|--------------------------|--------------------|--|

| -n = Valu | le at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

### bit 31-13 Unimplemented: Read as '0'

```

bit 12-8 FILHIT<4:0>: Filter Hit Number bit

11111 = Reserved

10000 = Reserved

01111 = Filter 15

00000 = Filter 0

bit 7

Unimplemented: Read as '0'

ICODE<6:0>: Interrupt Flag Code bits<sup>(1)</sup>

bit 6-0

1111111 = Reserved

1001001 = Reserved

1001000 = Invalid message received (IVRIF)

1000111 = CAN module mode change (MODIF)

1000110 = CAN timestamp timer (CTMRIF)

1000101 = Bus bandwidth error (SERRIF)

1000100 = Address error interrupt (SERRIF)

1000011 = Receive FIFO overflow interrupt (RBOVIF)

1000010 = Wake-up interrupt (WAKIF)

1000001 = Error Interrupt (CERRIF)

1000000 = No interrupt

0111111 = Reserved

0010000 = Reserved

0001111 = FIFO15 Interrupt (C1FSTAT<15> set)

0000000 = FIFO0 Interrupt (C1FSTAT<0> set)

```

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

|              |                   |                   | 011110 0011       |                     |                   |                   |                        |                  |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 51.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EL<3:0>           |                   | EDG2STAT               | EDG1STAT         |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | EL<3:0>           |                   | _                      | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15:8         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7:0          |                   |                   | ITRIM             | 1<5:0>              |                   |                   | IRNG                   | <1:0>            |

### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

### Legend:

| 8                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31 EDG1MOD: Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

### bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = IC4 Capture Event is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

### 0000 = Timer1 Event is selected

### bit 25 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

- 1 = Edge 2 has occurred

- 0 = Edge 2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

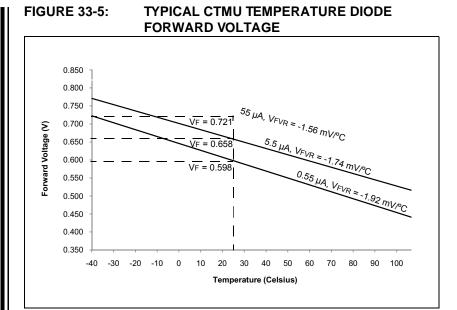

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| DC CHARACTERISTICS |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)                                                                                                                      |                 |                        |            |       |                                                   |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------|------------|-------|---------------------------------------------------|

|                    |        | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                 |                        |            |       |                                                   |

| Param.<br>No.      | Symbol | Characteristics                                                                                                                                                                            | Min.            | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |

|                    | VIL    | Input Low Voltage                                                                                                                                                                          |                 |                        |            |       |                                                   |

| DI10               |        | I/O Pins with PMP                                                                                                                                                                          | Vss             | —                      | 0.15 Vdd   | V     |                                                   |

|                    |        | I/O Pins                                                                                                                                                                                   | Vss             | —                      | 0.2 Vdd    | V     |                                                   |

| DI18               |        | SDAx, SCLx                                                                                                                                                                                 | Vss             | —                      | 0.3 VDD    | V     | SMBus disabled<br>(Note 4)                        |

| DI19               |        | SDAx, SCLx                                                                                                                                                                                 | Vss             | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |

|                    | VIH    | Input High Voltage                                                                                                                                                                         |                 |                        |            |       |                                                   |

| DI20               |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                                                                                                                                                    | 0.65 VDD        | _                      | Vdd        | V     | (Note 4,6)                                        |

|                    |        | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>                                                                                                                                            | 0.25 VDD + 0.8V | —                      | 5.5        | V     | (Note 4,6)                                        |

|                    |        | I/O Pins 5V-tolerant <sup>(5)</sup>                                                                                                                                                        | 0.65 VDD        | —                      | 5.5        | V     |                                                   |

| DI28               |        | SDAx, SCLx                                                                                                                                                                                 | 0.65 VDD        | —                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |

| DI29               |        | SDAx, SCLx                                                                                                                                                                                 | 2.1             | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |

| DI30               | ICNPU  | Change Notification<br>Pull-up Current                                                                                                                                                     | _               | -200                   | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |

| DI31               | ICNPD  | Change Notification<br>Pull-down Current <sup>(4)</sup>                                                                                                                                    | 50              | 200                    | —          | μA    | VDD = 3.3V, VPIN = VDD                            |

|                    | lı∟    | Input Leakage Current<br>(Note 3)                                                                                                                                                          |                 |                        |            |       |                                                   |

| DI50               |        | I/O Ports                                                                                                                                                                                  | _               | —                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |

| DI51               |        | Analog Input Pins                                                                                                                                                                          | _               | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |

| DI55               |        | MCLR <sup>(2)</sup>                                                                                                                                                                        | _               | _                      | <u>+</u> 1 | μA    | $VSS \le VPIN \le VDD$                            |

| DI56               |        | OSC1                                                                                                                                                                                       | -               | —                      | <u>+</u> 1 | μΑ    | $VSS \le VPIN \le VDD,$ XT and HS modes           |

### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.

- **6:** The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

### TABLE 31-13: COMPARATOR SPECIFICATIONS

| DC CHARACTERISTICS |                        |                                       | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 4): 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |                                                                            |  |

|--------------------|------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol                 | Characteristics                       | Min.                                                                                                                                                                                                                                                                                               | Тур. | Max. | Units | Comments                                                                   |  |

| D300               | VIOFF                  | Input Offset Voltage                  | —                                                                                                                                                                                                                                                                                                  | ±7.5 | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                  |  |

| D301               | VICM <b>(2)</b>        | Input Common Mode Voltage             | 0                                                                                                                                                                                                                                                                                                  | —    | Vdd  | V     | AVDD = VDD,<br>AVSS = VSS                                                  |  |

| D302               | CMRR <sup>(2)</sup>    | Common Mode Rejection Ratio           | 55                                                                                                                                                                                                                                                                                                 |      | _    | dB    | Max VICM = (VDD - 1)V                                                      |  |

| D303               | TRESP <sup>(1,2)</sup> | Response Time                         | —                                                                                                                                                                                                                                                                                                  | 150  | 400  | ns    | AVDD = VDD,<br>AVSS = VSS                                                  |  |

| D304               | ON20√ <sup>(2)</sup>   | Comparator Enabled to Output<br>Valid | —                                                                                                                                                                                                                                                                                                  | _    | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit |  |

| D305               | IVREF                  | Internal Voltage Reference            | 1.14                                                                                                                                                                                                                                                                                               | 1.2  | 1.26 | V     | _                                                                          |  |

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Vss to VDD.

2: These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

4: The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

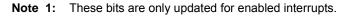

### TABLE 31-37: PARALLEL SLAVE PORT REQUIREMENTS

| AC CHARACTERISTICS |              |                                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |            |

|--------------------|--------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|

| Para<br>m.No.      | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                                | Тур. | Max. | Units | Conditions |

| PS1                | TdtV2wr<br>H | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                                  |      |      | ns    | _          |

| PS2                | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                                                                                                                                                                                                                                                  | —    | _    | ns    | _          |

| PS3                | TrdL2dt<br>V | RD and CS Active to Data-Out Valid                                               | _                                                                                                                                                                                                                                                                                   | —    | 60   | ns    | _          |

| PS4                | TrdH2dtl     | RD Active or CS Inactive to Data-Out Invalid                                     | 0                                                                                                                                                                                                                                                                                   | —    | 10   | ns    | _          |

| PS5                | Tcs          | CS Active Time                                                                   | Трв + 40                                                                                                                                                                                                                                                                            | _    | _    | ns    | —          |

| PS6                | Twr          | WR Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                            | _    | _    | ns    | —          |

| PS7                | Trd          | RD Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                            |      | _    | ns    | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

### FIGURE 31-21: PARALLEL MASTER PORT READ TIMING DIAGRAM

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2014-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0488-0