Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 81                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 48x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f512l-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGIST  | ER 5-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| bit 9-8 | IS1<1:0>: Interrupt Subpriority bits                                                                                  |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                            |

| bit 4-2 | IP0<2:0>: Interrupt Priority bits                                                                                     |

|         | 111 = Interrupt priority is 7                                                                                         |

|         | •                                                                                                                     |

|         |                                                                                                                       |

|         | 010 = Interrupt priority is 2                                                                                         |

|         | 001 = Interrupt priority is 1                                                                                         |

|         | 000 = Interrupt is disabled                                                                                           |

| bit 1-0 | IS0<1:0>: Interrupt Subpriority bits                                                                                  |

|         | 11 = Interrupt subpriority is 3                                                                                       |

|         | 10 = Interrupt subpriority is 2                                                                                       |

|         | 01 = Interrupt subpriority is 1                                                                                       |

|         | 00 = Interrupt subpriority is 0                                                                                       |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 5-1 for the exact bit definitions. |

## 6.1 Control Registers

## TABLE 6-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | a         |       |       |       |        |         |       |      | Bi        | ts        |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|-------|-------|-------|--------|---------|-------|------|-----------|-----------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14 | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8      | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     | _     | —     | —     | —      | _       |       | —    |           | —         | —    | —    | —    |      |      | —      | —    | 0000       |

| 1400                        |                        | 15:0      | WR    | WREN  | WRERR | LVDERR | LVDSTAT |       | _    | -         | _         | _    | _    | _    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     |       |       |       |        |         |       |      | NVMKE     | /<31.0>   |      |      |      |      |      |        |      | 0000       |

|                             |                        | 15:0      |       |       |       |        |         |       |      |           | 1501.02   |      |      |      |      |      |        |      | 0000       |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |       |       |        |         |       |      | NVMADE    | P<31.05   |      |      |      |      |      |        |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |       |       |       |        |         |       |      | INVIVIADE | K~51.02   |      |      |      |      |      |        |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       |       |       |        |         |       |      | NVMDAT    | A-31.0>   |      |      |      |      |      |        |      | 0000       |

| 1430                        | NVINDAIA               | 15:0      |       |       |       |        |         |       |      | NVIVIDAI  | A-31.02   |      |      |      |      |      |        |      | 0000       |

| F440                        | NVMSRC                 | 31:16     |       |       |       |        |         |       | ,    | VMSRCA    |           |      |      |      |      |      |        |      | 0000       |

| F440                        | ADDR                   | 15:0      |       |       |       |        |         |       | I    | VIVISRUAI | JUR-31.02 | •    |      |      |      |      |        |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 24.04        | U-0               | U-0                  | R/W-y             | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |

| 31:24        | _                 | —                    | Р                 | LLODIV<2:0>       | >                 | F                     | RCDIV<2:0>       |                  |

| 22.16        | U-0               | R-0                  | R-1               | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDI∖             | /<1:0>            | Р                     | LLMULT<2:0>      | •                |

| 15.0         | U-0               | R-0                  | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |

| 15:8         | _                 |                      | COSC<2:0>         |                   | _                 |                       | NOSC<2:0>        |                  |

| 7.0          | R/W-0             | R-0                  | R-0               | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

#### Legend:

bit 22

#### y = Value set from Configuration bits on POR

| •                 | •                | •                         |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-30 Unimplemented: Read as '0'

bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- SOSCRDY: Secondary Oscillator (SOSC) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 01:04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |

| 00.10     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     |                   |                   |                   | CHSSA<            | 23:16>            |                   |                  |                  |

| 45-0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      |                   |                   |                   | CHSSA             | <15:8>            |                   |                  |                  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |

## **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

#### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | CHDSA<            | 23:16>            |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSA             | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\textbf{Note:}}$  This must be the physical address of the destination.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Runge        |                   |                   |                   |                   |                   |                   |                  |                  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        |                   | _                 | _                 | _                 | _                 | _                 | _                |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | <7:0>             |                   |                  |                  |

## REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

## Legend:

| =ogona.           |                        |                      |                    |

|-------------------|------------------------|----------------------|--------------------|

| R = Readable bit  | e bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

<u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

All other modes: Unused.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | -                 |                   |                   | _                 |                  | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 |                   |                   | _                 |                  | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | —                 | _                 | -                 | -                 | —                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          | —                | VBUSVDIE         |

## REGISTER 10-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt enabled

- 0 = ID interrupt disabled

- bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt enabled

- 0 = 1 millisecond timer interrupt disabled

- bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt enabled

- 0 = Line state interrupt disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = ACTIVITY interrupt enabled

- 0 = ACTIVITY interrupt disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt enabled

- 0 = Session valid interrupt disabled

- bit 2 SESENDIE: B-Session End Interrupt Enable bit

- 1 = B-session end interrupt enabled

- 0 = B-session end interrupt disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-VBUS Valid Interrupt Enable bit

- 1 = A-VBUS valid interrupt enabled

- 0 = A-VBUS valid interrupt disabled

## 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

### 11.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

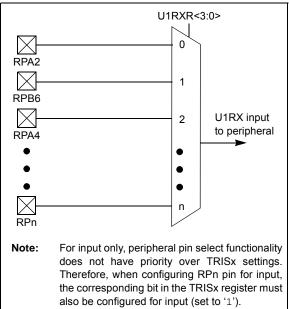

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

## FIGURE 11-2: REI

REMAPPABLE INPUT EXAMPLE FOR U1RX

#### 11.3.5 OUTPUT MAPPING

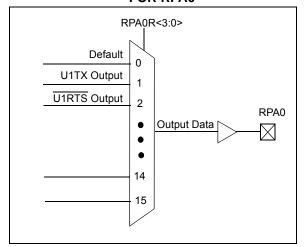

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

## 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

## 11.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

### 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

## TABLE 11-8: PORTD REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |               |               |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | _     | _     | —     | _     |               | —             | —            |              | _            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0000                        | THOLLD                          | 15:0      | —     | —     | —     | —     |               |               | —            | _            | _            | —            | _            |              | ANSELD3      | ANSELD2      | ANSELD1      | —            | 000E          |

| 6310                        | TRISD                           | 31:16     | —     | —     | —     | —     | —             |               | —            | —            | _            |              | _            | _            |              | —            |              |              | 0000          |

| 0310                        | TRIOD                           | 15:0      | —     | —     | —     | _     | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | OFFF          |

| 5320                        | PORTD                           | 31:16     | —     | _     | _     | _     | _             | _             | —            | _            | _            | _            | _            |              | _            | —            |              | _            | 0000          |

| 3320                        | TORID                           | 15:0      | —     | —     | —     | _     | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     | —     | —     | —     | _     | —             | —             | _            | _            | _            | —            | _            | -            | —            | —            | _            | _            | 0000          |

| 0330                        | LAID                            | 15:0      | -     | _     | _     | _     | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | xxxx          |

| 6340                        | ODCD                            | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0340                        | ODCD                            | 15:0      | Ι     |       |       | -     | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | 0000          |

| 6350                        | CNPUD                           | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0330                        | CINFUD                          | 15:0      | -     | _     | _     | _     | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | 0000          |

| 6360                        | CNPDD                           | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0300                        | CNFDD                           | 15:0      |       | _     | -     |       | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | 0000          |

| 6270                        | CNCOND                          | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0370                        | CINCOIND                        | 15:0      | ON    | _     | SIDL  |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 6380                        | CNEND                           | 31:16     |       | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0300                        | CNEND                           | 15:0      | Ι     | -     | -     | Ι     | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | _     | _             | _             | _            | —            | _            | _            | _            | _            | _            | _            |              | _            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | _     | _     | _     | -     | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | —                 | -                 | _                 | —                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | —                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | e]R<3:0>         |                  |

#### REGISTER 11-1: [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-4 Unimplemented: Read as '0'

#### bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

#### REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 |                   |                  | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | RPnR              | <3:0>            |                  |

## Legend:

| 0                 |                                                     |                      |                    |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

## TABLE 14-1: WATCHDOG TIMER REGISTER MAP

| ess                        |                                 | e         |       |       |       |       |       |       |      |      | Bits |      |      |           |      |      |          |        | s         |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|----------|--------|-----------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1     | 16/0   | All Reset |

| 0000                       | WDTCON                          | 31:16     | —     | —     | —     | —     |       | —     | —    | —    | —    | —    | —    | —         | —    | —    | -        | —      | 0000      |

| 0000                       | WDICON                          | 15:0      | ON    | —     | —     | —     | —     | —     | _    | —    | _    |      | SV   | VDTPS<4:0 | )>   |      | WDTWINEN | WDTCLR | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

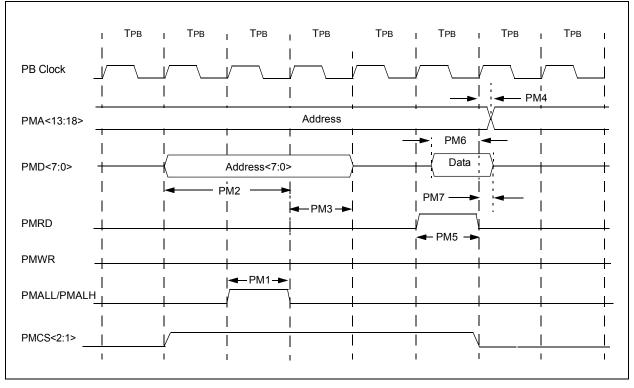

#### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- 0001 = Wait of 2 Трв 0000 = Wait of 1 Трв (default)

bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

11 = Wait of 4 TPB 10 = Wait of 3 TPB 01 = Wait of 2 TPB 00 = Wait of 1 TPB (default)

For Read operations: 11 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 1 TPB

- 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC sample and hold amplifier is sampling

- 0 = The ADC sample/hold amplifier is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

Clearing this bit will not affect any operation in progress.

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

### REGISTER 23-2: C1CFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

- bit 10-8 **PRSEG<2:0>:** Propagation Time Segment bits<sup>(4)</sup> 111 = Length is  $8 \times TQ$  $000 = \text{Length is } 1 \times TQ$ SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup> bit 7-6 11 = Length is  $4 \times TQ$  $10 = \text{Length is } 3 \times TQ$ 01 = Length is 2 x TQ  $00 = \text{Length is } 1 \times TQ$ bit 5-0 BRP<5:0>: Baud Rate Prescaler bits 111111 = Tq = (2 x 64)/SYSCLK 111110 = TQ = (2 x 63)/SYSCLK • 000001 = TQ = (2 x 2)/SYSCLK  $000000 = TQ = (2 \times 1)/SYSCLK$ Note 1: SEG2PH  $\leq$  SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. 2: 3 Time bit sampling is not allowed for BRP < 2.

- **3:** SJW  $\leq$  SEG2PH.

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

| REGISTE  | R 23-3:        | C1INT: CAN INTERRUPT REGISTER (CONTINUED)                                                                                                 |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | 1 = A bus      | CAN Bus Activity Wake-up Interrupt Flag bit<br>s wake-up activity interrupt has occurred<br>s wake-up activity interrupt has not occurred |

| bit 13   | 1 = A CAI      | CAN Bus Error Interrupt Flag bit<br>N bus error has occurred<br>N bus error has not occurred                                              |

| bit 12   | SERRIF:        | System Error Interrupt Flag bit <sup>(1)</sup>                                                                                            |

|          |                | tem error occurred (typically an illegal address was presented to the system bus) tem error has not occurred                              |

| bit 11   | <b>RBOVIF:</b> | Receive Buffer Overflow Interrupt Flag bit                                                                                                |

|          |                | eive buffer overflow has occurred<br>eive buffer overflow has not occurred                                                                |

| bit 10-4 | Unimpler       | mented: Read as '0'                                                                                                                       |

| bit 3    | MODIF: 0       | CAN Mode Change Interrupt Flag bit                                                                                                        |

|          |                | N module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP)<br>N module mode change has not occurred                      |

| bit 2    | CTMRIF:        | CAN Timer Overflow Interrupt Flag bit                                                                                                     |

|          |                | N timer (CANTMR) overflow has occurred<br>N timer (CANTMR) overflow has not occurred                                                      |

| bit 1    | RBIF: Re       | ceive Buffer Interrupt Flag bit                                                                                                           |

|          |                | eive buffer interrupt is pending<br>eive buffer interrupt is not pending                                                                  |

| bit 0    | TBIF: Tra      | nsmit Buffer Interrupt Flag bit                                                                                                           |

|          | 1 = A tran     | nsmit buffer interrupt is pending                                                                                                         |

- 0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (C1CON<15>).

## 24.1 Control Registers

## TABLE 24-1: COMPARATOR REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |      | Bi   | ts   |        |      |      |      |       |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Resets |

| 4000                        | CM1CON                          | 31:16     | _     | _     | —     | —     | —     | -     | —    | —    | -    | —      | —    | —    | _    | —     | —     | _     | 0000       |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4010                        | CM2CON                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| AUTU                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4020                        | CM3CON                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| A060                        | CMSTAT                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A000                        | CIVISTAT                        | 15:0      | —     | _     | SIDL  | —     | _     |       |      | _    | —    |        | —    | —    | —    | C3OUT | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| TABLE 31-5: | DC CHARACTERISTICS: OPERATING CURRENT (IDD) |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| DC CHARA                                | CTERISTICS             | 5    | (unless other | Standard Operating Conditions: 2.3V to 3.6Vunless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |             |  |  |  |  |  |  |

|-----------------------------------------|------------------------|------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|--|

| Parameter<br>No.                        | Typical <sup>(3)</sup> | Max. | Units         | Conditions                                                                                                                                                                                        |             |  |  |  |  |  |  |

| Operating Current (IDD) (Notes 1, 2, 5) |                        |      |               |                                                                                                                                                                                                   |             |  |  |  |  |  |  |

| DC20                                    | 2                      | 8    | mA            | 4 MF                                                                                                                                                                                              | lz (Note 4) |  |  |  |  |  |  |

| DC21                                    | 7                      | 13   | mA            | 1                                                                                                                                                                                                 | 0 MHz       |  |  |  |  |  |  |

| DC22                                    | 10                     | 18   | mA            | 20 MI                                                                                                                                                                                             | Hz (Note 4) |  |  |  |  |  |  |

| DC23                                    | 15                     | 25   | mA            | 30 MHz (Note 4)                                                                                                                                                                                   |             |  |  |  |  |  |  |

| DC24                                    | 20                     | 32   | mA            | 40 MHz                                                                                                                                                                                            |             |  |  |  |  |  |  |

| DC25                                    | 180                    | 250  | μA            | +25°C, 3.3V LPRC (31 kHz) (Note 4)                                                                                                                                                                |             |  |  |  |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in the "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

| AC CHA        | RACTERI       | ISTICS                                                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |             |            |                                              |  |  |  |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|----------------------------------------------|--|--|--|--|

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                                   |  |  |  |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                                                                                                               |                        | 40<br>40    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)                |  |  |  |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                                                                                                                     | —                      | 10          | MHz        | XT (Note 4)                                  |  |  |  |  |

| OS12          |               |                                                                                                                  | 4                                                                                                                                                                                                                                                                                     | —                      | 10          | MHz        | XTPLL<br>(Notes 3,4)                         |  |  |  |  |

| OS13          |               |                                                                                                                  | 10                                                                                                                                                                                                                                                                                    | —                      | 25          | MHz        | HS (Note 5)                                  |  |  |  |  |

| OS14          |               |                                                                                                                  | 10                                                                                                                                                                                                                                                                                    | —                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                         |  |  |  |  |

| OS15          |               |                                                                                                                  | 32                                                                                                                                                                                                                                                                                    | 32.768                 | 100         | kHz        | Sosc (Note 4)                                |  |  |  |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                                                                                                                                                                                                                                                     | _                      | _           | —          | See parameter<br>OS10 for Fosc<br>value      |  |  |  |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                                                                                                                           | —                      | —           | ns         | EC (Note 4)                                  |  |  |  |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | —                                                                                                                                                                                                                                                                                     | —                      | 0.05 x Tosc | ns         | EC (Note 4)                                  |  |  |  |  |

| OS40          | Tost          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                                                                                                                     | 1024                   | _           | Tosc       | (Note 4)                                     |  |  |  |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | —                                                                                                                                                                                                                                                                                     | 2                      | —           | ms         | (Note 4)                                     |  |  |  |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             |                                                                                                                                                                                                                                                                                       | 12                     |             | mA/V       | VDD = 3.3V,<br>TA = +25°C<br><b>(Note 4)</b> |  |  |  |  |

## TABLE 31-17: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

2: Instruction cycle period (TcY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

**3:** PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

4: This parameter is characterized, but not tested in manufacturing.

#### TABLE 31-37: PARALLEL SLAVE PORT REQUIREMENTS

| AC CHARACTERISTICS |              |                                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |            |  |

|--------------------|--------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|

| Para<br>m.No.      | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                                | Тур. | Max. | Units | Conditions |  |

| PS1                | TdtV2wr<br>H | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                                  |      |      | ns    | _          |  |

| PS2                | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                                                                                                                                                                                                                                                  | —    | _    | ns    | _          |  |

| PS3                | TrdL2dt<br>V | RD and CS Active to Data-Out Valid                                               | _                                                                                                                                                                                                                                                                                   | —    | 60   | ns    | _          |  |

| PS4                | TrdH2dtl     | RD Active or CS Inactive to Data-Out Invalid                                     | 0                                                                                                                                                                                                                                                                                   | —    | 10   | ns    | _          |  |

| PS5                | Tcs          | CS Active Time                                                                   | Трв + 40                                                                                                                                                                                                                                                                            | _    | _    | ns    | —          |  |

| PS6                | Twr          | WR Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                            | _    | _    | ns    | —          |  |

| PS7                | Trd          | RD Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                            |      | _    | ns    | —          |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

## FIGURE 31-21: PARALLEL MASTER PORT READ TIMING DIAGRAM

## TABLE 32-8:SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                                                        |        |      |      |       |            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------|------|------|-------|------------|

| Param.<br>No. | Symbol                                                                                                                                                                                                        | Characteristics                                        | Min.   | Тур. | Max. | Units | Conditions |

| MSP70         | TscL                                                                                                                                                                                                          | SCKx Input Low Time (Note 1,2)                         | Tsck/2 | —    | _    | ns    | _          |

| MSP71         | TscH                                                                                                                                                                                                          | SCKx Input High Time (Note 1,2)                        | Tsck/2 | —    |      | ns    | —          |

| MSP51         | TssH2doZ                                                                                                                                                                                                      | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 2)</b> | 5      |      | 25   | ns    |            |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

## TABLE 32-9:SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |         |      |       |            |  |

|--------------------|--------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|

| Param.<br>No.      | Symbol | Characteristics                 | Min.                                                                                                                                              | Typical | Max. | Units | Conditions |  |

| SP70               | TscL   | SCKx Input Low Time (Note 1,2)  | Tsck/2                                                                                                                                            | _       | _    | ns    | —          |  |

| SP71               | TscH   | SCKx Input High Time (Note 1,2) | Tsck/2                                                                                                                                            | _       | _    | ns    | —          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: The minimum clock period for SCKx is 40 ns.