Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx270f512lt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

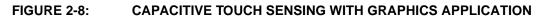

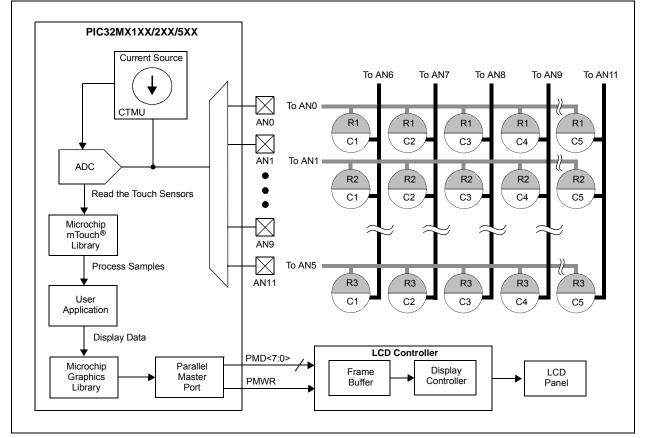

# 2.10 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-8, Figure 2-9, and Figure 2-10.

FIGURE 2-9: AUDIO PLAYBACK APPLICATION

| Bit<br>Range | Bit<br>31/23/15/7 |           |           |           |           | Bit Bit<br>29/21/13/5 28/20/12/4 |                    | Bit<br>26/18/10/2  | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------|-----------|-----------|-----------|----------------------------------|--------------------|--------------------|------------------|------------------|

| 31:24        | U-0               | U-0       | R/W-0, HS | U-0       | U-0       | U-0                              | U-0                | U-0                |                  |                  |

| 31.24        | —                 | —         | HVDR      | —         | —         | _                                | —                  | —                  |                  |                  |

| 23:16        | U-0               | U-0       | U-0       | U-0       | U-0       | U-0                              | U-0                | U-0                |                  |                  |

| 23.10        | —                 | —         | —         | —         | —         | _                                | —                  | —                  |                  |                  |

| 15:8         | U-0               | U-0       | U-0       | U-0       | U-0       | U-0                              | R/W-0, HS          | R/W-0              |                  |                  |

| 10.0         | —                 | —         | —         | —         | —         | _                                | CMR                | VREGS              |                  |                  |

| 7.0          | R/W-0, HS         | R/W-0, HS | U-0       | R/W-0, HS | R/W-0, HS | R/W-0, HS                        | R/W-1, HS          | R/W-1, HS          |                  |                  |

| 7:0          | EXTR              | SWR       | _         | WDTO      | SLEEP     | IDLE                             | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |                  |                  |

# REGISTER 7-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware | 9                    |                    |

|-------------------|----------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared | x = Bit is unknown |

| -n - value |                                                                          |

|------------|--------------------------------------------------------------------------|

|            |                                                                          |

| bit 31-30  | Unimplemented: Read as '0'                                               |

| bit 29     | HVDR: High Voltage Detect Reset Flag bit                                 |

|            | 1 = High Voltage Detect (HVD) Reset has occurred, voltage on VCAP > 2.5V |

|            | 0 = HVD Reset has not occurred                                           |

| bit 28-10  | Unimplemented: Read as '0'                                               |

| bit 9      | CMR: Configuration Mismatch Reset Flag bit                               |

|            | 1 = Configuration mismatch Reset has occurred                            |

|            | 0 = Configuration mismatch Reset has not occurred                        |

| bit 8      | VREGS: Voltage Regulator Standby Enable bit                              |

|            | 1 = Regulator is enabled and is on during Sleep mode                     |

|            | 0 = Regulator is disabled and is off during Sleep mode                   |

| bit 7      | EXTR: External Reset (MCLR) Pin Flag bit                                 |

|            | 1 = Master Clear (pin) Reset has occurred                                |

|            | 0 = Master Clear (pin) Reset has not occurred                            |

| bit 6      | SWR: Software Reset Flag bit                                             |

|            | 1 = Software Reset was executed                                          |

|            | 0 = Software Reset as not executed                                       |

| bit 5      | Unimplemented: Read as '0'                                               |

| bit 4      | WDTO: Watchdog Timer Time-out Flag bit                                   |

|            | 1 = WDT Time-out has occurred                                            |

|            | 0 = WDT Time-out has not occurred                                        |

| bit 3      | SLEEP: Wake From Sleep Flag bit                                          |

|            | 1 = Device was in Sleep mode                                             |

|            | 0 = Device was not in Sleep mode                                         |

| bit 2      | IDLE: Wake From Idle Flag bit                                            |

|            | 1 = Device was in Idle mode                                              |

|            | 0 = Device was not in Idle mode                                          |

| bit 1      | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                             |

|            | 1 = Brown-out Reset has occurred                                         |

|            | 0 = Brown-out Reset has not occurred                                     |

| bit 0      | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup>                       |

|            | 1 = Power-on Reset has occurred                                          |

|            | 0 = Power-on Reset has not occurred                                      |

|            |                                                                          |

Note 1: User software must clear this bit to view next detection.

| Bit<br>Range | Bit<br>31/23/15/7 |     |     | Bit Bit B<br>29/21/13/5 28/20/12/4 27/19 |        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-----|-----|------------------------------------------|--------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04        | U-0               | U-0 | U-0 | U-0                                      | U-0    | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —   | —   | —                                        | —      | -                 | _                | —                |  |  |  |  |  |

| 23:16        | U-0               | U-0 | U-0 | U-0                                      | U-0    | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10        | —                 | _   | _   | -                                        | _      | -                 |                  | —                |  |  |  |  |  |

| 45.0         | R-0               | R-0 | R-0 | R-0                                      | R-0    | R-0               | R-0              | R-0              |  |  |  |  |  |

| 15:8         | CHSPTR<15:8>      |     |     |                                          |        |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0               | R-0 | R-0 | R-0                                      | R-0    | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          |                   |     |     | CHSPTF                                   | R<7:0> |                   |                  |                  |  |  |  |  |  |

## REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 |     |             |        |         | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-----|-------------|--------|---------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | U-0               | U-0 | U-0         | U-0    | U-0     | U-0 U-0           |                   | U-0               |                  |                  |  |  |  |

| 31:24        |                   | _   | _           | _      | —       |                   | —                 | —                 |                  |                  |  |  |  |

| 23:16        | U-0               | U-0 | U-0         | U-0    | U-0     | U-0               | U-0               | U-0               |                  |                  |  |  |  |

| 23.10        |                   | _   | _           | _      | —       |                   | —                 | —                 |                  |                  |  |  |  |

| 45.0         | R-0               | R-0 | R-0         | R-0    | R-0 R-0 |                   | R-0               | R-0               |                  |                  |  |  |  |

| 15:8         | CHDPTR<15:8>      |     |             |        |         |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0 | R-0 R-0 R-0 |        |         | R-0               | R-0               | R-0               |                  |                  |  |  |  |

| 7:0          |                   |     |             | CHDPTF | R<7:0>  |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Runge        |                   |                   |                   |                   |                   |                   |                  |                  |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 51.24        |                   | _                 | _                 | _                 | _                 | _                 | _                |                  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 10.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 7:0          | R/W-0 R/W-0       |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHPDAT            | <7:0>             |                   |                  |                  |  |

# REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

# Legend:

| =ogona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

## bit 7-0 CHPDAT<7:0>: Channel Data Register bits

<u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

All other modes: Unused.

# TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| SSS                         |                  |           |       |       |       |       |       |       |      | Bi   | ts   |      |      |      |      |           |          |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-----------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1     | 16/0 | All Resets |

| FB38                        | RPA14R           | 31:16     | _     | —     | _     | _     | —     | _     | _    | _    | _    | _    | —    | _    | —    | —<br>RPA1 | -        | _    | 0000       |

|                             |                  | 15:0      |       |       | —     |       | _     | —     |      |      |      | —    |      |      |      | RPA14     | 4<3:0>   |      | 0000       |

| FB3C                        | RPA15R           | 31:16     |       |       | —     |       |       | —     |      |      |      | —    |      |      |      | -         | -        | _    | 0000       |

|                             |                  | 15:0      | _     |       | _     |       |       | _     |      |      |      | _    |      | _    |      | RPA1      | 5<3:0>   |      | 0000       |

| FB40 RPB0                   | RPB0R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |           | —        | —    | 0000       |

|                             |                  | 15:0      | _     |       | _     |       |       | _     |      |      |      | _    |      | _    |      | RPBC      | r        |      | 0000       |

| FB44 RPB1                   | RPB1R            | 31:16     | _     |       | _     |       |       | _     |      |      |      | _    |      | _    |      |           |          |      | 0000       |

|                             |                  | 15:0      | _     | _     | —     |       | _     | —     | _    | —    | _    | _    | —    | _    |      | RPB1      | r        |      | 0000       |

| FB4C F                      | RPB2R            | 31:16     | _     |       | _     |       |       | _     |      | _    |      | _    |      | _    |      |           | —        |      | 0000       |

|                             |                  | 15:0      | _     |       | _     |       |       | _     |      | _    |      | _    |      | _    |      | RPB2      |          |      | 0000       |

|                             | RPB3R            | 31:16     | _     | _     | _     | _     | —     | _     | _    | —    | _    | _    | —    | _    | _    | _         | —        | _    | 0000       |

|                             |                  | 15:0      | _     | _     | —     |       | _     | —     |      | —    |      | _    | _    | _    |      | RPB3      | 3<3:0>   |      | 0000       |

|                             | RPB5R            | 31:16     | _     | _     | —     |       | _     | —     |      | —    |      | _    | _    | _    |      |           | —        | —    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    | —    | _    | _    | _    |      | RPB5      |          |      | 0000       |

| FB58                        | RPB6R            | 31:16     | _     | _     | —     |       | _     | —     |      | —    |      | _    | _    | _    |      |           | —        | _    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    | _    | _    | —    | _    |      | RPB6      |          |      | 0000       |

| FB5C                        | RPB7R            | 31:16     | _     | _     |       | _     | —     | _     | _    | _    | _    | _    | —    | _    | _    |           | —        | —    | 0000       |

|                             |                  | 15:0      |       | _     | _     |       | _     | —     |      | —    |      | _    | _    | _    |      | RPB7      | <3:0>    |      | 0000       |

| FB60                        | RPB8R            | 31:16     | _     | _     | _     | _     | _     | —     |      | —    | _    | _    | —    | _    | _    |           | —        | —    | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    | —    | _    | _    | _    |      | RPB8      | <3:0>    |      | 0000       |

| FB64                        | RPB9R            | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |           | —        |      | 0000       |

|                             |                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | —    | _    |      | RPB9      | <3:0>    |      | 0000       |

| FB68                        | RPB10R           | 31:16     | _     | _     | _     | _     | —     | _     | _    | —    | _    | _    | —    | _    | _    | —         |          | —    | 0000       |

|                             |                  | 15:0      | _     | _     | _     |       | _     | —     |      |      |      | _    | _    | _    |      | RPB1      |          |      | 0000       |

| FB78                        | RPB14R           | 31:16     | _     |       |       |       |       |       |      |      |      | _    |      |      |      | -         | <u> </u> |      | 0000       |

|                             |                  | 15:0      | _     |       |       | _     | —     |       | _    | _    | _    | _    | _    | _    |      | RPB1      | 4<3:0>   |      | 0000       |

| FB7C                        | RPB15R           | 31:16     | _     |       | _     | _     | —     |       | _    | _    | _    | _    | _    | _    | —    |           |          | —    | 0000       |

|                             |                  | 15:0      | _     |       |       | _     | —     | _     | —    | _    | _    | _    | _    | _    |      | RPB1      | 5<3:0>   |      | 0000       |

| FB84                        | RPC1R            | 31:16     | _     |       | —     | _     | —     | —     | —    | _    | _    | —    | —    | —    | _    |           | —        | —    | 0000       |

|                             |                  | 15:0      | —     | —     | —     | -     | —     | —     | —    | _    | _    | —    | —    | —    |      | RPC1      | <3:0>    |      | 0000       |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

DS60001290D-page 153

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

|              |                                                                                                                                               | PIxCON: SF                                                                                                                                                      |                                                                                                                |                                                                                                   |                                                                                  | D:/               | <b>D</b> **      | D:"                  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------|------------------|----------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7                                                                                                                             | Bit<br>30/22/14/6                                                                                                                                               | Bit<br>29/21/13/5                                                                                              | Bit<br>28/20/12/4                                                                                 | Bit<br>27/19/11/3                                                                | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

| 31:24        | R/W-0                                                                                                                                         | R/W-0                                                                                                                                                           | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |  |

| 31.24        | FRMEN                                                                                                                                         | FRMSYNC                                                                                                                                                         | FRMPOL                                                                                                         | MSSEN                                                                                             | FRMSYPW                                                                          | F                 | RMCNT<2:0        | )>                   |  |

| 23:16        | R/W-0                                                                                                                                         | U-0                                                                                                                                                             | U-0                                                                                                            | U-0                                                                                               | U-0                                                                              | U-0               | R/W-0            | R/W-0                |  |

| 23.10        | MCLKSEL <sup>(2)</sup>                                                                                                                        | _                                                                                                                                                               | _                                                                                                              | —                                                                                                 | _                                                                                | —                 | SPIFE            | ENHBUF <sup>(2</sup> |  |

| 15:8         | R/W-0                                                                                                                                         | U-0                                                                                                                                                             | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |  |

| 15.0         | ON <sup>(1)</sup>                                                                                                                             | _                                                                                                                                                               | SIDL                                                                                                           | DISSDO                                                                                            | MODE32                                                                           | MODE16            | SMP              | CKE <sup>(3)</sup>   |  |

| 7.0          | R/W-0                                                                                                                                         | R/W-0                                                                                                                                                           | R/W-0                                                                                                          | R/W-0                                                                                             | R/W-0                                                                            | R/W-0             | R/W-0            | R/W-0                |  |

| 7:0          | SSEN                                                                                                                                          | CKP <sup>(4)</sup>                                                                                                                                              | MSTEN                                                                                                          | DISSDI                                                                                            | STXISE                                                                           | L<1:0>            | SRXIS            | EL<1:0>              |  |

| Legend:      |                                                                                                                                               |                                                                                                                                                                 |                                                                                                                |                                                                                                   |                                                                                  |                   |                  |                      |  |

| R = Read     | lable hit                                                                                                                                     |                                                                                                                                                                 | W = Writable                                                                                                   | a hit                                                                                             |                                                                                  | mented bit, rea   | ad as '0'        |                      |  |

| -n = Valu    |                                                                                                                                               |                                                                                                                                                                 | '1' = Bit is se                                                                                                |                                                                                                   | '0' = Bit is cle                                                                 |                   | x = Bit is un    | known                |  |

|              | e al POR                                                                                                                                      |                                                                                                                                                                 |                                                                                                                | ÷l                                                                                                |                                                                                  | areu              | x = bit is un    | IKHOWH               |  |

| bit 31       | 0 = Framed S                                                                                                                                  | SPI support is<br>SPI support is                                                                                                                                | enabled (SS<br>disabled                                                                                        | _                                                                                                 | S FSYNC input                                                                    |                   |                  |                      |  |

| bit 30       | FRMSYNC: F<br>1 = Frame sy<br>0 = Frame sy                                                                                                    | nc pulse inpu                                                                                                                                                   | it (Slave mod                                                                                                  | e)                                                                                                | SSx pin bit (Fra                                                                 | amed SPI mo       | de only)         |                      |  |

| bit 29       | <b>FRMPOL:</b> Fra<br>1 = Frame pu<br>0 = Frame pu                                                                                            | ame Sync Po<br>Ilse is active-                                                                                                                                  | larity bit (Frar<br>high                                                                                       |                                                                                                   | e only)                                                                          |                   |                  |                      |  |

| bit 28       | MSSEN: Mas<br>1 = Slave sele                                                                                                                  | ter Mode Sla<br>ect SPI suppo<br>ode. Polarity i                                                                                                                | ve Select Ena<br>ort enabled. T<br>s determined                                                                | he <u>SS</u> pin is a by the FRMF                                                                 | automatically o<br>POL bit.                                                      | driven during t   | transmission     | in                   |  |

| bit 27       | <b>FRMSYPW:</b> F                                                                                                                             | Frame Sync F                                                                                                                                                    | ulse Width b                                                                                                   | it                                                                                                |                                                                                  |                   |                  |                      |  |

|              | 0 = Frame sy                                                                                                                                  |                                                                                                                                                                 |                                                                                                                | viac                                                                                              |                                                                                  |                   |                  |                      |  |

| bit 26-24    | FRMCNT<2:0<br>pulse. This bit<br>111 = Reserv<br>110 = Reserv<br>101 = Genera<br>010 = Genera<br>010 = Genera<br>010 = Genera<br>001 = Genera | t is only valid<br>red; do not us<br>red; do not us<br>ate a frame sy<br>ate a frame sy | in FRAMED_<br>e<br>e<br>ync pulse on e<br>ync pulse on e<br>ync pulse on e<br>ync pulse on e<br>ync pulse on e | SYNC mode<br>every 32 data<br>every 16 data<br>every 8 data o<br>every 4 data o<br>every 2 data o | characters<br>characters<br>characters<br>characters<br>characters<br>characters | nber of data c    | characters tra   | ansmitted pe         |  |

| bit 23       | <b>MCLKSEL:</b> M<br>1 = REFCLK<br>0 = PBCLK is                                                                                               | is used by the                                                                                                                                                  | e Baud Rate                                                                                                    |                                                                                                   |                                                                                  |                   |                  |                      |  |

| bit 22-18    | Unimplemen                                                                                                                                    | ted: Read as                                                                                                                                                    | '0'                                                                                                            |                                                                                                   |                                                                                  |                   |                  |                      |  |

| Note 1:      | SYSCLK cyc                                                                                                                                    | le immediatel                                                                                                                                                   | y following th                                                                                                 | e instruction                                                                                     | e should not re<br>that clears the                                               |                   |                  | SFRs in the          |  |

| 2:           | This bit can c                                                                                                                                | •                                                                                                                                                               |                                                                                                                |                                                                                                   |                                                                                  |                   |                  |                      |  |

| 3:           | This bit is not mode (FRME                                                                                                                    |                                                                                                                                                                 | Framed SPI n                                                                                                   | node. The use                                                                                     | er should prog                                                                   | ram this bit to   | 0 '0' for the F  | ramed SPI            |  |

| 4:           | When AUDE                                                                                                                                     | When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value                                                      |                                                                                                                |                                                                                                   |                                                                                  |                   |                  |                      |  |

####

of CKP.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | —                 | _                 | _                 | —                 | —                 | —                | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                 | _                 | _                 | —                 | -                 | —                | _                |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |  |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |  |

# REGISTER 19-1: UxMODE: UARTx MODE REGISTER

# Legend:

| Legend.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

|              | Leister 20-7. Thistal TARALLEET ORT STATUS REGISTER (SEAVE MODES ORET) |                   |                   |                   |                   |                   |                  |                  |

|--------------|------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7                                                      | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0                                                                    | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                                                                      | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0                                                                    | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                                                                      | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | R-0                                                                    | R/W-0, HSC        | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF                                                                    | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1                                                                    | R/W-0, HSC        | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE                                                                    | OBUF              |                   |                   | OB3E              | OB2E              | OB1E             | OB0E             |

# REGISTER 20-7: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HSC = Set by Hardware; Cleared by Software |                                    |                    |  |  |

|-------------------|--------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                           | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                           | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

0 = No overflow occurred

- bit 13-12 **Unimplemented:** Read as '0'

# bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 OBE: Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

- 0 = No underflow occurredbit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 Output buffer is ampty (writing data to the buffer will

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

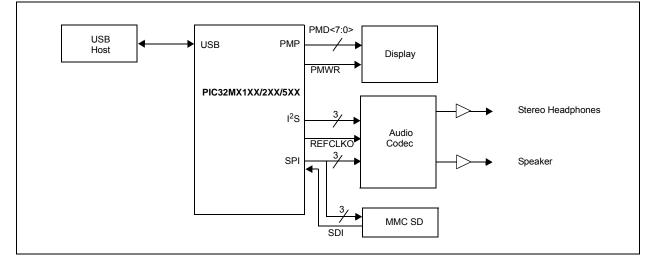

# 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual", which is available the Microchip from web site (www.microchip.com/PIC32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

- Up to 48 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- · Eight conversion result format options

- · Operation during CPU Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. The 10-bit ADC has up to 28 analog input pins, designated AN0-AN27. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

4: This selection is only used with CTMU capacitive and time measurement.

# REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED) bit 20-16 FSEL10<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 FLTEN9: Filter 9 Enable bit bit 15 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL9<1:0>: Filter 9 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL9<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN8: Filter 8 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL8<1:0>: Filter 8 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL8<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. Note:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0                   | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |

| 51.24        | EDG1MOD           | OD EDG1POL EDG1SEL<3:0> |                   |                     |                   | EDG2STAT          | EDG1STAT               |                  |  |

| 23:16        | R/W-0             | R/W-0                   | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |  |

| 23.10        | EDG2MOD           | EDG2POL                 |                   | EDG2S               | EL<3:0>           |                   | _                      | —                |  |

| 15.0         | R/W-0             | U-0                     | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |

| 15:8         | ON                | —                       | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |  |

| 7:0          | R/W-0             | R/W-0                   | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |  |

| 7:0          |                   |                         | ITRIM             | 1<5:0>              |                   |                   | IRNG                   | <1:0>            |  |

# REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

#### Legend:

| 8                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 EDG1MOD: Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

# bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = IC4 Capture Event is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

# 0000 = Timer1 Event is selected

# bit 25 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

- 1 = Edge 2 has occurred

- 0 = Edge 2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | R/P              | R/P              |

| 31:24        | —                 | —                 | —                 | -                 | —                 | _                 | FWDTWI           | NSZ<1:0>         |

| 00.40        | R/P               | R/P               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |

| 23:16        | FWDTEN            | WINDIS            | —                 |                   |                   | WDTPS<4:0>        |                  |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |

| 15:8         | FCKSM             | /<1:0>            | FPBDI             | V<1:0>            | <1:0> — OSC       |                   | POSCM            | OD<1:0>          |

| 7.0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P               | R/P              | R/P              |

| 7:0          | IESO              | —                 | FSOSCEN           |                   |                   | F                 | NOSC<2:0>        | •                |

## REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | r = Reserved bit | P = Programmable bit                    |  |  |

|-------------------|------------------|-----------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |

bit 31-26 Reserved: Write '1'

bit 25-24 **FWDTWINSZ:** Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

### bit 23 FWDTEN: Watchdog Timer Enable bit

- 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

### bit 22 WINDIS: Watchdog Timer Window Enable bit

- 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

- bit 21 Reserved: Write '1'

#### bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| ~ |                                                              |

|---|--------------------------------------------------------------|

|   | 10100 <b>= 1:1048576</b>                                     |

|   | 10011 <b>= 1:524288</b>                                      |

|   | 10010 <b>= 1:262144</b>                                      |

|   | 10001 <b>= 1:131072</b>                                      |

|   | 10000 <b>= 1:65536</b>                                       |

|   | 01111 <b>= 1:32768</b>                                       |

|   | 01110 <b>= 1:16384</b>                                       |

|   | 01101 <b>= 1:8192</b>                                        |

|   | 01100 <b>= 1:4096</b>                                        |

|   | 01011 <b>= 1:2048</b>                                        |

|   | 01010 <b>= 1:1024</b>                                        |

|   | 01001 <b>= 1:512</b>                                         |

|   | 01000 <b>= 1:256</b>                                         |

|   | 00111 <b>= 1:128</b>                                         |

|   | 00110 <b>= 1:64</b>                                          |

|   | 00101 <b>= 1:32</b>                                          |

|   | 00100 = 1:16                                                 |

|   | 00011 <b>= 1</b> :8                                          |

|   | 00010 = 1:4                                                  |

|   | 00001 <b>= 1:2</b>                                           |

|   | 00000 = 1:1                                                  |

|   | All other combinations not shown result in operation = 10100 |

|   | · ·                                                          |

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | R/P               | R/P               | R/P               | R/P               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 | —                 | —                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | _                 | _                 | _                 | -                 | _                 | -                | _                |  |

| 15:8         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 10.0         | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 7:0          | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

## REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bit                    |                  |  |  |

|-------------------|------------------|-----------------------------------------|------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b                     | bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |                  |  |  |

bit 31 FVBUSONIO: USB VBUS\_ON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 **IOL1WAY:** Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDL1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-16 Unimplemented: Read as '0'

- bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

### TABLE 31-10: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |         |      |       |            |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                                                                                                                                                                                                                                                                       | Min. <sup>(1)</sup> | Typical | Max. | Units | Conditions |

| BO10               | Vbor   | BOR Event on VDD transition high-to-low <sup>(2)</sup>                                                                                                                                                                                                                                | 2.0                 |         | 2.3  | V     | —          |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

# TABLE 31-11: ELECTRICAL CHARACTERISTICS: HVD

| DC CHARACTERISTICS           |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |         |      |       |            |

|------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|-------|------------|

| Param.<br>No. <sup>(1)</sup> | Symbol | Characteristics                                                                                                                                                                                                                                                                 | Min. | Typical | Max. | Units | Conditions |

| HV10                         | Vhvd   | High Voltage Detect on VCAP pin                                                                                                                                                                                                                                                 | —    | 2.5     |      | V     | _          |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

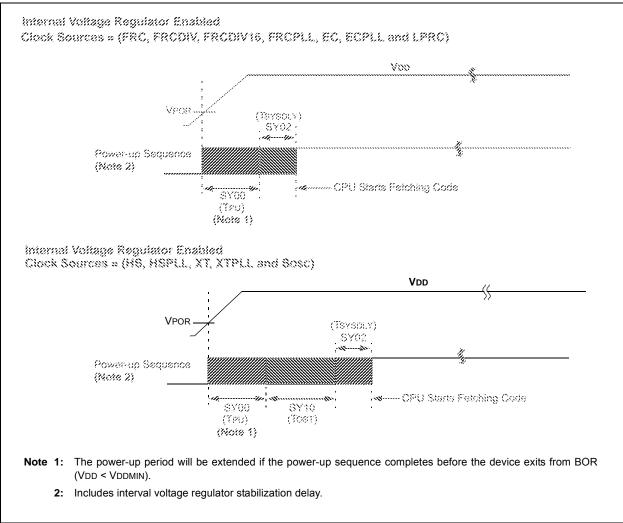

# FIGURE 31-4: POWER-ON RESET TIMING CHARACTERISTICS

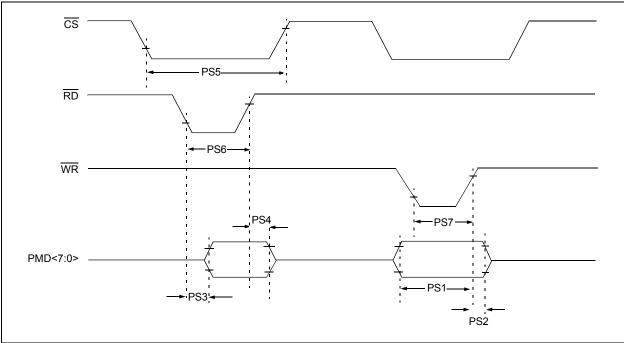

# FIGURE 31-20: PARALLEL SLAVE PORT TIMING

# 32.1 DC Characteristics

## TABLE 32-1: OPERATING MIPS VS. VOLTAGE

|                | Voo Bango                              | Temp. Range    | Max. Frequency                          |  |

|----------------|----------------------------------------|----------------|-----------------------------------------|--|

| Characteristic | VDD Range<br>(in Volts) <sup>(1)</sup> | (in °C)        | PIC32MX1XX/2XX/5XX 64/100-pin<br>Family |  |

| MDC5           | VBOR-3.6V                              | -40°C to +85°C | 50 MHz                                  |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for BOR values.

#### TABLE 32-2: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA                            | CTERISTICS             | 6    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |  |  |

|-------------------------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Parameter<br>No.                    | Typical <sup>(3)</sup> | Max. | Units                                                                                                                                           | Conditions |  |  |

| Operating Current (IDD) (Note 1, 2) |                        |      |                                                                                                                                                 |            |  |  |

| MDC24                               | 25                     | 40   | mA                                                                                                                                              | 50 MHz     |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- **3:** RTCC and JTAG are disabled

- **4:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

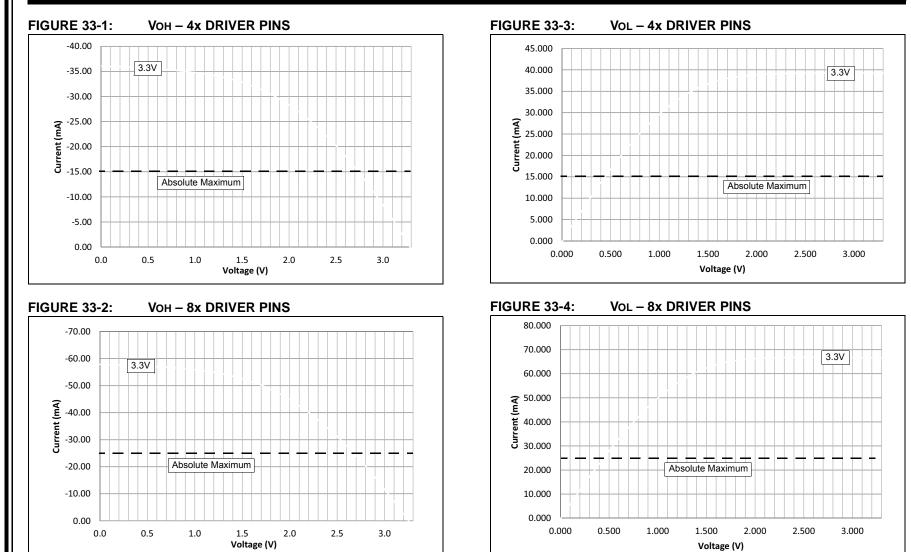

# 33.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

PIC32MX1XX/2XX/5XX 64/100-PIN FAMIL

© 2014-2016 Microchip Technology Inc

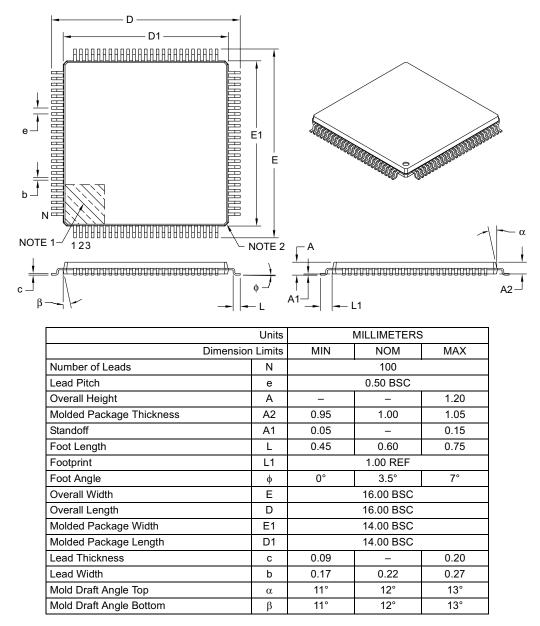

# 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

| DEVCFG0 (Device Configuration Word 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEVCFG1 (Device Configuration Word 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |