Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

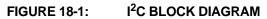

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 49                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 28x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx530f128h-50i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4: PIN NAMES FOR 100-PIN GENERAL PURPOSE DEVICES

### **100-PIN TQFP (TOP VIEW)**

### PIC32MX130F128L PIC32MX150F256L PIC32MX170F512L

100

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                   |

|-------|---------------------------------------|-------|---------------------------------|

| 1     | AN28/RG15                             | 36    | Vss                             |

| 2     | Vdd                                   | 37    | VDD                             |

| 3     | AN22/RPE5/PMD5/RE5                    | 38    | TCK/CTED2/RA1                   |

| 4     | AN23/PMD6/RE6                         | 39    | AN34/RPF13/SCK3/RF13            |

| 5     | AN27/PMD7/RE7                         | 40    | AN35/RPF12/RF12                 |

| 6     | AN29/RPC1/RC1                         | 41    | AN12/PMA11/RB12                 |

| 7     | AN30/RPC2/RC2                         | 42    | AN13/PMA10/RB13                 |

| 8     | AN31/RPC3/RC3                         | 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 9     | RPC4/CTED7/RC4                        | 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 10    | AN16/C1IND/RPG6/SCK2/PMA5/RG6         | 45    | Vss                             |

| 11    | AN17/C1INC/RPG7/PMA4/RG7              | 46    | VDD                             |

| 12    | AN18/C2IND/RPG8/PMA3/RG8              | 47    | AN36/RPD14/RD14                 |

| 13    | MCLR                                  | 48    | AN37/RPD15/SCK4/RD15            |

| 14    | AN19/C2INC/RPG9/PMA2/RG9              | 49    | RPF4/PMA9/RF4                   |

| 15    | Vss                                   | 50    | RPF5/PMA8/RF5                   |

| 16    | Vdd                                   | 51    | RPF3/RF3                        |

| 17    | TMS/CTED1/RA0                         | 52    | AN38/RPF2/RF2                   |

| 18    | AN32/RPE8/RE8                         | 53    | AN39/RPF8/RF8                   |

| 19    | AN33/RPE9/RE9                         | 54    | RPF7/RF7                        |

| 20    | AN5/C1INA/RPB5/RB5                    | 55    | RPF6/SCK1/INT0/RF6              |

| 21    | AN4/C1INB/RB4                         | 56    | SDA1/RG3                        |

| 22    | PGED3/AN3/C2INA/RPB3/RB3              | 57    | SCL1/RG2                        |

| 23    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 | 58    | SCL2/RA2                        |

| 24    | PGEC1/AN1/RPB1/CTED12/RB1             | 59    | SDA2/RA3                        |

| 25    | PGED1/AN0/RPB0/RB0                    | 60    | TDI/CTED9/RA4                   |

| 26    | PGEC2/AN6/RPB6/RB6                    | 61    | TDO/RA5                         |

| 27    | PGED2/AN7/RPB7/CTED3/RB7              | 62    | VDD                             |

| 28    | VREF-/PMA7/RA9                        | 63    | OSC1/CLKI/RC12                  |

| 29    | VREF+/PMA6/RA10                       | 64    | OSC2/CLKO/RC15                  |

| 30    | AVdd                                  | 65    | Vss                             |

| 31    | AVss                                  | 66    | RPA14/RA14                      |

| 32    | AN8/RPB8/CTED10/RB8                   | 67    | RPA15/RA15                      |

| 33    | AN9/RPB9/CTED4/RB9                    | 68    | RPD8/RTCC/RD8                   |

| 34    | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 69    | RPD9/RD9                        |

| 35    | AN11/PMA12/RB11                       | 70    | RPD10/PMA15/RD10                |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

### TABLE 5: PIN NAMES FOR 100-PIN USB DEVICES

### **100-PIN TQFP (TOP VIEW)**

PIC32MX230F128L PIC32MX530F128L PIC32MX250F256L PIC32MX550F256L PIC32MX270F512L PIC32MX570F512L

100

| Pin # | Full Pin Name                         | Div | n #  | Full Pin Name                   |

|-------|---------------------------------------|-----|------|---------------------------------|

|       |                                       |     |      |                                 |

| 1     | AN28/RG15                             |     | -    | /ss                             |

| 2     | VDD                                   | -   |      |                                 |

| 3     | AN22/RPE5/PMD5/RE5                    | 3   | .0   | ICK/CTED2/RA1                   |

| 4     | AN23/PMD6/RE6                         | 3   | -    | AN34/RPF13/SCK3/RF13            |

| 5     | AN27/PMD7/RE7                         | 4   | .0 A | AN35/RPF12/RF12                 |

| 6     | AN29/RPC1/RC1                         | 4   | -1 A | AN12/PMA11/RB12                 |

| 7     | AN30/RPC2/RC2                         | 4   | -2 A | AN13/PMA10/RB13                 |

| 8     | AN31/RPC3/RC3                         | 4   | -3 A | AN14/RPB14/CTED5/PMA1/RB14      |

| 9     | RPC4/CTED7/RC4                        | 4   | 4 A  | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 10    | AN16/C1IND/RPG6/SCK2/PMA5/RG6         | 4   | ·5 \ | /ss                             |

| 11    | AN17/C1INC/RPG7/PMA4/RG7              | 4   | ·6 \ | /DD                             |

| 12    | AN18/C2IND/RPG8/PMA3/RG8              | 4   | ·7 A | AN36/RPD14/RD14                 |

| 13    | MCLR                                  | 4   | -8 A | AN37/RPD15/SCK4/RD15            |

| 14    | AN19/C2INC/RPG9/PMA2/RG9              | 4   | .9 F | RPF4/PMA9/RF4                   |

| 15    | Vss                                   | 5   | 60 F | RPF5/PMA8/RF5                   |

| 16    | Vdd                                   | 5   | i1 L | JSBID/RPF3/RF3                  |

| 17    | TMS/CTED1/RA0                         | 5   | 2 A  | AN38/RPF2/RF2                   |

| 18    | AN32/RPE8/RE8                         | 5   | 3 A  | AN39/RPF8/RF8                   |

| 19    | AN33/RPE9/RE9                         | 5   | i4 \ | /BUS                            |

| 20    | AN5/C1INA/RPB5/VBUSON/RB5             | 5   | 5 \  | /USB3V3                         |

| 21    | AN4/C1INB/RB4                         | 5   | 6 E  | )-                              |

| 22    | PGED3/AN3/C2INA/RPB3/RB3              | 5   | 7 E  | )+                              |

| 23    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 | 5   | 8 5  | SCL2/RA2                        |

| 24    | PGEC1/AN1/RPB1/CTED12/RB1             | 5   | 9 5  | SDA2/RA3                        |

| 25    | PGED1/AN0/RPB0/RB0                    | 6   | т 0  | IDI/CTED9/RA4                   |

| 26    | PGEC2/AN6/RPB6/RB6                    | 6   | i1 T | IDO/RA5                         |

| 27    | PGED2/AN7/RPB7/CTED3/RB7              | 6   | i2 \ | /DD                             |

| 28    | VREF-/PMA7/RA9                        | 6   | i3 ( | DSC1/CLKI/RC12                  |

| 29    | VREF+/PMA6/RA10                       | 6   | i4 ( | DSC2/CLKO/RC15                  |

| 30    | AVdd                                  | 6   | 5 \  | /ss                             |

| 31    | AVss                                  | 6   | 6 F  | RPA14/SCL1/RA14                 |

| 32    | AN8/RPB8/CTED10/RB8                   | 6   | 57 F | RPA15/SDA1/RA15                 |

| 33    | AN9/RPB9/CTED4/RB9                    | 6   | i8 F | RPD8/RTCC/RD8                   |

| 34    | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 6   | ;9 F | RPD9/RD9                        |

| 35    | AN11/PMA12/RB11                       | 7   | '0 F | RPD10/SCK1/PMA15/RD10           |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 =Clock is multiplied by 17

- 001 =Clock is multiplied by 16

- 000 = Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = PLL module is in lock or PLL module start-up timer is satisfied

- 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 **CF:** Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

|              |                   | • • • • • • • • • •     |                         |                   |                      |                   |                       |                         |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | —                 | —                       | _                       |                   | —                    | —                 | —                     | —                       |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | —                 | —                       | _                       |                   | —                    | _                 | _                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.6         | —                 | —                       | _                       |                   | —                    | —                 | —                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | UIALLII           |                         |                         | IULLII            |                      | 00111             |                       | DETACHIF <sup>(6)</sup> |

|              | •                 | •                       |                         |                   |                      |                   |                       |                         |

### REGISTER 10-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit |                    |  |

|-------------------|-------------------------|----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented b        | vit, read as '0'   |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared       | x = Bit is unknown |  |

### bit 31-8 Unimplemented: Read as '0'

| bit 7 |    | STALLIF: STALL Handshake Interrupt bit                                                                                                                                                 |

|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |    | 1 = In Host mode, a STALL handshake was received during the handshake phase of the transaction                                                                                         |

|       |    | In Device mode, a STALL handshake was transmitted during the handshake phase of the transaction                                                                                        |

|       |    | 0 = STALL handshake has not been sent                                                                                                                                                  |

| bit 6 |    | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup>                                                                                                                               |

|       |    | 1 = Peripheral attachment was detected by the USB module                                                                                                                               |

|       |    | 0 = Peripheral attachment was not detected                                                                                                                                             |

| bit 5 |    | RESUMEIF: Resume Interrupt bit <sup>(2)</sup>                                                                                                                                          |

|       |    | 1 = K-State is observed on the D+ or D- pin for 2.5 $\mu$ s                                                                                                                            |

|       |    | 0 = K-State is not observed                                                                                                                                                            |

| bit 4 |    | IDLEIF: Idle Detect Interrupt bit                                                                                                                                                      |

|       |    | 1 = Idle condition detected (constant Idle state of 3 ms or more)                                                                                                                      |

|       |    | 0 = No Idle condition detected                                                                                                                                                         |

| bit 3 |    | <b>TRNIF:</b> Token Processing Complete Interrupt bit <sup>(3)</sup>                                                                                                                   |

|       |    | <ul> <li>1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information</li> <li>0 = Processing of current token not complete</li> </ul> |

| h:+ 0 |    |                                                                                                                                                                                        |

| bit 2 |    | <b>SOFIF:</b> SOF Token Interrupt bit<br>1 = SOF token received by the peripheral or the SOF threshold reached by the host                                                             |

|       |    | 0 = SOF token was not received nor threshold reached                                                                                                                                   |

| bit 1 |    | <b>UERRIF:</b> USB Error Condition Interrupt bit <sup>(4)</sup>                                                                                                                        |

| DICT  |    | 1 = Unmasked error condition has occurred                                                                                                                                              |

|       |    | 0 = Unmasked error condition has not occurred                                                                                                                                          |

| bit 0 |    | URSTIF: USB Reset Interrupt bit (Device mode) <sup>(5)</sup>                                                                                                                           |

| 2.00  |    | 1 = Valid USB Reset has occurred                                                                                                                                                       |

|       |    | 0 = No USB Reset has occurred                                                                                                                                                          |

| bit 0 |    | DETACHIF: USB Detach Interrupt bit (Host mode) <sup>(6)</sup>                                                                                                                          |

|       |    | 1 = Peripheral detachment was detected by the USB module                                                                                                                               |

|       |    | 0 = Peripheral detachment was not detected                                                                                                                                             |

| Note  | 1. | This bit is valid only if the HOSTEN bit is set (see Register 10-11), there is no activity on the USB for                                                                              |

| noto  | •• | $2.5 \mu$ s, and the current bus state is not SE0.                                                                                                                                     |

|       | 2: | When not in Suspend mode, this interrupt should be disabled.                                                                                                                           |

|       | 3: | Clearing this bit will cause the STAT FIFO to advance.                                                                                                                                 |

|       | 4: | Only error conditions enabled through the U1EIE register will set this bit.                                                                                                            |

|       | 5: | Device mode.                                                                                                                                                                           |

|       | 6: | Host mode.                                                                                                                                                                             |

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | —                 | —                 | —                 | -                 | -                 | —                | -                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | —                 | —                 | —                 | -                 |                   | —                | -                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 10.0         | _                 | —                 | —                 | —                 | _                 | _                 | —                | -                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | BDTPTRH<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

### REGISTER 10-18: U1BDTP2: USB BDT PAGE 2 REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** BDT Base Address bits This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

| ILE OIO II   |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   | —                 | —                 |                   | _                 | _                 |                  | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | -                 | _                 | —                 | -                 | —                 | _                 | -                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | -                 | _                 | —                 | -                 | —                 | _                 | -                | —                |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |  |  |

### REGISTER 10-19: U1BDTP3: USB BDT PAGE 3 REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | —                 | -                 | _                 | —                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | —                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | e]R<3:0>         |                  |

### REGISTER 11-1: [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-4 Unimplemented: Read as '0'

### bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

### REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 |                   |                  | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | —                 | —                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | RPnR              | <3:0>            |                  |

### Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

# REGISTER 15-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)('x' = 1 THROUGH 5)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### 16.0 OUTPUT COMPARE

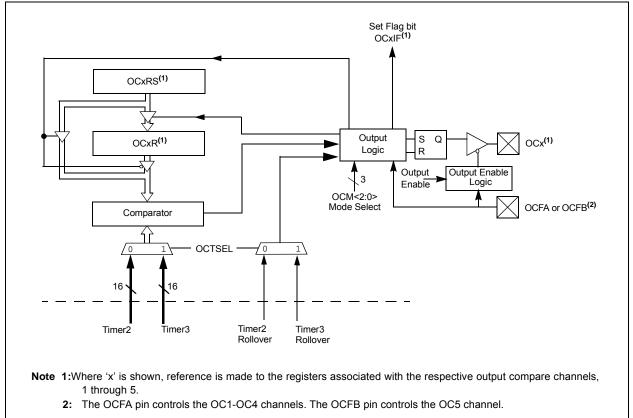

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are the key features of this module:

- · Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- · Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

### FIGURE 16-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   | —                 | _                 | _                 | —                 | —                 | —                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | —                 | _                 | _                 | _                 | —                 | -                 | —                | _                |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |  |  |

|              | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |  |  |

### REGISTER 19-1: UxMODE: UARTx MODE REGISTER

### Legend:

| Legend.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

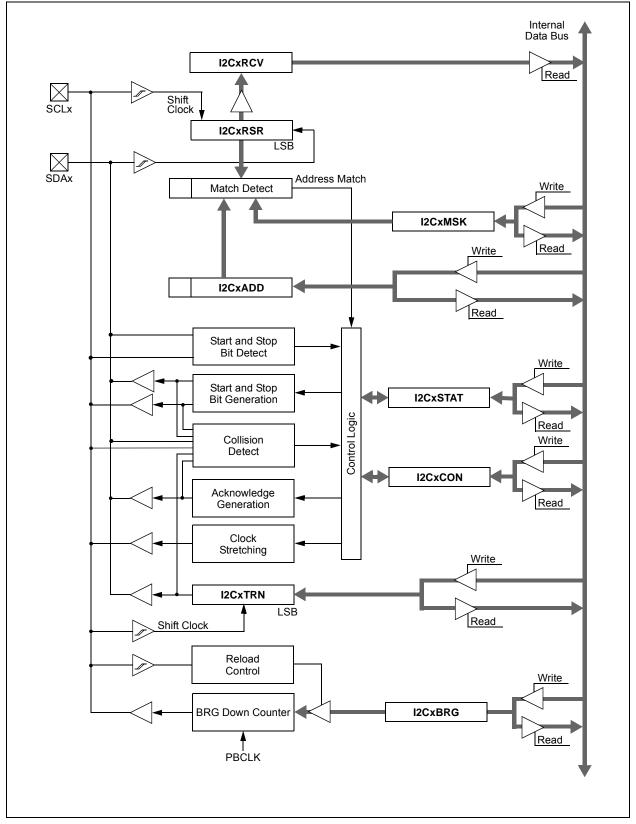

#### 21.0 **REAL-TIME CLOCK AND** CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available the Microchip web from site (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time.

The following are the key features of this module:

- · Time: hours. minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- · Provides calendar: Weekday, date, month and year

- · Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- · User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- · Requirements: External 32.768 kHz clock crystal

- · Alarm pulse or seconds clock output on RTCC pin

# RTCC BLOCK DIAGRAM

### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7                                 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|---------------------------------------------------|-------------------|-------------------|-------------------|-----------------------------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-x                                             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x R/W-x       |                  | R/W-x            |  |

| 31:24        |                                                   | YEAR1             | 0<3:0>            |                   | YEAR01<3:0>                             |                   |                  |                  |  |

| 00.40        | R/W-x                                             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                                                   | MONTH             | 10<3:0>           | MONTH01<3:0>      |                                         |                   |                  |                  |  |

|              | R/W-x                                             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                                                   | DAY10             | <3:0>             |                   | DAY01<3:0>                              |                   |                  |                  |  |

| 7.0          | U-0                                               | U-0               | U-0               | U-0               | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0          | _                                                 | —                 | —                 | —                 | WDAY01<3:0>                             |                   |                  |                  |  |

|              |                                                   | •                 |                   |                   |                                         |                   |                  |                  |  |

| Legend:      |                                                   |                   |                   |                   |                                         |                   |                  |                  |  |

| R = Read     | = Readable bit U = Unimplemented bit, read as '0' |                   |                   |                   |                                         |                   |                  |                  |  |

| -n = Value   | e at POR                                          |                   | '1' = Bit is se   | et                | '0' = Bit is cleared x = Bit is unknown |                   |                  |                  |  |

### REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digits

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1s place digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

### 26.1 Control Registers

### TABLE 26-1: CTMU REGISTER MAP

| ess                      |                                 | 6         | Bits    |         |          |       |         |          |          |          |                       |         | s    |       |          |      |      |      |           |

|--------------------------|---------------------------------|-----------|---------|---------|----------|-------|---------|----------|----------|----------|-----------------------|---------|------|-------|----------|------|------|------|-----------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11   | 26/10    | 25/9     | 24/8     | 23/7                  | 22/6    | 21/5 | 20/4  | 19/3     | 18/2 | 17/1 | 16/0 | All Reset |

| 1 200                    | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | EL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD               | EDG2POL |      | EDG25 | SEL<3:0> |      |      |      | 0000      |

| A200                     | CINUCON                         | 15:0      | ON      | -       | CTMUSIDL | TGEN  | EDGEN   | EDGSEQEN | IDISSEN  | CTTRIG   | IG ITRIM<5:0> IRNG<1: |         |      | <1:0> | 0000     |      |      |      |           |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

NOTES:

NOTES:

## 32.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX/5XX 64/100-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 31.0 "40 MHz Electrical Characteristics"**, with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 31.0** "40 MHz Electrical Characteristics", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX/5XX 64/100-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

### Absolute Maximum Ratings

### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +85°C            |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                              | -0.3V to +4.0V           |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 2.3V$ (Note 3) | -0.3V to +5.5V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | -0.3V to +3.6V           |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      | 15 mA                    |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 32-2).

- 3: See the "Device Pin Tables" section for the 5V tolerant pins.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

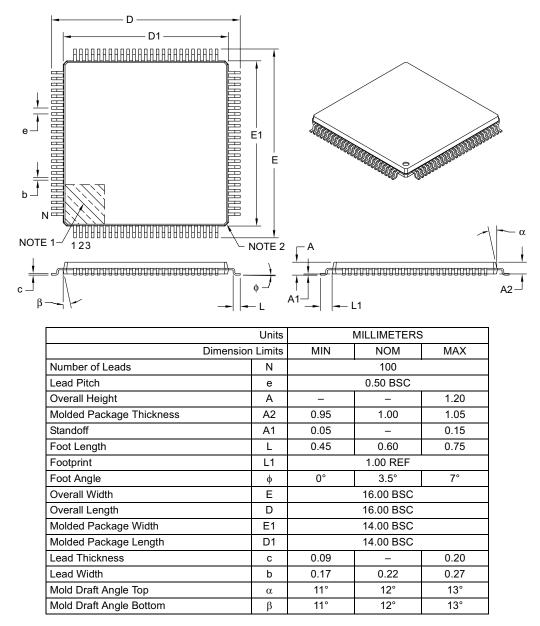

### 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

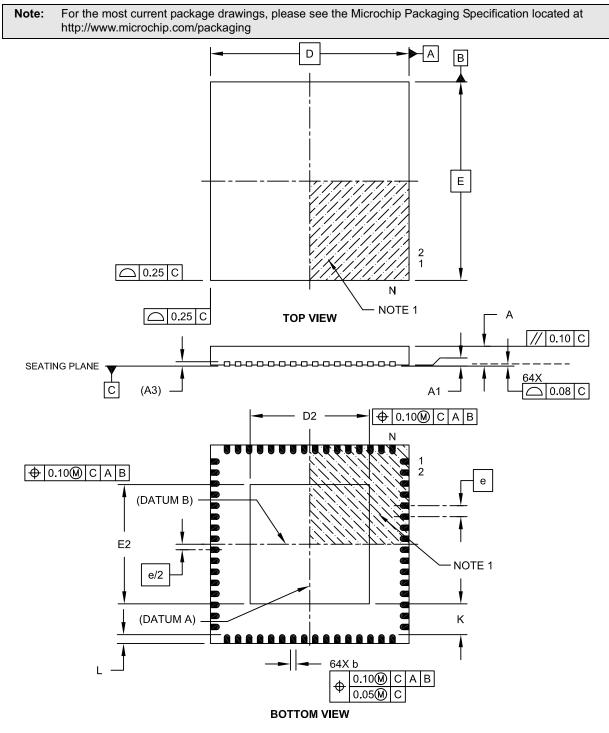

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2