Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx530f128h-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| IABLE 1-1 |                        | umber           |             | (•             |                                                                                                                                                                                        |

|-----------|------------------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name  | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                            |

| AN36      |                        | 47              | I           | Analog         |                                                                                                                                                                                        |

| AN37      | _                      | 48              | I           | Analog         |                                                                                                                                                                                        |

| AN38      | _                      | 52              | I           | Analog         |                                                                                                                                                                                        |

| AN39      | _                      | 53              | I           | Analog         |                                                                                                                                                                                        |

| AN40      | _                      | 79              | I           | Analog         |                                                                                                                                                                                        |

| AN41      | _                      | 80              | I           | Analog         | Analog input channels                                                                                                                                                                  |

| AN42      | _                      | 83              | Ι           | Analog         | Analog input channels.                                                                                                                                                                 |

| AN43      |                        | 84              | I           | Analog         |                                                                                                                                                                                        |

| AN44      | _                      | 87              | I           | Analog         |                                                                                                                                                                                        |

| AN45      | _                      | 88              | Ι           | Analog         |                                                                                                                                                                                        |

| AN46      | _                      | 93              | I           | Analog         |                                                                                                                                                                                        |

| AN47      | _                      | 94              | I           | Analog         |                                                                                                                                                                                        |

| CLKI      | 39                     | 63              | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                 |

| CLKO      | 40                     | 64              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with the OSC2 pin function. |

| OSC1      | 39                     | 63              | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                        |

| OSC2      | 40                     | 64              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                               |

| SOSCI     | 47                     | 73              | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                         |

| SOSCO     | 48                     | 74              | 0           | _              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                        |

| IC1       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| IC2       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| IC3       | PPS                    | PPS             | I           | ST             | Capture Input 1-5                                                                                                                                                                      |

| IC4       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| IC5       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |

| OC1       | PPS                    | PPS             | 0           | ST             | Output Compare Output 1                                                                                                                                                                |

| OC2       | PPS                    | PPS             | 0           | ST             | Output Compare Output 2                                                                                                                                                                |

| OC3       | PPS                    | PPS             | 0           | ST             | Output Compare Output 3                                                                                                                                                                |

| OC4       | PPS                    | PPS             | 0           | ST             | Output Compare Output 4                                                                                                                                                                |

| OC5       | PPS                    | PPS             | 0           | ST             | Output Compare Output 5                                                                                                                                                                |

| OCFA      | PPS                    | PPS             | Ι           | ST             | Output Compare Fault A Input                                                                                                                                                           |

| OCFB      | 30                     | 44              | I           | ST             | Output Compare Fault B Input                                                                                                                                                           |

|           |                        | IOS compati     |             |                | Analog = Analog input I = Input O = Output                                                                                                                                             |

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = P

P = Power

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 3 and MPLAB REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- *"Using MPLAB<sup>®</sup> ICD 3"* (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- *"MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide"* DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer or debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements

### 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

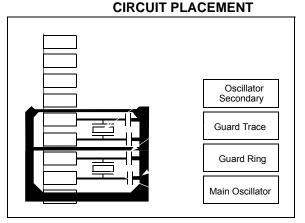

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

## FIGURE 2-3: SUGGESTED OSCILLATOR

<sup>© 2014-2016</sup> Microchip Technology Inc.

| Interment Course (1)                       | 100 # | Vector | ctor Interrupt Bit Location |              |              |              | Persistent |

|--------------------------------------------|-------|--------|-----------------------------|--------------|--------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>            | IRQ # | #      | Flag                        | Enable       | Priority     | Sub-priority | Interrupt  |

| CNA – PORTA Input Change Interrupt         | 44    | 33     | IFS1<12>                    | IEC1<12>     | IPC8<12:10>  | IPC8<9:8>    | Yes        |

| CNB – PORTB Input Change Interrupt         | 45    | 33     | IFS1<13>                    | IEC1<13>     | IPC8<12:10>  | IPC8<9:8>    | Yes        |

| CNC – PORTC Input Change Interrupt         | 46    | 33     | IFS1<14>                    | IEC1<14>     | IPC8<12:10>  | IPC8<9:8>    | Yes        |

| CND – PORTD Input Change Interrupt         | 47    | 33     | IFS1<15>                    | IEC1<15>     | IPC8<12:10>  | IPC8<9:8>    | Yes        |

| CNE – PORTE Input Change Interrupt         | 48    | 33     | IFS1<16>                    | IEC1<16>     | IPC8<12:10>  | IPC8<9:8>    | Yes        |

| CNF – PORTF Input Change Interrupt         | 49    | 33     | IFS1<17>                    | IEC1<17>     | IPC8<12:10>  | IPC8<9:8>    | Yes        |

| CNG – PORTG Input Change Interrupt         | 50    | 33     | IFS1<18>                    | IEC1<18>     | IPC8<12:10>  | IPC8<9:8>    | Yes        |

| PMP – Parallel Master Port                 | 51    | 34     | IFS1<19>                    | IEC1<19>     | IPC8<20:18>  | IPC8<17:16>  | Yes        |

| PMPE – Parallel Master Port Error          | 52    | 34     | IFS1<20>                    | IEC1<20>     | IPC8<20:18>  | IPC8<17:16>  | Yes        |

| SPI2E – SPI2 Fault                         | 53    | 35     | IFS1<21>                    | IEC1<21>     | IPC8<28:26>  | IPC8<25:24>  | Yes        |

| SPI2RX – SPI2 Receive Done                 | 54    | 35     | IFS1<22>                    | IEC1<22>     | IPC8<28:26>  | IPC8<25:24>  | Yes        |

| SPI2TX – SPI2 Transfer Done                | 55    | 35     | IFS1<23>                    | IEC1<23>     | IPC8<28:26>  | IPC8<25:24>  | Yes        |

| U2E – UART2 Error                          | 56    | 36     | IFS1<24>                    | IEC1<24>     | IPC9<4:2>    | IPC9<1:0>    | Yes        |

| U2RX – UART2 Receiver                      | 57    | 36     | IFS1<25>                    | IEC1<25>     | IPC9<4:2>    | IPC9<1:0>    | Yes        |

| U2TX – UART2 Transmitter                   | 58    | 36     | IFS1<26>                    | IEC1<26>     | IPC9<4:2>    | IPC9<1:0>    | Yes        |

| I2C2B – I2C2 Bus Collision Event           | 59    | 37     | IFS1<27>                    | IEC1<27>     | IPC9<12:10>  | IPC9<9:8>    | Yes        |

| I2C2S – I2C2 Slave Event                   | 60    | 37     | IFS1<28>                    | IEC1<28>     | IPC9<12:10>  | IPC9<9:8>    | Yes        |

| I2C2M – I2C2 Master Event                  | 61    | 37     | IFS1<29>                    | IEC1<29>     | IPC9<12:10>  | IPC9<9:8>    | Yes        |

| U3E – UART3 Error                          | 62    | 38     | IFS1<30>                    | IEC1<30>     | IPC9<20:18>  | IPC9<17:16>  | Yes        |

| U3RX – UART3 Receiver                      | 63    | 38     | IFS1<31>                    | IEC1<31>     | IPC9<20:18>  | IPC9<17:16>  | Yes        |

| U3TX – UART3 Transmitter                   | 64    | 38     | IFS2<0>                     | IEC2<0>      | IPC9<20:18>  | IPC9<17:16>  | Yes        |

| U4E – UART4 Error                          | 65    | 39     | IFS2<1>                     | IEC2<1>      | IPC9<28:26>  | IPC9<25:24>  | Yes        |

| U4RX – UART4 Receiver                      | 66    | 39     | IFS2<2>                     | IEC2<2>      | IPC9<28:26>  | IPC9<25:24>  | Yes        |

| U4TX – UART4 Transmitter                   | 67    | 39     | IFS2<3>                     | IEC2<3>      | IPC9<28:26>  | IPC9<25:24>  | Yes        |

| U5E – UART5 Error <sup>(2)</sup>           | 68    | 40     | IFS2<4>                     | IEC2<4>      | IPC10<4:2>   | IPC10<1:0>   | Yes        |

| U5RX – UART5 Receiver <sup>(2)</sup>       | 69    | 40     | IFS2<5>                     | IEC2<5>      | IPC10<4:2>   | IPC10<1:0>   | Yes        |

| U5TX – UART5 Transmitter <sup>(2)</sup>    | 70    | 40     | IFS2<6>                     | IEC2<6>      | IPC10<4:2>   | IPC10<1:0>   | Yes        |

| CTMU – CTMU Event <sup>(2)</sup>           | 71    | 41     | IFS2<7>                     | IEC2<7>      | IPC10<12:10> | IPC10<9:8>   | Yes        |

| DMA0 – DMA Channel 0                       | 72    | 42     | IFS2<8>                     | IEC2<8>      | IPC10<20:18> | IPC10<17:16> | No         |

| DMA1 – DMA Channel 1                       | 73    | 43     | IFS2<9>                     | IEC2<9>      | IPC10<28:26> | IPC10<25:24> | No         |

| DMA2 – DMA Channel 2                       | 74    | 44     | IFS2<10>                    | IEC2<10>     | IPC11<4:2>   | IPC11<1:0>   | No         |

| DMA3 – DMA Channel 3                       | 75    | 45     | IFS2<11>                    | IEC2<11>     | IPC11<12:10> | IPC11<9:8>   | No         |

| CMP3 – Comparator 3 Interrupt              | 76    | 46     | IFS2<12>                    | IEC2<12>     | IPC11<20:18> | IPC11<17:16> | No         |

| CAN1 – CAN1 Event                          | 77    | 47     | IFS2<13>                    | IEC2<13>     | IPC11<28:26> | IPC11<25:24> | Yes        |

| SPI3E – SPI3 Fault                         | 78    | 48     | IFS2<14>                    | IEC2<14>     | IPC12<4:2>   | IPC12<1:0>   | Yes        |

| SPI3RX – SPI3 Receive Done                 | 79    | 48     | IFS2<15>                    | IEC2<15>     | IPC12<4:2>   | IPC12<1:0>   | Yes        |

| SPI3TX – SPI3 Transfer Done                | 80    | 48     | IFS2<16>                    | IEC2<16>     | IPC12<4:2>   | IPC12<1:0>   | Yes        |

| SPI4E – SPI4 Fault <sup>(2)</sup>          | 81    | 49     | IFS2<17>                    | IEC2<17>     | IPC12<12:10> | IPC12<9:8>   | Yes        |

| SPI4RX – SPI4 Receive Done <sup>(2)</sup>  | 82    | 49     | IFS2<18>                    | IEC2<18>     | IPC12<12:10> | IPC12<9:8>   | Yes        |

| SPI4TX – SPI4 Transfer Done <sup>(2)</sup> | 83    | 49     | IFS2<19>                    | IEC2<19>     | IPC12<12:10> | IPC12<9:8>   | Yes        |

|                                            | •     | Lowe   | st Natural Or               | der Priority |              |              |            |

#### TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | _                 | _                 | -                 | _                | —                    |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | —                 | _                 | _                 | —                 | _                 |                   |                  | _                    |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 10.0         | —                 | _                 |                   | —                 | _                 |                   | —                | _                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | SWRST <sup>(1)</sup> |

### REGISTER 7-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | HC = Cleared by har | dware                |                    |

|-------------------|---------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared | x = Bit is unknown |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup>

- 1 = Enable software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section

6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

### 8.1 Control Registers

| TAB                         | LE 8-1:                         | 08        | SCILL | ATOR  | CONFI   | GURATI     | ON RE                            | GISTE       | R MAP    |      |         |         |          |            |      |                       |        |       |                     |

|-----------------------------|---------------------------------|-----------|-------|-------|---------|------------|----------------------------------|-------------|----------|------|---------|---------|----------|------------|------|-----------------------|--------|-------|---------------------|

| ess                         |                                 | 0         |       |       |         |            |                                  |             |          |      | Bits    |         |          |            |      |                       |        |       | s                   |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13   | 28/12      | 27/11                            | 26/10       | 25/9     | 24/8 | 23/7    | 22/6    | 21/5     | 20/4       | 19/3 | 18/2                  | 17/1   | 16/0  | All Resets          |

| F000                        | OSCCON                          | 31:16     | _     | —     | PI      | LLODIV<2:0 | >                                | FRCDIV<2:0> |          |      | —       | SOSCRDY | PBDIVRDY | PBDIV<1:0> |      | PLLMULT<2:0>          |        |       | x1xx <sup>(2)</sup> |

| F000                        | USCCON .                        | 15:0      | —     |       | COSC<2: | 0>         | —                                |             | NOSC<2:0 | >    | CLKLOCK | ULOCK   | SLOCK    | SLPEN      | CF   | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN | xxxx(2)             |

| F010                        | OSCTUN                          | 31:16     | _     | _     | _       | —          | _                                | _           | —        | _    | —       | —       | _        | _          |      | —                     | _      | —     | 0000                |

| 1010                        | 030101                          | 15:0      | —     |       |         | _          | —                                | _           | —        | —    | _       | _       |          |            | TUT  | N<5:0>                |        |       | 0000                |

| 5000                        | REFOCON                         | 31:16     | —     |       |         |            |                                  |             |          |      | RODIV<  | 14:0>   |          |            |      |                       |        |       | 0000                |

| F020                        | REFUCUN                         | 15:0      | ON    | —     | SIDL    | OE         | RSLP - DIVSWEN ACTIVE ROSEL<3:0> |             |          |      |         |         |          | 0000       |      |                       |        |       |                     |

| 5000                        | REFOTRIM                        | 31:16     |       |       |         |            | ROTRIM<                          | 8:0>        |          |      |         | -       | _        | _          | —    | —                     | —      | —     | 0000                |

| F030                        |                                 | 15:0      | _     | _     | -       | _          | —                                | _           | _        | _    | —       | _       | _        | _          | _    | —                     | _      | —     | 0000                |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on devices with a USB module.

.....

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 6         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |         |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|---------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3    | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | _     | —        | _     | —        | _       | —      | —         |          | 0000       |

| 5260                        |                                 | 15:0      |       |       | _     |       | —     | —     | —    | —    |       |          |       | FRML<    | 7:0>    |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | -     | _     | -     | _     | _     | _     | _    | _    | _     | —        | —     | —        | _       | -      | —         |          | 0000       |

| 5290                        | OT RMIR /                       | 15:0      | _     | —     | _     | —     | —     | —     | _    | —    | —     | —        | —     | —        | —       |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     |          | —       |        | -         | —        | 0000       |

| 5270                        | UTION                           | 15:0      | _     | —     |       | —     | —     | —     | —    | —    |       | PID      | <3:0> |          |         | EP     | ><3:0>    |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _     | —        | _     | —        | _       | _      | _         |          | 0000       |

| 52BU                        | 0130F                           | 15:0      |       | _     |       | _     | _     | _     | _    | _    |       |          |       | CNT<7    | /:0>    | -      | •         |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —       | _      | —         |          | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     |       | _     |       | —     | —     | _    |      |       |          |       | BDTPTRH  | <23:16> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —       | _      | —         |          | 0000       |

| 5200                        | OIBDIF5                         | 15:0      | _     |       | _     |       | —     | —     | _    |      |       |          |       | BDTPTRU  | <31:24> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —       | _      | —         |          | 0000       |

| 52L0                        | UICNIGI                         | 15:0      | _     |       | _     |       | —     | —     | _    |      | UTEYE | —        | _     | USBSIDL  | LSDEV   | _      | —         | UASUSPND | 0000       |

| 5300                        | U1EP0                           | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —       | _      | —         |          | 0000       |

| 5500                        | UILFU                           | 15:0      | _     |       | _     |       | —     | —     | _    |      | LSPD  | RETRYDIS | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | —        | —       | _      | —         |          | 0000       |

| 5510                        | UILFI                           | 15:0      | _     |       | _     |       | —     | —     | _    |      | _     | —        | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | _     |       | _     |       | —     | —     | —    |      | _     | —        | —     | —        | —       | _      | —         |          | 0000       |

| 5520                        | UILFZ                           | 15:0      |       |       |       |       | _     | _     | _    | _    | _     | _        | —     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —     | _     | —     | —     | —     | _    | —    | —     | —        | —     | —        | —       | —      | —         | _        | 0000       |

| 0000                        | 01EI 3                          | 15:0      |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | _     | _     | —     | —     | —    | —    | —     | —        | —     | _        | —       | —      | —         | _        | 0000       |

| 0040                        | 01214                           | 15:0      |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | _     | _     | —     | —     | —    | —    | —     | —        | —     | _        | —       | —      | —         | _        | 0000       |

| 5550                        | 01EI 5                          | 15:0      |       | —     | _     | —     | —     | —     | —    | —    | _     | _        | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | _     | —     |       | —     | —     | —     | —    | —    | —     | —        | _     | _        | —       | —      | —         | —        | 0000       |

| 5500                        | 01L10                           | 15:0      | -     | _     | -     | —     | _     | —     | —    |      | _     | —        | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | _     | —     | _     | —     | —     | —     | —    | —    | —     | -        | _     | —        | —       | —      | -         | —        | 0000       |

| 5570                        |                                 | 15:0      | -     | —     | -     | —     | _     | _     | —    | —    | —     | —        | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —     | _     | —     | —     | —     | —    | —    | —     | —        | _     | —        | —       | —      | -         | —        | 0000       |

| 5500                        |                                 | 15:0      | -     | _     | -     | _     | —     | —     | _    | —    | _     | —        | —     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

DS60001290D-page 108

#### TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                          |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |      |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

|                             |                  | 31:16     | _     | _     | _     | -     | _     | _     | _    | -    | -    | _    | -    | _    | _    | _    | -      | _    | 00         |

| FB88                        | RPC2R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC2 | 2<3:0> |      | 00         |

|                             |                  | 31:16     | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | —    | _    | —    | —    | _      | _    | 00         |

| FB8C                        | RPC3R            | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPC  | 3<3:0> |      | 00         |

| 5000                        | 00040            | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FB90                        | RPC4R            | 15:0      | _     | _     | _     | _     | —     | _     | _    | _    | _    | _    | —    | _    |      | RPC4 | <3:0>  |      | 00         |

| 5004                        | 000400           | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBB4                        | RPC13R           | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC1 | 3<3:0> |      | 00         |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    |      | —    | _    | _      |      | 00         |

| FBB8                        | RPC14R           | 15:0      | _     | _     | _     | _     | —     | —     | _    | —    | —    | _    | —    | _    |      | RPC1 | 4<3:0> |      | 00         |

| 50.00                       | 00000            | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBC0                        | RPD0R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    |      |      | RPD  | )<3:0> |      | 00         |

|                             |                  | 31:16     | _     | _     | _     | _     | —     | —     | _    | —    | —    | _    | —    | _    | —    | —    | _      | _    | 00         |

| FBC4                        | RPD1R            | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD' | <3:0>  |      | 00         |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    |      | —    | _    | _      |      | 00         |

| FBC8                        | RPD2R            | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD2 | 2<3:0> |      | 00         |

| 5000                        | 00000            | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBCC                        | RPD3R            | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD  | 3<3:0> |      | 00         |

| 5000                        | 00040            | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBD0                        | RPD4R            | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD4 | <3:0>  |      | 00         |

|                             | 00050            | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBD4                        | RPD5R            | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD  | 5<3:0> |      | 00         |

|                             |                  | 31:16     | —     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | _    | —    | —      |      | 00         |

| FBE0                        | RPD8R            | 15:0      | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD8 | 3<3:0> |      | 00         |

| 5054                        | 00000            | 31:16     | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBE4                        | RPD9R            | 15:0      | _     | —     | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD9 | 9<3:0> |      | 00         |

|                             | 000400           | 31:16     | _     | —     | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBE8                        | RPD10R           | 15:0      | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD1 | 0<3:0> |      | 00         |

|                             | 000440           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | —    | _    | _      | —    | 00         |

| FBEC                        | RPD11R           | 15:0      | —     | _     | —     | _     | —     | —     | _    | —    | _    | _    | _    | _    |      | RPD1 | 1<3:0> |      | 00         |

| FDFC                        |                  | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | —    | —    | —      | —    | 00         |

| FBF0                        | RPD12R           | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD1 | 2<3:0> |      | 00         |

| EDEC                        |                  | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | —    | —    | —      | —    | 00         |

| FBF8                        | RPD14R           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _    |      | RPD1 | 4<3:0> |      | 00         |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

#### **REGISTER 13-1: TxCON: TYPE B TIMER 'x' CONTROL REGISTER ('x' = 2 THROUGH 5)**

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        | —                    |                   | -                   | —                 | —                  | —                 | —                  | —                |

| 22:16        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23:16        | —                    | -                 | -                   | —                 | —                  | _                 | -                  | —                |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | —                 | —                  | _                 | _                  | —                |

| 7.0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(          | 3)                | T32 <sup>(2)</sup> |                   | TCS <sup>(3)</sup> | —                |

| Legend: |  |

|---------|--|

|---------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation even in Idle mode

- bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

When TCS = 1:

This bit is ignored and is read as '0'.

#### When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

- bit 6-4 **TCKPS<2:0>:** Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                   | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 |                   | WDTWINEN          | WDTCLR            |                  |                  |

#### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                    |                    |  |  |

|-------------------|-----------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 **WDTCLR:** Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC sample and hold amplifier is sampling

- 0 = The ADC sample/hold amplifier is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

Clearing this bit will not affect any operation in progress.

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

U-0

U-0

\_\_\_\_

R/W-0

SMPI<3:0>

U-0

R/W-0

CSCNA

R/W-0

Bit

25/17/9/1

U-0

U-0

U-0

\_\_\_\_

R/W-0

BUFM

Bit

24/16/8/0

U-0

U-0

U-0

R/W-0

ALTS

| REGISTE      | ER 22-2. A        | DICONZ. AI        |                   |                   |                   |                   |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               |  |

| 31.24        |                   |                   |                   |                   |                   |                   |  |

U-0

R/W-0

R/W-0

#### DECISTED 22 2. AD1CON2: ADC CONTROL REGISTER 2

U-0

R/W-0

U-0

\_

VCFG<2:0>

## Legend:

23:16

15:8

7:0

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

U-0

R/W-0

OFFCAL

R/W-0

#### bit 31-16 Unimplemented: Read as '0'

U-0

R/W-0

R-0

BUFS

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |  |  |

|-----|--------------------|--------------------|--|--|

| 000 | AVDD               | AVss               |  |  |

| 001 | External VREF+ pin | AVss               |  |  |

| 010 | AVDD               | External VREF- pin |  |  |

| 011 | External VREF+ pin | External VREF- pin |  |  |

| 1xx | AVDD               | AVss               |  |  |

#### bit 12 OFFCAL: Input Offset Calibration Mode Select bit

- 1 = Enable Offset Calibration mode

- Positive and negative inputs of the sample and hold amplifier are connected to VREFL

- 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 CSCNA: Input Scan Select bit

- 1 = Scan inputs

- 0 = Do not scan inputs

#### bit 9-8 Unimplemented: Read as '0'

- bit 7 BUFS: Buffer Fill Status bit

- Only valid when BUFM = 1.

- 1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

- 0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each  $16^{th}$  sample/convert sequence 1110 = Interrupts at the completion of conversion for each  $15^{th}$  sample/convert sequence

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | CH0NB             | _                 |                   | CH0SB<5:0>        |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CH0NA             | -                 |                   | CH0SA<5:0>        |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         |                   | _                 | _                 | _                 | _                 | —                 | _                | —                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

#### REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER

#### Legend:

bit 23

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 CHONB: Negative Input Select bit for Sample B 1 = Channel 0 negative input is AN1 0 = Channel 0 negative input is VREFL bit 30 Unimplemented: Read as '0'

bit 29-24 CH0SB<5:0>: Positive Input Select bits for Sample B

For 64-pin devices:

011110 = Channel 0 positive input is Open<sup>(1)</sup> 011101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup> 011100 = Channel 0 positive input is IVREF<sup>(3)</sup> 011011 = Channel 0 positive input is AN27 000001 = Channel 0 positive input is AN1 000000 = Channel 0 positive input is AN0

For 100-pin devices:

| 110010 = Channel 0 positive input is Open <sup>(1)</sup>                            |

|-------------------------------------------------------------------------------------|

| 110001 = Channel 0 positive input is CTMU temperature sensor (CTMUT) <sup>(2)</sup> |

| 110000 = Channel 0 positive input is IVREF <sup>(3)</sup>                           |

| 101111 = Channel 0 positive input is AN47                                           |

| •                                                                                   |

| •                                                                                   |

| •                                                                                   |

| 0000001 = Channel 0 positive input is AN1                                           |

| 0000000 = Channel 0 positive input is AN0                                           |

| CH0NA: Negative Input Select bit for Sample A Multiplexer Setting <sup>(3)</sup>    |

| 1 = Channel 0 negative input is AN1                                                 |

| $\perp$ – Channel U negative input is An i                                          |

- 0 = Channel 0 negative input is VREFL

- bit 22 Unimplemented: Read as '0'

Note 1: This selection is only used with CTMU capacitive and time measurement.

- 2: See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: Internal precision 1.2V reference. See Section 24.0 "Comparator" for more information.

| REGISTE  | R 23-3:        | C1INT: CAN INTERRUPT REGISTER (CONTINUED)                                                                                                 |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | 1 = A bus      | CAN Bus Activity Wake-up Interrupt Flag bit<br>s wake-up activity interrupt has occurred<br>s wake-up activity interrupt has not occurred |

| bit 13   | 1 = A CAI      | CAN Bus Error Interrupt Flag bit<br>N bus error has occurred<br>N bus error has not occurred                                              |

| bit 12   | SERRIF:        | System Error Interrupt Flag bit <sup>(1)</sup>                                                                                            |

|          |                | tem error occurred (typically an illegal address was presented to the system bus) tem error has not occurred                              |

| bit 11   | <b>RBOVIF:</b> | Receive Buffer Overflow Interrupt Flag bit                                                                                                |

|          |                | eive buffer overflow has occurred<br>eive buffer overflow has not occurred                                                                |

| bit 10-4 | Unimpler       | mented: Read as '0'                                                                                                                       |

| bit 3    | MODIF: 0       | CAN Mode Change Interrupt Flag bit                                                                                                        |

|          |                | N module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP)<br>N module mode change has not occurred                      |

| bit 2    | CTMRIF:        | CAN Timer Overflow Interrupt Flag bit                                                                                                     |

|          |                | N timer (CANTMR) overflow has occurred<br>N timer (CANTMR) overflow has not occurred                                                      |

| bit 1    | RBIF: Re       | ceive Buffer Interrupt Flag bit                                                                                                           |

|          |                | eive buffer interrupt is pending<br>eive buffer interrupt is not pending                                                                  |

| bit 0    | TBIF: Tra      | nsmit Buffer Interrupt Flag bit                                                                                                           |

|          | 1 = A tran     | nsmit buffer interrupt is pending                                                                                                         |

- 0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (C1CON<15>).

#### REGISTER 23-16: C1FIFOCONn: CAN FIFO CONTROL REGISTER 'n' ('n' = 0 THROUGH 15)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-----------------------|---------------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0                   | U-0                   | U-0                       | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                     | _                     | _                         | _                 | _                 | _                | —                |

| 02:16        | U-0               | U-0                   | U-0                   | R/W-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | —                     | _                     | FSIZE<4:0> <sup>(1)</sup> |                   |                   |                  |                  |

| 45.0         | U-0               | S/HC-0                | S/HC-0                | R/W-0                     | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | FRESET                | UINC                  | DONLY <sup>(1)</sup>      | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R-0                   | R-0                   | R-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | TXEN              | TXABAT <sup>(2)</sup> | TXLARB <sup>(3)</sup> | TXERR <sup>(3)</sup>      | TXREQ             | RTREN             | TXPR             | <1:0>            |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-21 Unimplemented: Read as '0'

| 511 01 21 |                                                                                                                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 20-16 | FSIZE<4:0>: FIFO Size bits <sup>(1)</sup>                                                                                                                                                                          |

|           | 11111 = Reserved                                                                                                                                                                                                   |

|           | •                                                                                                                                                                                                                  |

|           |                                                                                                                                                                                                                    |

|           | 10000 = Reserved                                                                                                                                                                                                   |

|           | 01111 = FIFO is 16 messages deep                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                    |

|           | •                                                                                                                                                                                                                  |

|           | 00000 = FIFO is 1 message deep                                                                                                                                                                                     |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                         |

| bit 14    | FRESET: FIFO Reset bits                                                                                                                                                                                            |

|           | <ul> <li>1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset. After setting, the user should poll whether this bit is clear before taking any action.</li> <li>0 = No effect</li> </ul> |

| 1.11.40   |                                                                                                                                                                                                                    |

| bit 13    | UINC: Increment Head/Tail bit                                                                                                                                                                                      |

|           | $\frac{\text{TXEN} = 1}{1} \text{ (FIFO configured as a Transmit FIFO)}$                                                                                                                                           |

|           | When this bit is set the FIFO head will increment by a single message                                                                                                                                              |

|           | $\frac{\text{TXEN} = 0}{1000}$ (FIFO configured as a Receive FIFO)                                                                                                                                                 |

|           | When this bit is set the FIFO tail will increment by a single message                                                                                                                                              |

| bit 12    | DONLY: Store Message Data Only bit <sup>(1)</sup>                                                                                                                                                                  |

|           | <u>TXEN = 1:</u> (FIFO configured as a Transmit FIFO)                                                                                                                                                              |

|           | This bit is not used and has no effect.                                                                                                                                                                            |

|           | <u>TXEN = 0:</u> (FIFO configured as a Receive FIFO)                                                                                                                                                               |

|           | 1 = Only data bytes will be stored in the FIFO                                                                                                                                                                     |

|           | 0 = Full message is stored, including identifier                                                                                                                                                                   |

| bit 11-8  | Unimplemented: Read as '0'                                                                                                                                                                                         |

|           |                                                                                                                                                                                                                    |

| Note 1:   | These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (C1CON<23:21>) = 100).                                                                                               |

|           |                                                                                                                                                                                                                    |

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

| DC CHARACTERISTICS                   |       |                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |            |                                               |

|--------------------------------------|-------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------|-----------------------------------------------|