Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx530f128h-v-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4: PIN NAMES FOR 100-PIN GENERAL PURPOSE DEVICES (CONTINUED)

| 10                                                    | 100-PIN TQFP (TOP VIEW) |       |                           |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------|-------------------------|-------|---------------------------|--|--|--|--|--|--|--|--|--|--|

| PIC32MX130F128L<br>PIC32MX150F256L<br>PIC32MX170F512L |                         |       |                           |  |  |  |  |  |  |  |  |  |  |

|                                                       |                         |       | 100 1                     |  |  |  |  |  |  |  |  |  |  |

| Pin #                                                 | Full Pin Name           | Pin # | Full Pin Name             |  |  |  |  |  |  |  |  |  |  |

| 71                                                    | RPD11/PMA14/RD11        | 86    | Vdd                       |  |  |  |  |  |  |  |  |  |  |

| 72                                                    | RPD0/RD0                | 87    | AN44/C3INA/RPF0/PMD11/RF0 |  |  |  |  |  |  |  |  |  |  |

| 73                                                    | SOSCI/RPC13/RC13        | 88    | AN45/RPF1/PMD10/RF1       |  |  |  |  |  |  |  |  |  |  |

| 74                                                    | SOSCO/RPC14/T1CK/RC14   | 89    | RPG1/PMD9/RG1             |  |  |  |  |  |  |  |  |  |  |

| 75                                                    | Vss                     | 90    | RPG0/PMD8/RG0             |  |  |  |  |  |  |  |  |  |  |

| 76                                                    | AN24/RPD1/RD1           | 91    | RA6                       |  |  |  |  |  |  |  |  |  |  |

| 77                                                    | AN25/RPD2/RD2           | 92    | CTED8/RA7                 |  |  |  |  |  |  |  |  |  |  |

|                                                       | AN26/C3IND/RPD3/RD3     | 93    | AN46/PMD0/RE0             |  |  |  |  |  |  |  |  |  |  |

|                                                       | AN40/RPD12/PMD12/RD12   | 94    | AN47/PMD1/RE1             |  |  |  |  |  |  |  |  |  |  |

|                                                       | AN41/PMD13/RD13         | 95    | RG14                      |  |  |  |  |  |  |  |  |  |  |

| -                                                     | RPD4/PMWR/RD4           | 96    | RG12                      |  |  |  |  |  |  |  |  |  |  |

| 02                                                    | RPD5/PMRD/RD5           | 97    | RG13                      |  |  |  |  |  |  |  |  |  |  |

|                                                       | AN42/C3INC/PMD14/RD6    | 98    | AN20/PMD2/RE2             |  |  |  |  |  |  |  |  |  |  |

|                                                       | AN43/C3INB/PMD15/RD7    | 99    | RPE3/CTPLS/PMD3/RE3       |  |  |  |  |  |  |  |  |  |  |

| 85                                                    | VCAP                    | 100   | AN21/PMD4/RE4             |  |  |  |  |  |  |  |  |  |  |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

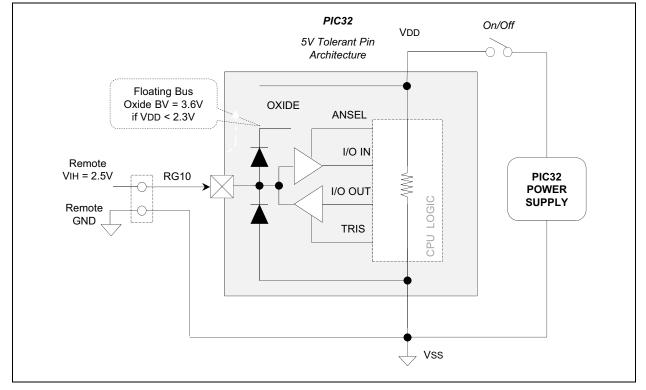

### 2.9.2 5V TOLERANT INPUT PINS

The internal high side diode on 5V tolerant pins are bussed to an internal floating node, rather than being connected to VDD, as shown in Figure 2-7. Voltages on these pins, if VDD < 2.3V, should not exceed roughly 3.2V relative to Vss of the PIC32 device. Voltage of 3.6V or higher will violate the absolute maximum specification, and will stress the oxide layer separating the high side floating node, which impacts device reliability. If a remotely powered "digital-only" signal can be guaranteed to always be  $\leq$  3.2V relative to Vss on the PIC32 device side, a 5V tolerant pin could be used without the need for a digital isolator. This is assuming there is not a ground loop issue, logic ground of the two circuits not at the same absolute level, and a remote logic low input is not less than Vss - 0.3V.

## TABLE 5-2: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |                        |       |                           |                  | Bits |      |      |             |            |             |             |         |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|------------------------|-------|---------------------------|------------------|------|------|------|-------------|------------|-------------|-------------|---------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(3)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                  | 26/10 | 25/9                      | 24/8             | 23/7 | 22/6 | 21/5 | 20/4        | 19/3       | 18/2        | 17/1        | 16/0    | All<br>Resets |

| 1050                        | IPC5                            | 31:16     | _     |       | _     | A     | AD1IP<2:0>             |       | AD1IS                     | i<1:0>           |      |      | -    |             | OC5IP<2:02 | >           | OC5IS       | S<1:0>  | 0000          |

| 10E0                        | IPC5                            | 15:0      | —     |       | —     | IC    | IC5IP<2:0>             |       | IC5IS                     | <1:0>            |      |      | —    |             | T5IP<2:0>  |             | T5IS        | <1:0>   | 0000          |

| 1050                        | IPC6                            | 31:16     | _     |       | _     | CM    | IP1IP<2:0>             | •     | CMP1                      | S<1:0>           |      | -    | _    |             | FCEIP<2:0  | >           | FCEIS       | S<1:0>  | 0000          |

| 10F0                        | IPC0                            | 15:0      | —     |       | —     | RT    | CCIP<2:0>              | •     | RTCCI                     | S<1:0>           |      |      | —    |             | FSCMIP<2:0 | >           | FSCM        | IS<1:0> | 0000          |

| 1100                        | IPC7                            | 31:16     | —     |       | —     | U     | U1IP<2:0>              |       | U1IS-                     | <1:0>            |      |      | —    | SPI1IP<2:0> |            | SPI1IS<1:0> |             | 0000    |               |

| 1100                        | IPC/                            | 15:0      | _     |       | —     | USI   | BIP<2:0> <sup>(2</sup> | )     | USBIS<1:0> <sup>(2)</sup> |                  | _    | _    | _    | CMP2IP<2:0> |            | CMP2IS<1:0> |             | 0000    |               |

| 1110                        | IPC8                            | 31:16     | —     |       | —     | SF    | PI2IP<2:0>             |       | SPI2IS<1:0>               |                  |      |      | —    |             | PMPIP<2:0  | >           | PMPIS<1:0>  |         | 0000          |

| 1110                        | IPCo                            | 15:0      | —     |       | —     | С     | NIP<2:0>               |       | CNIS<1:0>                 |                  | —    | —    | —    |             | I2C1IP<2:0 | >           | I2C1IS<1:0> |         | 0000          |

| 1120                        | IPC9                            | 31:16     | _     | _     | —     | U     | 4IP<2:0>               |       | U4IS<1:0>                 |                  | _    | —    | _    | U3IP<2:0>   |            |             | U3IS<1:0>   |         | 0000          |

| 1120                        | IF C9                           | 15:0      | _     | _     | —     | 120   | C2IP<2:0>              |       | 12C215                    | S<1:0>           | _    | —    | _    |             | U2IP<2:0>  |             | U2IS        | <1:0>   | 0000          |

| 1130                        | IPC10                           | 31:16     | _     | _     | _     | DM    | IA1IP<2:0>             | •     | DMA1                      | S<1:0>           | -    | -    | _    |             | DMA0IP<2:0 | >           | DMA0I       | S<1:0>  | 0000          |

| 1130                        | IFCIU                           | 15:0      | _     | _     | _     | CT    | MUIP<2:0>              | •     | CTMUI                     | S<1:0>           | _    | _    | _    |             | U5IP<2:0>  |             | U5IS        | <1:0>   | 0000          |

| 1140                        | IPC11                           | 31:16     | —     |       | —     | CA    | NIP<2:0>(5             | )     | CANIS                     | <1:0> <b>(5)</b> | —    | —    | —    |             | CMP3IP<2:0 | >           | CMP3I       | S<1:0>  | 0000          |

| 1140                        | IFCII                           | 15:0      | _     | _     | —     | DM    | IA3IP<2:0>             | •     | DMA3                      | S<1:0>           | _    | —    | _    |             | DMA2IP<2:0 | >           | DMA2I       | S<1:0>  | 0000          |

| 1150                        | IPC12                           | 31:16     | —     | —     | —     | —     | —                      | _     | —                         | —                | _    | _    | —    | —           |            | _           | —           |         | 0000          |

| 1150                        | IFC12                           | 15:0      | —     |       | —     | SP    | 4P<2:0>(1)             | )     | SPI4S<                    | :1:0> <b>(1)</b> | —    | —    | —    |             | SPI3P<2:0> | •           | SPI35       | S<1:0>  | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

3: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

4: This register does not have associated CLR, SET, and INV registers.

5: This bit is only implemented on devices with a CAN module.

NOTES:

| REGIOI       | LIX 10-J.         |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | -                 | —                 | —                 | -                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | —                 | —                 | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 |                   | _                 |                   |                   | —                | —                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | —                 | _                 | USLPGRD           | USBBUSY           | _                 | USUSPEND         | USBPWR           |

## REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| Logonal           |                  |                            |                    |  |

|-------------------|------------------|----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

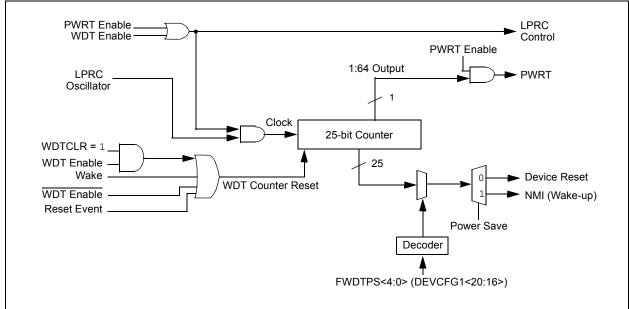

# 14.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin Family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Watchdog Timer (WDT), when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

### FIGURE 14-1: WATCHDOG AND POWER-UP TIMER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                   | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          | _                   |                   | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

### REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                          |                    |  |  |  |  |  |  |

|-------------------|-----------------------------------------------|--------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, I | read as '0'        |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 **WDTCLR:** Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

## **19.1 Control Registers**

## TABLE 19-1: UART1 THROUGH UART5 REGISTER MAP

| 'ess<br>)                   |                       | e             |        |                  |        |       |        |       |       | Bi          | ts          |         |       |           |               |       |        |       | s          |

|-----------------------------|-----------------------|---------------|--------|------------------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|-----------|---------------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15  | 30/14            | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4      | 19/3          | 18/2  | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16         | _      |                  | _      | _     | —      |       |       | —           | _           | —       | _     | _         |               | —     |        | _     | 0000       |

| 0000                        | OTWODE                | 15:0          | ON     | -                | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV     | BRGH          | PDSEI | _<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16         | —      | ADM_EN ADDR<7:0> |        |       |        |       |       |             |             | 0000    |       |           |               |       |        |       |            |

| 0010                        | 0101/1                | 15:0          | UTXISE | L<1:0>           | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE     | PERR          | FERR  | OERR   | URXDA | FFFF       |

| 6020                        | U1TXREG               | 31:16         | —      | —                | —      | —     | —      | —     | —     | —           | —           | —       | —     | —         | —             | —     | —      | —     | 0000       |

| 0020                        | 011XIII20             | 15:0          | —      | —                | —      | —     | —      | —     | —     | TX8         |             |         |       | Transmit  | Register      |       |        |       | 0000       |

| 6030                        | U1RXREG               | 31:16         | —      | _                | —      | _     | —      | _     | _     | —           | _           | —       | —     | —         | —             | —     | —      | —     | 0000       |

|                             | 01101120              | 15:0          | —      | —                | —      | _     | —      | —     | —     | RX8         |             |         |       | Receive   | Register      |       |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16         | —      | —                | —      | _     |        | —     | —     |             | _           |         | —     | —         |               |       | —      | —     | 0000       |

|                             |                       | 15:0          |        |                  |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |           |               |       |        |       | 0000       |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16         | _      | _                |        |       |        | _     | _     | —           | _           |         | _     |           | _             |       | —      |       | 0000       |

|                             |                       | 15:0          | ON     | —                | SIDL   | IREN  | RTSMD  | —     | UEN   | -           | WAKE        | LPBACK  | ABAUD | RXINV     | BRGH          | PDSEI | _<1:0> | STSEL | 0000       |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16         | —      | —                | —      | —     | —      | —     | —     | ADM_EN      |             |         |       | ADDR      | -             |       |        | -     | 0000       |

|                             |                       | 15:0          | UTXISE | L<1:0>           | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE     | PERR          | FERR  | OERR   | URXDA | FFFF       |

| 6220                        | U2TXREG               | 31:16         | _      | _                |        | _     | —      | _     | —     | _           | _           | _       | _     |           |               |       | _      | —     | 0000       |

|                             |                       | 15:0          | _      | _                |        |       | —      | _     | _     | TX8         |             |         |       | Transmit  | Register      |       |        |       | 0000       |

| 6230                        | U2RXREG               | 31:16         | _      | _                | —      | _     | —      | _     | _     | _           | _           | _       | _     |           | _             | —     | —      | —     | 0000       |

|                             |                       | 15:0          | _      | _                | —      | _     | _      | —     |       | RX8         |             |         |       | Receive   | Register      |       |        |       | 0000       |

| 6240                        | U2BRG <sup>(1)</sup>  | 31:16         | _      | _                |        |       | —      |       |       |             |             |         | _     |           | _             | —     | _      | —     | 0000       |

|                             |                       | 15:0          |        |                  |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |           |               |       |        |       | 0000       |

| 6400                        | U3MODE <sup>(1)</sup> | 31:16<br>15:0 | -      | _                | -      | -     | -      | —     | —     | —           |             | —       |       | —         | —             |       | _      | -     | 0000       |

| -                           |                       |               | ON     | _                | SIDL   | IREN  | RTSMD  |       | UEN   | -           | WAKE        | LPBACK  | ABAUD | RXINV     | BRGH          | PDSEI | _<1:0> | STSEL | 0000       |

| 6410                        | U3STA <sup>(1)</sup>  | 31:16         | —      | —                | -      | -     | -      | -     | —     | ADM_EN      |             | -1 -1 0 |       | ADDR      | -             | 5500  | 0500   |       | 0000       |

|                             |                       | 15:0          | UTXISE | -                | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | =L<1:0> | ADDEN | RIDLE     | PERR          | FERR  | OERR   | URXDA | FFFF       |

| 6420                        | <b>U3TXREG</b>        | 31:16         | _      |                  |        |       |        | _     | _     | —<br>       | _           | —       | _     |           | —             | _     | _      | —     | 0000       |

|                             |                       | 15:0          |        |                  |        |       |        |       |       | 0000        |             |         |       |           |               |       |        |       |            |

| 6430                        | U3RXREG               | 31:16         | _      |                  |        |       | _      | _     |       |             | _           | _       |       | - Boogive | —<br>Bogistor | _     | _      | —     | 0000       |

|                             |                       | 15:0          | —      | —                | —      |       |        | —     | —     | RX8         |             |         |       | Receive   | Register      |       |        |       | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register is only available on 100-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | —                 | —                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | —                 | -                 | —                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

### REGISTER 19-1: UxMODE: UARTx MODE REGISTER

### Legend:

| Legend.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

#### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| REGIST  | ER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)                                               |

|---------|--------------------------------------------------------------------------------------------------------|

| bit 7-0 | ARPT<7:0>: Alarm Repeat Counter Value bits <sup>(3)</sup>                                              |

|         | 11111111 =Alarm will trigger 256 times                                                                 |

|         | •                                                                                                      |

|         | •                                                                                                      |

|         | •<br>00000000 =Alarm will trigger one time                                                             |

|         | The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1. |

| Note 1: | Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = $00$ and CHIME = $0$ . |

| 2:      | This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.             |

| 3:      | This assumes a CPU read will execute in less than 32 PBCLKs.                                           |

| Note:   | This register is reset only on a Power-on Reset (POR).                                                 |

|         |                                                                                                        |

NOTES:

| [            |                   |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   |                   |                   | SID<1             | 0:3>              |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 23.10        |                   | SID<2:0>          |                   | —                 | MIDE              | _                 | EID<'            | 17:16>           |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         |                   |                   |                   | EID<1             | 5:8>              |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | EID<7             | 7:0>              |                   |                  |                  |

#### REGISTER 23-9: C1RXMn: CAN ACCEPTANCE FILTER MASK 'n' REGISTER (n = 0, 1, 2 OR 3)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Include the SIDx bit in filter comparison

- 0 = The SIDx bit is a 'don't care' in filter operation

- bit 20 Unimplemented: Read as '0'

- bit 19 MIDE: Identifier Receive Mode bit

- 1 = Match only message types (standard/extended address) that correspond to the EXID bit in filter

- Match either standard or extended address message if filters match (that is, if (Filter SID) = (Message SID) or if (FILTER SID/EID) = (Message SID/EID))

#### bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Include the EIDx bit in filter comparison

- 0 = The EIDx bit is a 'don't care' in filter operation

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|

| 31:24        | R/W-0              | R/W-0              |  |

| 31.24        | C1FIFOBA<31:24>   |                   |                   |                   |                   |                   |                    |                    |  |

| 00.40        | R/W-0              | R/W-0              |  |

| 23:16        | C1FIFOBA<23:16>   |                   |                   |                   |                   |                   |                    |                    |  |

| 15:8         | R/W-0              | R/W-0              |  |

|              | C1FIFOBA<15:8>    |                   |                   |                   |                   |                   |                    |                    |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |

|              | C1FIFOBA<7:0>     |                   |                   |                   |                   |                   |                    |                    |  |

#### REGISTER 23-15: C1FIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

#### Legend:

| Logonan           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-0 C1FIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Bits <1:0> are read-only and read as '0', forcing the messages to be 32-bit word-aligned in device RAM.

**Note 1:** This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

| REGIST  | ER 26-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)                                          |

|---------|----------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                           |

|         | 1 = Edge 1 must occur before Edge 2 can occur                                                |

|         | 0 = No edge sequence is needed                                                               |

| bit 9   | <b>IDISSEN:</b> Analog Current Source Control bit <sup>(2)</sup>                             |

|         | 1 = Analog current source output is grounded                                                 |

|         | 0 = Analog current source output is not grounded                                             |

| bit 8   | CTTRIG: Trigger Control bit                                                                  |

|         | 1 = Trigger output is enabled                                                                |

|         | 0 = Trigger output is disabled                                                               |

| bit 7-2 | ITRIM<5:0>: Current Source Trim bits                                                         |

|         | 011111 = Maximum positive change from nominal current                                        |

|         | 011110                                                                                       |

|         |                                                                                              |

|         |                                                                                              |

|         | 000001 = Minimum positive change from nominal current                                        |

|         | 000000 = Nominal current output specified by IRNG<1:0>                                       |

|         | 111111 = Minimum negative change from nominal current                                        |

|         |                                                                                              |

|         | •                                                                                            |

|         | 100010                                                                                       |

|         | 100001 = Maximum negative change from nominal current                                        |

| bit 1-0 | IRNG<1:0>: Current Range Select bits <sup>(3)</sup>                                          |

|         | 11 = 100 times base current                                                                  |

|         | 10 = 10 times base current                                                                   |

|         | 01 = Base current level                                                                      |

|         | 00 = 1000 times base current <sup>(4)</sup>                                                  |

| Nets 4  | When this bit is set for Dules Delay Operation, the EDOOOEL (0.0), bits must be act to (1.1) |

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-41) in Section 31.0 "40 MHz Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

# 27.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

#### 27.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

#### 27.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PMDL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4                | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-0               | r-1               | r-1               | R/P                              | r-1               | r-1               | r-1              | R/P              |

| 31:24        | —                 | —                 | _                 | СР                               | —                 | —                 | _                | BWP              |

| 00.40        | r-1               | r-1               | r-1               | r-1                              | R/P               | R/P               | R/P              | R/P              |

| 23:16        | —                 | _                 | _                 | _                                | PWP<9:6>          |                   |                  |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P                              | R/P               | R/P               | r-1              | r-1              |

| 15:8         |                   |                   | PWP<5:0>          |                                  |                   |                   | _                | —                |

| 7:0          | r-1               | r-1               | r-1               | R/P                              | R/P               | R/P               | R/P              | R/P              |

|              | _                 | _                 | _                 | ICESEL<1:0> JTAGEN <sup>(1</sup> |                   |                   | DEBU             | G<1:0>           |

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit P = Programmable bit |                          |                    |

|-------------------|---------------------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31 Reserved: Write '0'

- bit 30-29 Reserved: Write '1'

- bit 28 **CP:** Code-Protect bit

- Prevents boot and program Flash memory from being read or modified by an external programming device.

- 1 = Protection is disabled

- 0 = Protection is enabled

- bit 27-25 Reserved: Write '1'

- bit 24 **BWP:** Boot Flash Write-Protect bit

- Prevents boot Flash memory from being modified during code execution.

- 1 = Boot Flash is writable

- 0 = Boot Flash is not writable

- bit 23-20 Reserved: Write '1'

- Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

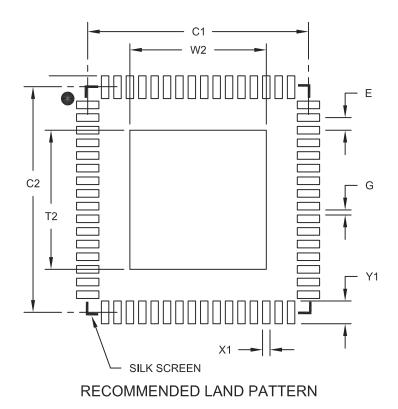

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 5.40x5.40mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimension Limits           |             | MIN      | NOM  | MAX  |  |

| Contact Pitch E            |             | 0.50 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 5.50 |  |

| Optional Center Pad Length | T2          |          |      | 5.50 |  |

| Contact Pad Spacing        | C1          |          | 8.90 |      |  |

| Contact Pad Spacing        | C2          |          | 8.90 |      |  |

| Contact Pad Width (X64)    | X1          |          |      | 0.30 |  |

| Contact Pad Length (X64)   | Y1          |          |      | 0.85 |  |

| Distance Between Pads      | G           | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2154A