Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 81                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 48x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx530f128l-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | Pin N                  | umber           |             |                |                        |

|----------|------------------------|-----------------|-------------|----------------|------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description            |

| AN0      | 16                     | 25              | Ι           | Analog         |                        |

| AN1      | 15                     | 24              | Ι           | Analog         |                        |

| AN2      | 14                     | 23              | Ι           | Analog         |                        |

| AN3      | 13                     | 22              | Ι           | Analog         |                        |

| AN4      | 12                     | 21              | Ι           | Analog         |                        |

| AN5      | 11                     | 20              | I           | Analog         |                        |

| AN6      | 17                     | 26              | Ι           | Analog         |                        |

| AN7      | 18                     | 27              | I           | Analog         |                        |

| AN8      | 21                     | 32              | I           | Analog         |                        |

| AN9      | 22                     | 33              | Ι           | Analog         |                        |

| AN10     | 23                     | 34              | Ι           | Analog         |                        |

| AN11     | 24                     | 35              | I           | Analog         |                        |

| AN12     | 27                     | 41              | Ι           | Analog         |                        |

| AN13     | 28                     | 42              | Ι           | Analog         |                        |

| AN14     | 29                     | 43              | I           | Analog         |                        |

| AN15     | 30                     | 44              | Ι           | Analog         |                        |

| AN16     | 4                      | 10              | I           | Analog         |                        |

| AN17     | 5                      | 11              | I           | Analog         |                        |

| AN18     | 6                      | 12              | Ι           | Analog         | Analog input channels. |

| AN19     | 8                      | 14              | Ι           | Analog         |                        |

| AN20     | 62                     | 98              | I           | Analog         |                        |

| AN21     | 64                     | 100             | Ι           | Analog         |                        |

| AN22     | 1                      | 3               | I           | Analog         |                        |

| AN23     | 2                      | 4               | Ι           | Analog         |                        |

| AN24     | 49                     | 76              | Ι           | Analog         |                        |

| AN25     | 50                     | 77              | Ι           | Analog         |                        |

| AN26     | 51                     | 78              | I           | Analog         |                        |

| AN27     | 3                      | 5               | I           | Analog         |                        |

| AN28     |                        | 1               | I           | Analog         |                        |

| AN29     | —                      | 6               | Ι           | Analog         |                        |

| AN30     | _                      | 7               | I           | Analog         |                        |

| AN31     |                        | 8               | Ι           | Analog         |                        |

| AN32     | _                      | 18              | I           | Analog         |                        |

| AN33     | _                      | 19              | Ι           | Analog         |                        |

| AN34     |                        | 39              | Ι           | Analog         |                        |

| AN35     |                        | 40              |             | Analog         | 1                      |

# TABLE 1-1:PINOUT I/O DESCRIPTIONS

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                     | Pin N                    | umber           |             |                |                                                          |

|---------------------|--------------------------|-----------------|-------------|----------------|----------------------------------------------------------|

| Pin Name            | 64-pin<br>QFN/<br>TQFP   | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                              |

| PMA2                | 8                        | 14              | 0           | TTL/ST         |                                                          |

| PMA3                | 6                        | 12              | 0           | TTL/ST         |                                                          |

| PMA4                | 5                        | 11              | 0           | TTL/ST         |                                                          |

| PMA5                | 4                        | 10              | 0           | TTL/ST         |                                                          |

| PMA6                | 16                       | 29              | 0           | TTL/ST         |                                                          |

| PMA7                | 22                       | 28              | 0           | TTL/ST         |                                                          |

| PMA8                | 32                       | 50              | 0           | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) or |

| PMA9                | 31                       | 49              | 0           | TTL/ST         | Address/Data (Multiplexed Master modes)                  |

| PMA10               | 28                       | 42              | 0           | TTL/ST         |                                                          |

| PMA11               | 27                       | 41              | 0           | TTL/ST         |                                                          |

| PMA12               | 24                       | 35              | 0           | TTL/ST         |                                                          |

| PMA13               | 23                       | 34              | 0           | TTL/ST         |                                                          |

| PMA14               | 45                       | 71              | 0           | TTL/ST         |                                                          |

| PMA15               | 44                       | 70              | 0           | TTL/ST         |                                                          |

| PMCS1               | 45                       | 71              | 0           | TTL/ST         |                                                          |

| PMCS2               | 44                       | 70              | 0           | TTL/ST         |                                                          |

| PMD0                | 60                       | 93              | I/O         | TTL/ST         |                                                          |

| PMD1                | 61                       | 94              | I/O         | TTL/ST         |                                                          |

| PMD2                | 62                       | 98              | I/O         | TTL/ST         |                                                          |

| PMD3                | 63                       | 99              | I/O         | TTL/ST         |                                                          |

| PMD4                | 64                       | 100             | I/O         | TTL/ST         |                                                          |

| PMD5                | 1                        | 3               | I/O         | TTL/ST         |                                                          |

| PMD6                | 2                        | 4               | I/O         | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) o  |

| PMD7                | 3                        | 5               | I/O         | TTL/ST         | Address/Data (Multiplexed Master modes)                  |

| PMD8                | —                        | 90              | I/O         | TTL/ST         |                                                          |

| PMD9                |                          | 89              | I/O         | TTL/ST         |                                                          |

| PMD10               | —                        | 88              | I/O         | TTL/ST         |                                                          |

| PMD11               | —                        | 87              | I/O         | TTL/ST         |                                                          |

| PMD12               | —                        | 79              | I/O         | TTL/ST         | 1                                                        |

| PMD13               | —                        | 80              | I/O         | TTL/ST         | 1                                                        |

| PMD14               | —                        | 83              | I/O         | TTL/ST         | 1                                                        |

| PMD15               | —                        | 84              | I/O         | TTL/ST         | 1                                                        |

| PMRD                | 53                       | 82              | 0           | —              | Parallel Master Port Read Strobe                         |

| PMWR                | 52                       | 81              | 0           | —              | Parallel Master Port Write Strobe                        |

| VBUS <sup>(2)</sup> | 34                       | 54              | Ι           | Analog         | USB Bus Power Monitor                                    |

| •                   | CMOS = CM<br>ST = Schmit | t Trigger inp   | ut with (   | CMOS level     | ls TTL = TTL input buffer P = Power                      |

|                     | -                        | -               |             |                | t a USB module.<br>USB module.                           |

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Name        | Function                                                                                                                                                              |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| HWREna                  | Enables access via the RDHWR instruction to selected hardware registers.                                                                                              |

| BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.                                                                                                    |

| Count <sup>(1)</sup>    | Processor cycle count.                                                                                                                                                |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| Compare <sup>(1)</sup>  | Timer interrupt control.                                                                                                                                              |

| Status <sup>(1)</sup>   | Processor status and control.                                                                                                                                         |

| IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                                                                                                                  |

| Cause <sup>(1)</sup>    | Cause of last general exception.                                                                                                                                      |

| EPC <sup>(1)</sup>      | Program counter at last exception.                                                                                                                                    |

| PRId                    | Processor identification and revision.                                                                                                                                |

| EBASE                   | Exception vector base register.                                                                                                                                       |

| Config                  | Configuration register.                                                                                                                                               |

| Config1                 | Configuration register 1.                                                                                                                                             |

| Config2                 | Configuration register 2.                                                                                                                                             |

| Config3                 | Configuration register 3.                                                                                                                                             |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| Debug <sup>(2)</sup>    | Debug control and exception status.                                                                                                                                   |

| DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                                                                                                              |

| Reserved                | Reserved in the PIC32MX1XX/2XX/5XX 64/100-pin family core.                                                                                                            |

| ErrorEPC <sup>(1)</sup> | Program counter at last error.                                                                                                                                        |

| DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                                                                                                                    |

|                         | NameReservedHWREnaBadVAddr(1)Count(1)ReservedCompare(1)Status(1)IntCtl(1)Cause(1)EPC(1)PRIdEBASEConfigConfig1Config2Config3ReservedDebug(2)DEPC(2)ReservedErrorEPC(1) |

| TABLE 3-2. COPROCESSOR UREGISTERS | <b>TABLE 3-2:</b> | <b>COPROCESSOR 0 REGISTERS</b> |

|-----------------------------------|-------------------|--------------------------------|

|-----------------------------------|-------------------|--------------------------------|

Note 1: Registers used in exception processing.

**2:** Registers used during debug.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

# 3.3 **Power Management**

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

## 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 27.0 "Power-Saving Features".

## 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX-1XX/2XX/5XX 64/100-pin family core is in the clock tree and clocking registers. The PIC32MX family uses extensive use of local gated-clocks to reduce this dynamic power consumption.

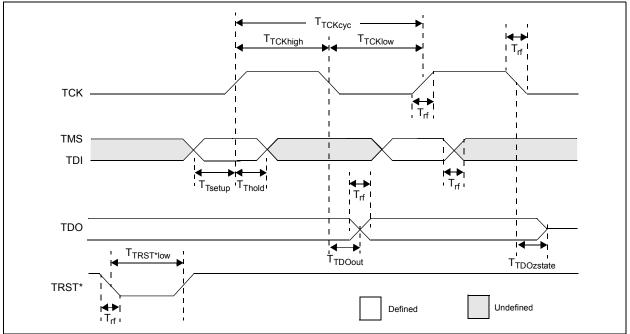

# 3.4 EJTAG Debug Support

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K<sup>®</sup> core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

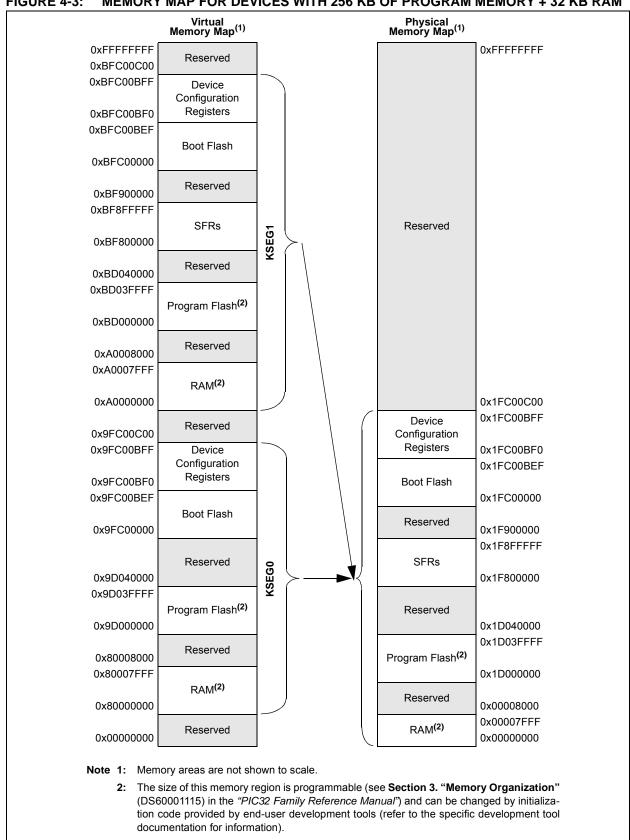

## FIGURE 4-3: MEMORY MAP FOR DEVICES WITH 256 KB OF PROGRAM MEMORY + 32 KB RAM

# 4.3 Control Registers

Register 4-1 through Register 4-8 are used for setting the RAM and Flash memory partitions for data and code.

|                                   | ER 4-1: I                                                       |                                                                             | •••                             |                   | RATION RE                          |                                       |                  |                  |  |  |

|-----------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------|-------------------|------------------------------------|---------------------------------------|------------------|------------------|--|--|

| Bit<br>Range                      | Bit<br>31/23/15/7                                               | Bit<br>30/22/14/6                                                           | Bit<br>29/21/13/5               | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2                     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 31:24                             | U-0                                                             | U-0                                                                         | U-0                             | U-0               | U-0                                | U-0                                   | U-0              | U-0              |  |  |

| 31:24                             | —                                                               | -                                                                           | —                               | —                 | —                                  | _                                     | —                | _                |  |  |

|                                   | U-0                                                             | U-0                                                                         | U-0                             | R/W-1             | R/W-1                              | R/W-1                                 | R/W-1            | R/W-1            |  |  |

| 23:16                             | BMX<br>ERRIXIBMX<br>ERRICDBMX<br>ERRDMABMX<br>ERRDSBMX<br>ERRIS |                                                                             |                                 |                   |                                    |                                       |                  |                  |  |  |

| 15:8                              | U-0  U-0  U-0  U-0  U-0  U-0  U-0                               |                                                                             |                                 |                   |                                    |                                       |                  |                  |  |  |

|                                   | U-0                                                             | R/W-1                                                                       | U-0                             | U-0               | U-0                                | R/W-0                                 | R/W-0            | R/W-1            |  |  |

| 7:0                               | _                                                               | BMX<br>WSDRM                                                                | _                               | _                 | _                                  | · · · · · · · · · · · · · · · · · · · | 3MXARB<2:0       |                  |  |  |

| Legend:<br>R = Reac<br>-n = Value |                                                                 |                                                                             | W = Writable<br>'1' = Bit is se |                   | U = Unimplei<br>'0' = Bit is cle   | mented bit, re<br>eared               | ad as '0'        |                  |  |  |

| bit 31-21                         | Unimpleme                                                       | nted: Read a                                                                | <b>s</b> '0'                    |                   |                                    |                                       |                  |                  |  |  |

| bit 20                            | BMXERRIX                                                        | I: Enable Bus                                                               | Error from IX                   | l bit             |                                    |                                       |                  |                  |  |  |

|                                   | 1 = Enable I                                                    | ous error exce                                                              | ptions for unr                  | mapped addre      | ess accesses i                     | nitiated from I                       | XI shared bu     | s                |  |  |

|                                   | 0 = Disable                                                     | bus error exce                                                              | eptions for un                  | mapped addro      | ess accesses                       | initiated from                        | IXI shared bu    | IS               |  |  |

| bit 19                            | BMXERRIC                                                        | D: Enable Bu                                                                | s Error from I                  | CD Debug Un       | it bit                             |                                       |                  |                  |  |  |

|                                   | 1 = Enable I                                                    | ous error exce                                                              | ptions for unr                  | mapped addre      | ess accesses i                     | nitiated from I                       | CD               |                  |  |  |

|                                   | 0 = Disable                                                     | bus error exce                                                              | eptions for un                  | mapped addro      | ess accesses                       | initiated from                        | ICD              |                  |  |  |

| bit 18                            | BMXERRD                                                         | MA: Bus Error                                                               | from DMA bi                     | t                 |                                    |                                       |                  |                  |  |  |

|                                   | 1 = Enable I                                                    | ous error exce                                                              | ptions for unr                  | mapped addre      | ess accesses i                     | nitiated from I                       | DMA              |                  |  |  |

|                                   | 0 = Disable                                                     | bus error exce                                                              | eptions for un                  | mapped addr       | ess accesses                       | initiated from                        | DMA              |                  |  |  |

| bit 17                            |                                                                 |                                                                             |                                 |                   | disabled in De                     |                                       |                  |                  |  |  |

|                                   |                                                                 |                                                                             |                                 |                   | ess accesses i                     |                                       | CPU data acc     | ess              |  |  |

|                                   |                                                                 |                                                                             |                                 |                   | ess accesses                       |                                       |                  |                  |  |  |

| bit 16                            |                                                                 |                                                                             |                                 |                   | bit (disabled i                    |                                       |                  |                  |  |  |

|                                   |                                                                 |                                                                             |                                 |                   | ess accesses i                     |                                       |                  | on access        |  |  |

|                                   |                                                                 |                                                                             |                                 |                   | ess accesses                       |                                       |                  |                  |  |  |

| bit 15-7                          |                                                                 | nted: Read a                                                                |                                 |                   |                                    |                                       |                  |                  |  |  |

| bit 6                             | -                                                               |                                                                             |                                 | Access from       | Data RAM Wa                        | ait State bit                         |                  |                  |  |  |

|                                   | -                                                               |                                                                             |                                 |                   | ate for address                    |                                       |                  |                  |  |  |

|                                   |                                                                 |                                                                             |                                 |                   | ates for addre                     |                                       |                  |                  |  |  |

|                                   |                                                                 |                                                                             |                                 |                   |                                    |                                       |                  |                  |  |  |

| DIT 5-3                           | -                                                               | Unimplemented: Read as '0'<br>BMXARB<2:0>: Bus Matrix Arbitration Mode bits |                                 |                   |                                    |                                       |                  |                  |  |  |

|                                   |                                                                 | Dins Mat                                                                    | iv Arbitration                  | Modo hite         |                                    |                                       |                  |                  |  |  |

|                                   |                                                                 |                                                                             |                                 |                   | ill produce un                     | defined behav                         | vior)            |                  |  |  |

|                                   |                                                                 |                                                                             |                                 |                   | ill produce und                    | defined behav                         | ior)             |                  |  |  |

| bit 2-0                           |                                                                 |                                                                             |                                 |                   | ill produce und                    | defined behav                         | ior)             |                  |  |  |

| bit 5-3<br>bit 2-0                | 111 = Rese                                                      | rved (using th                                                              | ese configura                   | tion modes w      |                                    |                                       |                  |                  |  |  |

|                                   | 111 = Rese<br>011 = Rese                                        | rved (using th<br>rved (using th                                            | ese configura                   | tion modes w      | ill produce und<br>ill produce und |                                       |                  |                  |  |  |

|                                   | 111 = Rese                                                      | rved (using th<br>rved (using th<br>ation Mode 2                            | ese configura<br>ese configura  | tion modes w      |                                    |                                       |                  |                  |  |  |

|                                   | 111 = Rese<br><br>011 = Rese<br>010 = Arbitr<br>001 = Arbitr    | rved (using th<br>rved (using th                                            | ese configura<br>ese configura  | tion modes w      |                                    |                                       |                  |                  |  |  |

# REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 | _                | _                |  |  |  |

| 00.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |  |

# **REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER**

# Legend:

| Legena.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

# 5.1 Interrupts Control Registers

## TABLE 5-2: INTERRUPT REGISTER MAP

| sse                         |                                 |               |                 | Bits           |                   |                  |                  |                 |                |                 |                   |                       |                       |                      |                         |                         |                |                 |               |

|-----------------------------|---------------------------------|---------------|-----------------|----------------|-------------------|------------------|------------------|-----------------|----------------|-----------------|-------------------|-----------------------|-----------------------|----------------------|-------------------------|-------------------------|----------------|-----------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(3)</sup> | Bit Range     | 31/15           | 30/14          | 29/13             | 28/12            | 27/11            | 26/10           | 25/9           | 24/8            | 23/7              | 22/6                  | 21/5                  | 20/4                 | 19/3                    | 18/2                    | 17/1           | 16/0            | All<br>Resets |

| 1000                        | INTCON                          | 31:16         | _               |                | _                 | —                | _                |                 | —              | _               | —                 | —                     | —                     | -                    | -                       | -                       | -              | -               | 0000          |

|                             |                                 | 15:0          |                 |                | _                 | MVEC             | —                |                 | TPC<2:0>       |                 | _                 | _                     | _                     | INT4EP               | INT3EP                  | INT2EP                  | INT1EP         | INT0EP          | 0000          |

| 1010                        | INTSTAT <sup>(4)</sup>          | 31:16<br>15:0 |                 |                |                   |                  | _                |                 |                |                 |                   |                       |                       | _                    | <br>VEC<                | 5:0>                    | _              |                 | 0000          |

|                             |                                 | 31:16         |                 |                |                   |                  |                  |                 |                |                 |                   |                       |                       |                      | VLOV                    | 0.0-                    |                |                 | 0000          |

| 1020                        | IPTMR                           | 15:0          |                 |                |                   | IPTMR<31:0>      |                  |                 |                |                 |                   | 0000                  |                       |                      |                         |                         |                |                 |               |

| 1030                        | IFS0                            | 31:16         | FCEIF           | RTCCIF         | FSCMIF            | AD1IF            | OC5IF            | IC5IF           | IC5EIF         | T5IF            | INT4IF            | OC4IF                 | IC4IF                 | IC4EIF               | T4IF                    | INT3IF                  | OC3IF          | IC3IF           | 0000          |

| 1030                        | 150                             | 15:0          | IC3EIF          | T3IF           | INT2IF            | OC2IF            | IC2IF            | IC2EIF          | T2IF           | INT1IF          | OC1IF             | IC1IF                 | IC1EIF                | T1IF                 | INT0IF                  | CS1IF                   | CS0IF          | CTIF            | 0000          |

| 1040                        | IFS1                            | 31:16         | <b>U3RXIF</b>   | U3EIF          | I2C2MIF           | I2C2SIF          | I2C2BIF          | U2TXIF          | U2RXIF         | U2EIF           | SPI2TXIF          | SPI2RXIF              | SPI2EIF               | PMPEIF               | PMPIF                   | CNGIF                   | CNFIF          | CNEIF           | 0000          |

| 1010                        |                                 | 15:0          | CNDIF           | CNCIF          | CNBIF             | CNAIF            | I2C1MIF          | I2C1SIF         | I2C1BIF        | U1TXIF          | U1RXIF            | U1EIF                 | SPI1TXIF              | SPI1RXIF             | SPI1EIF                 | USBIF <sup>(2)</sup>    | CMP2IF         | CMP1IF          | 0000          |

| 1050                        | IFS2                            | 31:16         | —               | —              | —                 |                  | —                | —               | —              | —               | _                 | (1)                   | (1)                   | —                    | SPI4TXIF <sup>(1)</sup> | SPI4RXIF <sup>(1)</sup> | -              | <b>SPI3TXIF</b> |               |

|                             |                                 | 15:0          | SPI3RXIF        | SPI3EIF        | CANIF             | CMP3IF           | DMA3IF           | DMA2IF          | DMA1IF         | DMA0IF          | CTMUIF            | U5TXIF <sup>(1)</sup> | U5RXIF <sup>(1)</sup> | U5EIF <sup>(1)</sup> | U4TXIF                  | U4RXIF                  | U4EIF          | U3TXIF          | 0000          |

| 1060                        | IEC0                            | 31:16         | FCEIE<br>IC3EIE | RTCCIE<br>T3IE | FSCMIE<br>INT2IE  | AD1IE            | OC5IE            | IC5IE<br>IC2EIE | IC5EIE<br>T2IE | T5IE            | INT4IE            | OC4IE                 | IC4IE                 | IC4EIE<br>T1IE       | T4IE<br>INT0IE          | INT3IE                  | OC3IE          | IC3IE<br>CTIE   | 0000          |

|                             |                                 | 15:0<br>31:16 | U3RXIE          | U3EIE          | INTZIE<br>I2C2MIE | OC2IE<br>I2C2SIE | IC2IE<br>I2C2BIE | U2TXIE          | U2RXIE         | INT1IE<br>U2EIE | OC1IE<br>SPI2TXIE | IC1IE<br>SPI2RXIE     | SPI2EIE               | PMPEIE               | PMPIE                   | CS1IE<br>CNGIE          | CS0IE<br>CNFIE | CITE            | 0000          |

| 1070                        | IEC1                            | 15:0          | CNDIE           | CNCIE          | CNBIE             | CNAIE            | I2C2BIE          | I2C1SIE         | I2C1BIE        | U1TXIE          | U1RXIE            | U1EIE                 | SPIZEIE               | SPI1RXIE             | SPI1EIE                 | USBIE <sup>(2)</sup>    | CMP2IE         | CMP1IE          | 0000          |

|                             |                                 | 31:16         | _               |                |                   | _                |                  | -               |                | _               |                   | _                     |                       |                      |                         |                         | _              |                 | 0000          |

| 1080                        | IEC2                            | 15:0          | _               | _              | _                 | _                | DMA3IE           | DMA2IE          | DMA1IE         | DMA0IE          | CTMUIE            | U5TXIE <sup>(1)</sup> | U5RXIE <sup>(1)</sup> | U5EIE <sup>(1)</sup> | U4TXIE                  | U4RXIE                  | U4EIE          | U3TXIE          | 0000          |

|                             |                                 | 31:16         | _               | _              | _                 | IN               | T0IP<2:0>        |                 | INTOIS         |                 | _                 | _                     | _                     |                      | CS1IP<2:0>              | ,                       | CS1IS          | 6<1:0>          | 0000          |

| 1090                        | IPC0                            | 15:0          | _               | _              | _                 | CS               | S0IP<2:0>        |                 | CSOIS          | <1:0>           |                   | _                     | _                     |                      | CTIP<2:0>               |                         | CTIS           | <1:0>           | 0000          |

| 10A0                        | IPC1                            | 31:16         | _               | —              | —                 | IN               | T1IP<2:0>        |                 | INT1IS         | 6<1:0>          | _                 | _                     | _                     |                      | OC1IP<2:0>              | >                       | OC1IS          | 6<1:0>          | 0000          |

| IUAU                        | IPCT                            | 15:0          | _               | _              | —                 | IC               | 1IP<2:0>         |                 | IC1IS<1:0>     |                 | _                 | _                     | _                     |                      | T1IP<2:0>               |                         | T1IS           | <1:0>           | 0000          |

| 10B0                        | IPC2                            | 31:16         |                 |                | —                 | IN               | T2IP<2:0>        |                 | INT2IS<1:0>    |                 |                   | -                     | —                     |                      | OC2IP<2:0>              | >                       | OC2IS          | 6<1:0>          | 0000          |

| IUBU                        | 1602                            | 15:0          | _               | _              | —                 | IC               | 2IP<2:0>         |                 | IC2IS<1:0>     |                 | _                 | —                     | —                     |                      | T2IP<2:0>               |                         | T2IS           | <1:0>           | 0000          |

| 10C0                        | IPC3                            | 31:16         | _               | —              | —                 |                  | T3IP<2:0>        |                 | INT3IS         |                 | _                 | —                     | _                     |                      | OC3IP<2:0>              | >                       |                | 6<1:0>          | 0000          |

| 1000                        | " 00                            | 15:0          | _               |                | —                 |                  | 3IP<2:0>         |                 | IC3IS          | -               | _                 | —                     | —                     |                      | T3IP<2:0>               |                         | T3IS           | -               | 0000          |

| 10D0                        | IPC4                            | 31:16         | —               | —              | —                 |                  | T4IP<2:0>        |                 | INT4IS         | -               | _                 | —                     | _                     |                      | OC4IP<2:0>              | >                       | OC4IS          |                 | 0000          |

| Longer                      |                                 | 15:0          | -               | —              | —                 |                  | 4IP<2:0>         |                 | IC4IS          |                 |                   | —                     | _                     |                      | T4IP<2:0>               |                         | T4IS           | <1:0>           | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

3: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

4: This register does not have associated CLR, SET, and INV registers.

5: This bit is only implemented on devices with a CAN module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS9             | IFS8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1             | IFS0             |

## REGISTER 5-4: IFSx: INTERRUPT FLAG STATUS REGISTER

# Legend:

| 5                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 5-1 for the exact bit definitions.

## REGISTER 5-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IEC31-IEC0: Interrupt Enable bits

- 1 = Interrupt is enabled

- 0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 5-1 for the exact bit definitions.

# 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX1XX/2XX/5XX 64/100-pin devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX1XX/2XX/5XX 64/100-pin devices, the Flash page size is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

## REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        | —                 | —                 | —                 |                   | R                 | KBUFELM<4:(       | )>               |                  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        | —                 | —                 | —                 | TXBUFELM<4:0>     |                   |                   |                  |                  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |

| 15:8         |                   | —                 | —                 | FRMERR            | SPIBUSY           |                   | _                | SPITUR           |

| 7:0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |

|              | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            | _                 | SPITBF           | SPIRBF           |

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 **SPITUR:** Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

- This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

- This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 SPIRBE: RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR ≠ SWPTR)

- bit 4 Unimplemented: Read as '0'

U-0

U-0

\_\_\_\_

R/W-0

SMPI<3:0>

U-0

R/W-0

CSCNA

R/W-0

Bit

25/17/9/1

U-0

U-0

U-0

\_\_\_\_

R/W-0

BUFM

Bit

24/16/8/0

U-0

U-0

U-0

R/W-0

ALTS

| REGISTE      | ER 22-2. A        | DICONZ. AI        |                   |                   |                   |                   |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               |  |

| 31.24        |                   |                   |                   |                   |                   |                   |  |

U-0

R/W-0

R/W-0

#### DECISTED 22 2. AD1CON2: ADC CONTROL REGISTER 2

U-0

R/W-0

U-0

\_

VCFG<2:0>

# Legend:

23:16

15:8

7:0

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

U-0

R/W-0

OFFCAL

R/W-0

## bit 31-16 Unimplemented: Read as '0'

U-0

R/W-0

R-0

BUFS

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVDD               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

#### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

- 1 = Enable Offset Calibration mode

- Positive and negative inputs of the sample and hold amplifier are connected to VREFL

- 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 CSCNA: Input Scan Select bit

- 1 = Scan inputs

- 0 = Do not scan inputs

#### bit 9-8 Unimplemented: Read as '0'

- bit 7 BUFS: Buffer Fill Status bit

- Only valid when BUFM = 1.

- 1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

- 0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

- 1111 = Interrupts at the completion of conversion for each  $16^{th}$  sample/convert sequence 1110 = Interrupts at the completion of conversion for each  $15^{th}$  sample/convert sequence

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

- bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | —                 | —                 | ABAT              | F                 | REQOP<2:0>       | •                |

| 00.40        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23:16        | OPMOD<2:0>        |                   |                   | CANCAP            | —                 | —                 | —                | -                |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDLE             | —                 | CANBUSY           | —                 | —                | _                |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | _                 | _                 |                   | I                 | DNCNT<4:0>        |                  |                  |

## **REGISTER 23-1: C1CON: CAN MODULE CONTROL REGISTER**

| Legend:           | HC = Hardware Clear | S = Settable bit          |                    |

|-------------------|---------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-28 Unimplemented: Read as '0'

- bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

## bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

## bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

## bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 ON: CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | FLTEN11           | MSEL1             | 1<1:0>            | FSEL11<4:0>       |                   |                   |                  |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN10           | MSEL10<1:0>       |                   | FSEL10<4:0>       |                   |                   |                  |                  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FLTEN9            | MSEL9<1:0>        |                   |                   | F                 | SEL9<4:0>         |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN8            | MSEL              | 8<1:0>            | FSEL8<4:0>        |                   |                   |                  |                  |

## REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |