Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 81                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx530f128lt-50i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

#### TABLE 4: PIN NAMES FOR 100-PIN GENERAL PURPOSE DEVICES (CONTINUED)

| 10    | 0-PIN TQFP (TOP VIEW)                                 |       |                           |

|-------|-------------------------------------------------------|-------|---------------------------|

|       | PIC32MX130F128L<br>PIC32MX150F256L<br>PIC32MX170F512L |       |                           |

|       |                                                       |       | 100 1                     |

| Pin # | Full Pin Name                                         | Pin # | Full Pin Name             |

| 71    | RPD11/PMA14/RD11                                      | 86    | Vdd                       |

| 72    | RPD0/RD0                                              | 87    | AN44/C3INA/RPF0/PMD11/RF0 |

| 73    | SOSCI/RPC13/RC13                                      | 88    | AN45/RPF1/PMD10/RF1       |

| 74    | SOSCO/RPC14/T1CK/RC14                                 | 89    | RPG1/PMD9/RG1             |

| 75    | Vss                                                   | 90    | RPG0/PMD8/RG0             |

| 76    | AN24/RPD1/RD1                                         | 91    | RA6                       |

| 77    | AN25/RPD2/RD2                                         | 92    | CTED8/RA7                 |

|       | AN26/C3IND/RPD3/RD3                                   | 93    | AN46/PMD0/RE0             |

|       | AN40/RPD12/PMD12/RD12                                 | 94    | AN47/PMD1/RE1             |

|       | AN41/PMD13/RD13                                       | 95    | RG14                      |

| -     | RPD4/PMWR/RD4                                         | 96    | RG12                      |

| 02    | RPD5/PMRD/RD5                                         | 97    | RG13                      |

|       | AN42/C3INC/PMD14/RD6                                  | 98    | AN20/PMD2/RE2             |

|       | AN43/C3INB/PMD15/RD7                                  | 99    | RPE3/CTPLS/PMD3/RE3       |

| 85    | VCAP                                                  | 100   | AN21/PMD4/RE4             |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

## **Table of Contents**

| 1.0   | Device Overview                                    | 13  |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs    |     |

| 3.0   | CPU                                                |     |

| 4.0   | Memory Organization                                |     |

| 5.0   | Interrupt Controller                               |     |

| 6.0   | Flash Program Memory                               |     |

| 7.0   | Resets                                             |     |

| 8.0   | Oscillator Configuration                           |     |

| 9.0   | Direct Memory Access (DMA) Controller              |     |

| 10.0  | USB On-The-Go (OTG)                                |     |

| 11.0  | I/O Ports                                          | 129 |

|       | Timer1                                             |     |

| 13.0  | Timer2/3, Timer4/5                                 | 163 |

| 14.0  | Watchdog Timer (WDT)                               | 169 |

| 15.0  | Input Capture                                      | 173 |

| 16.0  | Output Compare                                     | 177 |

| 17.0  | Serial Peripheral Interface (SPI)                  |     |

| 18.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        |     |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART) | 199 |

| 20.0  | Parallel Master Port (PMP)                         | 207 |

|       | Real-Time Clock and Calendar (RTCC)                |     |

| 22.0  | 10-bit Analog-to-Digital Converter (ADC)           | 231 |

| 23.0  | Controller Area Network (CAN)                      | 243 |

| 24.0  | Comparator                                         |     |

| 25.0  | Comparator Voltage Reference (CVREF)               |     |

| 26.0  | Charge Time Measurement Unit (CTMU)                | 279 |

| 27.0  | Power-Saving Features                              | 285 |

| 28.0  | Special Features                                   | 291 |

| 29.0  | Instruction Set                                    | 303 |

| 30.0  | Development Support                                | 305 |

| 31.0  | 40 MHz Electrical Characteristics                  | 309 |

|       | 50 MHz Electrical Characteristics                  |     |

| 33.0  | DC and AC Device Characteristics Graphs            | 359 |

|       | Packaging Information                              |     |

| The M | Vicrochip Web Site                                 | 377 |

|       | omer Change Notification Service                   |     |

|       | omer Support                                       |     |

| Produ | uct Identification System                          | 378 |

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

RECOMMENDED

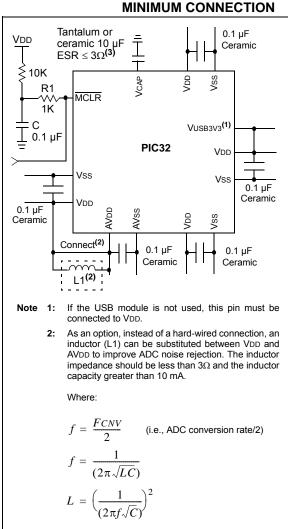

FIGURE 2-1:

2: Aluminum or electrolytic capacitors should not be used. ESR  $\leq$  3 $\Omega$  from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

#### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

### 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0 "40 MHz Electrical Characteristics"** for additional information on CEFC specifications.

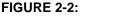

## 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- Device Reset

- Device programming and debugging

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

# EXAMPLE OF MCLR PIN CONNECTIONS

Resets from brief glitches or to extend the device Reset period during POR. 3: No pull-ups or bypass capacitors are allowed on

No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

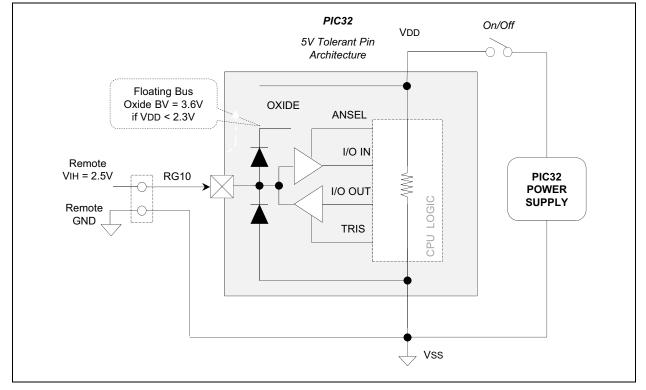

#### 2.9.2 5V TOLERANT INPUT PINS

The internal high side diode on 5V tolerant pins are bussed to an internal floating node, rather than being connected to VDD, as shown in Figure 2-7. Voltages on these pins, if VDD < 2.3V, should not exceed roughly 3.2V relative to Vss of the PIC32 device. Voltage of 3.6V or higher will violate the absolute maximum specification, and will stress the oxide layer separating the high side floating node, which impacts device reliability. If a remotely powered "digital-only" signal can be guaranteed to always be  $\leq$  3.2V relative to Vss on the PIC32 device side, a 5V tolerant pin could be used without the need for a digital isolator. This is assuming there is not a ground loop issue, logic ground of the two circuits not at the same absolute level, and a remote logic low input is not less than Vss - 0.3V.

### 3.2 Architecture Overview

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

#### 3.2.1 EXECUTION UNIT

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/<br/>DIVIDE UNIT LATENCIES AND REPEAT RATES

| Op code                 | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |

|-------------------------|--------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |

| MUL                     | 16 bits                        | 2       | 1           |

|                         | 32 bits                        | 3       | 2           |

| DIV/DIVU                | 8 bits                         | 12      | 11          |

|                         | 16 bits                        | 19      | 18          |

|                         | 24 bits                        | 26      | 25          |

|                         | 32 bits                        | 33      | 32          |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS9             | IFS8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1             | IFS0             |

#### REGISTER 5-4: IFSx: INTERRUPT FLAG STATUS REGISTER

## Legend:

| 5                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 5-1 for the exact bit definitions.

#### REGISTER 5-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IEC31-IEC0: Interrupt Enable bits

- 1 = Interrupt is enabled

- 0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 5-1 for the exact bit definitions.

## 7.1 Control Registers

## TABLE 7-1: RESET SFR SUMMARY

| Virtual Address<br>(BF80_#)<br>Register<br>Name <sup>(1</sup> )<br>Bit Range |                                 |       |       |       |       |       |       |       | Bi   | ts    |      |      |      |      |       |      |      |       |                     |

|------------------------------------------------------------------------------|---------------------------------|-------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|---------------------|

| Virtual Addr<br>(BF80_#)                                                     | Register<br>Name <sup>(1)</sup> | Ran   | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Resets          |

| F600                                                                         | RCON                            | 31:16 |       | —     | HVDR  | —     | —     | —     | —    | —     | —    | —    | —    | —    | —     | —    | —    |       | 0000                |

| F000                                                                         | RCON                            | 15:0  |       | _     | —     | _     | _     | —     | CMR  | VREGS | EXTR | SWR  | _    | WDTO | SLEEP | IDLE | BOR  | POR   | <sub>xxxx</sub> (1) |

| <b>F610</b>                                                                  | DOWDOT                          | 31:16 | _     | _     | —     | —     | _     | _     | _    | —     | _    | _    | _    | —    | _     | _    | -    | —     | 0000                |

| F610                                                                         | RSWRST                          | 15:0  | _     | —     | _     | —     | —     | _     | —    | _     | _    | _    | —    | —    | —     | _    | _    | SWRST | 0000                |

Legend: — = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

**Note 1:** The Reset value is dependent on the DEVCFGx Configuration bits and the type of reset.

NOTES:

#### TABLE 11-1: INPUT PIN SELECTION

| [pin name]R SFR      | [pin name]R bits                                                                                                                                                                                                                                                                                                                                                                               | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT3R                | INT3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0000 = RPD2<br>0001 = RPG8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| T2CKR                | T2CKR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0010 = RPF4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IC3R                 | IC3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| U1RXR                | U1RXR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0101 = RPB9<br>0110 = RPB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| U2RXR                | U2RXR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0111 = RPC14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| U5CTSR               | U5CTSR<3:0>                                                                                                                                                                                                                                                                                                                                                                                    | 1000 = RPB5 <sup>(7)</sup><br>1001 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SDI3R                | SDI3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 1010 = RPC1 <sup>(3)</sup><br>1011 = RPD14 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDI4R                | SDI4R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 1100 = RPG1 <sup>(3)</sup><br>1101 = RPA14 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| REFCLKIR             | REFCLKIR<3:0>                                                                                                                                                                                                                                                                                                                                                                                  | 1110 = Reserved<br>1111 = RPF2 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INT4R                | INT4R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0000 <b>= RPD3</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| T5CKR                | T5CKR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0001 = RPG7<br>0010 = RPF5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 0011 = RPD11<br>0100 = RPF0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 0101 = RPB1<br>0110 = RPE5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 0111 = RPC13<br>1000 = RPB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 1001 = RPF12 <sup>(3)</sup><br>1010 = RPC4 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 1011 = RPD15 <sup>(3)</sup><br>1100 = RPG0 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                | 1101 = RPA15 <sup>(3)</sup><br>1110 = RPF2 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| C1RXR <sup>(5)</sup> | C1RXR<3:0> <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                      | 1110 = R(F2(2)<br>1111 = RPF7 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INT2R                | INT2R<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0000 = RPD9<br>0001 = RPG6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| T4CKR                | T4CKR<3:0>                                                                                                                                                                                                                                                                                                                                                                                     | 0010 = RPB8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IC2R                 | IC2R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IC5R                 | IC5R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      | 0101 = RPB0<br>0110 = RPE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| U1CTSR               | U1CTSR<3:0>                                                                                                                                                                                                                                                                                                                                                                                    | 0111 = RPB7<br>1000 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| U2CTSR               | U2CTSR<3:0>                                                                                                                                                                                                                                                                                                                                                                                    | 1001 = RPF12 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SS1R                 | SS1R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      | 1010 = RPD12 <sup>(3)</sup><br>1011 = RPF8 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SS3R                 | SS1R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      | 1100 = RPC3 <sup>(3)</sup><br>1101 = RPE9 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SS3R                 | SS3R<3:0>                                                                                                                                                                                                                                                                                                                                                                                      | 1110 = RPD14 <sup>(3)</sup><br>1111 = RPB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                      | INT3R           T2CKR           IC3R           U1RXR           U2RXR           U5CTSR           SDI3R           SDI4R           REFCLKIR           INT4R           U3RXR           U4CTSR           SDI1R           SDI2R           U4CTSR           SDI2R           U1RXR <sup>(5)</sup> INT2R           INT2R           U1CTSR           U2RXR           U2RXR           SS1R           SS3R | INT3R         INT3R           IZCKR         T2CKR           IC3R         IC3R           IC3R         IC3R           U1RXR         U1RXR           U2RXR         U2RXR           U5CTSR         U5CTSR           SDI3R         SDI3R           SDI3R         SDI3R           SDI4R         SDI4R           SDI4R         SDI4R           SDI4R         SDI4R           INT4R         INT4R           INT4R         INT4R           INT4R         INT4R           INT4R         INT4R           INT4R         IAT4           INT4R         IAT4           IV3RXR         U3RXR           U3RXR         U3RXR           U4CTSR         U4CTSR           U4CTSR         SDI1R           U4CTSR         SDI2R           SDI2R         SDI2R           SDI2R         SDI2R           SDI2R         SDI2R           INT2R         INT2R           INT2R         IC2R           IC2R         IC2R           IC2R         IC2R           IC5R         IC5R           IV1CTSR |

Note 1: This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

**3:** This selection is not available on 64-pin devices.

4: This selection is not available when USBID functionality is used on USB devices.

5: This selection is not available on devices without a CAN module.

6: This selection is not available on USB devices.

7: This selection is not available when VBUSON functionality is used on USB devices.

## TABLE 11-6: PORTC REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |           |           |           |           |       |       |      | Bits |      |      |      |      |         |         |         |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|------|---------|---------|---------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3    | 18/2    | 17/1    | 16/0 | All<br>Resets |

| 6200                        | ANSELC                          | 31:16     | _         | —         | —         | _         | —     | -     |      |      | _    | —    | _    |      | —       |         | —       | —    | 0000          |

| 0200                        | /                               | 15:0      | —         | —         | —         | —         | —     | —     | —    | _    | —    | _    | —    | _    | ANSELC3 | ANSELC2 | ANSELC1 | —    | 000E          |

| 6210                        | TRISC                           | 31:16     |           | —         | —         | —         | _     | _     | _    |      | _    |      | —    | _    | _       | _       | —       | _    | 0000          |

| 02.0                        |                                 | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | —     | —     | —    | _    | —    | _    | —    | _    | —       | —       | —       | —    | F000          |

| 6220                        | PORTC                           | 31:16     | —         | —         | —         | —         | _     | _     | _    | _    | —    | _    | —    | _    | —       | _       | —       |      | 0000          |

| 0220                        | 1 on 10                         | 15:0      | RC15      | RC14      | RC13      | RC12      | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | xxxx          |

| 6230                        | LATC                            | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 0200                        | Ento                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | xxxx          |

| 6240                        | ODCC                            | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 02.10                       | 0200                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 6250                        | CNPUC                           | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 0200                        |                                 | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 6260                        | CNPDC                           | 31:16     |           | —         | —         | —         | —     | _     | _    | _    | —    | —    | —    |      | —       | _       | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 6270                        | CNCONC                          | 31:16     |           |           |           | _         |       |       | _    |      | —    | _    | —    |      | —       |         | —       |      | 0000          |

| 0270                        | oncono                          | 15:0      | ON        |           | SIDL      |           |       |       | _    |      | —    | _    | —    |      | —       |         | —       |      | 0000          |

| 6280                        | CNENC                           | 31:16     |           | —         |           |           |       |       | _    |      | —    | _    | —    |      | —       |         | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | —     | _     | _    |      | —    |      | —    | _    | —       |         | —       | _    | 0000          |

| 6200                        | CNSTATC                         | 31:16     | _         | —         | —         | _         | _     |       |      |      | -    | —    | -    |      | —       |         | —       | —    | 0000          |

| 0290                        | GNOTAIC                         | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     |       |      |      | -    | _    |      |      | _       |         | —       | _    | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

## TABLE 11-8: PORTD REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |               |               |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | _     | _     | —     | _     |               | —             | —            |              | _            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0000                        | THOLLD                          | 15:0      | —     | —     | —     | —     |               |               | —            | _            | _            | —            | _            |              | ANSELD3      | ANSELD2      | ANSELD1      | —            | 000E          |

| 6310                        | TRISD                           | 31:16     | —     | —     | —     | —     | —             |               | —            | —            | _            |              | —            | _            |              | —            |              |              | 0000          |

| 0310                        | TRIOD                           | 15:0      | —     | —     | —     | _     | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | OFFF          |

| 5320                        | PORTD                           | 31:16     | —     | _     | _     | _     | _             | _             | —            | _            | _            | _            | _            |              | _            | —            |              | _            | 0000          |

| 3320                        | TORID                           | 15:0      | —     | —     | —     | _     | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | 6330 LATD                       | 31:16     | —     | —     | —     | _     | —             | —             | _            | _            | _            | —            | _            | -            | —            | —            | _            | _            | 0000          |

| 0330                        | LAID                            | 15:0      | -     | _     | _     | _     | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | xxxx          |

| 6340                        | ODCD                            | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0340                        | ODCD                            | 15:0      | Ι     |       |       | -     | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | 0000          |

| 6350                        | CNPUD                           | 31:16     | -     | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0330                        | CINFUD                          | 15:0      | -     | _     | _     | _     | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | 0000          |

| 6360                        | CNPDD                           | 31:16     | -     | _     | _     | _     |               | _             | _            |              |              | _            |              |              | _            | _            | _            | _            | 0000          |

| 0300                        | CNFDD                           | 15:0      | -     | _     | -     |       | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | 0000          |

| 6270                        | CNCOND                          | 31:16     | -     | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0370                        | CINCOIND                        | 15:0      | ON    | _     | SIDL  |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 6380                        | CNEND                           | 31:16     | -     | _     | -     |       | —             | —             | _            | —            | —            | —            | —            | —            | —            | _            | _            | —            | 0000          |

| 0300                        | CNEND                           | 15:0      | Ι     | -     | -     | Ι     | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | _     | _             | _             | _            | —            | _            | _            | _            | _            | _            | _            |              | _            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | _     | _     | _     | -     | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

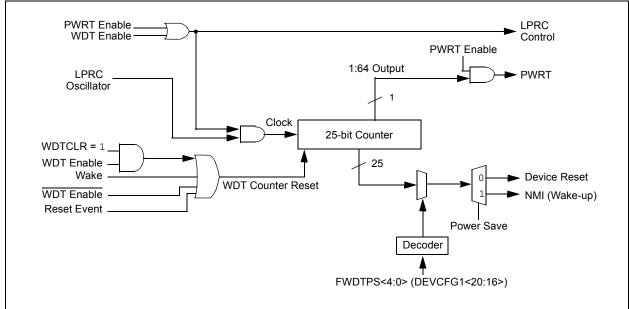

## 14.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin Family family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Watchdog Timer (WDT), when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

#### FIGURE 14-1: WATCHDOG AND POWER-UP TIMER BLOCK DIAGRAM

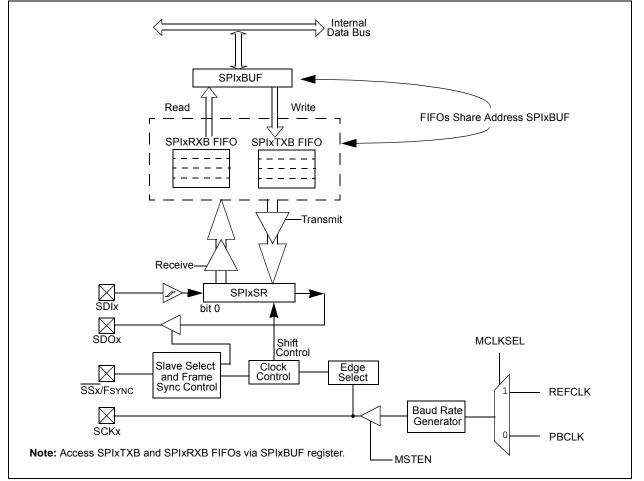

## 17.0 SERIAL PERIPHERAL INTERFACE (SPI)