Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx530f128lt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | —                 | _                 | _                 | —                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 |                   | _                 | _                 | —                 | —                | _                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   | BMXDK             | PBA<15:8>         |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | BMXDKPBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24     | CHSSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.10     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45-0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8      |                   |                   |                   | CHSSA<15:8>       |                   |                   |                  |                  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0       | CHSSA<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

## **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

## **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | CHDSA             | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | CHDSA<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\text{Note:}}$  This must be the physical address of the destination.

## TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                          |                      |           |       |        |       |       |       |       |      | В    | its  |      |      |      |      |      |        |      |            |

|-----------------------------|----------------------|-----------|-------|--------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14  | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

|                             |                      | 31:16     | _     | _      | _     | -     | _     | _     | _    | -    | -    | _    | -    | _    | _    | _    | -      | _    | 00         |

| FB88                        | RPC2R                | 15:0      | _     | _      | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC2 | 2<3:0> |      | 00         |

|                             |                      | 31:16     | _     | _      | _     | _     | —     | _     | _    | _    | _    | _    | —    | _    | —    | —    | _      | _    | 00         |

| FB8C                        | RPC3R                | 15:0      | _     | —      | —     | _     | —     | —     | _    | —    | —    | _    | —    | _    |      | RPC  | 3<3:0> |      | 00         |

| 5000                        | 00040                | 31:16     | _     | —      | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FB90                        | RPC4R                | 15:0      | _     | _      | _     | _     | —     | _     | _    | _    | _    | _    | —    | _    |      | RPC4 | <3:0>  |      | 00         |

| 5004                        | 000400               | 31:16     | _     | —      | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBB4                        | RPC13R               | 15:0      | _     | —      | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC1 | 3<3:0> |      | 00         |

|                             |                      | 31:16     | _     | _      | _     | _     | _     | _     | _    | _    | _    | _    | _    |      | —    | _    | _      |      | 00         |

| FBB8                        | RPC14R               | 15:0      | _     | _      | _     | _     | —     | —     | _    | —    | —    | _    | —    | _    |      | RPC1 | 4<3:0> |      | 00         |

| 50.00                       | 00000                | 31:16     | _     | —      | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBC0                        | RPD0R                | 15:0      | _     | _      | _     | _     | _     | _     | _    | _    | _    | _    | _    |      |      | RPD  | )<3:0> |      | 00         |

|                             |                      | 31:16     | _     | _      | _     | _     | —     | —     | _    | —    | —    | _    | —    | _    | —    | —    | _      | _    | 00         |

| FBC4                        | RPD1R                | 15:0      | _     | —      | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD' | <3:0>  |      | 00         |

|                             |                      | 31:16     | _     | _      | _     | _     | _     | _     | _    | _    | _    | _    | _    |      | _    | _    | _      |      | 00         |

| FBC8                        | RPD2R                | 15:0      | _     | —      | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    |      | RPD2 | 2<3:0> |      | 00         |

| 5000                        | 00000                | 31:16     | _     | —      | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBCC                        | RPD3R                | 15:0      | _     | —      | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD  | 3<3:0> |      | 00         |

| 5000                        | 00040                | 31:16     | _     | —      | —     | _     | —     | —     | —    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBD0                        | RPD4R                | 15:0      | _     | —      | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD4 | <3:0>  |      | 00         |

|                             | 00050                | 31:16     | _     | —      | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBD4                        | RPD5R                | 15:0      | _     | —      | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD  | 5<3:0> |      | 00         |

|                             |                      | 31:16     | —     | —      | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | _    | —    | —      |      | 00         |

| FBE0                        | RPD8R                | 15:0      | _     | —      | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD8 | 3<3:0> |      | 00         |

| 5054                        | 00000                | 31:16     | _     | —      | —     | _     | —     | —     | _    | —    | —    | _    | —    | _    | —    | —    | —      | _    | 00         |

| FBE4                        | RPD9R                | 15:0      | _     | —      | —     | _     | —     | —     | _    | —    | —    | _    | —    | _    |      | RPD9 | 9<3:0> |      | 00         |

|                             |                      | 31:16     | _     | —      | —     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | —      |      | 00         |

| FBE8                        | RPD10R               | 15:0      | _     | —      | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPD1 | 0<3:0> |      | 00         |

|                             | 000440               | 31:16     | _     | _      | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | —    | _    | _      | —    | 00         |

| FBEC                        | RPD11R               | 15:0      | —     | _      | —     | _     | —     | —     | _    | —    | _    | _    | _    | _    |      | RPD1 | 1<3:0> |      | 00         |

| FDFC                        |                      | 31:16     | _     | —      | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | —    | —    | —      | —    | 00         |

| FBF0                        | FBF0 RPD12R 15:0 RPD |           | RPD1  | 2<3:0> |       | 00    |       |       |      |      |      |      |      |      |      |      |        |      |            |

| EDEC                        |                      | 31:16     | _     | —      | —     | —     | _     | _     | _    | _    | _    | _    | _    | _    | —    | —    | —      | —    | 00         |

| FBF8                        | RPD14R               | 15:0      | _     | _      | _     | _     | _     | _     | _    |      | _    | _    | _    | _    |      | RPD1 | 4<3:0> |      | 00         |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

|                             | LE 19-1:                 | UAI       |        | ROUGE   | UARTS  |       |           |                               |       | (ש.         |                       |         |       |          |          |      |        |       |            |

|-----------------------------|--------------------------|-----------|--------|---------|--------|-------|-----------|-------------------------------|-------|-------------|-----------------------|---------|-------|----------|----------|------|--------|-------|------------|

| ess                         |                          | đ         |        |         |        |       |           |                               |       | Bi          | ts                    |         |       |          |          |      |        |       | s          |

| Virtual Address<br>(BF80_#) | Register<br>Name         | Bit Range | 31/15  | 30/14   | 29/13  | 28/12 | 27/11     | 26/10                         | 25/9  | 24/8        | 23/7                  | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6440                        |                          | 31:16     | _      | —       | —      |       | —         |                               | —     | —           |                       | —       | _     |          | _        | _    | _      |       | 0000       |

| 0440                        | USBRG. /                 | 15:0      |        |         |        |       |           | Baud Rate Generator Prescaler |       |             |                       |         | 0000  |          |          |      |        |       |            |

| 6600                        | U4MODE <sup>(1)</sup>    | 31:16     | _      | _       | _      |       | _         |                               | _     | _           |                       | —       | _     |          | _        | _    | _      |       | 0000       |

| 0000                        | 04IVIODL.                | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD     | —                             | UEN   | <1:0>       | WAKE                  | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6610                        | U4STA <sup>(1)</sup>     | 31:16     | _      | —       | —      | -     | —         | _                             | —     | ADM_EN      |                       |         |       | ADDF     | R<7:0>   |      | -      |       | 0000       |

| 0010                        | 04017                    | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK    | UTXEN                         | UTXBF | TRMT        | URXISI                | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6620                        | U4TXREG                  | 31:16     | —      |         | —      | _     | _         | _                             |       | —           | _                     | —       | —     | _        | —        | —    | —      | —     | 0000       |

| 0020                        | OFINICO                  | 15:0      | —      |         | —      | _     | _         | _                             |       | TX8         | TX8 Transmit Register |         |       |          | 0000     |      |        |       |            |

| 6630                        | U4RXREG                  | 31:16     | —      |         | —      | _     | _         | _                             |       | _           |                       | —       | _     | _        | _        | _    | _      | —     | 0000       |

| 0000                        | OHIVILO                  | 15:0      | —      |         | —      | _     | _         | _                             |       | RX8         |                       |         |       | Receive  | Register |      |        |       | 0000       |

| 6640                        | U4BRG <sup>(1)</sup>     | 31:16     | —      | —       | —      | —     | —         | —                             | —     | —           | —                     | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0010                        | U IBIKO                  | 15:0      |        |         |        |       |           |                               | Bau   | d Rate Gen  | erator Pres           | caler   |       |          |          |      |        |       | 0000       |

| 6800                        | U5MODE <sup>(1,2)</sup>  | 31:16     |        | —       | —      |       | —         | _                             | —     |             |                       | —       | —     |          | —        | —    | —      |       | 0000       |

|                             | 00111022                 | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD     | _                             | UEN   | <1:0>       | WAKE                  | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6810                        | U5STA <sup>(1,2)</sup>   | 31:16     | —      | —       | —      | —     | —         | —                             | —     | ADM_EN      |                       |         |       | 1        | R<7:0>   | 1    | 1      | 1     | 0000       |

|                             |                          | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK    | UTXEN                         | UTXBF | TRMT        | URXIS                 | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6820                        | U5TXREG <sup>(1,2)</sup> | 31:16     | _      |         | —      | _     | —         |                               |       |             | _                     | —       | —     | —        |          | —    |        |       | 0000       |

|                             |                          | 15:0      | _      |         | —      | _     | —         |                               |       | TX8         |                       |         |       | Transmit | Register |      |        |       | 0000       |

| 6830                        | U5RXREG <sup>(1,2)</sup> | 31:16     | _      |         | —      | —     | —         |                               |       | —           | —                     | —       | —     | —        | —        | —    | —      | —     | 0000       |

|                             |                          | 1010      | —      |         | —      | —     | —         |                               |       | RX8         |                       |         |       | Receive  | Register |      |        |       | 0000       |

| 6840                        | U5BRG <sup>(1,2)</sup>   | 31:16     | —      | —       | —      | —     | —         | —                             | —     | —           | —                     | —       | —     | —        | —        | —    | —      |       | 0000       |

|                             |                          | 15:0      |        |         |        |       | 'o' Booot |                               |       | d Rate Gene | erator Pres           | caler   |       |          |          |      |        |       | 0000       |

## TABLE 19-1: UART1 THROUGH UART5 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register is only available on 100-pin devices.

## 20.1 Control Registers

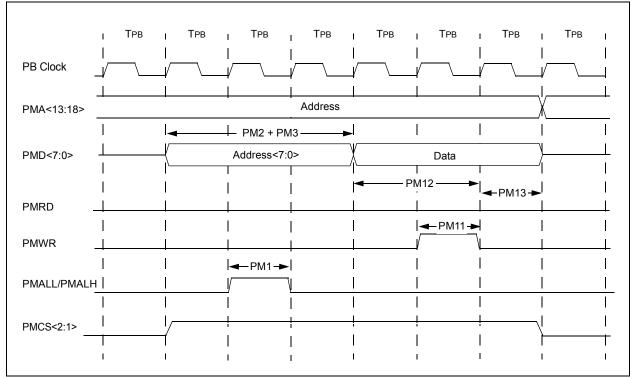

## TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | ē         |               |               |                    |               |         |        |        | Bi     | its        |         |      |       |        |      |         |      |            |

|-----------------------------|---------------------------------|-----------|---------------|---------------|--------------------|---------------|---------|--------|--------|--------|------------|---------|------|-------|--------|------|---------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13              | 28/12         | 27/11   | 26/10  | 25/9   | 24/8   | 23/7       | 22/6    | 21/5 | 20/4  | 19/3   | 18/2 | 17/1    | 16/0 | All Resets |

| 7000                        | PMCON                           | 31:16     | —             | _             | _                  | _             | -       | —      | -      |        | RDSTART    | —       | -    | —     | _      | _    | DUALBUF | _    | 0000       |

| 1000                        |                                 | 15:0      | ON            | —             | SIDL               | ADRML         | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF∢       | <1:0>   | ALP  | CS2P  | CS1P   | —    | WRSP    | RDSP | 0000       |

| 7010                        | PMMODE                          | 31:16     | —             | —             | —                  | —             | —       | _      | —      | —      | —          | _       | —    | —     | —      | —    | -       | _    | 0000       |

|                             |                                 | 15:0      | BUSY          | IRQM          | <1:0>              | INCM          | <1:0>   | MODE16 | MODE   | <1:0>  | WAITE      | 3<1:0>  |      | WAITN | 1<3:0> |      | WAITE   |      | 0000       |

|                             |                                 | 31:16     | —             | —             | _                  | —             | —       | —      | —      | —      | —          | —       | —    | —     | —      | —    | —       | _    | 0000       |

| 7020                        | PMADDR                          | 15:0      | CS2<br>ADDR15 | CS1<br>ADDR14 |                    |               |         |        |        |        | ADDR       | <13:0>  |      |       |        |      |         |      | 0000       |

|                             |                                 | 31:16     | ADDR15        | ADDR 14       | _                  |               | _       |        | _      | _      | _          |         | _    |       |        | _    | _       | _    | 0000       |

| 7030                        | PMDOUT                          | 15:0      |               |               |                    | DATAOUT<15:0> |         |        |        |        |            |         | 0000 |       |        |      |         |      |            |

|                             |                                 | 31:16     |               |               |                    |               |         |        |        |        |            |         | _    |       |        |      | _       | _    | 0000       |

| 7040                        | PMDIN                           | 15:0      |               |               |                    |               |         |        |        | DATAIN | l<15:0>    |         |      |       |        |      |         |      | 0000       |

|                             |                                 | 31:16     | _             | _             | _                  | _             | _       | _      | _      | _      | _          | —       | _    | _     | _      | _    | _       | _    | 0000       |

| 7050                        | PMAEN                           | 15:0      |               |               |                    |               |         |        |        | PTEN   | <15:0>     |         |      |       |        |      |         |      | 0000       |

| 7060                        | PMSTAT                          | 31:16     | —             | —             | _                  | —             | _       | _      | _      | —      | —          | _       | _    | —     | —      | —    | —       | _    | 0000       |

| 7000                        | FINISTAT                        | 15:0      | IBF           | IBOV          |                    | _             | IB3F    | IB2F   | IB1F   | IB0F   | OBE        | OBUF    |      | _     | OB3E   | OB2E | OB1E    | OB0E | BFBF       |

|                             |                                 | 31:16     | —             | _             |                    | —             |         | —      | 1      | -      | -          | —       | 1    | —     | _      | -    | -       |      | 0000       |

| 7070                        | PMWADDR                         | 15:0      | WCS2          | WCS1          | _                  | —             | _       | _      | _      | —      | —          |         | _    | —     | —      | _    | -       | _    | 0000       |

|                             |                                 | 15.0      | WADDR15       | WADDR14       | ADDR14 WADDR<13:0> |               |         |        |        |        |            | 0000    |      |       |        |      |         |      |            |

|                             |                                 | 31:16     | —             | —             | _                  | —             |         | _      | _      | _      | _          |         | _    | —     | —      | _    | —       |      | 0000       |

| 7080                        | PMRADDR                         | 15:0      | RCS2          | RCS1          | _                  | —             | _       |        | —      | —      | —          | _       | —    | —     | —      | _    | —       | _    | 0000       |

|                             |                                 |           | RADDR15       | RADDR14       |                    |               |         |        |        |        | RADDF      | R<13:0> |      |       |        |      |         |      | 0000       |

| 7090                        | PMRDIN                          | 31:16     | 31:16         | —             | —                  | —             | _       | _      | —      | —      | —          | —       | —    | —     | —      | _    | —       | _    | 0000       |

| 1030                        |                                 | 15:0      | 15:0          |               |                    |               |         |        |        | R      | DATAIN<15: | 0>      |      |       |        |      |         |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 31:24        | U-0                 | U-0                 |

| 31.24        | —                 | —                 | —                 | _                 | —                 | —                 | —                   | —                   |

| 23:16        | U-0                 | U-0                 |

| 23.10        | —                 | —                 | —                 | _                 | —                 | —                 | —                   | —                   |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                 | —                 | F                 | ORM<2:0>            |                     |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7.0          |                   | SSRC<2:0>         |                   | CLRASAM           | _                 | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1

## Legend:

bit 14

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12-11 Unimplemented: Read as '0'

- bit 10-8 **FORM<2:0>:** Data Output Format bits

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

#### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing SAMP bit ends sampling and starts conversion

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

## REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER (CONTINUED)

```

bit 21-16 CH0SA<5:0>: Positive Input Select bits for Sample A Multiplexer Setting

For 64-pin devices:

011110 = Channel 0 positive input is Open<sup>(1)</sup>

011101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

011100 = Channel 0 positive input is IVREF<sup>(3)</sup>

011011 = Channel 0 positive input is AN27

000001 = Channel 0 positive input is AN1

000000 = Channel 0 positive input is AN0

For 100-pin devices:

110010 = Channel 0 positive input is Open<sup>(1)</sup>

110001 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(2)</sup>

110000 = Channel 0 positive input is IVREF<sup>(3)</sup>

101111 = Channel 0 positive input is AN47

0000001 = Channel 0 positive input is AN1

0000000 = Channel 0 positive input is AN0

bit 15-0

Unimplemented: Read as '0'

```

- Note 1: This selection is only used with CTMU capacitive and time measurement.

- 2: See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 3: Internal precision 1.2V reference. See Section 24.0 "Comparator" for more information.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0                     | U-0                | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                       | _                  | _                 | —                 | —                 | —                 | -                | _                |  |

| 00.40        | U-0                     | R/W-0              | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | —                       | WAKFIL             | _                 | _                 |                   | SEG               | ,4)              |                  |  |

| 45.0         | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | SEG2PHTS <sup>(1)</sup> | SAM <sup>(2)</sup> | SEG1PH<2:0>       |                   |                   | PRSEG<2:0>        |                  |                  |  |

| 7:0          | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | SJW<1:0> <sup>(3)</sup> |                    |                   | BRP<5:0>          |                   |                   |                  |                  |  |

## **REGISTER 23-2: C1CFG: CAN BAUD RATE CONFIGURATION REGISTER**

| Legend:           | HC = Hardware Clear | S = Settable bit                   |                    |  |

|-------------------|---------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-23 Unimplemented: Read as '0'

- bit 22 WAKFIL: CAN Bus Line Filter Enable bit 1 = Use CAN bus line filter for wake-up 0 = CAN bus line filter is not used for wake-up

- bit 21-19 Unimplemented: Read as '0'

| 511 21 15 |                                                                               |

|-----------|-------------------------------------------------------------------------------|

| bit 18-16 | SEG2PH<2:0>: Phase Buffer Segment 2 bits <sup>(1,4)</sup>                     |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x TQ                                                        |

| bit 15    | SEG2PHTS: Phase Segment 2 Time Select bit <sup>(1)</sup>                      |

|           | 1 = Freely programmable                                                       |

|           | 0 = Maximum of SEG1PH or Information Processing Time, whichever is greater    |

| bit 14    | SAM: Sample of the CAN Bus Line bit <sup>(2)</sup>                            |

|           | 1 = Bus line is sampled three times at the sample point                       |

|           | 0 = Bus line is sampled once at the sample point                              |

| bit 13-11 | SEG1PH<2:0>: Phase Buffer Segment 1 bits <sup>(4)</sup>                       |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x TQ                                                        |

|           |                                                                               |

| Note 1:   | SEG2PH $\leq$ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. |

| 2:        | 3 Time bit sampling is not allowed for BRP < 2.                               |

| 3:        | SJW ≤ SEG2PH.                                                                 |

|           |                                                                               |

- 4: The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

- This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> Note: (C1CON < 23:21 >) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | _                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | —                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

## **REGISTER 23-3: C1INT: CAN INTERRUPT REGISTER**

## Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | IVRIE: Invalid Message Received Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | <b>WAKIE:</b> CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                            |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | <b>MODIE:</b> Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by cl                                                                                          |

learing or setting the ON bit N (C1CON<15>).

## REGISTER 23-12: C1FLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED) bit 20-16 FSEL10<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 FLTEN9: Filter 9 Enable bit bit 15 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL9<1:0>: Filter 9 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL9<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN8: Filter 8 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL8<1:0>: Filter 8 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL8<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. Note:

## **REGISTER 23-17:** C1FIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' ('n' = 0 THROUGH 15)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2        | Bit<br>25/17/9/1        | Bit<br>24/16/8/0          |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|---------------------------|

| 01.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24        | —                 | —                 | —                 | _                 | —                 | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16        | —                 | —                 | —                 | _                 | RXOVFLIE          | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0                      | R-0                     | R-0                       |

| 15:8         | —                 | —                 | —                 | _                 | —                 | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R-0                      | R-0                     | R-0                       |

| 7:0          | —                 | —                 | —                 | _                 | RXOVFLIF          | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

## bit 31-27 Unimplemented: Read as '0'

| DIL 31-21 | Unimplemented. Read as 0                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------|

| bit 26    | TXNFULLIE: Transmit FIFO Not Full Interrupt Enable bit                                                          |

|           | 1 = Interrupt enabled for FIFO not full                                                                         |

|           | 0 = Interrupt disabled for FIFO not full                                                                        |

| bit 25    | <b>TXHALFIE:</b> Transmit FIFO Half Full Interrupt Enable bit                                                   |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

|           | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 24    | <b>TXEMPTYIE:</b> Transmit FIFO Empty Interrupt Enable bit                                                      |

|           | <ul> <li>1 = Interrupt enabled for FIFO empty</li> <li>0 = Interrupt disabled for FIFO empty</li> </ul>         |

| hit 23-20 | Unimplemented: Read as '0'                                                                                      |

| bit 19    | RXOVFLIE: Overflow Interrupt Enable bit                                                                         |

| DIC 13    | 1 = Interrupt enabled for overflow event                                                                        |

|           | 0 = Interrupt disabled for overflow event                                                                       |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                             |

|           | 1 = Interrupt enabled for FIFO full                                                                             |

|           | 0 = Interrupt disabled for FIFO full                                                                            |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                   |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

|           | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 16    | RXNEMPTYIE: Empty Interrupt Enable bit                                                                          |

|           | <ul> <li>1 = Interrupt enabled for FIFO not empty</li> <li>0 = Interrupt disabled for FIFO not empty</li> </ul> |

| hit 15 11 |                                                                                                                 |

| bit 10    | Unimplemented: Read as '0'                                                                                      |

| DICTO     | <b>TXNFULLIF:</b> Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                      |

|           | <u>TXEN = 1:</u> (FIFO configured as a transmit buffer)<br>1 = FIFO is not full                                 |

|           | 0 = FIFO is full                                                                                                |

|           | TXEN = 0: (FIFO configured as a receive buffer)                                                                 |

|           | Unused, reads '0'                                                                                               |

|           |                                                                                                                 |

| Note 1:   | This bit is read-only and reflects the status of the FIFO.                                                      |

NOTES:

## 27.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

## 27.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

## 27.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PMDL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 |          |      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|----------|------|-------------------|------------------|------------------|--|--|

| 31:24        | R/P               | R/P               | R/P               | R/P      | U-0  | U-0               | U-0              | U-0              |  |  |

|              | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY | _    | —                 | —                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0      | U-0  | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | _                 | _                 | _        | -    | _                 | -                | _                |  |  |

| 15:8         | R/P               | R/P               | R/P               | R/P      | R/P  | R/P               | R/P              | R/P              |  |  |

| 10.0         | USERID<15:8>      |                   |                   |          |      |                   |                  |                  |  |  |

| 7:0          | R/P               | R/P               | R/P               | R/P      | R/P  | R/P               | R/P              | R/P              |  |  |

| 7:0          |                   |                   |                   | USERID<  | 7:0> |                   |                  |                  |  |  |

## REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bi  | it                 |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 FVBUSONIO: USB VBUS\_ON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 **IOL1WAY:** Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDL1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-16 Unimplemented: Read as '0'

- bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

## TABLE 31-10: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |         |      |       |            |  |

|--------------------|--------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|

| Param.<br>No.      | Symbol | Characteristics                                        | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                               | Typical | Max. | Units | Conditions |  |

| BO10               | Vbor   | BOR Event on VDD transition high-to-low <sup>(2)</sup> | 2.0                                                                                                                                                                                                                                                                               | _       | 2.3  | V     | —          |  |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

## TABLE 31-11: ELECTRICAL CHARACTERISTICS: HVD

| DC CHARACTERISTICS           |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |         |      |       |            |  |

|------------------------------|--------|-------------------------------------------------------|------|---------|------|-------|------------|--|

| Param.<br>No. <sup>(1)</sup> | Symbol | Characteristics                                       | Min. | Typical | Max. | Units | Conditions |  |

| HV10                         | Vhvd   | High Voltage Detect on VCAP pin                       | —    | 2.5     |      | V     | _          |  |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

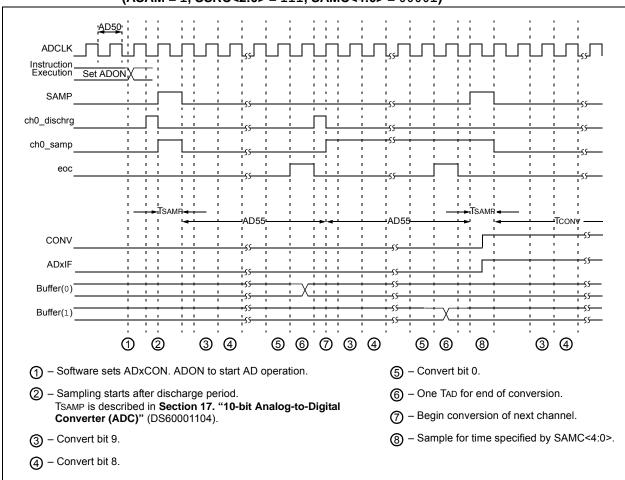

## FIGURE 31-19: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

| AC CHARACTERISTICS |         |                                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |      |       |            |  |

|--------------------|---------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                                                  | Тур.  | Max. | Units | Conditions |  |

| PM1                | TLAT    | PMALL/PMALH Pulse Width                                              | _                                                                                                                                                                                                                                                                                     | 1 Трв |      | _     | _          |  |

| PM2                | Tadsu   | Address Out Valid to PMALL/<br>PMALH Invalid (address setup time)    | _                                                                                                                                                                                                                                                                                     | 2 Трв | _    | _     | _          |  |

| PM3                | Tadhold | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                                                                                                                                                                                                                                                     | 1 Трв | _    | —     |            |  |

| PM4                | Tahold  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                                                     | _     | _    | ns    | _          |  |

| PM5                | Trd     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                                                     | 1 Трв | _    | _     | _          |  |

| PM6                | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                                                                                                                                                                                                                                                    | —     | _    | ns    | _          |  |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to<br>Data In Invalid (data hold time)        | —                                                                                                                                                                                                                                                                                     | 80    | _    | ns    | _          |  |

## TABLE 31-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

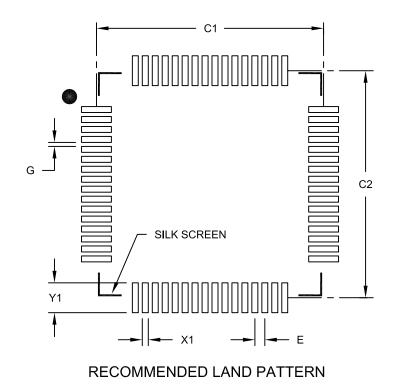

## 64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|------|----------|-------------|--|--|--|

| Dimensior                | Dimension Limits |      | NOM      | MAX         |  |  |  |

| Contact Pitch            | E                |      | 0.50 BSC |             |  |  |  |

| Contact Pad Spacing      | C1               |      | 11.40    |             |  |  |  |

| Contact Pad Spacing      | C2               |      | 11.40    |             |  |  |  |

| Contact Pad Width (X64)  | X1               |      |          | 0.30        |  |  |  |

| Contact Pad Length (X64) | Y1               |      |          | 1.50        |  |  |  |

| Distance Between Pads    | G                | 0.20 |          |             |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

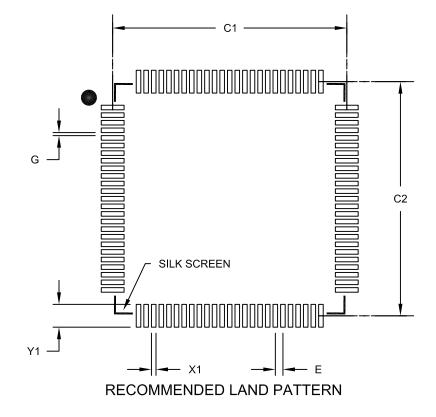

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units            | MILLIMETERS |          |      |  |

|---------------------------|------------------|-------------|----------|------|--|

| Dimensior                 | Dimension Limits |             | NOM      | MAX  |  |

| Contact Pitch             | E                |             | 0.50 BSC |      |  |

| Contact Pad Spacing       | C1               |             | 15.40    |      |  |

| Contact Pad Spacing       | C2               |             | 15.40    |      |  |

| Contact Pad Width (X100)  | X1               |             |          | 0.30 |  |

| Contact Pad Length (X100) | Y1               |             |          | 1.50 |  |

| Distance Between Pads     | G                | 0.20        |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B