Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx550f256h-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.1 Interrupts Control Registers

#### TABLE 5-2: INTERRUPT REGISTER MAP

| sse                         |                                 |               |                 |                  |                   |                  |                  |                 |                |                 | Bits              |                       |                       |                      |                         |                         |                |                 |               |

|-----------------------------|---------------------------------|---------------|-----------------|------------------|-------------------|------------------|------------------|-----------------|----------------|-----------------|-------------------|-----------------------|-----------------------|----------------------|-------------------------|-------------------------|----------------|-----------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(3)</sup> | Bit Range     | 31/15           | 30/14            | 29/13             | 28/12            | 27/11            | 26/10           | 25/9           | 24/8            | 23/7              | 22/6                  | 21/5                  | 20/4                 | 19/3                    | 18/2                    | 17/1           | 16/0            | All<br>Resets |

| 1000                        | INTCON                          | 31:16         | _               |                  | _                 | —                | _                |                 | —              | _               | —                 | —                     | —                     | -                    | -                       | -                       | -              | -               | 0000          |

|                             |                                 | 15:0          |                 |                  | _                 | MVEC             | —                |                 | TPC<2:0>       |                 | _                 | _                     | _                     | INT4EP               | INT3EP                  | INT2EP                  | INT1EP         | INT0EP          | 0000          |

| 1010                        | INTSTAT <sup>(4)</sup>          | 31:16<br>15:0 |                 |                  |                   |                  | _                |                 |                |                 |                   |                       |                       | _                    | <br>VEC<                | 5:0>                    | _              |                 | 0000          |

|                             |                                 | 31:16         |                 |                  |                   |                  |                  |                 |                |                 |                   |                       |                       |                      | VLOV                    | 0.0-                    |                |                 | 0000          |

| 1020                        | IPTMR                           | 15:0          |                 | IPTMR<31:0> 0000 |                   |                  |                  |                 |                |                 |                   |                       |                       |                      |                         |                         |                |                 |               |

| 1030                        | IFS0                            | 31:16         | FCEIF           | RTCCIF           | FSCMIF            | AD1IF            | OC5IF            | IC5IF           | IC5EIF         | T5IF            | INT4IF            | OC4IF                 | IC4IF                 | IC4EIF               | T4IF                    | INT3IF                  | OC3IF          | IC3IF           | 0000          |

| 1030                        | 150                             | 15:0          | IC3EIF          | T3IF             | INT2IF            | OC2IF            | IC2IF            | IC2EIF          | T2IF           | INT1IF          | OC1IF             | IC1IF                 | IC1EIF                | T1IF                 | INT0IF                  | CS1IF                   | CS0IF          | CTIF            | 0000          |

| 1040                        | IFS1                            | 31:16         | <b>U3RXIF</b>   | U3EIF            | I2C2MIF           | I2C2SIF          | I2C2BIF          | U2TXIF          | U2RXIF         | U2EIF           | SPI2TXIF          | SPI2RXIF              | SPI2EIF               | PMPEIF               | PMPIF                   | CNGIF                   | CNFIF          | CNEIF           | 0000          |

| 1010                        |                                 | 15:0          | CNDIF           | CNCIF            | CNBIF             | CNAIF            | I2C1MIF          | I2C1SIF         | I2C1BIF        | U1TXIF          | U1RXIF            | U1EIF                 | SPI1TXIF              | SPI1RXIF             | SPI1EIF                 | USBIF <sup>(2)</sup>    | CMP2IF         | CMP1IF          | 0000          |

| 1050                        | IFS2                            | 31:16         | —               | —                | —                 |                  | —                | —               | —              | —               | _                 | (1)                   | (1)                   | —                    | SPI4TXIF <sup>(1)</sup> | SPI4RXIF <sup>(1)</sup> | -              | <b>SPI3TXIF</b> |               |

|                             |                                 | 15:0          | SPI3RXIF        | SPI3EIF          | CANIF             | CMP3IF           | DMA3IF           | DMA2IF          | DMA1IF         | DMA0IF          | CTMUIF            | U5TXIF <sup>(1)</sup> | U5RXIF <sup>(1)</sup> | U5EIF <sup>(1)</sup> | U4TXIF                  | U4RXIF                  | U4EIF          | U3TXIF          | 0000          |

| 1060                        | IEC0                            | 31:16         | FCEIE<br>IC3EIE | RTCCIE<br>T3IE   | FSCMIE<br>INT2IE  | AD1IE            | OC5IE            | IC5IE<br>IC2EIE | IC5EIE<br>T2IE | T5IE            | INT4IE            | OC4IE                 | IC4IE                 | IC4EIE<br>T1IE       | T4IE<br>INT0IE          | INT3IE                  | OC3IE          | IC3IE<br>CTIE   | 0000          |

|                             |                                 | 15:0<br>31:16 | U3RXIE          | U3EIE            | INTZIE<br>I2C2MIE | OC2IE<br>I2C2SIE | IC2IE<br>I2C2BIE | U2TXIE          | U2RXIE         | INT1IE<br>U2EIE | OC1IE<br>SPI2TXIE | IC1IE<br>SPI2RXIE     | SPI2EIE               | PMPEIE               | PMPIE                   | CS1IE<br>CNGIE          | CS0IE<br>CNFIE | CITE            | 0000          |

| 1070                        | IEC1                            | 15:0          | CNDIE           | CNCIE            | CNBIE             | CNAIE            | I2C2BIE          | I2C1SIE         | I2C1BIE        | U1TXIE          | U1RXIE            | U1EIE                 | SPIZEIE               | SPI1RXIE             | SPI1EIE                 | USBIE <sup>(2)</sup>    | CMP2IE         | CMP1IE          | 0000          |

|                             |                                 | 31:16         | _               |                  |                   | _                |                  | -               |                |                 |                   | _                     |                       |                      |                         |                         | _              |                 | 0000          |

| 1080                        | IEC2                            | 15:0          | _               | _                | _                 | _                | DMA3IE           | DMA2IE          | DMA1IE         | DMA0IE          | CTMUIE            | U5TXIE <sup>(1)</sup> | U5RXIE <sup>(1)</sup> | U5EIE <sup>(1)</sup> | U4TXIE                  | U4RXIE                  | U4EIE          | U3TXIE          | 0000          |

|                             |                                 | 31:16         | _               | _                | _                 | IN               | T0IP<2:0>        |                 | INTOIS         |                 | _                 | _                     | _                     |                      | CS1IP<2:0>              | ,                       | CS1IS          | 6<1:0>          | 0000          |

| 1090                        | IPC0                            | 15:0          | _               | _                | _                 | CS               | S0IP<2:0>        |                 | CSOIS          | <1:0>           |                   | _                     | _                     |                      | CTIP<2:0>               |                         | CTIS           | <1:0>           | 0000          |

| 10A0                        | IPC1                            | 31:16         | _               | —                | —                 | IN               | T1IP<2:0>        |                 | INT1IS         | 6<1:0>          | _                 | _                     | _                     |                      | OC1IP<2:0>              | >                       | OC1IS          | 6<1:0>          | 0000          |

| IUAU                        | IPCT                            | 15:0          | _               | _                | —                 | IC               | 1IP<2:0>         |                 | IC1IS          | <1:0>           | _                 | _                     | _                     |                      | T1IP<2:0>               |                         | T1IS           | <1:0>           | 0000          |

| 10B0                        | IPC2                            | 31:16         |                 |                  | —                 | IN               | T2IP<2:0>        |                 | INT2IS         | 6<1:0>          |                   | -                     | —                     |                      | OC2IP<2:0>              | >                       | OC2IS          | 6<1:0>          | 0000          |

| IUBU                        | 1602                            | 15:0          | _               | _                | —                 | IC               | 2IP<2:0>         |                 | IC2IS          | <1:0>           | _                 | —                     | —                     |                      | T2IP<2:0>               |                         | T2IS           | <1:0>           | 0000          |

| 10C0                        | IPC3                            | 31:16         | _               | —                | —                 |                  | T3IP<2:0>        |                 | INT3IS         |                 | _                 | —                     | _                     |                      | OC3IP<2:0>              | >                       |                | 6<1:0>          | 0000          |

| 1000                        | " 00                            | 15:0          | _               |                  | —                 |                  | 3IP<2:0>         |                 | IC3IS          | -               | _                 | —                     | —                     |                      | T3IP<2:0>               |                         | T3IS<1:0>      |                 | 0000          |

| 10D0                        | IPC4                            | 31:16         | —               | —                | —                 |                  | T4IP<2:0>        |                 | INT4IS         | -               | _                 | —                     | _                     |                      | OC4IP<2:0>              | >                       | OC4IS          |                 | 0000          |

| Longer                      |                                 | 15:0          | -               | —                | —                 |                  | 4IP<2:0>         |                 | IC4IS          |                 |                   | —                     | _                     |                      | T4IP<2:0>               |                         | T4IS           | <1:0>           | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

3: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

4: This register does not have associated CLR, SET, and INV registers.

5: This bit is only implemented on devices with a CAN module.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|------------------------|-----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|--|--|

| 24.04        | U-0                    | U-0                   | R/W-y             | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |  |  |

| 31:24        | 31:24 — — PLLODIV<2:0> |                       |                   |                   | >                 | FRCDIV<2:0>           |                  |                  |  |  |

| 22.16        | U-0                    | R-0                   | R-1               | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |  |  |

| 23:16        | —                      | SOSCRDY PBDIVRDY PBDI |                   |                   | /<1:0>            | Р                     | LLMULT<2:0>      | •                |  |  |

| 15.0         | U-0                    | R-0                   | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |  |  |

| 15:8         | _                      |                       | COSC<2:0>         |                   | _                 |                       | NOSC<2:0>        |                  |  |  |

| 7.0          | R/W-0                  | R-0                   | R-0               | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |  |  |

| 7:0          | CLKLOCK                | ULOCK <sup>(1)</sup>  | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |  |  |

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

#### Legend:

bit 22

#### y = Value set from Configuration bits on POR

| •                 | •                | •                         |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-30 Unimplemented: Read as '0'

bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- SOSCRDY: Secondary Oscillator (SOSC) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

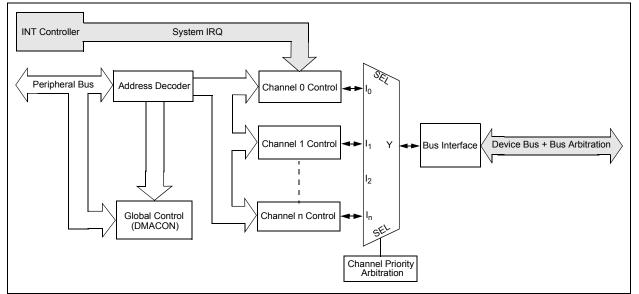

## 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

The following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

## FIGURE 9-1: DMA BLOCK DIAGRAM

#### **TABLE 9-3:** DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |       |       |       |       |       |       |      | Bi     | ts      |         |        |         |             |        |        |         |            |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|-------|-------|------|--------|---------|---------|--------|---------|-------------|--------|--------|---------|------------|

| VIITUAI AGGRESS<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7    | 22/6    | 21/5   | 20/4    | 19/3        | 18/2   | 17/1   | 16/0    | All Resets |

|                             | DCH1SSIZ                        | 31:16         | —     |       |       | —     |       |       |      | —      | _       | —       |        |         | —           | —      | —      |         | 000        |

| ,,,,,                       | Donnool2                        | 15:0          |       |       |       |       |       |       |      | CHSSIZ | 2<15:0> | •       |        |         | i           | i      | i      | ·       | 000        |

| 3180                        | DCH1DSIZ                        | 31:16         | —     | —     | —     | —     | —     | —     | —    | —      | _       | —       | —      | —       | —           | —      | _      | —       | 000        |

| 5100                        | DOITIDOIZ                       | 15:0          |       |       |       |       |       |       |      | CHDSIZ | 2<15:0> |         |        |         |             |        |        |         | 000        |

| 3190                        | DCH1SPTR                        | 31:16         | —     | _     | —     | —     | _     | —     | —    | —      | —       | —       | —      | —       | —           | —      | —      | —       | 000        |

|                             |                                 | 15:0          |       |       |       |       |       |       |      | CHSPT  | R<15:0> | -       |        |         |             |        |        |         | 000        |

| 31A0                        | DCH1DPTR                        | 31:16         | —     |       | —     | _     |       | _     | —    | —      | —       | —       | —      | _       | —           | —      | —      | —       | 000        |

|                             |                                 | 15:0          |       |       |       |       |       |       |      | CHDPT  | R<15:0> |         |        |         |             |        |        |         | 000        |

| 31B0                        | DCH1CSIZ                        | 31:16         | —     | _     | —     | —     | _     | —     | —    | -      | —       | -       | —      | —       |             |        |        | _       | 000        |

|                             |                                 | 15:0          |       |       |       |       |       |       |      | CHCSIZ | 2<15:0> | 1       |        |         |             |        |        |         | 000        |

| 31C0                        | DCH1CPTR                        | 31:16         | —     |       | _     |       |       |       |      |        | -       | —       | _      |         |             |        |        |         | 000        |

|                             |                                 | 15:0          |       |       |       |       |       |       |      | CHCPTI | ≺<15:0> |         |        |         |             |        |        |         | 000        |

| 31D0                        | DCH1DAT                         | 31:16<br>15:0 | _     | _     |       |       | _     |       |      |        | _       | —       | —      |         | <br>AT<7:0> | —      | —      | _       | 000        |

|                             |                                 | 31:16         | _     |       |       |       | _     |       |      |        |         | _       | _      | CHPDF   |             | _      |        |         | 000        |

| 31E0                        | DCH2CON                         | 15:0          |       |       |       |       |       |       |      | CHCHNS | CHEN    | CHAED   | CHCHN  | CHAEN   |             | CHEDET | CHPR   |         | 000        |

|                             |                                 | 31:16         | —     |       |       | _     |       |       |      |        | CHLIN   | CHALD   | CHCHN  | CHAIR   |             | GHEDET | CHER   | .1<1.0> | 000        |

| 31F0                        | DCH2ECON                        | 15:0          |       |       |       | CHSIR |       |       |      |        | CFORCE  | CABORT  | PATEN  | SIRQEN  | AIRQEN      | _      |        | _       | FFF        |

|                             |                                 | 31:16         | _     | _     | _     |       |       | _     | _    | _      | CHSDIE  | CHSHIE  | CHDDIE | CHDHIE  | CHBCIE      | CHCCIE | CHTAIE | CHERIE  |            |

| 3200                        | DCH2INT                         | 15:0          | _     | _     |       | _     | _     | _     | _    | _      | CHSDIE  | CHSHIF  | CHDDIE | CHDHIE  | CHBCIE      | CHCCIF | CHTAIF | CHERIF  |            |

|                             |                                 | 31:16         |       |       |       |       |       |       |      |        |         | 0.10111 | 0.1551 | 0.15111 | 0112011     | 011001 | 0      | 0.12.1  | 000        |

| 3210                        | DCH2SSA                         | 15:0          |       |       |       |       |       |       |      | CHSSA  | <31:0>  |         |        |         |             |        |        |         | 000        |

|                             |                                 | 31:16         |       |       |       |       |       |       |      |        |         |         |        |         |             |        |        |         | 000        |

| 3220                        | DCH2DSA                         | 15:0          |       |       |       |       |       |       |      | CHDSA  | <31:0>  |         |        |         |             |        |        |         | 000        |

|                             | D.01100017                      | 31:16         | _     | _     | _     | _     | _     | _     | _    | _      | _       | _       | _      | _       | _           | _      | _      | _       | 000        |

| 3230                        | DCH2SSIZ                        | 15:0          |       |       |       |       |       |       |      | CHSSIZ | 2<15:0> |         |        |         |             |        |        |         | 000        |

| 0040                        | DOUDDOIZ                        | 31:16         | _     | _     | —     | —     | —     | —     | —    | _      | —       | _       | —      | —       | —           | —      | _      | —       | 000        |

| 3240                        | DCH2DSIZ                        | 15:0          |       |       |       |       |       |       |      | CHDSIZ | 2<15:0> |         |        |         |             |        |        |         | 000        |

| 2250                        | DCH2SPTR                        | 31:16         | —     | _     | —     | —     | —     | —     | —    | —      | —       | —       | —      | —       | —           | —      | _      | —       | 000        |

| 3230                        |                                 | 15:0          |       |       |       |       |       |       |      | CHSPT  | R<15:0> |         |        |         |             |        |        |         | 000        |

| 3260                        | DCH2DPTR                        | 31:16         | _     | _     | —     | —     | —     | —     | —    | —      | _       | —       | _      | —       |             | —      |        | —       | 000        |

| 3200                        |                                 | 15:0          |       |       |       |       |       |       |      | CHDPTI | R<15:0> |         |        |         |             |        |        |         | 000        |

| 3270                        | DCH2CSIZ                        | 31:16         | _     | _     | —     | —     |       | —     | _    | —      | _       | —       | _      | _       |             | —      |        | —       | 000        |

| 5210                        | DONZOSIZ                        | 15:0          |       |       |       |       |       |       |      | CHCSIZ | 2<15:0> |         |        |         |             |        |        |         | 000        |

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

## PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | -                 | -                 | -                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | -                 | -                 | -                 | -                 |                  | —                |

| 7:0          | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | _                 | _                 | USBSIDL           | USBSIDL           |                   | _                | UASUSPND         |

### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test enabled

- 0 = Eye-Pattern Test disabled

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 3 LSDEV: Low-Speed Device Enable bit

- 1 = USB module operates in Low-Speed Device mode only

- 0 = USB module operates in OTG, Host, or Full-Speed Device mode

- bit 2-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 31.24        | _                    | —                 | —                 | —                 | —                        | _                 | -                | _                |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 23.10        | —                    | _                 | —                 | —                 | —                        | —                 | _                | —                |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | SPISGNEXT            | _                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR           |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0            |

| 7:0          | AUDEN <sup>(1)</sup> |                   |                   |                   | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | )<1:0>(1,2)      |

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| ı' |

|----|

| ļ  |

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extened

#### bit 14-13 Unimplemented: Read as '0'

- bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit 1 = Frame Error overflow generates error events 0 = Frame Error does not generate error events bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit 1 = Receive overflow generates error events 0 = Receive overflow does not generate error events bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit 1 = Transmit Underrun Generates Error Events 0 = Transmit Underrun Does Not Generates Error Events bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions) 1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data 0 = A ROV is a critical error which stop SPI operation bit 8 IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions) 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty 0 = A TUR is a critical error which stop SPI operation AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup> bit 7 1 = Audio protocol enabled 0 = Audio protocol disabled bit 6-5 Unimplemented: Read as '0' AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup> bit 3 1 = Audio data is mono (Each data word is transmitted on both left and right channels) 0 = Audio data is stereo bit 2 Unimplemented: Read as '0' AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup> bit 1-0 11 = PCM/DSP mode 10 = Right Justified mode 01 = Left Justified mode  $00 = I^2 S \mod I$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

#### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        | —                 | —                 | —                 | RXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | —                 | —                 | —                 |                   | Tک                | (BUFELM<4:(       | )>               |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |  |

| 15:8         |                   | —                 | —                 | FRMERR            | SPIBUSY           |                   | _                | SPITUR           |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            | _                 | SPITBF           | SPIRBF           |  |  |

| Legend:           | C = Clearable bit | HS = Set in hardware               |                    |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 **SPITUR:** Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

- This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

- This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 SPIRBE: RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR ≠ SWPTR)

- bit 4 Unimplemented: Read as '0'

NOTES:

## TABLE 22-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | 0             |       |                                              |  |  |  |  |         | Bi         | ts       |          |  |            |  |  | ú            |

|-----------------------------|------------------|---------------|-------|----------------------------------------------|--|--|--|--|---------|------------|----------|----------|--|------------|--|--|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 |                                              |  |  |  |  |         |            |          |          |  | All Resets |  |  |              |

| 9100                        | ADC1BUF9         | 31:16<br>15:0 |       | ADC Result Word 9 (ADC1BUF9<31:0>)           |  |  |  |  |         |            |          |          |  |            |  |  |              |

| 9110                        | ADC1BUFA         | 31:16<br>15:0 |       | ADC Result Word A (ADC1BUFA<31:0>)           |  |  |  |  |         |            |          |          |  |            |  |  |              |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |       | ADC Result Word B (ADC1BUFB<31:0>) 0000 0000 |  |  |  |  |         |            |          |          |  |            |  |  |              |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |       |                                              |  |  |  |  | ADC Res | ult Word C | (ADC1BUF | C<31:0>) |  |            |  |  | 0000         |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |       | ADC Result Word D (ADC1BUFD<31:0>) 0000 0000 |  |  |  |  |         |            |          |          |  |            |  |  |              |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 |       | ADC Result Word E (ADC1BUFE<31:0>) 0000      |  |  |  |  |         |            |          |          |  |            |  |  |              |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |       |                                              |  |  |  |  | ADC Res | ult Word F | (ADC1BUF | F<31:0>) |  |            |  |  | 0000<br>0000 |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for details.

2: For 64-pin devices, the MSB of these bits is not available.

3: For 64-pin devices, only the CSSL30:CSSL0 bits are available.

## TABLE 23-1: CAN1 REGISTER SUMMARY (CONTINUED)

| ess                        |                                 | 6             |       |        |       |       |       | ,         |          | Bits      | ;      |        |        |       |          |            |          |                |            |

|----------------------------|---------------------------------|---------------|-------|--------|-------|-------|-------|-----------|----------|-----------|--------|--------|--------|-------|----------|------------|----------|----------------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14  | 29/13 | 28/12 | 27/11 | 26/10     | 25/9     | 24/8      | 23/7   | 22/6   | 21/5   | 20/4  | 19/3     | 18/2       | 17/1     | 16/0           | All Resets |

| B340                       | C1FIFOBA                        | 31:16<br>15:0 |       |        |       |       |       |           |          | C1FIFOBA  | <31:0> |        |        |       |          |            |          |                | 0000       |

| B350                       | C1FIFOCONn                      | 31:16         |       | _      |       |       | _     | —         | _        | _         |        | —      |        |       | -        | SIZE<4:0>  | -        |                | 0000       |

| D330                       | (n = 0-15)                      | 15:0          | —     | FRESET | UINC  | DONLY | _     | —         | _        | —         | TXEN   | TXABAT | TXLARB | TXERR | TXREQ    | RTREN      | TXPRI    | <1:0>          | 0000       |

| B360                       | C1FIFOINTn                      | 31:16         | -     | -      | —     | —     | —     | TXNFULLIE | TXHALFIE | TXEMPTYIE | —      | —      | -      | —     | RXOVFLIE | RXFULLIE   | RXHALFIE | RXN<br>EMPTYIE | 0000       |

| D300                       | (n = 0-15)                      | 15:0          | _     | -      |       | -     | _     | TXNFULLIF | TXHALFIF | TXEMPTYIF | _      | —      | -      | _     | RXOVFLIF | RXFULLIF   | RXHALFIF | RXN<br>EMPTYIF | 0000       |

| B370                       | C1FIFOUAn                       | 31:16         |       |        |       |       |       |           |          | C1FIFOUA  | -21:05 |        |        |       |          |            |          |                | 0000       |

| B370                       | (n = 0-15)                      | 15:0          |       |        |       |       |       |           |          | CIFIFUUA  | ~31.02 |        |        |       |          |            |          |                | 0000       |

| B380                       | C1FIFOCIn                       | 31:16         | _     | _      | _     | _     | -     | _         | -        | _         | _      | _      | _      |       | _        | _          | _        | -              | 0000       |

| 6300                       | (n = 0-15)                      | 15:0          | —     | —      | _     | _     | _     | _         | _        | _         | _      | —      | —      |       | C1       | FIFOCIn<4: | 0>       |                | 0000       |

Legend: Note 1 x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more 1: information.

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24     | R/W-0             | R/W-0 R/W-0       |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     | FLTEN3            | MSEL:             | 3<1:0>            | FSEL3<4:0>        |                   |                   |                  |                  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | FLTEN2            | MSEL              | 2<1:0>            | FSEL2<4:0>        |                   |                   |                  |                  |  |  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.0      | FLTEN1            | MSEL              | 1<1:0>            | FSEL1<4:0>        |                   |                   |                  |                  |  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0       | FLTEN0 MSEL0<1:0> |                   |                   | FSEL0<4:0>        |                   |                   |                  |                  |  |  |  |

## REGISTER 23-10: C1FLTCON0: CAN FILTER CONTROL REGISTER 0

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN3: Filter 3 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL3<1:0>: Filter 3 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                    |

| bit 28-24 | FSEL3<4:0>: FIFO Selection bits<br>11111 = Reserved<br>10000 = Reserved<br>01111 = Message matching filter is stored in FIFO buffer 15<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN2: Filter 2 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                       |

| bit 22-21 | MSEL2<1:0>: Filter 2 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                    |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## 24.1 Control Registers

## TABLE 24-1: COMPARATOR REGISTER MAP

| ess                         |                                             |           |       | Bits  |       |       |       |       |      |      |      |        |      |      |      |       |       |       |            |

|-----------------------------|---------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | (BF80_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Resets |

| 4000                        | CM1CON                                      | 31:16     | _     | _     | —     | —     | —     | _     | —    | —    | -    | —      | —    | —    | _    | —     | —     | _     | 0000       |

| A000                        | CIVITCON                                    | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4010                        | CM2CON                                      | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| AUTU                        | CIVIZCON                                    | 15:0      | ON    | COE   | CPOL  | —     |       | —     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4020                        | CM3CON                                      | 31:16     | —     | -     | —     | —     |       | —     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A020                        | CIVISCON                                    | 15:0      | ON    | COE   | CPOL  | —     |       | —     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| A060                        | CMSTAT                                      | 31:16     | —     | -     | —     | —     |       | —     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A000                        | CIVISTAT                                    | 15:0      | —     | _     | SIDL  | _     | _     |       |      | _    | —    |        | —    | —    | —    | C3OUT | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

NOTES:

## PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

NOTES:

| DC CHARACT       | ERISTICS               |               | (unless oth  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |                 |               |  |  |  |  |  |

|------------------|------------------------|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--|--|--|--|--|

| Parameter<br>No. | Typical <sup>(2)</sup> | Max.          | Units        | Units Conditions                                                                                                                                                                                                                                                                  |                 |               |  |  |  |  |  |

| Idle Current (II | DLE): Core Of          | f, Clock on E | Base Current | (Notes 1, 4)                                                                                                                                                                                                                                                                      |                 |               |  |  |  |  |  |

| DC30a            | 1.5                    | 5             | mA           | 4 MHz (Note 3)                                                                                                                                                                                                                                                                    |                 |               |  |  |  |  |  |

| DC31a            | 3                      | 8             | mA           |                                                                                                                                                                                                                                                                                   | 10 MHz          |               |  |  |  |  |  |

| DC32a            | 5                      | 12            | mA           |                                                                                                                                                                                                                                                                                   | 20 MHz (Note 3) |               |  |  |  |  |  |

| DC33a            | 6.5                    | 15            | mA           |                                                                                                                                                                                                                                                                                   | 30 MHz (Note 3) |               |  |  |  |  |  |

| DC34a            | 8                      | 20            | mA           | 40 MHz                                                                                                                                                                                                                                                                            |                 |               |  |  |  |  |  |

| DC37a            | 75                     | 100           | μA           | -40°C                                                                                                                                                                                                                                                                             |                 | LPRC (31 kHz) |  |  |  |  |  |

| DC37b            | 180                    | 250           | μA           | +25°C 3.3V (No                                                                                                                                                                                                                                                                    |                 |               |  |  |  |  |  |

| DC37c            | 280                    | 380           | μA           | +85°C                                                                                                                                                                                                                                                                             |                 |               |  |  |  |  |  |

### TABLE 31-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** The test conditions for IIDLE current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1  $\,$

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: IIDLE electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

## PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

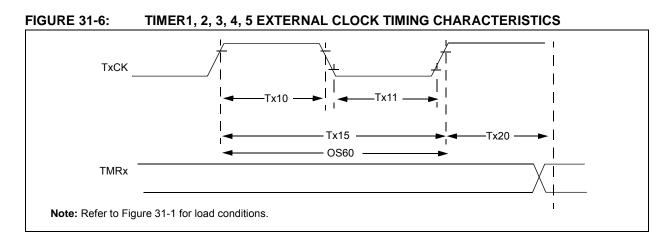

## TABLE 31-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA        | ARACTERIS                       | TICS <sup>(1)</sup>                                          |                                                                                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                                            |         |      |                               |                               |  |  |  |

|---------------|---------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------|------|-------------------------------|-------------------------------|--|--|--|

| Param.<br>No. | Symbol                          | Charac                                                       | teristics <sup>(2)</sup>                                                                                |                                                                                                                                                                                                                                                                                       | Min.                                       | Typical | Max. | Units                         | Conditions                    |  |  |  |

| TA10          | High Time with prescale         |                                                              |                                                                                                         | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                                                                                                     | —                                          | —       | ns   | Must also meet parameter TA15 |                               |  |  |  |

|               |                                 |                                                              | Asynchronous, with prescaler                                                                            |                                                                                                                                                                                                                                                                                       | 10                                         | —       | _    | ns                            | —                             |  |  |  |

| TA11          | T⊤xL                            | TxCK<br>Low Time                                             | Synchronous, with prescaler                                                                             |                                                                                                                                                                                                                                                                                       | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns          | —       | _    | ns                            | Must also meet parameter TA15 |  |  |  |

|               | Asynchronous,<br>with prescaler |                                                              |                                                                                                         | 10                                                                                                                                                                                                                                                                                    | _                                          | _       | ns   | —                             |                               |  |  |  |

| TA15          | ΤτχΡ                            | TxCK<br>Input Period                                         | Synchronou with presca                                                                                  |                                                                                                                                                                                                                                                                                       | [(Greater of 25 ns or<br>2 Трв)/N] + 30 ns | —       | —    | ns                            | VDD > 2.7V                    |  |  |  |

|               |                                 |                                                              |                                                                                                         |                                                                                                                                                                                                                                                                                       | [(Greater of 25 ns or<br>2 TPB)/N] + 50 ns | -       | —    | ns                            | VDD < 2.7V                    |  |  |  |

|               |                                 |                                                              | Asynchrono<br>with presca                                                                               |                                                                                                                                                                                                                                                                                       | 20                                         | —       | —    | ns                            | VDD > 2.7V<br>(Note 3)        |  |  |  |

|               |                                 |                                                              |                                                                                                         |                                                                                                                                                                                                                                                                                       | 50                                         | -       | _    | ns                            | VDD < 2.7V<br>(Note 3)        |  |  |  |

| OS60          | FT1                             | Input Freque<br>(oscillator en                               | OSC1/T1CK Oscillator<br>nput Frequency Range<br>oscillator enabled by setting<br>he TCS (T1CON<1>) bit) |                                                                                                                                                                                                                                                                                       | 32                                         | —       | 100  | kHz                           | —                             |  |  |  |

| TA20          | TCKEXTMRL                       | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                                                                                         | K                                                                                                                                                                                                                                                                                     |                                            |         | 1    | Трв                           | —                             |  |  |  |

**Note 1:** Timer1 is a Type A timer.

**2:** This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

## TABLE 31-39: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHA        |         | ISTICS                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |      |       |            |  |  |  |

|---------------|---------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                                | Тур.  | Max. | Units | Conditions |  |  |  |

| PM11          | Twr     | PMWR Pulse Width                                                          | —                                                                                                                                                                                                                                                                                   | 1 Трв | _    | _     | _          |  |  |  |

| PM12          | Tdvsu   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) | —                                                                                                                                                                                                                                                                                   | 2 Трв | _    | _     | _          |  |  |  |

| PM13          | Tdvhold | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             | —                                                                                                                                                                                                                                                                                   | 1 Трв | _    |       | —          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

### TABLE 31-40: OTG ELECTRICAL SPECIFICATIONS

| AC CHA        | RACTERI | STICS                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |                                                                                   |  |  |  |

|---------------|---------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions                                                                        |  |  |  |

| USB313        | VUSB3V3 | USB Voltage                       | 3.0                                                                                                                                                                                                                                                                                   |      | 3.6  | V     | Voltage on VUSB3V3<br>must be in this range<br>for proper USB<br>operation        |  |  |  |

| USB315        | VILUSB  | Input Low Voltage for USB Buffer  | —                                                                                                                                                                                                                                                                                     | —    | 0.8  | V     | —                                                                                 |  |  |  |

| USB316        | VIHUSB  | Input High Voltage for USB Buffer | 2.0                                                                                                                                                                                                                                                                                   | —    | _    | V     | —                                                                                 |  |  |  |

| USB318        | VDIFS   | Differential Input Sensitivity    | _                                                                                                                                                                                                                                                                                     | _    | 0.2  | V     | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |  |  |  |

| USB319        | VCM     | Differential Common Mode Range    | 0.8                                                                                                                                                                                                                                                                                   |      | 2.5  | V     | —                                                                                 |  |  |  |

| USB320        | Zout    | Driver Output Impedance           | 28.0                                                                                                                                                                                                                                                                                  | —    | 44.0 | Ω     | —                                                                                 |  |  |  |

| USB321        | Vol     | Voltage Output Low                | 0.0                                                                                                                                                                                                                                                                                   | _    | 0.3  | V     | 1.425 kΩ load<br>connected to VUSB3V3                                             |  |  |  |

| USB322        | Vон     | Voltage Output High               | 2.8                                                                                                                                                                                                                                                                                   | _    | 3.6  | V     | 1.425 kΩ load connected to ground                                                 |  |  |  |

| Note | 1: | These parameters are characterized, but not tested in manufacturing. |

|------|----|----------------------------------------------------------------------|

|------|----|----------------------------------------------------------------------|

## 32.2 AC Characteristics and Timing Parameters