Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Betano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx550f256h-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4: PIN NAMES FOR 100-PIN GENERAL PURPOSE DEVICES

## **100-PIN TQFP (TOP VIEW)**

## PIC32MX130F128L PIC32MX150F256L PIC32MX170F512L

100

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                   |

|-------|---------------------------------------|-------|---------------------------------|

| 1     | AN28/RG15                             | 36    | Vss                             |

| 2     | Vdd                                   | 37    | VDD                             |

| 3     | AN22/RPE5/PMD5/RE5                    | 38    | TCK/CTED2/RA1                   |

| 4     | AN23/PMD6/RE6                         | 39    | AN34/RPF13/SCK3/RF13            |

| 5     | AN27/PMD7/RE7                         | 40    | AN35/RPF12/RF12                 |

| 6     | AN29/RPC1/RC1                         | 41    | AN12/PMA11/RB12                 |

| 7     | AN30/RPC2/RC2                         | 42    | AN13/PMA10/RB13                 |

| 8     | AN31/RPC3/RC3                         | 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 9     | RPC4/CTED7/RC4                        | 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 10    | AN16/C1IND/RPG6/SCK2/PMA5/RG6         | 45    | Vss                             |

| 11    | AN17/C1INC/RPG7/PMA4/RG7              | 46    | VDD                             |

| 12    | AN18/C2IND/RPG8/PMA3/RG8              | 47    | AN36/RPD14/RD14                 |

| 13    | MCLR                                  | 48    | AN37/RPD15/SCK4/RD15            |

| 14    | AN19/C2INC/RPG9/PMA2/RG9              | 49    | RPF4/PMA9/RF4                   |

| 15    | Vss                                   | 50    | RPF5/PMA8/RF5                   |

| 16    | Vdd                                   | 51    | RPF3/RF3                        |

| 17    | TMS/CTED1/RA0                         | 52    | AN38/RPF2/RF2                   |

| 18    | AN32/RPE8/RE8                         | 53    | AN39/RPF8/RF8                   |

| 19    | AN33/RPE9/RE9                         | 54    | RPF7/RF7                        |

| 20    | AN5/C1INA/RPB5/RB5                    | 55    | RPF6/SCK1/INT0/RF6              |

| 21    | AN4/C1INB/RB4                         | 56    | SDA1/RG3                        |

| 22    | PGED3/AN3/C2INA/RPB3/RB3              | 57    | SCL1/RG2                        |

| 23    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 | 58    | SCL2/RA2                        |

| 24    | PGEC1/AN1/RPB1/CTED12/RB1             | 59    | SDA2/RA3                        |

| 25    | PGED1/AN0/RPB0/RB0                    | 60    | TDI/CTED9/RA4                   |

| 26    | PGEC2/AN6/RPB6/RB6                    | 61    | TDO/RA5                         |

| 27    | PGED2/AN7/RPB7/CTED3/RB7              | 62    | VDD                             |

| 28    | VREF-/PMA7/RA9                        | 63    | OSC1/CLKI/RC12                  |

| 29    | VREF+/PMA6/RA10                       | 64    | OSC2/CLKO/RC15                  |

| 30    | AVdd                                  | 65    | Vss                             |

| 31    | AVss                                  | 66    | RPA14/RA14                      |

| 32    | AN8/RPB8/CTED10/RB8                   | 67    | RPA15/RA15                      |

| 33    | AN9/RPB9/CTED4/RB9                    | 68    | RPD8/RTCC/RD8                   |

| 34    | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 69    | RPD9/RD9                        |

| 35    | AN11/PMA12/RB11                       | 70    | RPD10/PMA15/RD10                |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| IABLE 1-1 |                        | umber           |             | (•             |                                                                                                                                                                                        |  |  |  |

|-----------|------------------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name  | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                            |  |  |  |

| AN36      |                        | 47              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| AN37      | _                      | 48              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| AN38      | _                      | 52              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| AN39      | _                      | 53              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| AN40      | _                      | 79              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| AN41      | _                      | 80              | I           | Analog         | Analog input channels                                                                                                                                                                  |  |  |  |

| AN42      | _                      | 83              | I           | Analog         | Analog input channels.                                                                                                                                                                 |  |  |  |

| AN43      |                        | 84              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| AN44      | _                      | 87              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| AN45      | _                      | 88              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| AN46      | _                      | 93              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| AN47      | _                      | 94              | I           | Analog         |                                                                                                                                                                                        |  |  |  |

| CLKI      | 39                     | 63              | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                 |  |  |  |

| CLKO      | 40                     | 64              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with the OSC2 pin function. |  |  |  |

| OSC1      | 39                     | 63              | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                        |  |  |  |

| OSC2      | 40                     | 64              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                               |  |  |  |

| SOSCI     | 47                     | 73              | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                         |  |  |  |

| SOSCO     | 48                     | 74              | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                        |  |  |  |

| IC1       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |  |  |  |

| IC2       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |  |  |  |

| IC3       | PPS                    | PPS             | I           | ST             | Capture Input 1-5                                                                                                                                                                      |  |  |  |

| IC4       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |  |  |  |

| IC5       | PPS                    | PPS             | I           | ST             |                                                                                                                                                                                        |  |  |  |

| OC1       | PPS                    | PPS             | 0           | ST             | Output Compare Output 1                                                                                                                                                                |  |  |  |

| OC2       | PPS                    | PPS             | 0           | ST             | Output Compare Output 2                                                                                                                                                                |  |  |  |

| OC3       | PPS                    | PPS             | 0           | ST             | Output Compare Output 3                                                                                                                                                                |  |  |  |

| OC4       | PPS                    | PPS             | 0           | ST             | Output Compare Output 4                                                                                                                                                                |  |  |  |

| OC5       | PPS                    | PPS             | 0           | ST             | Output Compare Output 5                                                                                                                                                                |  |  |  |

| OCFA      | PPS                    | PPS             | Ι           | ST             | Output Compare Fault A Input                                                                                                                                                           |  |  |  |

| OCFB      | 30                     | 44              | I           | ST             | Output Compare Fault B Input                                                                                                                                                           |  |  |  |

|           |                        | IOS compati     |             |                | Analog = Analog input I = Input O = Output                                                                                                                                             |  |  |  |

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer P = P

P = Power

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

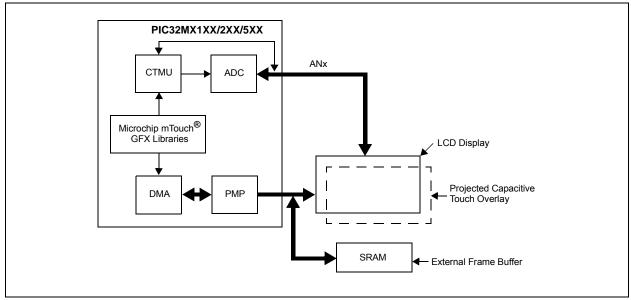

## 2.10 Typical Application Connection Examples

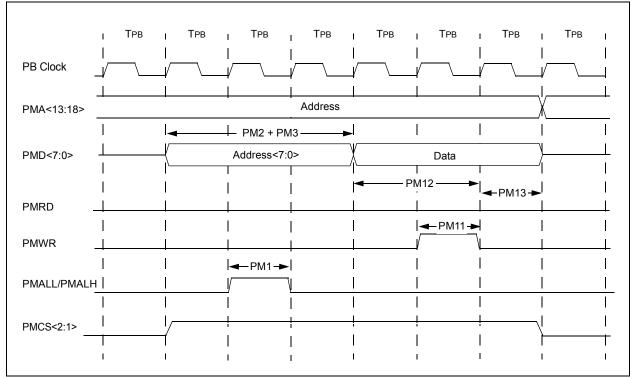

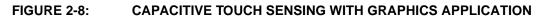

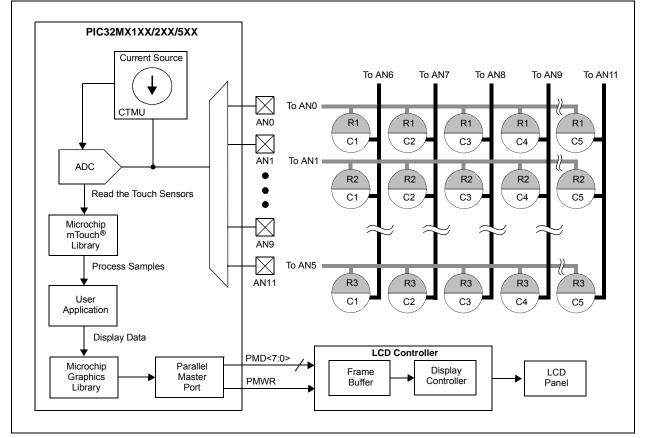

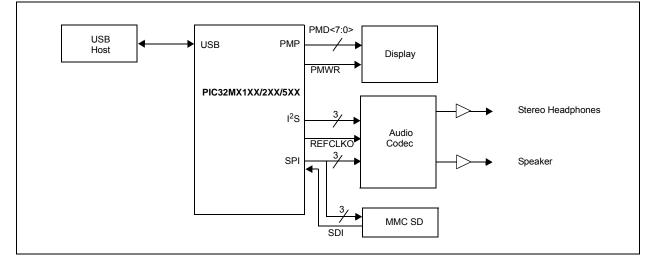

Examples of typical application connections are shown in Figure 2-8, Figure 2-9, and Figure 2-10.

FIGURE 2-9: AUDIO PLAYBACK APPLICATION

# FIGURE 2-10: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

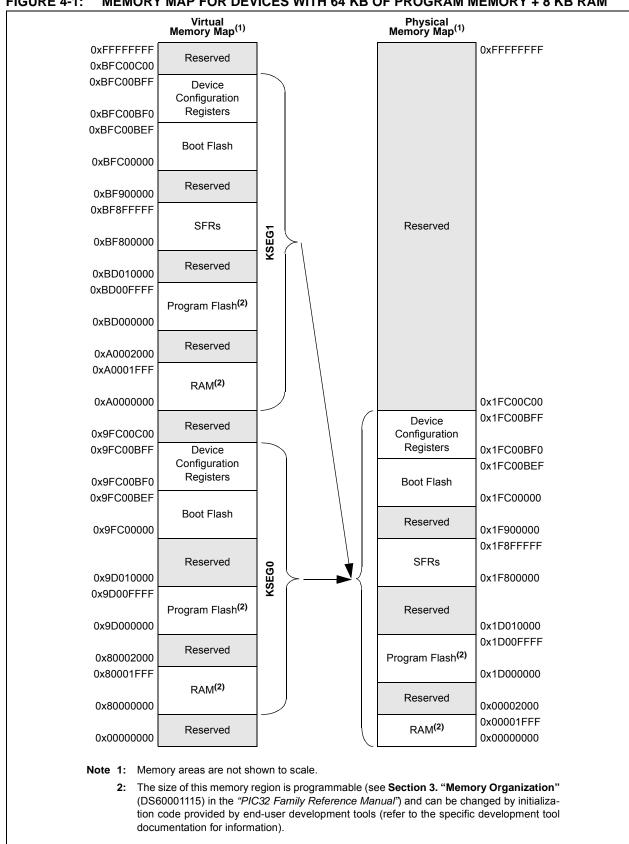

## FIGURE 4-1: MEMORY MAP FOR DEVICES WITH 64 KB OF PROGRAM MEMORY + 8 KB RAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS9             | IFS8             |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1             | IFS0             |  |  |  |  |

## REGISTER 5-4: IFSx: INTERRUPT FLAG STATUS REGISTER

## Legend:

| 5                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 5-1 for the exact bit definitions.

## REGISTER 5-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IEC31-IEC0: Interrupt Enable bits

- 1 = Interrupt is enabled

- 0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 5-1 for the exact bit definitions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   | ROTRIM<8:1>       |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | ROTRIM<0>         |                   | _                 | _                 | —                 |                   | —                | _                |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | —                 | _                 | _                 | _                 | _                 | —                | _                |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          |                   | _                 | _                 | _                 | _                 | _                 |                  | —                |  |  |  |  |

## REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

**Note:** While the ON bit (REFOCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

| LEGISTER 5-10. DETACOIZ. DINA CHANNEL & CELE-SIZE REGISTER |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

|------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range                                               | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 01.04                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24                                                      |                   | —                 | -                 | -                 | —                 | —                 | -                | —                |  |  |

| 22:16                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16                                                      | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |

| 45.0                                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8                                                       | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0                                                        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0                                                        |                   |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |  |  |

## REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

## bit 31-16 Unimplemented: Read as '0'

## bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

1111111111111111 = 65,535 bytes transferred on an event

## **REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | -                 | _                 |                   |                  | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                          |                      |                    |

|-------------------|--------------------------|----------------------|--------------------|

| R = Readable bit  | U = Unimplemented bit, r | ead as '0'           |                    |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

## Note: When in Pattern Detect mode, this register is reset on a pattern detect.

## TABLE 11-6: PORTC REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |           |           |           |           |       |       |      | Bits |      |      |      |      |         |         |         |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|------|---------|---------|---------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3    | 18/2    | 17/1    | 16/0 | All<br>Resets |

| 6200                        | ANSELC                          | 31:16     | _         | —         | —         | _         | —     | -     |      |      | _    | —    | _    |      | —       |         | —       | _    | 0000          |

| 0200                        | /                               | 15:0      | —         | —         | —         | —         | —     | —     | —    | _    | —    | _    | —    | _    | ANSELC3 | ANSELC2 | ANSELC1 | —    | 000E          |

| 6210                        | TRISC                           | 31:16     |           | —         | —         | —         | _     | _     | _    |      | _    |      | —    | _    | _       | _       | —       | _    | 0000          |

| 02.0                        |                                 | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | —     | —     | —    | _    | —    | _    | —    | _    | —       | —       | —       | —    | F000          |

| 6220                        | PORTC                           | 31:16     | —         | —         | —         | —         | _     | _     | _    | _    | —    | _    | —    | _    | —       | _       | —       |      | 0000          |

| 0220                        | 1 on to                         | 15:0      | RC15      | RC14      | RC13      | RC12      | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | xxxx          |

| 6230                        | LATC                            | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 0200                        | Ento                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | xxxx          |

| 6240                        | ODCC                            | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 02.10                       | 0200                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 6250                        | CNPUC                           | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 0200                        |                                 | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 6260                        | CNPDC                           | 31:16     |           | —         | —         | —         | —     | _     | _    | _    | —    | —    | —    |      | —       | _       | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | _    | 0000          |

| 6270                        | CNCONC                          | 31:16     |           | _         |           |           |       |       | _    |      | —    | _    | —    |      | —       |         | —       |      | 0000          |

| 0270                        | oncono                          | 15:0      | ON        |           | SIDL      |           |       |       | _    |      | —    | _    | —    |      | —       |         | —       |      | 0000          |

| 6280                        | CNENC                           | 31:16     |           |           |           |           |       |       | _    |      | —    | _    | —    |      | —       |         | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | —     | _     | _    |      | —    |      | —    | _    | —       |         | —       | _    | 0000          |

| 6200                        | CNSTATC                         | 31:16     | _         | —         | —         | _         | _     |       |      |      | -    | —    | -    |      | —       |         | —       | —    | 0000          |

| 0290                        | GNOTAIC                         | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     |       |      |      | -    | _    |      |      | _       |         | —       | _    | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

## TABLE 11-9: PORTE REGISTER MAP FOR 100-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |              | E            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6400                        | ANSELE                          | 31:16     | _     | _     | _     |       | _     | _     | —            | -            |              | _            | —            | _            | —            | —            | —            | _            | 0000          |

| 0400                        | ANOLLL                          | 15:0      | _     | _     | —     | _     | _     | _     | ANSELE9      | ANSELE8      | ANSELE7      | ANSELE6      | ANSELE5      | ANSELE4      | —            | ANSELE2      | ANSELE1      | ANSELE0      | 03F7          |

| 6410                        | TRISE                           | 31:16     | _     | —     | _     | —     | —     | _     | _            | _            | _            | _            |              | _            | —            | _            | —            | —            | 0000          |

| 0410                        | INIOL                           | 15:0      | _     | _     | —     | _     | _     | _     | TRISE9       | TRISE8       | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | 03FF          |

| 6420                        | PORTE                           | 31:16     | —     | —     | —     | —     | —     | _     | —            | _            | _            |              |              |              | —            | —            | —            | —            | 0000          |

| 0420                        | TORTE                           | 15:0      | —     | —     | —     | —     | —     | _     | RE9          | RE8          | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 6440                        | LATE                            | 31:16     | —     | —     | —     | —     | —     |       | —            | _            |              |              |              |              |              |              | —            | —            | 0000          |

| 0440                        | L/ (1 L                         | 15:0      | —     | —     | —     | —     | —     |       | LATE9        | LATE8        | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | xxxx          |

| 6440                        | ODCE                            | 31:16     | —     | —     | —     | —     | —     |       | —            | _            |              |              |              |              |              |              | —            | —            | 0000          |

| 0440                        | ODOL                            | 15:0      | —     | —     | —     | —     | —     |       | ODCE9        | ODCE8        | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 6450                        | CNPUE                           | 31:16     | —     | —     | —     | —     | —     |       | —            | _            |              |              |              |              |              |              | —            | —            | 0000          |

| 0100                        |                                 | 15:0      | —     | —     | —     | —     | —     | —     | CNPUE9       | CNPUE8       | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPDE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 6460                        | CNPDE                           | 31:16     | —     | —     | —     | —     | —     | —     | —            | —            | —            | —            |              | —            | —            | —            | —            | —            | 0000          |

| 0100                        | ON DE                           | 15:0      | —     | —     | —     | —     | —     | —     | CNPDE9       | CNPDE8       | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

| 6470                        | CNCONE                          | 31:16     | —     | —     | —     | —     | —     | —     | —            | —            | —            | _            |              | _            | —            | —            | —            | —            | 0000          |

| 0110                        | ONCOME                          | 15:0      | ON    | —     | SIDL  | —     | —     | —     | —            | —            | —            | _            |              | _            | —            | —            | —            | —            | 0000          |

| 6480                        | CNENE                           | 31:16     | —     | —     | —     | —     | —     | —     | —            | —            | —            | —            |              | —            | —            | —            | —            | —            | 0000          |

| 0400                        | ONLINE                          | 15:0      | —     | —     | —     | —     | —     |       | CNIEE9       | CNIEE8       | CNIEE7       | CNIEE6       | CNIEE5       | CNIEE4       | CNIEE3       | CNIEE2       | CNIEE1       | CNIEE0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | —     | —     | _     | —            | —            | _            | _            |              | _            |              |              | —            | —            | 0000          |

| 6490                        | CNSTATE                         | 15:0      | —     | —     | —     | —     | —     | -     | CN<br>STATE9 | CN<br>STATE8 | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

#### **Control Registers** 13.2

## TABLE 13-1: TIMER2 THROUGH TIMER5 REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |             | Bi   | its    |      |           |      |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|-------------|------|--------|------|-----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9        | 24/8 | 23/7   | 22/6 | 21/5      | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16     |       | —     | _     | _     | —     | -     | —           | -    | _      | l    | _         | _    | —    | —    | _    | _    | 0000       |

| 0000                        | 12001                           | 15:0      | ON    | —     | SIDL  | _     | —     | _     | _           | _    | TGATE  | -    | TCKPS<2:0 | >    | T32  | _    | TCS  | _    | 0000       |

| 0810                        | TMR2                            | 31:16     | _     | —     | —     | —     | —     | —     | —           | —    | —      | _    | —         | _    | —    | —    | —    | _    | 0000       |

| 0010                        | TIVITYZ                         | 15:0      |       | -     |       |       | -     |       |             | TMR2 | <15:0> |      |           |      |      |      |      |      | 0000       |

| 0820                        | PR2                             | 31:16     | _     | —     | —     | —     | —     | —     | —           | —    | —      | _    | —         | _    | —    | —    | —    | _    | 0000       |

| 0020                        | 1112                            | 15:0      |       |       |       |       |       |       |             | PR2< | 15:0>  |      |           |      |      |      |      |      | FFFF       |

| 0400                        | T3CON                           | 31:16     | _     | _     | —     | _     |       | _     | —           | _    | —      |      | —         | _    | —    |      | _    |      | 0000       |

| 0/100                       | 10001                           | 15:0      | ON    |       | SIDL  | _     |       | _     | —           | _    | TGATE  | -    | TCKPS<2:0 | >    | —    |      | TCS  |      | 0000       |

| 0A10                        | TMR3                            | 31:16     | —     | —     | —     | —     | —     | —     | —           | —    | —      | —    | —         | —    | —    | —    | —    | —    | 0000       |

| 0/110                       | 1111110                         | 15:0      |       |       |       |       |       |       |             | TMR3 | <15:0> |      |           |      |      |      |      |      | 0000       |

| 0A20                        | PR3                             | 31:16     |       | _     | —     | —     |       | —     | —           | —    | —      | —    | —         | _    | —    | —    | —    | —    | 0000       |

| 0/ 120                      |                                 | 15:0      |       |       |       |       |       |       |             | PR3< | 15:0>  |      |           |      |      |      |      |      | FFFF       |

| 0C00                        | T4CON                           | 31:16     | _     |       | —     | _     |       | _     | _           | _    | —      |      | —         | _    | -    |      | _    |      | 0000       |

|                             |                                 | 15:0      | ON    | —     | SIDL  | _     | —     | _     | _           | _    | TGATE  |      | TCKPS<2:0 | >    | T32  | —    | TCS  |      | 0000       |

| 0C10                        | TMR4                            | 31:16     | _     | —     | —     | —     | —     | —     | —           | —    | —      | _    | —         | —    | —    | —    | —    |      | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |             | TMR4 | <15:0> |      |           |      |      |      |      |      | 0000       |

| 0C20                        | PR4                             | 31:16     | _     | —     | —     | —     | —     | —     | —           | —    | —      | —    | —         | —    | —    | —    | —    | _    | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |             | PR4< | 15:0>  |      |           |      |      |      |      |      | FFFF       |

| 0E00                        | T5CON                           | 31:16     | -     | —     | -     | _     | —     | _     | _           | _    | _      |      | —         | _    | —    | —    | -    | _    | 0000       |

|                             |                                 | 15:0      | ON    | —     | SIDL  | _     | _     | _     | _           | _    | TGATE  |      | TCKPS<2:0 | >    | _    | _    | TCS  |      | 0000       |

| 0E10                        | TMR5                            | 31:16     |       | —     | _     | —     | _     | _     | —           | -    | —      | _    | _         | _    | _    | _    | —    | _    | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |             | TMR5 | <15:0> |      |           |      |      |      |      |      | 0000       |

| 0E20                        | PR5                             | 31:16     |       | —     | —     | _     | —     | —     | —           | _    | —      | _    | —         | _    | —    | —    | —    | —    | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       | ara ahaum i | PR5< |        |      |           |      |      |      |      |      | FFFF       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

## REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        | —                 | —                 | —                 |                   | R                 | KBUFELM<4:(       | )>               |                  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        | —                 | —                 | —                 |                   | Tک                | (BUFELM<4:(       | )>               |                  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |

| 15:8         |                   | —                 | —                 | FRMERR            | SPIBUSY           |                   | _                | SPITUR           |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            | _                 | SPITBF           | SPIRBF           |

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 **SPITUR:** Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

- This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

- This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 SPIRBE: RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR ≠ SWPTR)

- bit 4 Unimplemented: Read as '0'

| REGIST  | ER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8   | <ul> <li>TRMT: Transmit Shift Register is Empty bit (read-only)</li> <li>1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer</li> </ul>                                                                                                                                  |

| bit 7-6 | <pre>URXISEL&lt;1:0&gt;: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 =Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)</pre> |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                   |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                                                                                                                                                     |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                                            |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                                                         |

| bit 1   | <b>OERR:</b> Receive Buffer Overrun Error Status bit.<br>This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.<br>1 = Receive buffer has overflowed                                                                                                                                                                                     |

|         | 0 = Receive buffer has not overflowed                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 0   | <ul> <li>URXDA: Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                    |

## 20.1 Control Registers

## TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| model         model <t< th=""><th>ess</th><th></th><th>9</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th>В</th><th>its</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></t<>                                                                                                                                                                                                                               | ess                         |                                 | 9         |         |         |            |       |        |        |        | В      | its        |         |      |       |        |      |       |       |            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|-----------|---------|---------|------------|-------|--------|--------|--------|--------|------------|---------|------|-------|--------|------|-------|-------|------------|

| 7000         PMCON         15.0         ON         —         SIDL         ADRUX<1:0>         PMPTL         PTWEN         PTREN         CSF<1:0>         ALP         CS2P         CS1P         —         WRSP         RDSP         0000           7010         PMMODE         15.0         BUSY         IRQM<10>         INCM<10>         MODE16         MODE10         WAITE<10>         WAITE<10         WAITE<10         WAITE<10 <th>Virtual Address<br/>(BF80_#)</th> <th>Register<br/>Name<sup>(1)</sup></th> <th>Bit Range</th> <th>31/15</th> <th>30/14</th> <th>29/13</th> <th>28/12</th> <th>27/11</th> <th>26/10</th> <th>25/9</th> <th>24/8</th> <th>23/7</th> <th>22/6</th> <th>21/5</th> <th>20/4</th> <th>19/3</th> <th>18/2</th> <th>17/1</th> <th>16/0</th> <th>All Resets</th> | Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13      | 28/12 | 27/11  | 26/10  | 25/9   | 24/8   | 23/7       | 22/6    | 21/5 | 20/4  | 19/3   | 18/2 | 17/1  | 16/0  | All Resets |

| Constraint         Constra                                                                                                                                                                                                                                                                                   | 7000                        | PMCON                           | 31:16     | _       | _       |            |       |        |        |        |        |            |         |      |       |        | _    |       |       | 0000       |

| 7010         PMMODE         15.0         BUSY         IRQM<1.0>         INCM<1.0>         MODE 16         MODE<1.0>         WAITE<1.0>         WAITE<1                                                                                                                                                                                                                                                                                            | 1000                        |                                 |           | ON      | —       | SIDL       | ADRMU | X<1:0> | PMPTTL | PTWREN | PTRDEN | CSF        | <1:0>   | ALP  | CS2P  | CS1P   | —    | WRSP  | RDSP  | 0000       |

| No         BUSY         IRQM<1:0>         INCM<1:0>         MODE16         MODE<1:0>         WAITE<1:0>         0000           7020         PMADR         100         GS2         CS1                                                                              0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7010                        | PMMODE                          |           |         | —       |            |       |        |        |        |        |            |         | —    |       |        | —    |       |       |            |

| 7020       PMADDR       CS2       CS1<br>ADDR15       ADDR14       ADDR13:0>       ADDR13:0>       ADDR13:0>       0000         7030       PMDOUT       31:16       -       -       -       -       -       -       -       0000         7030       PMDOUT       31:16       -       -       -       -       -       -       -       -       0000         7040       PMDIN       31:16       -       -       -       -       -       -       -       -       0000         7050       PMAEN       31:16       -       -       -       -       -       -       -       -       0000         7060       PMAEN       15:0       -       -       -       -       -       -       -       0000         7060       PMSTAT       15:0       -       -       -       -       -       -       -       0000         7070       PMWAT       15:0       ISO       ISO <t< td=""><td></td><td></td><td></td><td>BUSY</td><td>IRQM</td><td>&lt;1:0&gt;</td><td>INCM</td><td>&lt;1:0&gt;</td><td>MODE16</td><td>MODE</td><td>=&lt;1:0&gt;</td><td>WAITE</td><td>3&lt;1:0&gt;</td><td></td><td>WAITN</td><td>1&lt;3:0&gt;</td><td></td><td>WAITE</td><td>&lt;1:0&gt;</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                  |                             |                                 |           | BUSY    | IRQM    | <1:0>      | INCM  | <1:0>  | MODE16 | MODE   | =<1:0> | WAITE      | 3<1:0>  |      | WAITN | 1<3:0> |      | WAITE | <1:0> |            |

| 150         ADDR15         ADDR14           7030         PMDOUT         31:16         -         -         -         -         -         -         -         -         -         000           7030         PMDOUT         31:16         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         0000           7040         PMDIN         31:16         -         -         -         -         -         -         -         -         -         -         0000           7050         PMAEN         31:16         -         -         -         -         -         -         -         -         -         0000           7050         PMAEN         31:16         -         -         -         -         -         -         -         -         -         -         -         -         -         0000           7060         PMSTAT         31:16         -         -         -         -         -         -         -         -         -         -         -         -         0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |                                 | 31:16     |         |         | —          | —     | _      | _      | —      | —      | —          | —       | —    | —     | —      | _    | —     | _     |            |

| PMDOUT         31:16         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         000           7040         PMDIN         31:16         -         -         -         -         -         -         -         -         -         -         -         0000           7050         PMAEN         31:16         -         -         -         -         -         -         -         -         -         -         0000           7050         PMSTAT         31:16         -         -         -         -         -         -         -         -         -         -         -         0000         0000         0000         0000 </td <td>7020</td> <td>PMADDR</td> <td>15:0</td> <td></td> <td></td> <td colspan="11">ADDR&lt;13:0&gt;</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7020                        | PMADDR                          | 15:0      |         |         | ADDR<13:0> |       |        |        |        |        |            |         |      |       |        |      |       |       |            |

| 7030       PMDOUT       15:0       DATAOUT       0000         7040       PMDIN       31:16       -       -       -       -       -       -       -       -       0000         7040       PMDIN       31:16       -       -       -       -       -       -       -       -       -       -       -       0000         7050       PMAEN       31:16       -       -       -       -       -       -       -       -       -       -       -       0000         7050       PMAEN       31:16       -       -       -       -       -       -       -       -       -       0000         7060       PMSTAT       31:16       -       -       -       -       -       -       -       -       -       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |                                 | 21.16     | -       |         |            |       |        |        |        |        |            |         |      |       |        |      |       |       | _          |

| 704         PMDIN         31:16         -         -         -         -         -         -         -         -         -         000           705         PMAEN         31:16         -         -         -         -         -         -         -         -         -         000           705         PMAEN         31:16         -         -         -         -         -         -         -         -         -         000           705         PMAEN         31:16         -         -         -         -         -         -         -         -         -         000           706         PMSTAT         31:16         -         -         -         -         -         -         -         -         000           7070         PMWADR         31:16         -         -         -         -         -         -         -         -         000           7070         PMWADR         15:0         IBF         IBOV         -         -         -         -         -         -         000           7070         PMWADR         15:0         WCS2         WCS1         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7030                        | PMDOUT                          |           | _       |         |            |       |        |        |        |        |            |         |      |       |        |      |       |       |            |

| 700     PMDIN     15:0     DATAIN     000       700     PMAEN     31:16     -     -     -     -     -     -     -     -     000       700     PMSTAT     31:16     -     -     -     -     -     -     -     -     000       7010     PMSTAT     31:16     -     -     -     -     -     -     -     -     000       7010     PMSADR     31:16     -     -     -     -     -     -     -     -     000       7010     PMRADR     31:16     -     -     -     -     -     -     -     -     -     000       7010     PMRADR     31:16     -     -     -     -     -     -     -     -     0000       7010     PMRADR     31:16     -     -     -     -     -     -     -     -     0000       7010     PMRADR     31:16     -     -     -     -     -     -     -     -     0000       7010     PMRADR     31:16     -     -     -     -     -     -     -     -     0000       7000     PMRADR </td <td></td> <td>DATAOL</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |                                 |           |         |         |            |       |        |        |        | DATAOL |            |         |      |       |        |      |       |       |            |