Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx550f256ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS |            |

|------------|-------------------------|------------|

| IADLE I-I. | FINUUT I/U DESCRIFTIONS | CONTINUED) |

|           | Pin N                                 | umber                                 |             |                |                                                                                   |  |  |  |  |  |

|-----------|---------------------------------------|---------------------------------------|-------------|----------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name  | 64-pin<br>QFN/<br>TQFP                | 100-pin<br>TQFP                       | Pin<br>Type | Buffer<br>Type | Description                                                                       |  |  |  |  |  |

| INT0      | 35 <sup>(1)</sup> , 46 <sup>(2)</sup> | 55 <sup>(1)</sup> , 72 <sup>(2)</sup> | I           | ST             | External Interrupt 0                                                              |  |  |  |  |  |

| INT1      | PPS                                   | PPS                                   | Ι           | ST             | External Interrupt 1                                                              |  |  |  |  |  |

| INT2      | PPS                                   | PPS                                   | Ι           | ST             | External Interrupt 2                                                              |  |  |  |  |  |

| INT3      | PPS                                   | PPS                                   | Ι           | ST             | External Interrupt 3                                                              |  |  |  |  |  |

| INT4      | PPS                                   | PPS                                   | Ι           | ST             | External Interrupt 4                                                              |  |  |  |  |  |

| RA0       | _                                     | 17                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RA1       | _                                     | 38                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RA2       | —                                     | 58                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RA3       | —                                     | 59                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RA4       | _                                     | 60                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RA5       | _                                     | 61                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RA6       | _                                     | 91                                    | I/O         | ST             | PORTA is a bidirectional I/O port                                                 |  |  |  |  |  |

| RA7       | _                                     | 92                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RA9       | _                                     | 28                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RA10      | _                                     | 29                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RA14      | _                                     | 66                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RA15      |                                       | 67                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RB0       | 16                                    | 25                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RB1       | 15                                    | 24                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RB2       | 14                                    | 23                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RB3       | 13                                    | 22                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RB4       | 12                                    | 21                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RB5       | 11                                    | 20                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RB6       | 17                                    | 26                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RB7       | 18                                    | 27                                    | I/O         | ST             |                                                                                   |  |  |  |  |  |

| RB8       | 21                                    | 32                                    | I/O         | ST             | PORTB is a bidirectional I/O port                                                 |  |  |  |  |  |

| RB9       | 22                                    | 33                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RB10      | 23                                    | 34                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RB11      | 24                                    | 35                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RB12      | 27                                    | 41                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RB13      | 28                                    | 42                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RB14      | 29                                    | 43                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| RB15      | 30                                    | 44                                    | I/O         | ST             | 1                                                                                 |  |  |  |  |  |

| Legend: ( | CMOS = CN                             | IOS compati<br>t Trigger inpl         | ble inpu    | it or output   | Analog = Analog input I = Input O = Output<br>Is TTL = TTL input buffer P = Power |  |  |  |  |  |

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 | _                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |

## **REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER**

# Legend:

| Legena.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 | —                 | _                 |                   | IP3<2:0>          | IS3<1:0>          |                  |                  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | —                 | _                 |                   | IP2<2:0>          | IS2<1:0>          |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | —                 | —                 | —                 |                   | IP1<2:0>          |                   | IS1<             | :1:0>            |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 |                   | IP0<2:0>          |                   | IS0<             | :1:0>            |

### REGISTER 5-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

000 = Interrupt is disabled

bit 25-24 **IS3<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 23-21 **Unimplemented:** Read as '0'

bit 20-18 IP2<2:0>: Interrupt Priority bits

```

111 = Interrupt priority is 7

```

```

•

•

• 010 - Interrupt priority

```

- 010 = Interrupt priority is 2

- 001 = Interrupt priority is 1 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

- bit 12-10 IP1<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

- 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

Note: This register represents a generic definition of the IPCx register. Refer to Table 5-1 for the exact bit definitions.

## TABLE 11-6: PORTC REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |           |           |           |           |       |       |      | Bits |      |      |      |      |         |         |         |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|------|---------|---------|---------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3    | 18/2    | 17/1    | 16/0 | All<br>Resets |

| 6200                        | ANSELC                          | 31:16     | _         | —         | —         | _         | —     | -     |      |      | _    | —    | _    |      | —       |         | —       | _    | 0000          |

| 0200                        | /                               | 15:0      | —         | —         | —         | —         | —     | —     | —    | -    | —    | _    | —    | _    | ANSELC3 | ANSELC2 | ANSELC1 | —    | 000E          |

| 6210                        | TRISC                           | 31:16     |           | —         | —         | —         | _     | _     | _    |      | _    |      | —    | _    | _       | _       | —       | _    | 0000          |

| 02.0                        |                                 | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | —     | —     | —    | -    | —    | _    | —    | _    | —       | —       | —       | —    | F000          |

| 6220                        | PORTC                           | 31:16     | —         | —         | —         | —         | _     | _     | _    | _    | —    | _    | —    | _    | —       | _       | —       |      | 0000          |

| 0220                        | TOKIC                           | 15:0      | RC15      | RC14      | RC13      | RC12      | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | xxxx          |

| 6230                        | LATC                            | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       |      | 0000          |

| 0200                        | Ento                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | xxxx          |

| 6240                        | ODCC                            | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 02.10                       | 0200                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 6250                        | CNPUC                           | 31:16     |           | —         | —         | —         | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 0200                        |                                 | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 6260                        | CNPDC                           | 31:16     |           | —         | —         | —         | —     | _     | _    | _    | —    | —    | —    |      | —       | _       | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | —     | —     | —    | —    | —    | —    | —    | —    | —       | _       | —       | —    | 0000          |

| 6270                        | CNCONC                          | 31:16     |           |           |           | _         |       |       |      |      | —    | _    | —    | _    | —       |         | —       |      | 0000          |

| 0270                        | oncono                          | 15:0      | ON        |           | SIDL      |           |       |       |      |      | —    | _    | —    | _    | —       |         | —       |      | 0000          |

| 6280                        | CNENC                           | 31:16     |           | —         |           |           |       |       |      |      | —    | _    | —    | _    | —       |         | —       |      | 0000          |

| 0200                        |                                 | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | —     | _     | _    |      | —    |      | —    | _    | —       |         | —       | _    | 0000          |

| 6200                        | CNSTATC                         | 31:16     | _         | —         | —         | _         | _     |       |      |      | -    | —    | -    |      | —       |         | —       | —    | 0000          |

| 0290                        | GNOTAIC                         | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     |       |      |      | -    | _    |      |      | _       |         | —       | _    | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

#### REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        | —                 | —                 | —                 | RXBUFELM<4:0>     |                   |                   |                  |                  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | —                 | —                 | —                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |  |  |  |

| 15:8         |                   | —                 | —                 | FRMERR            | SPIBUSY           |                   | _                | SPITUR           |  |  |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE            | _                 | SPITBF           | SPIRBF           |  |  |  |  |

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 **SPITUR:** Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

- This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

- This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 SPIRBE: RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR ≠ SWPTR)

- bit 4 Unimplemented: Read as '0'

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |  |

| 31:24        | —                 | _                 | —                 | _                 | _                 | _                 | _                | ADM_EN           |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |  |  |  |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |  |  |  |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |  |

### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

## Legend:

| Logonal           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

#### bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 =Interrupt is generated and asserted while the transmit buffer contains at least one empty space

### bit 13 UTXINV: Transmit Polarity Inversion bit

- If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

### If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

#### bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by the port.

#### bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by the port.

#### bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

| REGIST  | ER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8   | <ul> <li>TRMT: Transmit Shift Register is Empty bit (read-only)</li> <li>1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer</li> </ul>                                                                                                                                  |

| bit 7-6 | <pre>URXISEL&lt;1:0&gt;: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 =Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)</pre> |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                   |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                                                                                                                                                     |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                                            |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                                                         |

| bit 1   | <b>OERR:</b> Receive Buffer Overrun Error Status bit.<br>This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.<br>1 = Receive buffer has overflowed                                                                                                                                                                                     |

|         | 0 = Receive buffer has not overflowed                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 0   | <ul> <li>URXDA: Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                    |

## REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- • 0001 = Wait of 2 Трв

- 0000 = Wait of 1 TPB (default)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 TPB 10 = Wait of 3 TPB 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

For Read operations: 11 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 1 TPB 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit         Bit           30/22/14/6         29/21/13/5           U-0         U-0 |             | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-----------------------------------------------------------------------------------|-------------|-------------------|-------------------|-------------------|--------------------------|------------------|--|--|

| 31:24        | U-0               | U-0 U-0                                                                           |             | U-0               | U-0               | U-0               | U-0                      | U-0              |  |  |

| 31.24        |                   |                                                                                   | _           | _                 | _                 |                   |                          | —                |  |  |

| 22:16        | U-0 U-0           |                                                                                   | U-0         | U-0               | U-0               | U-0               | U-0                      | U-0              |  |  |

| 23:16        | -                 | _                                                                                 | _           | _                 | _                 | _                 | _                        | —                |  |  |

| 15.0         | R/W-0             | R/W-0                                                                             | R/W-0 R/W-0 |                   | R/W-0 R/W-0       |                   | R/W-0                    | R/W-0            |  |  |

| 15:8         | PTEN<1            | 5:14> <sup>(1)</sup>                                                              | PTEN<13:8>  |                   |                   |                   |                          |                  |  |  |

| 7.0          | R/W-0             | R/W-0                                                                             | R/W-0 R/W-0 |                   | R/W-0             | R/W-0             | R/W-0                    | R/W-0            |  |  |

| 7:0          |                   |                                                                                   | PTEN        | <7:2>             |                   |                   | PTEN<1:0> <sup>(2)</sup> |                  |  |  |

## REGISTER 20-6: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

# Legend:

| Legenu.           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-16 Unimplemented: Write '0'; ignore read

- bit 15-14 **PTEN<15:14>:** PMCSx Address Port Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS2 and PMCS1<sup>(1)</sup>

- 0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits

- 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15/PMA14 or CS2/CS1 is selected by the CSF<1:0> bits (PMCON<7:6>).

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by the ADRMUX<1:0> bits in the PMCON register.

| Bit<br>Range |       |       |       |          | Bit Bit<br>8/20/12/4 27/19/11/3 |       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------|-------|-------|----------|---------------------------------|-------|------------------|------------------|--|

| 24.24        | U-0   | U-0   | U-0   | U-0      | U-0                             | U-0   | U-0              | U-0              |  |

| 31:24        | _     | _     | —     | _        | —                               | —     | _                | —                |  |

| 22:16        | U-0   | U-0   | U-0   | U-0      | U-0                             | U-0   | U-0              | U-0              |  |

| 23:16        | —     | —     | —     | -        | —                               | —     | -                | —                |  |

| 45.0         | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0                           | R/W-0 | R/W-0            | R/W-0            |  |

| 15:8         |       |       |       | RDATAIN< | 15:8>                           |       |                  |                  |  |

| 7:0          | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0                           | R/W-0 | R/W-0            | R/W-0            |  |

|              |       |       |       | RDATAIN< | <7:0>                           |       |                  |                  |  |

## REGISTER 20-10: PMRDIN: PARALLEL PORT READ INPUT DATA REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **RDATAIN<15:0>:** Port Read Input Data bits

**Note:** This register is only used when the DUALBUF bit (PMCON<17>) is set to '1' and exclusively for reads. If the DUALBUF bit is '0', the PMDIN register (Register 20-5) is used for reads instead of PMRDIN.

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |     |      |       | Bit Bit<br>28/20/12/4 27/19/11/3 2 |        | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|----------------------------------|-----|------|-------|------------------------------------|--------|------------------|------------------|--|--|--|--|

| 31:24        | U-0                              | U-0 | U-0  | U-0   | U-0                                | U-0    | U-0              | U-0              |  |  |  |  |

| 51.24        |                                  | —   | _    | _     | _                                  |        | _                | —                |  |  |  |  |

| 00.40        | U-0                              | U-0 | R-0  | R-0   | R-0                                | R-0    | R-0              | R-0              |  |  |  |  |

| 23:16        | —                                | —   | TXBO | TXBP  | RXBP                               | TXWARN | RXWARN           | EWARN            |  |  |  |  |

| 15.0         | R-0                              | R-0 | R-0  | R-0   | R-0                                | R-0    | R-0              | R-0              |  |  |  |  |

| 15:8         | TERRCNT<7:0>                     |     |      |       |                                    |        |                  |                  |  |  |  |  |

| 7:0          | R-0                              | R-0 | R-0  | R-0   | R-0                                | R-0    | R-0              | R-0              |  |  |  |  |

| 7:0          |                                  |     |      | RERRC | NT<7:0>                            |        |                  |                  |  |  |  |  |

## REGISTER 23-5: C1TREC: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-22 Unimplemented: Read as '0'

bit 21 **TXBO:** Transmitter in Error State Bus OFF (TERRCNT  $\geq$  256)

- bit 20 **TXBP:** Transmitter in Error State Bus Passive (TERRCNT ≥ 128)

- bit 19 **RXBP:** Receiver in Error State Bus Passive (RERRCNT  $\geq$  128)

bit 18 **TXWARN:** Transmitter in Error State Warning (128 > TERRCNT ≥ 96)

bit 17 **RXWARN:** Receiver in Error State Warning (128 > RERRCNT  $\ge$  96)

bit 16 EWARN: Transmitter or Receiver is in Error State Warning

- bit 15-8 TERRCNT<7:0>: Transmit Error Counter

- bit 7-0 RERRCNT<7:0>: Receive Error Counter

## REGISTER 23-6: C1FSTAT: CAN FIFO STATUS REGISTER

| Bit<br>Range |          |          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------|----------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0      | U-0      | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | _        | —        |                   | _                 | _                 | _                 |                  | _                |  |

| 23:16        | U-0      | U-0      | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —        | _        | _                 | —                 | _                 | _                 | _                | _                |  |

| 15:8         | R-0      | R-0      | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 10.0         | FIFOIP15 | FIFOIP14 | FIFOIP13          | FIFOIP12          | FIFOIP11          | FIFOIP10          | FIFOIP9          | FIFOIP8          |  |

| 7:0          | R-0      | R-0      | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | FIFOIP7  | FIFOIP6  | FIFOIP5           | FIFOIP4           | FIFOIP3           | FIFOIP2           | FIFOIP1          | FIFOIP0          |  |

| Legend:                            |                  |                           |                    |

|------------------------------------|------------------|---------------------------|--------------------|

| R = Readable bit                   | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR '1' = Bit is set |                  | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 FIFOIP<15:0>: FIFOx Interrupt Pending bits

1 = One or more enabled FIFO interrupts are pending

0 = No FIFO interrupts are pending

| Bit<br>Range | Bit<br>31/23/15/7 |       |             |        |         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0   |                    |  |  |  |  |  |

|--------------|-------------------|-------|-------------|--------|---------|------------------|--------------------|--------------------|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0 | R/W-0       | R/W-0  | R/W-0   | R/W-0            | R/W-0              | R/W-0              |  |  |  |  |  |

| 31.24        | C1FIFOBA<31:24>   |       |             |        |         |                  |                    |                    |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0 | R/W-0       | R/W-0  | R/W-0   | R/W-0            | R/W-0              | R/W-0              |  |  |  |  |  |

| 23.10        | C1FIFOBA<23:16>   |       |             |        |         |                  |                    |                    |  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0 | R/W-0       | R/W-0  | R/W-0   | R/W-0            | R/W-0              | R/W-0              |  |  |  |  |  |

| 10.0         | C1FIFOBA<15:8>    |       |             |        |         |                  |                    |                    |  |  |  |  |  |

| 7:0          | R/W-0 R/W-0       |       | R/W-0 R/W-0 |        | R/W-0   | R/W-0            | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |  |  |

| 7:0          |                   |       |             | C1FIFO | BA<7:0> |                  |                    |                    |  |  |  |  |  |

### REGISTER 23-15: C1FIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

#### Legend:

| Logonal           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 C1FIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Bits <1:0> are read-only and read as '0', forcing the messages to be 32-bit word-aligned in device RAM.

**Note 1:** This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

## 24.1 Control Registers

# TABLE 24-1: COMPARATOR REGISTER MAP

| ess                         |                                 |           |       | Bits  |       |       |       |       |      |      |      |        |      |      |      |       |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Resets |

| 4000                        | CM1CON                          | 31:16     | —     | _     | —     | —     | —     | -     | —    | —    | _    | —      | —    | —    | _    | —     | —     | _     | 0000       |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | —     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4010                        | CM2CON                          | 31:16     | —     | -     | —     | —     |       | —     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| AUTU                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | —     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4020                        | CM3CON                          | 31:16     | —     | -     | —     | —     |       | —     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | —     |       | _     | —    | COUT | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | E1C3       |

| 4060                        | CMSTAT                          | 31:16     | —     | -     | —     | —     |       | _     | —    | —    | _    | —      | _    | —    | _    | —     | —     | —     | 0000       |

| A060                        | CIVISTAT                        | 15:0      | —     | _     | SIDL  | —     | _     |       |      | _    | —    |        | —    | —    | —    | C3OUT | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

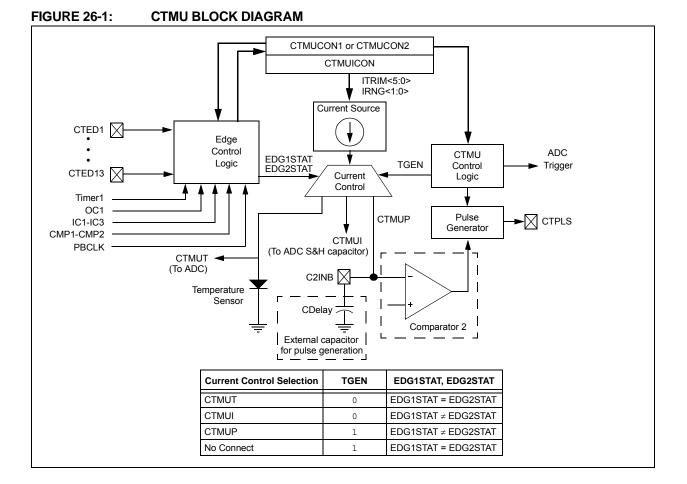

# 26.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167) in the "PIC32 Family Reference Manual", which is available the site from Microchip web (www.microchip.com).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The CTMU module includes the following key features:

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 26-1.

© 2014-2016 Microchip Technology Inc.

NOTES:

| AC CHARACTERISTICS |           |                                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |         |       |                                                           |  |

|--------------------|-----------|----------------------------------------------------------------------|------------------------------------------------------|------------------------|---------|-------|-----------------------------------------------------------|--|

| Param.<br>No.      | Symbol    | Characteristics                                                      | Min.                                                 | Typical <sup>(1)</sup> | Max.    | Units | Conditions                                                |  |

| Clock P            | arameter  | S                                                                    | •                                                    | •                      |         |       | ·                                                         |  |

| AD50               | Tad       | ADC Clock Period <sup>(2)</sup>                                      | 65                                                   | —                      | —       | ns    | See Table 31-35                                           |  |

| Convers            | sion Rate | •                                                                    |                                                      |                        |         |       |                                                           |  |

| AD55               | TCONV     | Conversion Time                                                      |                                                      | 12 Tad                 | _       |       | —                                                         |  |

| AD56               | FCNV      | Throughput Rate<br>(Sampling Speed)                                  | _                                                    | _                      | 1000    | ksps  | AVDD = 3.0V to 3.6V                                       |  |

|                    |           |                                                                      | _                                                    | —                      | 400     | ksps  | AVDD = 2.5V to 3.6V                                       |  |

| AD57               | TSAMP     | Sample Time                                                          | 1 Tad                                                | —                      | —       | _     | TSAMP must be $\geq$ 132 ns                               |  |

| Timing             | Paramete  | rs                                                                   |                                                      |                        |         |       |                                                           |  |

| AD60               | TPCS      | Conversion Start from Sample<br>Trigger <sup>(3)</sup>               |                                                      | 1.0 Tad                | _       | _     | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected |  |

| AD61               | TPSS      | Sample Start from Setting<br>Sample (SAMP) bit                       | 0.5 TAD                                              | —                      | 1.5 Tad | _     | —                                                         |  |

| AD62               | TCSS      | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(3)</sup>   | _                                                    | 0.5 Tad                | —       | _     | _                                                         |  |

| AD63               | TDPU      | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(3)</sup> |                                                      |                        | 2       | μS    | _                                                         |  |

## TABLE 31-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** Characterized by design but not tested.

**4:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

## TABLE 31-41: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS  |        |                                                    |      | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3):2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                                  |  |  |  |

|---------------------|--------|----------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|--|--|--|

| Param<br>No.        | Symbol | Characteristic                                     | Min. | Тур.                                                                                                                                                                                                                                                                                              | Max. | Units | Conditions                       |  |  |  |

| CTMU CURRENT SOURCE |        |                                                    |      |                                                                                                                                                                                                                                                                                                   |      |       |                                  |  |  |  |

| CTMUI1              | Ιουτ1  | Base Range <sup>(1)</sup>                          | _    | 0.55                                                                                                                                                                                                                                                                                              | _    | μA    | CTMUCON<9:8> = 01                |  |  |  |

| CTMUI2              | Ιουτ2  | 10x Range <sup>(1)</sup>                           | _    | 5.5                                                                                                                                                                                                                                                                                               | _    | μA    | CTMUCON<9:8> = 10                |  |  |  |

| CTMUI3              | Ιουτ3  | 100x Range <sup>(1)</sup>                          | _    | 55                                                                                                                                                                                                                                                                                                | _    | μA    | CTMUCON<9:8> = 11                |  |  |  |

| CTMUI4              | IOUT4  | 1000x Range <sup>(1)</sup>                         | —    | 550                                                                                                                                                                                                                                                                                               | _    | μA    | CTMUCON<9:8> = 00                |  |  |  |

| CTMUFV1             | VF     | Temperature Diode Forward Voltage <sup>(1,2)</sup> | _    | 0.598                                                                                                                                                                                                                                                                                             | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 01 |  |  |  |

|                     |        |                                                    | _    | 0.658                                                                                                                                                                                                                                                                                             | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 10 |  |  |  |

|                     |        |                                                    | _    | 0.721                                                                                                                                                                                                                                                                                             | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 11 |  |  |  |

| CTMUFV2             | Vfvr   | Temperature Diode Rate of Change <sup>(1,2)</sup>  | _    | -1.92                                                                                                                                                                                                                                                                                             | _    | mV/ºC | CTMUCON<9:8> = 01                |  |  |  |

|                     |        |                                                    | _    | -1.74                                                                                                                                                                                                                                                                                             | _    | mV/ºC | CTMUCON<9:8> = 10                |  |  |  |

|                     |        |                                                    | _    | -1.56                                                                                                                                                                                                                                                                                             | _    | mV/ºC | CTMUCON<9:8> = 11                |  |  |  |

**Note 1:** Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

2: Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

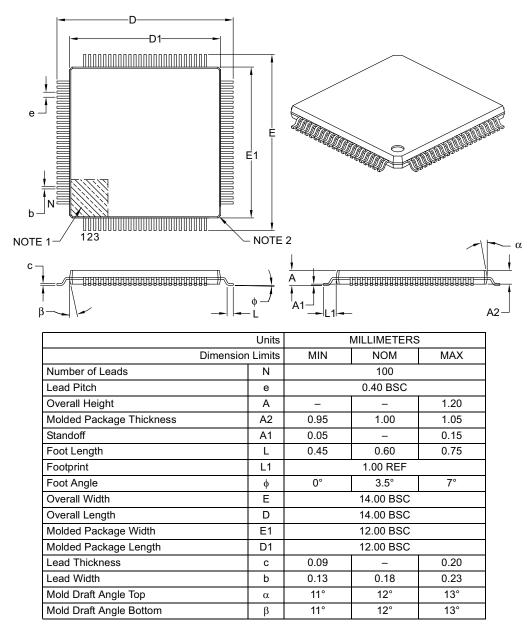

# 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B