Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 81                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                            |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

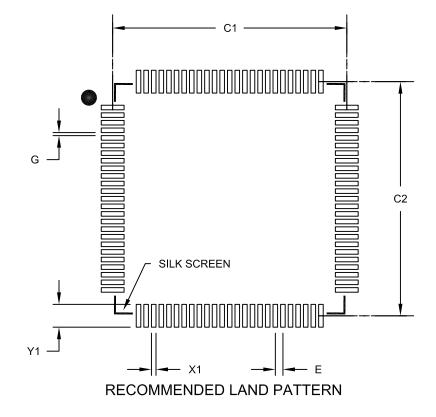

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx550f256l-50i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

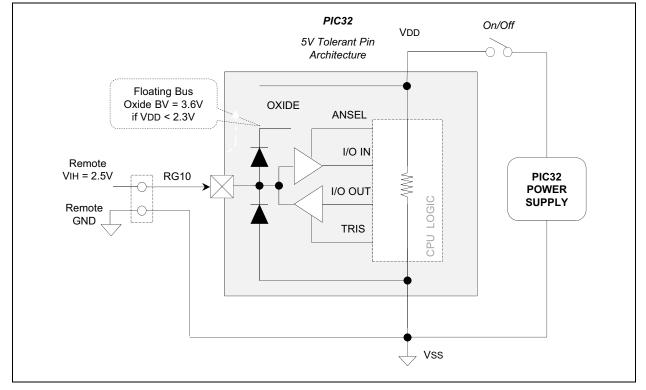

### 2.9.2 5V TOLERANT INPUT PINS

The internal high side diode on 5V tolerant pins are bussed to an internal floating node, rather than being connected to VDD, as shown in Figure 2-7. Voltages on these pins, if VDD < 2.3V, should not exceed roughly 3.2V relative to Vss of the PIC32 device. Voltage of 3.6V or higher will violate the absolute maximum specification, and will stress the oxide layer separating the high side floating node, which impacts device reliability. If a remotely powered "digital-only" signal can be guaranteed to always be  $\leq$  3.2V relative to Vss on the PIC32 device side, a 5V tolerant pin could be used without the need for a digital isolator. This is assuming there is not a ground loop issue, logic ground of the two circuits not at the same absolute level, and a remote logic low input is not less than Vss - 0.3V.

NOTES:

### 6.1 Control Registers

### TABLE 6-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | a         |       |                  |       |        |         |       |      | Bi        | ts        |      |      |      |      |      |        |      | 6          |

|-----------------------------|------------------------|-----------|-------|------------------|-------|--------|---------|-------|------|-----------|-----------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14            | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8      | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     | _     | —                | —     | —      | _       |       | —    |           | —         | —    | —    | —    |      |      | —      | —    | 0000       |

| 1400                        |                        | 15:0      | WR    | WREN             | WRERR | LVDERR | LVDSTAT |       | _    | -         | _         | _    | _    | _    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     |       |                  |       |        |         |       |      | NVMKE     | /<31.0>   |      |      |      |      |      |        |      | 0000       |

|                             |                        | 15:0      |       |                  |       |        |         |       |      |           | 1501.02   |      |      |      |      |      |        |      | 0000       |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                  |       |        |         |       |      | NVMADE    | P<31.05   |      |      |      |      |      |        |      | 0000       |

| 1 420                       | NVINADDR               | 15:0      |       |                  |       |        |         |       |      | INVIVIADE | K~51.02   |      |      |      |      |      |        |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       | NVMDATA<31:0>    |       |        |         |       |      |           |           |      |      |      |      |      |        |      |            |

| 1430                        | NVINDAIA               | 15:0      |       |                  |       |        |         |       |      | NVIVIDAI  | A-31.02   |      |      |      |      |      |        |      | 0000       |

| F440                        | NVMSRC                 | 31:16     |       | NVMSRCADDR<31:0> |       |        |         |       |      |           |           |      |      |      |      |      |        |      |            |

| F440                        | ADDR                   | 15:0      |       |                  |       |        |         |       | I    | VIVISRUAI | JUR-31.02 | •    |      |      |      |      |        |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |       |                     |                      |                       |                        |       |        |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------------|----------------------|-----------------------|------------------------|-------|--------|-------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |       |                     |                      |                       |                        |       |        | -     |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24.24 | U-0   | U-0                 | U-0                  | U-0                   | U-0                    | U-0   | U-0    | U-0   |

| 23:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31:24 | _     | —                   | _                    | —                     | _                      | —     | _      | —     |

| Image: Normal system         Image: No | 00:16 | U-0   | U-0                 | U-0                  | U-0                   | U-0                    | U-0   | U-0    | U-0   |

| 15:8         WR         WREN <sup>(1)</sup> WRERR <sup>(2)</sup> LVDERR <sup>(2)</sup> LVDSTAT <sup>(2)</sup> —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         _         _         _         _         _         _         _         _         _         _         _         _         _ <td>23.10</td> <td>—</td> <td>—</td> <td>—</td> <td>—</td> <td>_</td> <td>—</td> <td>—</td> <td>—</td>                                                                                                                                                                                                                                                                                                                                                                 | 23.10 | —     | —                   | —                    | —                     | _                      | —     | —      | —     |

| WR         WREN''         WRER''         LVDERR''         LVDSTAT''         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         Image: Main Main Main Main Main Main Main Main                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45.0  | R/W-0 | R/W-0               | R-0                  | R-0                   | -                      |       | U-0    | U-0   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15:8  | WR    | WREN <sup>(1)</sup> | WRERR <sup>(2)</sup> | LVDERR <sup>(2)</sup> | LVDSTAT <sup>(2)</sup> |       | _      | —     |

| 1.0 — — — — NVMOP<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7:0   | U-0   | U-0                 | U-0                  | U-0                   | R/W-0                  | R/W-0 | R/W-0  | R/W-0 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7:0   | _     | —                   | -                    | —                     |                        | NVMOF | P<3:0> |       |

### **REGISTER 6-1:** NVMCON: PROGRAMMING CONTROL REGISTER

### Legend:

| Logonal           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0'                                                                                        |

|-----------|-------------------------------------------------------------------------------------------------------------------|

| bit 15    | WR: Write Control bit                                                                                             |

|           | This bit is writable when WREN = 1 and the unlock sequence is followed.                                           |

|           | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                             |

|           | 0 = Flash operation complete or inactive                                                                          |

| bit 14    | WREN: Write Enable bit <sup>(1)</sup>                                                                             |

|           | 1 = Enable writes to WR bit and enables LVD circuit                                                               |

|           | 0 = Disable writes to WR bit and disables LVD circuit                                                             |

|           | This is the only bit in this register reset by a device Reset.                                                    |

| bit 13    | WRERR: Write Error bit <sup>(2)</sup>                                                                             |

|           | This bit is read-only and is automatically set by hardware.                                                       |

|           | 1 = Program or erase sequence did not complete successfully                                                       |

|           | 0 = Program or erase sequence completed normally                                                                  |

| bit 12    | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(2)</sup>                                 |

|           | This bit is read-only and is automatically set by hardware.                                                       |

|           | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                              |

|           | 0 = Voltage level is acceptable for programming                                                                   |

| bit 11    | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(2)</sup>                               |

|           | This bit is read-only and is automatically set, and cleared, by hardware.                                         |

|           | 1 = Low-voltage event active                                                                                      |

|           | 0 = Low-voltage event NOT active                                                                                  |

| bit 10-4  | Unimplemented: Read as '0'                                                                                        |

| bit 3-0   | NVMOP<3:0>: NVM Operation bits                                                                                    |

|           | These bits are writable when WREN = $0$ .                                                                         |

|           | 1111 =Reserved                                                                                                    |

|           | •                                                                                                                 |

|           | •                                                                                                                 |

|           | •                                                                                                                 |

|           | 0111 = Reserved                                                                                                   |

|           | 0110 =No operation<br>0101 =Program Flash (PFM) erase operation: erases PFM, if all pages are not write-protected |

|           | 0100 =Page erase operation: erases page selected by NVMADDR, if it is not write-protected                         |

|           | 0011 =Row program operation: programs row selected by NVMADDR, if it is not write-protected                       |

|           | 0010 =No operation                                                                                                |

|           | 0001 =Word program operation: programs word selected by NVMADDR, if it is not write-protected                     |

|           | 0000 = No operation                                                                                               |

|           |                                                                                                                   |

| Note 1:   | This bit is cleared by any reset (i.e., POR, BOR, WDT, MCLR, SWR).                                                |

| -         |                                                                                                                   |

2: This bit is only cleared by setting NVMOP = 0000, and initiating a Flash WR operation or a POR. Any other kind of reset (i.e., BOR, WDT, MCLR) does not clear this bit.

| ess                         |                                 |                              |             |       |       |       |        |       |      | Bi          | ts        |            |            |            |         |             |        |        |            |

|-----------------------------|---------------------------------|------------------------------|-------------|-------|-------|-------|--------|-------|------|-------------|-----------|------------|------------|------------|---------|-------------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                    | 31/15       | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8        | 23/7      | 22/6       | 21/5       | 20/4       | 19/3    | 18/2        | 17/1   | 16/0   | All Resets |

| 3060                        | DCH0CON                         | 31:16<br>15:0                | —<br>CHBUSY | —     | —     | _     | —      | —     | —    | —<br>CHCHNS | —<br>CHEN | —<br>CHAED | —<br>CHCHN | —<br>CHAEN | —       | —<br>CHEDET |        | -      | 00         |

|                             |                                 | 31:16                        |             |       |       |       |        |       |      |             |           |            |            |            |         |             |        |        |            |

| 3070                        | DCH0ECON                        | 15:0                         |             |       |       | CHSIR | Q<7:0> |       |      |             | CFORCE    | CABORT     | PATEN      | SIRQEN     |         |             | _      |        | FF         |

|                             |                                 | 31:16                        | _           | _     | —     | _     | _      | _     | _    | _           | CHSDIE    | CHSHIE     | CHDDIE     | CHDHIE     | CHBCIE  | CHCCIE      | CHTAIE | CHERIE | 00         |

| 3080                        | DCH0INT                         | 15:0                         | _           | _     | _     | _     | _      | _     |      |             | CHSDIF    | CHSHIF     | CHDDIF     | CHDHIF     | CHBCIF  | CHCCIF      | CHTAIF | CHERIF | 00         |

| 3090                        | DCH0SSA                         | 31:16<br>15:0                |             |       |       |       |        |       |      | CHSSA       | <31:0>    |            |            |            | •       |             |        |        | 00         |

| 30A0                        | DCH0DSA                         | 31:16<br>15:0                |             |       |       |       |        |       |      | CHDSA       | <31:0>    |            |            |            |         |             |        |        | 00         |

|                             | D.0110.0017                     | 31:16                        | _           | _     | _     | _     | _      | _     | _    | _           | _         | _          | _          | _          | _       | _           | _      | _      | 00         |

| 30B0                        | DCH0SSIZ                        | 15:0                         |             |       |       |       |        |       |      | CHSSIZ      | Z<15:0>   |            |            |            |         |             |        |        | 0.0        |

| 2000                        | DCH0DSIZ                        | 31:16                        | _           | —     | _     | —     | _      | _     |      | _           | _         | _          | _          | _          | _       | _           | —      | _      | 00         |

| 5000                        | DCHUD3IZ                        | 15:0                         |             |       |       |       |        |       |      | CHDSIZ      | Z<15:0>   |            |            |            |         |             |        |        | 00         |

| 3000                        | DCH0SPTR                        | 31:16                        | —           | _     | —     | —     | _      | _     | —    | -           | _         | —          |            |            | _       | —           | _      |        | 00         |

| 0000                        | Donioor III                     | 15:0                         |             |       |       |       |        |       |      | CHSPTI      | R<15:0>   |            |            |            |         |             |        |        | 00         |

| 30E0                        | DCH0DPTR                        | 31:16                        | —           | _     | —     | —     | —      | —     | —    |             | _         | —          |            | —          | —       | —           | _      | _      | 00         |

|                             |                                 | 15:0                         |             |       |       |       |        |       |      | CHDPTI      | R<15:0>   |            |            |            |         |             |        |        | 00         |

| 30F0                        | DCH0CSIZ                        | 31:16                        | —           |       | —     | —     | —      | —     |      |             | -         |            | —          | —          |         | —           | _      | _      | 00         |

|                             |                                 | 15:0                         |             |       |       |       | _      |       |      | CHCSIZ      | 2<15:0>   | _          |            | _          |         |             |        |        | 00         |

| 3100                        | DCH0CPTR                        | 31:16<br>15:0                | —           |       |       |       | _      |       |      | CHCPTI      |           |            |            |            | _       | —           | _      |        | 00         |

|                             |                                 | 31:16                        |             | _     | _     | _     | _      | _     | _    |             |           | _          | _          |            |         | _           | _      | _      | 00         |

| 3110                        | DCH0DAT                         | 15:0                         | _           | _     | _     | _     | _      | _     | _    | _           |           |            |            |            | AT<7:0> |             |        |        | 00         |

|                             |                                 | 31:16                        | _           | _     | _     | _     | _      | _     |      | _           | _         | —          | —          | _          | _       | _           | _      | _      | 00         |

| 3120                        | DCH1CON                         | 15:0                         | CHBUSY      | _     | _     | _     | _      | _     | _    | CHCHNS      | CHEN      | CHAED      | CHCHN      | CHAEN      | _       | CHEDET      | CHPR   | <1:0>  | 00         |

| 0400                        | DOLUEDON                        | 31:16                        | _           | _     | _     | _     | _      | _     | _    | -           |           |            |            | CHAIR      | Q<7:0>  |             |        |        | 00         |

| 3130                        | DCH1ECON                        | 15:0                         |             |       |       | CHSIR | Q<7:0> |       |      |             | CFORCE    | CABORT     | PATEN      | SIRQEN     | AIRQEN  | _           | —      | —      | FF         |

| 3140                        | DCH1INT                         | 31:16                        |             | _     |       | _     | _      |       |      | _           | CHSDIE    | CHSHIE     | CHDDIE     | CHDHIE     | CHBCIE  | CHCCIE      | CHTAIE | CHERIE | 00         |

| 5140                        | DCHIINI                         | 15:0                         | —           |       | —     | _     | _      | _     | —    | —           | CHSDIF    | CHSHIF     | CHDDIF     | CHDHIF     | CHBCIF  | CHCCIF      | CHTAIF | CHERIF | 00         |

| 3150                        | DCH1SSA                         | 31:16<br>15:0<br>CHSSA<31:0> |             |       |       |       |        |       |      |             |           |            |            |            |         |             |        |        |            |

| 3160                        | DCH1DSA                         | 31:16<br>15:0                |             |       |       |       |        |       |      | CHDSA       | <31:0>    |            |            |            |         |             |        |        | 00         |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information. Note 1:

# PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

| REGIOI       |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | -                 | —                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | —                 | —                 | -                 | —                 | —                 | —                 | —                | _                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | —                 | —                 |                   | _                 |                   |                   | —                | —                |  |  |  |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |  |

| 7.0          | UACTPND           | —                 | _                 | USLPGRD           | USBBUSY           | _                 | USUSPEND         | USBPWR           |  |  |  |

### REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

### Legend:

| Logonal                           |                  |                            |                    |  |

|-----------------------------------|------------------|----------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, rea | ad as '0'          |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

| Bit<br>Range            | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24                   |                   | —                 |                   |                   |                   |                   |                  | _                |

| 23:16                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10                   |                   | —                 |                   |                   | -                 |                   |                  | _                |

| 15:8                    | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0                    | -                 | —                 | -                 | -                 | _                 | -                 | —                | —                |

| 7:0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0 LSPDEN DEVADDR<6:0> |                   |                   |                   |                   |                   |                   |                  |                  |

### REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

### Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low Speed Enable Indicator bit

1 = Next token command to be executed at Low Speed

0 = Next token command to be executed at Full Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

| Bit<br>Range  | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|---------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24         | _                 | —                 | -                 | -                 | -                 | _                 | -                | -                |  |  |  |

| 22:16         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16         | _                 | —                 | _                 | _                 | _                 | —                 | -                | —                |  |  |  |

| 15:8          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0          | -                 | —                 | -                 | -                 | -                 | —                 |                  | —                |  |  |  |

| 7.0           | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0 FRML<7:0> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

### REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | -                 | -                 | -                 | -                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | -                 | -                 | -                 | -                 |                  | —                |

| 7:0          | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | _                 | _                 | USBSIDL           | USBSIDL           |                   | _                | UASUSPND         |

### REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test enabled

- 0 = Eye-Pattern Test disabled

### bit 6-5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

### bit 3 LSDEV: Low-Speed Device Enable bit

- 1 = USB module operates in Low-Speed Device mode only

- 0 = USB module operates in OTG, Host, or Full-Speed Device mode

- bit 2-1 Unimplemented: Read as '0'

### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock

### TABLE 14-1: WATCHDOG TIMER REGISTER MAP

| ess                        |                                 | e         |       | Bits  |       |       |       |       |      |      |      |                               |      |      |      |      |      |      |           |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------------------------------|------|------|------|------|------|------|-----------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6                          | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0000                       | WDTCON                          | 31:16     | —     | —     | —     | —     |       | —     | —    | —    | —    | —                             | —    | —    | —    | —    | -    | —    | 0000      |

| 0000                       | WDICON                          | 15:0      | ON    | —     | —     | —     | —     | —     | _    | —    | _    | SWDTPS<4:0> WDTWINEN WDTCLR 0 |      |      |      |      | 0000 |      |           |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

### 21.1 Control Registers

### TABLE 21-1: RTCC REGISTER MAP

| ess                         |           | 0     |        |       |         |          |            |            |                   |      | Bits       |          |        |       |         |            |         |       | 8         |

|-----------------------------|-----------|-------|--------|-------|---------|----------|------------|------------|-------------------|------|------------|----------|--------|-------|---------|------------|---------|-------|-----------|

| Virtual Address<br>(BF80_#) | 31        |       | 31/15  | 30/14 | 29/13   | 28/12    | 27/11      | 26/10      | 25/9              | 24/8 | 23/7       | 22/6     | 21/5   | 20/4  | 19/3    | 18/2       | 17/1    | 16/0  | All Reset |

| 0200                        | RTCCON    | 31:16 | _      | _     | _       | -        | _          | -          |                   |      |            |          | CAL<   | :9:0> |         |            |         |       | 0000      |

| 0200                        | RICCON    | 15:0  | ON     | _     | SIDL    | —        | _          | _          |                   | _    | RTSECSEL   | RTCCLKON | _      | _     | RTCWREN | RTCSYNC    | HALFSEC | RTCOE | 0000      |

| 0210                        | RTCALRM   | 31:16 | —      | _     |         | —        | -          |            |                   |      |            | -        |        | —     | —       | -          | -       | —     | 0000      |

| 0210                        | IN OALIN  | 15:0  | ALRMEN | CHIME | PIV     | ALRMSYNC |            | AMASI      | <b>&lt;</b> <3:0> |      |            |          |        | ARPT  | <7:0>   |            |         |       | 0000      |

| 0220                        | RTCTIME   | 31:16 |        | HR10  | 0<3:0>  |          |            | HR01       | <3:0>             |      | MIN10<3:0> |          |        |       |         | MIN01<3:0> |         |       | xxxx      |

| 0220                        | INTO THME | 15:0  |        | SEC1  | 0<3:0>  |          |            | SEC07      | 1<3:0>            |      | —          | —        | _      | —     | _       | —          | —       | _     | xx00      |

| 0230                        | RTCDATE   | 31:16 |        | YEAR  | 10<3:0> |          |            | YEAR0      | 1<3:0>            |      |            | MONTH10  | )<3:0> |       |         | MONTH      | 01<3:0> |       | xxxx      |

| 0230                        | RIODAIL   | 15:0  |        | DAY1  | 0<3:0>  |          |            | DAY01      | 1<3:0>            |      | —          | —        | _      | —     |         | WDAY0      | 1<3:0>  |       | xx00      |

| 0240                        | ALRMTIME  | 31:16 |        | HR10  | 0<3:0>  |          |            | HR01       | <3:0>             |      |            | MIN10<   | 3:0>   |       |         | MIN01      | <3:0>   |       | xxxx      |

| 0240                        |           | 15:0  |        | SEC1  | 0<3:0>  |          | SEC01<3:0> |            |                   | —    | —          | _        | —      | _     | —       | —          | _       | xx00  |           |

| 0250                        | ALRMDATE  | 31:16 | —      | _     | _       | _        |            |            |                   |      | MONTH10    | )<3:0>   |        |       | MONTH   | 01<3:0>    |         | 00xx  |           |

| 0200                        |           | 15:0  |        | DAY1  | 0<3:0>  |          |            | DAY01<3:0> |                   |      | _          | _        | _      | —     |         | WDAY0      | 1<3:0>  |       | xx0x      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC sample and hold amplifier is sampling

- 0 = The ADC sample/hold amplifier is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

Clearing this bit will not affect any operation in progress.

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

### TABLE 23-1: CAN1 REGISTER SUMMARY (CONTINUED)

| ess                         |                                 |               |       |                     |       |       |       |           |          | Bits      | ;      |        |        |       |          |           |              |                |            |

|-----------------------------|---------------------------------|---------------|-------|---------------------|-------|-------|-------|-----------|----------|-----------|--------|--------|--------|-------|----------|-----------|--------------|----------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14               | 29/13 | 28/12 | 27/11 | 26/10     | 25/9     | 24/8      | 23/7   | 22/6   | 21/5   | 20/4  | 19/3     | 18/2      | 17/1         | 16/0           | All Resets |

| B340                        | C1FIFOBA                        | 31:16<br>15:0 |       |                     |       |       |       |           |          | C1FIFOBA  | <31:0> |        |        |       |          |           |              |                | 0000       |

| B350                        | C1FIFOCONn                      | 31:16         |       | _                   |       | _     | _     | _         | _        | _         | —      | _      | _      |       | ŀ        | SIZE<4:0> |              |                | 0000       |

| D330                        | (n = 0-15)                      | 15:0          | _     | FRESET              | UINC  | DONLY | _     | —         | —        | —         | TXEN   | TXABAT | TXLARB | TXERR | TXREQ    | RTREN     | N TXPRI<1:0> |                | 0000       |

| B360                        | C1FIFOINTn                      | 31:16         | _     | -                   | -     | —     | —     | TXNFULLIE | TXHALFIE | TXEMPTYIE | —      | —      | —      | —     | RXOVFLIE | RXFULLIE  | RXHALFIE     | RXN<br>EMPTYIE | 0000       |

| B300                        | (n = 0-15)                      | 15:0          | _     | -                   | Ι     | -     | _     | TXNFULLIF | TXHALFIF | TXEMPTYIF | _      | —      | _      | —     | RXOVFLIF | RXFULLIF  | RXHALFIF     | RXN<br>EMPTYIF | 0000       |

| B370                        | C1FIFOUAn                       | 31:16         |       |                     |       |       |       |           |          |           | <21.0> |        |        |       |          |           |              |                | 0000       |

| 6370                        | (n = 0-15)                      | 15:0          |       | C1FIFOUA<31:0> 0000 |       |       |       |           |          |           |        |        |        |       | 0000     |           |              |                |            |

| B380                        | C1FIFOCIn                       | 31:16         |       | _                   | _     | _     |       | —         |          | _         | —      | —      | -      |       | _        | _         | _            |                | 0000       |

| 5300                        | (n = 0-15)                      | 15:0          | -     |                     |       |       |       |           |          |           |        |        |        |       |          |           |              |                |            |

Legend: Note 1 x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more 1: information.

## REGISTER 23-11: C1FLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED) bit 20-16 FSEL6<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 FLTEN5: Filter 17 Enable bit bit 15 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL5<1:0>: Filter 5 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL5<4:0>: FIFO Selection bits 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN4: Filter 4 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL4<1:0>: Filter 4 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected FSEL4<4:0>: FIFO Selection bits bit 4-0 11111 = Reserved 10000 = Reserved 01111 = Message matching filter is stored in FIFO buffer 15 00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | R/P              | R/P              |  |  |  |  |  |  |

| 31:24        |                   |                   | —                 | -                 | —                 | _                 | FWDTWI           | NSZ<1:0>         |  |  |  |  |  |  |

| 00.40        | R/P               | R/P               | r-1               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |  |  |

| 23:16        | FWDTEN            | WINDIS            | —                 |                   | WDTPS<4:0>        |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |  |  |  |  |  |  |

| 15:8         | FCKSM             | /<1:0>            | FPBDI             | V<1:0>            | —                 | OSCIOFNC          | POSCM            | OD<1:0>          |  |  |  |  |  |  |

| 7.0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P               | R/P              | R/P              |  |  |  |  |  |  |

| 7:0          | IESO —            |                   | FSOSCEN           | FSOSCEN —         |                   | — FNC             |                  | OSC<2:0>         |  |  |  |  |  |  |

### REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | r = Reserved bit P = Programmable bit |                          |                    |  |

|-------------------|---------------------------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-26 Reserved: Write '1'

bit 25-24 **FWDTWINSZ:** Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

### bit 23 FWDTEN: Watchdog Timer Enable bit

- 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

### bit 22 WINDIS: Watchdog Timer Window Enable bit

- 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

- bit 21 Reserved: Write '1'

### bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| ~ |                                                              |

|---|--------------------------------------------------------------|

|   | 10100 <b>= 1:1048576</b>                                     |

|   | 10011 <b>= 1:524288</b>                                      |

|   | 10010 <b>= 1:262144</b>                                      |

|   | 10001 <b>= 1:131072</b>                                      |

|   | 10000 <b>= 1:65536</b>                                       |

|   | 01111 <b>= 1:32768</b>                                       |

|   | 01110 <b>= 1:16384</b>                                       |

|   | 01101 <b>= 1:8192</b>                                        |

|   | 01100 <b>= 1:4096</b>                                        |

|   | 01011 <b>= 1:2048</b>                                        |

|   | 01010 <b>= 1:1024</b>                                        |

|   | 01001 <b>= 1:512</b>                                         |

|   | 01000 <b>= 1:256</b>                                         |

|   | 00111 <b>= 1:128</b>                                         |

|   | 00110 <b>= 1:64</b>                                          |

|   | 00101 <b>= 1:32</b>                                          |

|   | 00100 = 1:16                                                 |

|   | 00011 <b>= 1</b> :8                                          |

|   | 00010 = 1:4                                                  |

|   | 00001 <b>= 1:2</b>                                           |

|   | 00000 = 1:1                                                  |

|   | All other combinations not shown result in operation = 10100 |

|   | · ·                                                          |

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

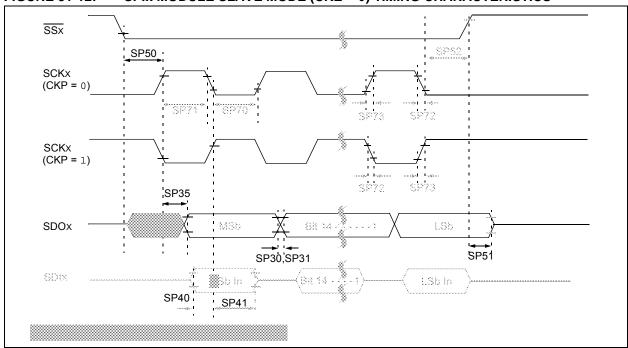

### FIGURE 31-12: SPIx MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

### TABLE 31-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIS             | TICS                                                         | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Indus<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-ten |                     |      |       |                    |  |

|---------------|-----------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                               | Min.                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                 | Tsck/2                                                                                                                                                                                                  | —                   | _    | ns    | —                  |  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                | TSCK/2                                                                                                                                                                                                  | _                   | _    | ns    | —                  |  |

| SP72          | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                                       | _                   | _    | ns    | See parameter DO32 |  |

| SP73          | TscR                  | SCKx Input Rise Time                                         | —                                                                                                                                                                                                       | —                   | _    | ns    | See parameter DO31 |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                          | —                                                                                                                                                                                                       | —                   | _    | ns    | See parameter DO32 |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                          | —                                                                                                                                                                                                       | _                   | _    | ns    | See parameter DO31 |  |

| SP35          | TSCH2DOV,             | SDOx Data Output Valid after                                 | —                                                                                                                                                                                                       | —                   | 15   | ns    | VDD > 2.7V         |  |

|               | TscL2DoV              | SCKx Edge                                                    | —                                                                                                                                                                                                       | —                   | 20   | ns    | VDD < 2.7V         |  |

| SP40          | TDIV2sCH,<br>TDIV2sCL | Setup Time of SDIx Data Input<br>to SCKx Edge                | 10                                                                                                                                                                                                      | _                   | _    | ns    | —                  |  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                 | 10                                                                                                                                                                                                      | _                   | _    | ns    | —                  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 175                                                                                                                                                                                                     | _                   | _    | ns    | —                  |  |

| SP51          | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 3)</b>       | 5                                                                                                                                                                                                       | —                   | 25   | ns    | —                  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | Тѕск + 20                                                                                                                                                                                               | _                   |      | ns    | —                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 50 ns.

4: Assumes 50 pF load on all SPIx pins.

### TABLE 31-34: ADC MODULE SPECIFICATIONS

|               |            | ACTERISTICS                                          | Standard Operating Conditions (see Note 5): 2.5V to 3.6V<br>(unless otherwise stated) |             |                                  |          |                                                                                               |  |  |  |  |  |

|---------------|------------|------------------------------------------------------|---------------------------------------------------------------------------------------|-------------|----------------------------------|----------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

|               |            | ACTERISTICS                                          | Operating te                                                                          | emperature  |                                  |          | C for Industrial<br>°C for V-temp                                                             |  |  |  |  |  |

| Param.<br>No. | Symbol     | Characteristics                                      | Min.                                                                                  | Typical     | Max.                             | Units    | Conditions                                                                                    |  |  |  |  |  |

| Device        | Supply     |                                                      |                                                                                       |             |                                  |          |                                                                                               |  |  |  |  |  |

| AD01          | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5                                                     | _           | Lesser of<br>VDD + 0.3 or<br>3.6 | V        | _                                                                                             |  |  |  |  |  |

| AD02          | AVss       | Module Vss Supply                                    | Vss                                                                                   | _           | AVdd                             | V        | (Note 1)                                                                                      |  |  |  |  |  |

| Referen       | ce Inputs  |                                                      |                                                                                       |             |                                  |          |                                                                                               |  |  |  |  |  |

| AD05<br>AD05a | Vrefh      | Reference Voltage High                               | AVss + 2.0<br>2.5                                                                     | _           | AVDD<br>3.6                      | V<br>V   | (Note 1)<br>VREFH = AVDD (Note 3)                                                             |  |  |  |  |  |

| AD06          | Vrefl      | Reference Voltage Low                                | AVss                                                                                  |             | Vrefh – 2.0                      | V        | (Note 1)                                                                                      |  |  |  |  |  |