Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 81                                                                                |

| Program Memory Size        | 256КВ (256К х 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx550f256lt-50i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)**

|                       | Pin Number             |                 |             |                |                                                                                                    |  |

|-----------------------|------------------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------|--|

| Pin Name              | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                        |  |

| VUSB3V3 <b>(2)</b>    | 35                     | 55              | Р           | —              | USB internal transceiver supply. If the USB module is not used, this pin must be connected to VDD. |  |

| VBUSON <sup>(2)</sup> | 11                     | 20              | 0           | —              | USB Host and OTG bus power control Output                                                          |  |

| D+ <sup>(2)</sup>     | 37                     | 57              | I/O         | Analog         | USB D+                                                                                             |  |

| D-(2)                 | 36                     | 56              | I/O         | Analog         | USB D-                                                                                             |  |

| USBID <sup>(2)</sup>  | 33                     | 51              | Ι           | ST             | USB OTG ID Detect                                                                                  |  |

| PGED1                 | 16                     | 25              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication<br>Channel 1                                  |  |

| PGEC1                 | 15                     | 24              | I           | ST             | Clock Input pin for Programming/Debugging Communication Channel 1                                  |  |

| PGED2                 | 18                     | 27              | I/O         | ST             | Data I/O Pin for Programming/Debugging Communication<br>Channel 2                                  |  |

| PGEC2                 | 17                     | 26              | I           | ST             | Clock Input Pin for Programming/Debugging Communication Channel 2                                  |  |

| PGED3                 | 13                     | 22              | I/O         | ST             | Data I/O Pin for Programming/Debugging Communication<br>Channel 3                                  |  |

| PGEC3                 | 14                     | 23              | I           | ST             | Clock Input Pin for Programming/Debugging Communication<br>Channel 3                               |  |

| CTED1                 | _                      | 17              | Ι           | ST             | CTMU External Edge Input 1                                                                         |  |

| CTED2                 |                        | 38              | I           | ST             | CTMU External Edge Input 2                                                                         |  |

| CTED3                 | 18                     | 27              | I           | ST             | CTMU External Edge Input 3                                                                         |  |

| CTED4                 | 22                     | 33              | Ι           | ST             | CTMU External Edge Input 4                                                                         |  |

| CTED5                 | 29                     | 43              | Ι           | ST             | CTMU External Edge Input 5                                                                         |  |

| CTED6                 | 30                     | 44              | Ι           | ST             | CTMU External Edge Input 6                                                                         |  |

| CTED7                 | _                      | 9               | Ι           | ST             | CTMU External Edge Input 7                                                                         |  |

| CTED8                 |                        | 92              | Ι           | ST             | CTMU External Edge Input 8                                                                         |  |

| CTED9                 |                        | 60              | Ι           | ST             | CTMU External Edge Input 9                                                                         |  |

| CTED10                | 21                     | 32              | Ι           | ST             | CTMU External Edge Input 10                                                                        |  |

| CTED11                | 23                     | 34              | Ι           | ST             | CTMU External Edge Input 11                                                                        |  |

| CTED12                | 15                     | 24              | Ι           | ST             | CTMU External Edge Input 12                                                                        |  |

| CTED13                | 14                     | 23              | Ι           | ST             | CTMU External Edge Input 13                                                                        |  |

| C1RX                  | PPS                    | PPS             | Ι           | ST             | Enhanced CAN Receive                                                                               |  |

| C1TX                  | PPS                    | PPS             | 0           | ST             | Enhanced CAN Transmit                                                                              |  |

**Legend:** CMOS = CMOS compatible input or output

P = Power

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer **Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module. 4: This pin is only available on 100-pin devices without a USB module.

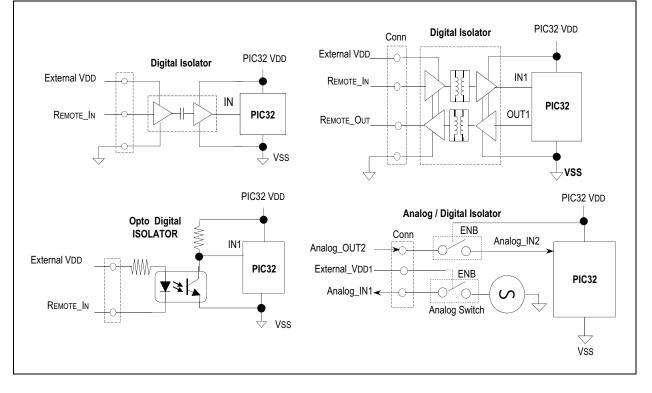

Without proper signal isolation, on non-5V tolerant pins, the remote signal can power the PIC32 device through the high side ESD protection diodes. Besides violating the absolute maximum rating specification when VDD of the PIC32 device is restored and ramping up or ramping down, it can also negatively affect the internal Power-on Reset (POR) and Brown-out Reset (BOR) circuits, which can lead to improper initialization of internal PIC32 logic circuits. In these cases, it is recommended to implement digital or analog signal isolation as depicted in Figure 2-6, as appropriate. This is indicative of all industry microcontrollers and not just Microchip products.

#### TABLE 2-1: EXAMPLES OF DIGITAL/ ANALOG ISOLATORS WITH OPTIONAL LEVEL TRANSLATION

| Example Digital/Analog<br>Signal Isolation Circuits | Inductive Coupling | Capacitive Coupling | Opto Coupling | Analog/Digital Switch |

|-----------------------------------------------------|--------------------|---------------------|---------------|-----------------------|

| ADuM7241 / 40 ARZ (1 Mbps)                          | Х                  |                     | _             |                       |

| ADuM7241 / 40 CRZ (25 Mbps)                         | Х                  |                     |               | _                     |

| IS0721                                              |                    | Х                   |               | _                     |

| LTV-829S (2 Channel)                                | _                  |                     | Х             | _                     |

| LTV-849S (4 Channel)                                | _                  |                     | Х             | _                     |

| FSA266 / NC7WB66                                    | _                  |                     |               | Х                     |

### FIGURE 2-6: DIGITAL/ANALOG SIGNAL ISOLATION CIRCUITS

| INE OID IE   | LEGISTER 9-12. DETROSTER DWA CHANNEL & SOURCE SIZE REGISTER |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7                                           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.04        | U-0                                                         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                                                           | —                 | _                 | _                 | —                 | —                 | —                | —                |

| 00.40        | U-0                                                         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                                                           | —                 | —                 | —                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0                                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                                                             | CHSSIZ<15:8>      |                   |                   |                   |                   |                  |                  |

| 7.0          | R/W-0                                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                                                             |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |

#### REGISTER 9-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

#### **REGISTER 9-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   | CHDSIZ<15:8>      |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| KE0131       | CEGISTER 10-1. OTOTGIR. 03B OTO INTERROPT STATUS REGISTER |                   |                   |                   |                   |                   |                  |                  |

|--------------|-----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7                                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0                                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                                                         | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0                                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                                                         | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 15:8         | U-0                                                       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                                                         | —                 | —                 |                   | -                 | _                 | -                | —                |

| 7.0          | R/WC-0, HS                                                | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7:0          | IDIF                                                      | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |

#### REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable   | bit                |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIF: ID State Change Indicator bit

- 1 = Change in ID state detected

- 0 = No change in ID state detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1millisecond, but different from last time

- 0 = USB line state has not been stable for 1 millisecond

#### bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = Change on the session valid input detected

- 0 = No change on the session valid input detected

#### REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   |                   | —                 |                   | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   | —                 |                   |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | _                 | _                 |                   |                   | —                 |                   | _                | —                |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7.0          |                   | ENDP              | T<3:0>            |                   | DIR               | PPBI              |                  | —                |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the BDT, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last BD Direction Indicator bit

- 1 = Last transaction was a transmit transfer (TX)

- 0 = Last transaction was a receive transfer (RX)

- bit 2 **PPBI:** Ping-Pong BD Pointer Indicator bit

- 1 = The last transaction was to the ODD BD bank

- 0 = The last transaction was to the EVEN BD bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF bit (U1IR<3>) is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

| TABLE 11-2: | OUTPUT PIN SELECTION |

|-------------|----------------------|

|-------------|----------------------|

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection |

|----------------------|----------|-------------|---------------------------------------|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                     |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = <u>U3TX</u>                    |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved       |

| RPD10                | RPD10R   | RPD10R<3:0> | 0100 = Reserved                       |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                       |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                           |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved                       |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 - Reserved                       |

| RPB5 <sup>(7)</sup>  | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                       |

| RPC1 <sup>(3)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 = OC3                            |

| RPD14 <sup>(3)</sup> | RPD14R   | RPD14R<3:0> |                                       |

| RPG1 <sup>(3)</sup>  | RPG1R    | RPG1R<3:0>  | 1110 = SDO3                           |

| RPA14 <sup>(3)</sup> | RPA14R   | RPA14R<3:0> | 1111 = SDO4 <sup>(3)</sup>            |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                     |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 = U2TX                           |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                       |

| RPD11                | RPD11R   | RPD11R<3:0> |                                       |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0101 = Reserved                       |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = SDO2                           |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                       |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 <b>= SDO1</b>                    |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                       |

| RPF3 <sup>(4)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved<br>1011 = OC4         |

| RPC4 <sup>(3)</sup>  | RPC4R    | RPC4R<3:0>  | 1100 = Reserved                       |

| RPD15 <sup>(3)</sup> | RPD15R   | RPD15R<3:0> | 1101 = C3OUT                          |

| RPG0 <sup>(3)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 <b>=</b> SDO3                    |

| RPA15 <sup>(3)</sup> | RPA15R   | RPA15R<3:0> | 1111 = SDO4 <sup>(3)</sup>            |

**Note 1:** This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin devices.

4: This selection is not available when USBID functionality is used on USB devices.

5: This selection is not available on devices without a CAN module.

6: This selection is not available on USB devices.

7: This selection is not available when VBUSON functionality is used on USB devices.

| bit 8   | ER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)<br>PTRDEN: Read/Write Strobe Port Enable bit |

|---------|---------------------------------------------------------------------------------------------------------|

|         | 1 = PMRD/PMWR port enabled                                                                              |

|         | 0 = PMRD/PMWR port disabled                                                                             |

| bit 7-6 | CSF<1:0>: Chip Select Function bits <sup>(2)</sup>                                                      |

|         | 11 = Reserved                                                                                           |

|         | 10 = PMCS1 and PMCS2 function as Chip Select                                                            |

|         | 01 = PMCS1 functions as address bit 14; PMCS2 functions as Chip Select                                  |

|         | 00 = PMCS1 and PMCS2 function as address bits 14 and 15, respectively                                   |

| bit 5   | ALP: Address Latch Polarity bit <sup>(2)</sup>                                                          |

|         | <ul> <li>1 = Active-high (PMALL and PMALH)</li> <li>0 = Active-low (PMALL and PMALH)</li> </ul>         |

| bit 4   | CS2P: Chip Select 0 Polarity bit <sup>(2)</sup>                                                         |

|         | 1 = Active-high (PMCS2)                                                                                 |

|         | $0 = \text{Active-low}(\overline{\text{PMCS2}})$                                                        |

| bit 3   | CS1P: Chip Select 0 Polarity bit <sup>(2)</sup>                                                         |

|         | 1 = Active-high (PMCS1)                                                                                 |

|         | $0 = \text{Active-low}(\overline{\text{PMCS1}})$                                                        |

| bit 2   | Unimplemented: Read as '0'                                                                              |

| bit 1   | WRSP: Write Strobe Polarity bit                                                                         |

|         | For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):                                               |

|         | 1 = Write strobe active-high (PMWR)                                                                     |

|         | 0 = Write strobe active-low (PMWR)                                                                      |

|         | For Master mode 1 (MODE<1:0> = $11$ ):                                                                  |

|         | 1 = Enable strobe active-high (PMENB)                                                                   |

|         | 0 = Enable strobe active-low (PMENB)                                                                    |

| bit 0   | RDSP: Read Strobe Polarity bit                                                                          |

|         | For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):                                               |

|         | 1 = Read Strobe active-high (PMRD)                                                                      |

|         | 0 = Read Strobe active-low (PMRD)                                                                       |

|         | For Master mode 1 (MODE<1:0> = 11):                                                                     |

|         | 1 = Read/write strobe active-high (PMRD/PMWR)                                                           |

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

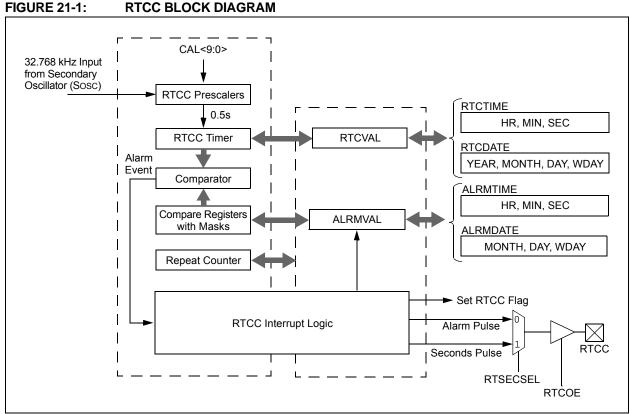

#### 21.0 **REAL-TIME CLOCK AND** CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available the Microchip web from site (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time.

The following are the key features of this module:

- · Time: hours. minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- · Provides calendar: Weekday, date, month and year

- · Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- · User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- · Requirements: External 32.768 kHz clock crystal

- · Alarm pulse or seconds clock output on RTCC pin

### RTCC BLOCK DIAGRAM

### 21.1 Control Registers

#### TABLE 21-1: RTCC REGISTER MAP

| ess                         |                                 | 0              |        |       |         |          |            |            |        | l     | Bits       |          |       |      |              |         |         |       | s         |

|-----------------------------|---------------------------------|----------------|--------|-------|---------|----------|------------|------------|--------|-------|------------|----------|-------|------|--------------|---------|---------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range      | 31/15  | 30/14 | 29/13   | 28/12    | 27/11      | 26/10      | 25/9   | 24/8  | 23/7       | 22/6     | 21/5  | 20/4 | 19/3         | 18/2    | 17/1    | 16/0  | All Reset |

| 0200                        | RTCCON                          | 31:16          | _      | _     |         | —        | _          |            |        |       |            |          | CAL<  | 9:0> |              |         |         |       | 0000      |

| 0200                        | RICCON                          | 15:0           | ON     | _     | SIDL    | —        | _          | _          |        | —     | RTSECSEL   | RTCCLKON | _     | _    | RTCWREN      | RTCSYNC | HALFSEC | RTCOE | 0000      |

| 0210                        | RTCALRM                         | 31:16          | —      | _     | _       | —        | _          | _          |        | —     | _          | —        | _     | _    | —            | —       | —       | —     | 0000      |

| 0210                        | RICALKI                         | 15:0           | ALRMEN | CHIME | PIV     | ALRMSYNC |            | AMASK<3:0> |        |       | ARPT<7:0>  |          |       |      |              |         | 0000    |       |           |

| 0220                        | RTCTIME                         | 31:16          |        | HR10  | 0<3:0>  |          |            | HR01       | <3:0>  |       | MIN10<3:0> |          |       |      | MIN01<3:0>   |         |         | xxxx  |           |

| 0220                        | INTO THME                       | 15:0           |        | SEC1  | 0<3:0>  |          | SEC01<3:0> |            |        | _     | —          | _        | _     | —    | —            | —       | —       | xx00  |           |

| 0230                        | RTCDATE                         | 31:16          |        | YEAR  | 10<3:0> |          |            | YEAR0      | 1<3:0> |       |            | MONTH10  | <3:0> |      | MONTH01<3:0> |         |         |       | xxxx      |

| 0230                        | RIODAIL                         | 15:0           |        | DAY1  | 0<3:0>  |          |            | DAY01      | 1<3:0> |       | _          | —        | _     | _    |              | WDAY0   | 1<3:0>  |       | xx00      |

| 0240                        | ALRMTIME                        | 31:16          |        | HR10  | 0<3:0>  |          |            | HR01       | <3:0>  |       |            | MIN10<   | 3:0>  |      |              | MIN01   | <3:0>   |       | xxxx      |

| 0240                        |                                 | 15:0           |        | SEC1  | 0<3:0>  |          | SEC01<3:0> |            |        | _     | —          | _        | _     | —    | —            | —       | —       | xx00  |           |

| 0250                        |                                 | ALRMDATE 31:16 |        | —     |         | MONTH10  | <3:0>      |            |        | MONTH | 01<3:0>    |          | 00xx  |      |              |         |         |       |           |

| 0200                        |                                 |                |        |       | —       | —        | _          | _          |        | WDAY0 | 1<3:0>     |          | xx0x  |      |              |         |         |       |           |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

#### REGISTER 23-1: C1CON: CAN MODULE CONTROL REGISTER (CONTINUED)

| bit 13   | SIDLE: CAN Stop in Idle bit                                                                                                             |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul><li>1 = CAN Stops operation when system enters Idle mode</li><li>0 = CAN continues operation when system enters Idle mode</li></ul> |

| bit 12   | Unimplemented: Read as '0'                                                                                                              |

| bit 11   | CANBUSY: CAN Module is Busy bit                                                                                                         |

|          | 1 = The CAN module is active                                                                                                            |

|          | 0 = The CAN module is completely disabled                                                                                               |

| bit 10-5 | Unimplemented: Read as '0'                                                                                                              |

### bit 4-0 **DNCNT<4:0>:** Device Net Filter Bit Number bits

10011-11111 = Invalid Selection (compare up to 18-bits of data with EID) 10010 = Compare up to data byte 2 bit 6 with EID17 (C1RXFn<17>)

•

-

00001 = Compare up to data byte 0 bit 7 with EID0 (C1RXFn<0>) 00000 = Do not compare data bytes

**Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

#### REGISTER 23-2: C1CFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

- bit 10-8 **PRSEG<2:0>:** Propagation Time Segment bits<sup>(4)</sup> 111 = Length is  $8 \times TQ$  $000 = \text{Length is } 1 \times TQ$ SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup> bit 7-6 11 = Length is  $4 \times TQ$  $10 = \text{Length is } 3 \times TQ$ 01 = Length is 2 x TQ  $00 = \text{Length is } 1 \times TQ$ bit 5-0 BRP<5:0>: Baud Rate Prescaler bits 111111 = Tq = (2 x 64)/SYSCLK 111110 = TQ = (2 x 63)/SYSCLK • 000001 = TQ = (2 x 2)/SYSCLK  $000000 = TQ = (2 \times 1)/SYSCLK$ Note 1: SEG2PH  $\leq$  SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. 2: 3 Time bit sampling is not allowed for BRP < 2.

- **3:** SJW  $\leq$  SEG2PH.

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

| REGISTE   | R 23-10: C1FLTCON0: CAN FILTER CONTROL REGISTER 0 (CONTINUED)                               |

|-----------|---------------------------------------------------------------------------------------------|

| bit 20-16 | FSEL2<4:0>: FIFO Selection bits                                                             |

|           | 11111 = Reserved                                                                            |

|           |                                                                                             |

|           |                                                                                             |

|           | 10000 = Reserved                                                                            |

|           | 01111 = Message matching filter is stored in FIFO buffer 15                                 |

|           | •                                                                                           |

|           | •                                                                                           |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                  |

| bit 15    | FLTEN1: Filter 1 Enable bit                                                                 |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                             |

| bit 14-13 | MSEL1<1:0>: Filter 1 Mask Select bits                                                       |

|           | 11 = Acceptance Mask 3 selected                                                             |

|           | 10 = Acceptance Mask 2 selected                                                             |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                          |

| bit 12-8  | FSEL1<4:0>: FIFO Selection bits                                                             |

| DIL 12-0  | 11111 = Reserved                                                                            |

|           | •                                                                                           |

|           |                                                                                             |

|           | •<br>10000 = Reserved                                                                       |

|           | 01111 = Message matching filter is stored in FIFO buffer 15                                 |

|           | •                                                                                           |

|           | •                                                                                           |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                  |

| bit 7     | FLTEN0: Filter 0 Enable bit                                                                 |

|           | 1 = Filter is enabled                                                                       |

|           | 0 = Filter is disabled                                                                      |

| bit 6-5   | MSEL0<1:0>: Filter 0 Mask Select bits                                                       |

|           | 11 = Acceptance Mask 3 selected                                                             |

|           | 10 = Acceptance Mask 2 selected                                                             |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                          |

| bit 4-0   | <b>FSEL0&lt;4:0&gt;:</b> FIFO Selection bits                                                |

|           | 11111 = Reserved                                                                            |

|           | •                                                                                           |

|           |                                                                                             |

|           | •<br>10000 = Reserved                                                                       |

|           | 01111 = Message matching filter is stored in FIFO buffer 15                                 |

|           | •                                                                                           |

|           |                                                                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                  |

| Netar     | The bits in this register can only be medified if the corresponding filter enable (ELTEN) b |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                   | —                 | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 10.0         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | —                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

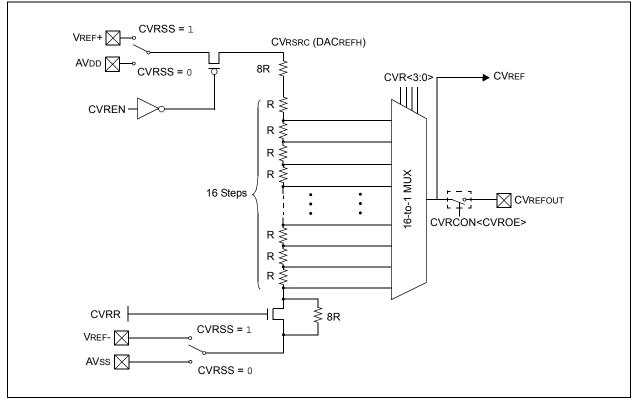

### 25.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

This data sheet summarizes the features Note: of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 25-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The CVREF module has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

#### FIGURE 25-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

#### 26.1 Control Registers

#### TABLE 26-1: CTMU REGISTER MAP

| ess                      | Bits                            |           |         |         |          |       |         |          |          |          |         | s       |       |       |          |      |      |       |           |

|--------------------------|---------------------------------|-----------|---------|---------|----------|-------|---------|----------|----------|----------|---------|---------|-------|-------|----------|------|------|-------|-----------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11   | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5  | 20/4  | 19/3     | 18/2 | 17/1 | 16/0  | All Reset |

| 1 200                    | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | EL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |       | EDG25 | SEL<3:0> |      |      |       | 0000      |

| A200                     | CINUCON                         | 15:0      | ON      | -       | CTMUSIDL | TGEN  | EDGEN   | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM | <5:0> |          |      | IRNG | <1:0> | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### 29.0 INSTRUCTION SET

The PIC32MX1XX/2XX/5XX 64/100-pin family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to *"MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set"* at www.imgtec.com for more information.

| TABLE 31-5: | DC CHARACTERISTICS: OPERATING CURRENT (IDD) |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| DC CHARA         | CTERISTICS             | 5              | (unless other    | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |             |  |  |  |

|------------------|------------------------|----------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| Parameter<br>No. | Typical <sup>(3)</sup> | Max.           | Units Conditions |                                                                                                                                                                                                    |             |  |  |  |

| Operating (      | Current (IDD)          | (Notes 1, 2, 5 | )                |                                                                                                                                                                                                    |             |  |  |  |

| DC20             | 2                      | 8              | mA               | 4 MF                                                                                                                                                                                               | lz (Note 4) |  |  |  |

| DC21             | 7                      | 13             | mA               | 1                                                                                                                                                                                                  | 0 MHz       |  |  |  |

| DC22             | 10                     | 18             | mA               | 20 MI                                                                                                                                                                                              | Hz (Note 4) |  |  |  |

| DC23             | 15                     | 25             | mA               | 30 MHz (Note 4)                                                                                                                                                                                    |             |  |  |  |

| DC24             | 20                     | 32             | mA               | 40 MHz                                                                                                                                                                                             |             |  |  |  |

| DC25             | 180                    | 250            | μA               | +25°C, 3.3V LPRC (31 kHz) (Note 4)                                                                                                                                                                 |             |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in the "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

#### TABLE 31-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CH4        | ARACTERIS | TICS                                                   |                        | (unless          | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |   |     |                                     |                       |  |  |

|---------------|-----------|--------------------------------------------------------|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------------------------------------|-----------------------|--|--|

| Param.<br>No. | Symbol    | Cha                                                    | racteristic            | s <sup>(1)</sup> | s <sup>(1)</sup> Min.                                                                                                                                                                              |   |     | Conditions                          |                       |  |  |

| TB10          | Т⊤хН      | TxCK<br>High Time                                      | Synchron<br>prescaler  | ous, with        | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns                                                                                                                                                                  | — | ns  | Must also meet<br>parameter<br>TB15 | value<br>(1, 2, 4, 8, |  |  |

| TB11          | ΤτχL      | TxCK<br>Low Time                                       | Synchron<br>prescaler  | ous, with        | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns                                                                                                                                                                  | _ | ns  | Must also meet<br>parameter<br>TB15 | 16, 32, 64,<br>256)   |  |  |

| TB15          | ΤτχΡ      | TxCK<br>Input                                          | Synchrono<br>prescaler | ous, with        | [(Greater of [(25 ns or<br>2 Трв)/N] + 30 ns                                                                                                                                                       | _ | ns  | VDD > 2.7V                          |                       |  |  |

|               |           | Period                                                 |                        |                  | [(Greater of [(25 ns or<br>2 Трв)/N] + 50 ns                                                                                                                                                       |   | ns  | VDD < 2.7V                          |                       |  |  |

| TB20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer Increr |                        |                  | —                                                                                                                                                                                                  | 1 | Трв | _                                   |                       |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

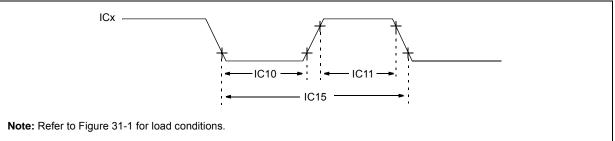

#### FIGURE 31-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

#### TABLE 31-25: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHA        | RACTERI | STICS                          | (unless oth | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                                         |                                  |  |  |  |

|---------------|---------|--------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------------|----------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup> |             | Min.                                                                                                                                                                                                                                                                                  | Max. | Units | Conditions                              |                                  |  |  |  |

| IC10          | TccL    | ICx Input                      | Low Time    | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                                                                                                     | _    | ns    | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |  |  |  |

| IC11          | ТссН    | ICx Input                      | t High Time | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                                                                                                     | _    | ns    | Must also<br>meet<br>parameter<br>IC15. |                                  |  |  |  |

| IC15          | TCCP    | ICx Input                      | Period      | [(25 ns or 2 Трв)/N]<br>+ 50 ns                                                                                                                                                                                                                                                       | —    | ns    | —                                       |                                  |  |  |  |

| Note 1: | These parameters are | characterized, but not | t tested in manufacturing. |

|---------|----------------------|------------------------|----------------------------|

|         |                      |                        |                            |

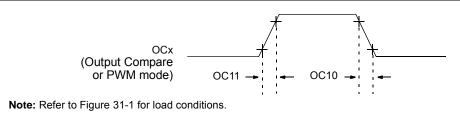

#### FIGURE 31-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 31-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |       |                    |  |  |

|--------------------|--------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| OC10               | TccF   | OCx Output Fall Time           | —                                                                                                                                                                                                                                                                                     | —                      | _    | ns    | See parameter DO32 |  |  |

| OC11               | TccR   | OCx Output Rise Time           | —                                                                                                                                                                                                                                                                                     | —                      | —    | ns    | See parameter DO31 |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

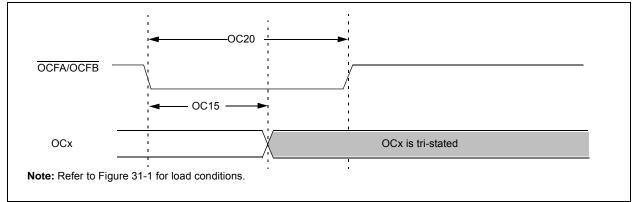

#### FIGURE 31-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 31-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |     |       |            |  |  |

|--------------------|--------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-------|------------|--|--|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup> | Min                                                                                                                                                                                                                                                                                   | Typical <sup>(2)</sup> | Max | Units | Conditions |  |  |

| OC15               | Tfd    | Fault Input to PWM I/O Change  | —                                                                                                                                                                                                                                                                                     | —                      | 50  | ns    | _          |  |  |

| OC20               | TFLT   | Fault Input Pulse Width        | 50                                                                                                                                                                                                                                                                                    | —                      |     | ns    | —          |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

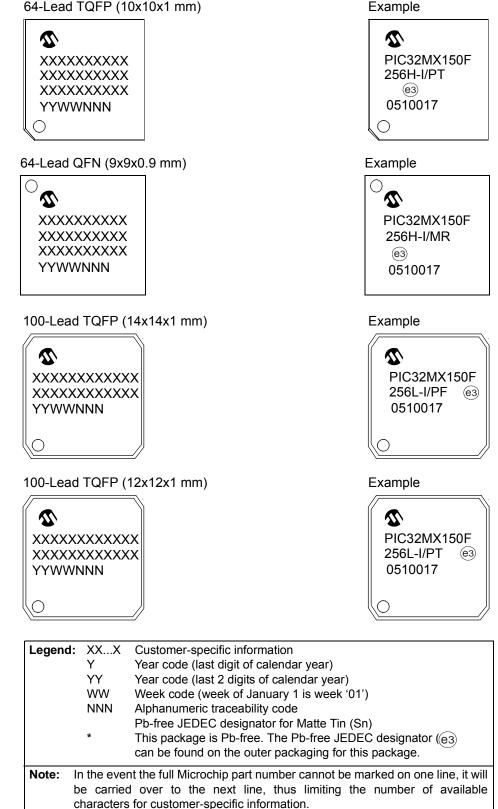

#### 34.0 **PACKAGING INFORMATION**

#### 34.1 **Package Marking Information**

64-Lead TQFP (10x10x1 mm)