Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| /oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx550f256lt-i-pt |

#### TABLE 3: PIN NAMES FOR 64-PIN USB DEVICES

64-PIN QFN<sup>(4)</sup> AND TQFP (TOP VIEW)

PIC32MX230F128H PIC32MX530F128H PIC32MX250F256H PIC32MX550F256H PIC32MX270F512H PIC32MX570F512H

QFN<sup>(4)</sup>

TQFP

| Pin# | Full Pin Name                             |

|------|-------------------------------------------|

| 1    | AN22/RPE5/PMD5/RE5                        |

| 2    | AN23/PMD6/RE6                             |

| 3    | AN27/PMD7/RE7                             |

| 4    | AN16/C1IND/RPG6/SCK2/PMA5/RG6             |

| 5    | AN17/C1INC/RPG7/PMA4/RG7                  |

| _    | A 1 1 4 2 1 2 2 1 2 1 2 1 2 2 2 2 2 2 2 2 |

| 5  | AN17/C1INC/RPG7/PMA4/RG7                  |

|----|-------------------------------------------|

| 6  | AN18/C2IND/RPG8/PMA3/RG8                  |

| 7  | MCLR                                      |

| 8  | AN19/C2INC/RPG9/PMA2/RG9                  |

| 9  | Vss                                       |

| 10 | VDD                                       |

| 11 | AN5/C1INA/RPB5/VBUSON/RB5                 |

| 12 | AN4/C1INB/RB4                             |

| 13 | PGED3/AN3/C2INA/RPB3/RB3                  |

| 14 | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2     |

| 15 | PGEC1/VREF-/AN1/RPB1/CTED12/RB1           |

| 16 | PGED1/VREF+/AN0/RPB0/PMA6/RB0             |

| 17 | PGEC2/AN6/RPB6/RB6                        |

| 18 | PGED2/AN7/RPB7/CTED3/RB7                  |

| 19 | AVDD                                      |

| 20 | AVss                                      |

| 21 | AN8/RPB8/CTED10/RB8                       |

| 22 | AN9/RPB9/CTED4/PMA7/RB9                   |

| 23 | TMS/CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| Pin # | Full Pin Name         |

|-------|-----------------------|

| 33    | USBID/RPF3/RF3        |

| 34    | VBUS                  |

| 35    | Vusb3v3               |

| 36    | D-                    |

| 37    | D+                    |

| 38    | VDD                   |

| 39    | OSC1/CLKI/RC12        |

| 40    | OSC2/CLKO/RC15        |

| 41    | Vss                   |

| 42    | RPD8/RTCC/RD8         |

| 43    | RPD9/SDA1/RD9         |

| 44    | RPD10/SCL1/PMA15/RD10 |

| 45    | RPD11/PMA14/RD11      |

| 46    | RPD0/INT0/RD0         |

| 47    | SOSCI/RPC13/RC13      |

| 48    | SOSCO/RPC14/T1CK/RC14 |

| 49    | AN24/RPD1/RD1         |

| 50    | AN25/RPD2/SCK1/RD2    |

| 51    | AN26/C3IND/RPD3/RD3   |

| 52    | RPD4/PMWR/RD4         |

| 53    | RPD5/PMRD/RD5         |

| 54    | C3INC/RD6             |

| 55    | C3INB/RD7             |

| 56    | VCAP                  |

| 57    | VDD                   |

| 58    | C3INA/RPF0/RF0        |

| 59    | RPF1/RF1              |

| 60    | PMD0/RE0              |

| 61    | PMD1/RE1              |

| 62    | AN20/PMD2/RE2         |

| 63    | RPE3/CTPLS/PMD3/RE3   |

| 64    | AN21/PMD4/RE4         |

32 Note

24

25 26

27

28

30

Vss

VDD

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 11.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

AN14/RPB14/SCK3/CTED5/PMA1/RB14 AN15/RPB15/OCFB/CTED6/PMA0/RB15

TDO/AN11/PMA12/RB11

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/RB13

RPF4/SDA2/PMA9/RF4 RPF5/SCL2/PMA8/RF5

4: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

#### REGISTER 6-4: NVMDATA: FLASH PROGRAM DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        |                   |                   |                   | NVMDA             | TA<31:24>         |                   |                  |                  |  |  |  |  |  |

| 22.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | NVMDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | NVMD              | ATA<7:0>          |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

**Note:** The bits in this register are only reset by a Power-on Reset (POR).

#### REGISTER 6-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | NVMSRCADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

#### REGISTER 9-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | _                          | _                 | _                 | _                 |                   | _                 | _                | _                |  |  |  |  |

| 22:46        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15:8         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 13.6         | CHSIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |  |

| 7.0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN            |                   | -                | _                |  |  |  |  |

Legend:S = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-16 CHAIRQ<7:0>: Channel Transfer Abort IRQ bits(1)

11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag

•

•

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag

00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits(1)

11111111 = Interrupt 255 will initiate a DMA transfer

•

00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

bit 6 CABORT: DMA Abort Transfer bit

1 = A DMA transfer is aborted when this bit is written to a '1'

0 = This bit always reads '0'

bit 5 PATEN: Channel Pattern Match Abort Enable bit

1 = Abort transfer and clear CHEN on pattern match

0 = Pattern match is disabled

bit 4 SIRQEN: Channel Start IRQ Enable bit

1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

0 = Interrupt number CHSIRQ is ignored and does not start a transfer

bit 3 AIRQEN: Channel Abort IRQ Enable bit

1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

bit 2-0 Unimplemented: Read as '0'

Note 1: See Table 5-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

#### REGISTER 9-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

111111111111111 = 65,535 byte source size

:

•

0000000000000010 = 2 byte source size

00000000000000001 = 1 byte source size

0000000000000000 = 65,536 byte source size

#### REGISTER 9-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | •                 |                   | CHDSIZ            | ·<7:0>            |                   | •                |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDSIZ<15:0>: Channel Destination Size bits

111111111111111 = 65,535 byte destination size

•

0000000000000001 = 1 byte destination size

0000000000000000 = 65,536 byte destination size

PORTC REGISTER MAP FOR 64-PIN DEVICES ONLY **TABLE 11-6:**

| ess                         |                                 | •         |           |           |           |           |       |       |      | Bits |      |      |      |      |         |         |         |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|------|---------|---------|---------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3    | 18/2    | 17/1    | 16/0 | All<br>Resets |

| 6200                        | ANGELO                          | 31:16     | _         |           |           | _         |       | _     |      | _    | _    | _    | _    |      | _       | _       | _       | _    | 0000          |

| 0200                        | 6200 ANSELC                     | 15:0      | _         |           |           | _         |       | _     |      | _    | _    | _    | _    | _    | ANSELC3 | ANSELC2 | ANSELC1 | _    | 000E          |

| 6210                        | TRISC                           | 31:16     | _         |           |           | _         |       | _     |      | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0210                        | TRISC                           | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | -     | _     | -    | _    | _    | _    | _    | -    | _       | _       | _       | _    | F000          |

| 6220                        | PORTC                           | 31:16     | _         | _         | _         | _         |       |       |      |      | _    |      | _    | _    | _       | _       | _       |      | 0000          |

| 0220                        | 10110                           | 15:0      | RC15      | RC14      | RC13      | RC12      | -     | _     | -    | _    | _    | _    | _    | -    | _       | _       | _       | _    | xxxx          |

| 6230                        | LATC                            | 31:16     | _         | _         | _         | _         | _     |       |      |      | _    |      | _    |      | _       | _       | _       |      | 0000          |

| 0200                        | Dilo                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       |      | xxxx          |

| 6240                        | ODCC                            | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       |      | 0000          |

| 0240                        | 0000                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       |      | 0000          |

| 6250                        | CNPUC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0200                        | 0141 00                         | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 6260                        | CNPDC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0200                        | ON BO                           | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 6270                        | CNCONC                          | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0270                        | 01100110                        | 15:0      | ON        | _         | SIDL      | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 6280                        | CNENC                           | 31:16     | _         | _         |           | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       |      | 0000          |

| 0200                        | CHENO                           | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 6290                        | CNSTATC                         | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

| 0200                        | 5290 CNSTATC                    | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     | _     | _    | _    | _    | _    | _    | _    | _       | _       | _       | _    | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for Note 1: more information.

#### REGISTER 17-1: SPIXCON: SPI CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |  |  |  |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|--|--|--|

| 31:24        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |  |

| 31.24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | FRMCNT<2:0>       |                  |                       |  |  |  |

| 22:46        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |  |  |  |

| 23:16        | MCLKSEL <sup>(2)</sup> | _                  | _                 | _                 |                   | _                 | SPIFE            | ENHBUF <sup>(2)</sup> |  |  |  |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |  |

| 15:8         | ON <sup>(1)</sup>      | _                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |  |  |  |

| 7:0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |  |

| 7:0          | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXISEL<1:0>     |                       |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FRMEN: Framed SPI Support bit

1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

bit 30 FRMSYNC: Frame Sync Pulse Direction Control on SSx pin bit (Framed SPI mode only)

1 = Frame sync pulse input (Slave mode)

0 = Frame sync pulse output (Master mode)

bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

1 = Frame pulse is active-high

0 = Frame pulse is active-low

bit 28 MSSEN: Master Mode Slave Select Enable bit

1 = Slave select SPI support enabled. The  $\overline{SS}$  pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

0 = Slave select SPI support is disabled.

bit 27 FRMSYPW: Frame Sync Pulse Width bit

1 = Frame sync pulse is one character wide

0 = Frame sync pulse is one clock wide

bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED SYNC mode.

111 = Reserved: do not use

110 = Reserved; do not use

101 = Generate a frame sync pulse on every 32 data characters

100 = Generate a frame sync pulse on every 16 data characters

011 = Generate a frame sync pulse on every 8 data characters

010 = Generate a frame sync pulse on every 4 data characters

001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character

bit 23 MCLKSEL: Master Clock Enable bit<sup>(2)</sup>

1 = REFCLK is used by the Baud Rate Generator

0 = PBCLK is used by the Baud Rate Generator

#### bit 22-18 Unimplemented: Read as '0'

**Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit can only be written when the ON bit = 0.

**3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

**4:** When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

#### REGISTER 17-3: SPIXSTAT: SPI STATUS REGISTER (CONTINUED)

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit

1 = Transmit buffer, SPIxTXB is empty

0 = Transmit buffer, SPIxTXB is not empty

Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

bit 2 Unimplemented: Read as '0'

bit 1 SPITBF: SPI Transmit Buffer Full Status bit

1 = Transmit not yet started, SPITXB is full

0 = Transmit buffer is not full

Standard Buffer Mode:

Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR.

Enhanced Buffer Mode:

Set when CWPTR + 1 = SRPTR; cleared otherwise

bit 0 SPIRBF: SPI Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB.

Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

### REGISTER 18-1: $12CxCON: 1^2C'x' CONTROL REGISTER ('x' = 1 AND 2)$

|              |                               |       |                                             |           | ,                 |                   |                  |                  |

|--------------|-------------------------------|-------|---------------------------------------------|-----------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit Bit 31/23/15/7 30/22/14/6 |       | Bit Bit Bit 29/21/13/5 28/20/12/4 27/19/11/ |           | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0                           | U-0   | U-0                                         | U-0       | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                             | _     | _                                           | _         | _                 | _                 | _                | _                |

| 22.40        | U-0                           | U-0   | U-0                                         | U-0       | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                             | _     | _                                           | _         | _                 | _                 | _                | _                |

| 45.0         | R/W-0                         | U-0   | R/W-0                                       | R/W-1, HC | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup>             | _     | SIDL                                        | SCLREL    | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0                         | R/W-0 | R/W-0                                       | R/W-0, HC | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN                          | STREN | ACKDT                                       | ACKEN     | RCEN              | PEN               | RSEN             | SEN              |

**Legend:** HC = Cleared in Hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: I<sup>2</sup>C Enable bit<sup>(1)</sup>

1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

$0 = \text{Disables the } 1^2\text{C module}$ ; all  $1^2\text{C pins are controlled by PORT functions}$

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

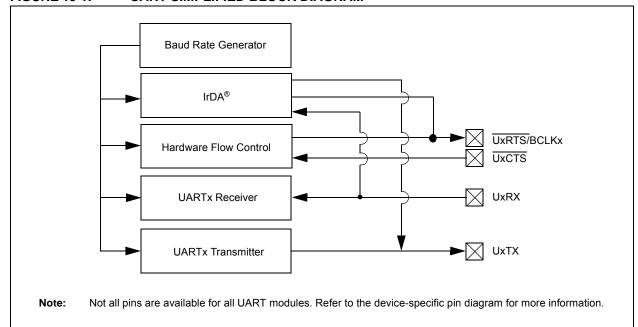

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 21.** "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX/5XX 64/100-pin family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN and IrDA®. The module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, odd or no parity options (for 8-bit data)

- · One or two Stop bits

- · Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- · 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9<sup>th</sup> bit = 1)

- · Separate transmit and receive interrupts

- · Loopback mode for diagnostic support

- · LIN Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the

FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                    | _                 | _                 | _                 | _                 | -                | _                |  |

| 00.40        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | _                    | _                 | _                 | _                 | _                 | _                | _                |  |

| 45.0         | R-0               | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.8         | 15:8 BUSY         |                      | <1:0>             | INCM              | <1:0>             | MODE16            | MODE             | E<1:0>           |  |

| 7.0          | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | WAITB             | <1:0> <sup>(1)</sup> |                   | WAITM             | <3:0>(1)          |                   | WAITE<1:0>(1)    |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **BUSY:** Busy bit (Master mode only)

1 = Port is busy

0 = Port is not busy

bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

11 = Reserved, do not use

10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

01 = Interrupt generated at the end of the read/write cycle

00 = No Interrupt generated

bit 12-11 INCM<1:0>: Increment Mode bits

11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

10 = Decrement ADDR<15:0> by 1 every read/write cycle<sup>(2)</sup>

01 = Increment ADDR<15:0> by 1 every read/write cycle(2)

00 = No increment or decrement of address

bit 10 MODE16: 8/16-bit Mode bit

1 = 16-bit mode: a read or write to the data register invokes a single 16-bit transfer

0 = 8-bit mode: a read or write to the data register invokes a single 8-bit transfer

bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

11 = Master mode 1 (PMCSx, PMRD/PMWR, PMENB, PMA<x:0>, PMD<7:0> and PMD<8:15>(3))

10 = Master mode 2 (PMCSx, PMRD, PMWR, PMA<x:0>, PMD<7:0> and PMD<8:15><sup>(3)</sup>)

01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS, PMD<7:0> and PMA<1:0>)

00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS and PMD<7:0>)

bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

**Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- 3: These pins are active when MODE16 = 1 (16-bit mode).

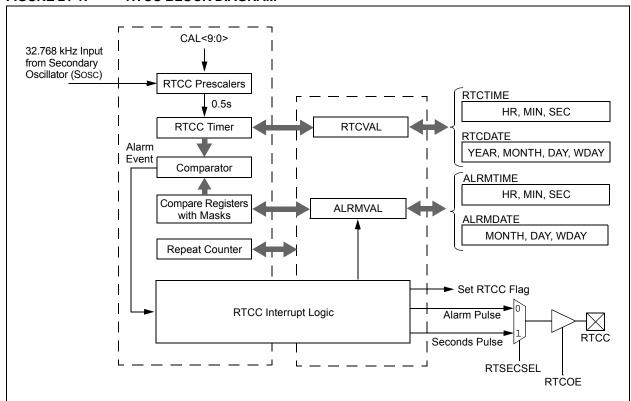

## 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available the Microchip web (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time.

The following are the key features of this module:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- Provides calendar: Weekday, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- · Optimized for long-term battery operation

- · Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

#### FIGURE 21-1: RTCC BLOCK DIAGRAM

#### REGISTER 21-1: RTCCON: RTC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------------|------------------|

| 31:24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                  | R/W-0            |

| 31.24        | _                       | _                 | _                 | _                 | _                      | _                 | CAL<9                  | ):8>             |

| 23:16        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                  | R/W-0            |

| 23.10        |                         |                   |                   | CAL<              | 7:0>                   |                   |                        |                  |

| 15:8         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                    | U-0              |

| 15.6         | ON <sup>(1,2)</sup>     | _                 | SIDL              | _                 | _                      | _                 | _                      | _                |

| 7:0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                    | R/W-0            |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          | _                 | 1                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup> | RTCOE            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: RTC Drift Calibration bits, which contain a signed 10-bit integer value

0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute

•

000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute

0000000000 = No adjustment

1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute

•

100000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute

bit 15 **ON:** RTCC On bit<sup>(1,2)</sup>

1 = RTCC module is enabled

0 = RTCC module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Disables the PBCLK to the RTCC when CPU enters in Idle mode

0 = Continue normal operation in Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(3)</sup>

1 = RTCC Seconds Clock is selected for the RTCC pin

0 = RTCC Alarm Pulse is selected for the RTCC pin

bit 6 RTCCLKON: RTCC Clock Enable Status bit

1 = RTCC Clock is actively running

0 = RTCC Clock is not running

bit 5-4 Unimplemented: Read as '0'

**Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- **4:** The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

#### REGISTER 23-18: C1FIFOUAn: CAN FIFO USER ADDRESS REGISTER 'n' ('n' = 0 THROUGH 15)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|

| 31:24        | R-x                | R-x                |  |  |  |

| 31.24        |                   |                   |                   | C1FIFOU           | An<31:24>         |                   |                    |                    |  |  |  |

| 23:16        | R-x                | R-x                |  |  |  |

| 23.10        |                   |                   |                   | C1FIFOU           | An<23:16>         |                   |                    |                    |  |  |  |

| 15:8         | R-x                | R-x                |  |  |  |

| 13.6         |                   | C1FIFOUAn<15:8>   |                   |                   |                   |                   |                    |                    |  |  |  |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |

| 7.0          |                   |                   |                   | C1FIFOL           | JAn<7:0>          |                   |                    |                    |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 C1FIFOUAn<31:0>: CAN FIFO User Address bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This bit will always read '0', which forces byte-alignment of messages.

**Note:** This register is not guaranteed to read correctly in Configuration mode, and should only be accessed when the module is not in Configuration mode.

### REGISTER 23-19: C1FIFOCIn: CAN MODULE MESSAGE INDEX REGISTER 'n' ('n' = 0 THROUGH 15)

| Bit<br>Range           | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24                  | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10                  | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6                   | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0                    | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0 — — C1FIFOCIn<4:0> |                   |                   |                   |                   |                   |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-5 Unimplemented: Read as '0'

bit 4-0 C1FIFOCIn<4:0>: CAN Side FIFO Message Index bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return an index to the message that the FIFO will use to save the next message.

### 27.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- · Control register lock sequence

- · Configuration bit select lock

#### 27.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### 27.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PMDL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

TABLE 27-2: PERIPHERAL MODULE DISABLE REGISTER SUMMARY

| ess                         |                  | •         |       |       |       |        |        |        |        | Bit                  | s    |      |      |       |       |        |        |        | £                         |

|-----------------------------|------------------|-----------|-------|-------|-------|--------|--------|--------|--------|----------------------|------|------|------|-------|-------|--------|--------|--------|---------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12  | 27/11  | 26/10  | 25/9   | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4  | 19/3  | 18/2   | 17/1   | 16/0   | All Resets <sup>(1)</sup> |

| F240                        | PMD1             | 31:16     | _     | _     | _     | _      | _      | -      | _      | _                    | _    | -    | -    | _     | -     | _      | _      | _      | 0000                      |

| F240                        | FIVIDI           | 15:0      | _     | _     | _     | CVRMD  | _      | -      | _      | CTMUMD               | _    | -    |      | _     | -     | _      | _      | AD1MD  | 0000                      |

| F250                        | PMD2             | 31:16     | _     | _     | _     | _      | _      | _      | _      | _                    | _    | _    |      | _     | _     | _      | _      | _      | 0000                      |

| F250                        | FIVIDZ           | 15:0      | _     | _     | _     | _      | _      | -      | _      | _                    | _    | -    |      | _     | -     | CMP3MD | CMP2MD | CMP1MD | 0000                      |

| F260                        | PMD3             | 31:16     | _     | _     |       | _      |        | ı      |        | _                    |      | ı    | I    | OC5MD | OC4MD | OC3MD  | OC2MD  | OC1MD  | 0000                      |

| F260                        | FINIDS           | 15:0      | _     | _     |       | _      |        | ı      |        | _                    |      | ı    | I    | IC5MD | IC4MD | IC3MD  | IC2MD  | IC1MD  | 0000                      |

| F270                        | PMD4             | 31:16     | _     | _     |       | _      |        | ı      |        | _                    |      | ı    | I    |       | ı     | 1      | _      |        | 0000                      |

| F270                        | FIVID4           | 15:0      | _     | _     |       | _      |        | ı      |        | _                    |      | ı    | I    | T5MD  | T4MD  | T3MD   | T2MD   | T1MD   | 0000                      |

| F280                        | PMD5             | 31:16     | _     | _     |       | CAN1MD |        | ı      |        | USBMD <sup>(1)</sup> |      | ı    | I    |       | ı     | 1      | I2C1MD | I2C1MD | 0000                      |

| F200                        | FINIDO           | 15:0      | _     | _     |       | _      | SPI4MD | SPI3MD | SPI2MD | SPI1MD               |      | ı    | I    | U5MD  | U4MD  | U3MD   | U2MD   | U1MD   | 0000                      |

| F290                        | PMD6             | 31:16     | _     | _     |       | _      |        | ı      |        | _                    |      | ı    | I    |       | ı     | 1      | _      | PMPMD  | 0000                      |

| F290                        | i wiD0           | 15:0      | _     | _     | _     | _      | _      | I      | -      | _                    | _    | I    | I    | -     | I     | -      | REFOMD | RTCCMD | 0000                      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on devices with a USB module.

#### TABLE 31-18: PLL CLOCK TIMING SPECIFICATIONS

AC CHARACTERISTICS Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$  for V-temp

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup>                                      | Min.  | Typical | Max.  | Units | Conditions                           |

|---------------|--------|---------------------------------------------------------------------|-------|---------|-------|-------|--------------------------------------|

| OS50          | FPLLI  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 3.92  | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51          | Fsys   | On-Chip VCO System Frequency                                        | 60    | _       | 120   | MHz   | _                                    |

| OS52          | TLOCK  | PLL Start-up Time (Lock Time)                                       | _     | _       | 2     | ms    | _                                    |

| OS53          | DCLK   | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      | -0.25 | _       | +0.25 | %     | Measured over 100 ms period          |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

#### **TABLE 31-19: INTERNAL FRC ACCURACY**

| AC CHA        | RACTERISTICS           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $ -40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C for Industrial} \\ -40^{\circ}\text{C} \leq \text{TA} \leq +105^{\circ}\text{C for V-temp} $ |         |      |       |                     |  |  |  |

|---------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|---------------------|--|--|--|

| Param.<br>No. | Characteristics        | Min.                                                                                                                                                                                                                                                  | Typical | Max. | Units | Conditions          |  |  |  |

| Internal      | FRC Accuracy @ 8.00 MH | z <sup>(1)</sup>                                                                                                                                                                                                                                      |         |      |       |                     |  |  |  |

| F20a          | FRC                    | -0.9 — +0.9 % -40                                                                                                                                                                                                                                     |         |      |       | -40°C ≤ TA ≤ +85°C  |  |  |  |

| F20b          | FRC                    | -2                                                                                                                                                                                                                                                    | _       | +2   | %     | -40°C ≤ TA ≤ +105°C |  |  |  |

**Note 1:** Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

#### TABLE 31-20: INTERNAL LPRC ACCURACY

| AC CHA                 | ARACTERISTICS                   | (unless | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |            |  |  |  |  |

|------------------------|---------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No.          | Characteristics                 | Min.    | Typical                                                                                                                                                                                              | Max. | Units | Conditions |  |  |  |  |

| LPRC @                 | LPRC @ 31.25 kHz <sup>(1)</sup> |         |                                                                                                                                                                                                      |      |       |            |  |  |  |  |

| F21 LPRC -15 — +15 % — |                                 |         |                                                                                                                                                                                                      |      |       |            |  |  |  |  |

Note 1: Change of LPRC frequency as VDD changes.

TABLE 31-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHA        | ARACTERIS            | TICS                                               | (unless      | d Operating<br>otherwise st<br>g temperature | t <b>ated)</b><br>e -40°C : | ≤ <b>T</b> A ≤ <b>+</b> 8 | 3V to 3.6V<br>35°C for Industrial<br>105°C for V-temp |

|---------------|----------------------|----------------------------------------------------|--------------|----------------------------------------------|-----------------------------|---------------------------|-------------------------------------------------------|

| Param.<br>No. | Symbol               | Characteristics <sup>(1)</sup>                     | Min.         | Typical <sup>(2)</sup>                       | Max.                        | Units                     | Conditions                                            |

| SP51          | TssH2DoZ             | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4) | 5            | _                                            | 25                          | ns                        | _                                                     |

| SP52          | TscH2ssH<br>TscL2ssH | SSx ↑ after SCKx Edge                              | Тscк +<br>20 | _                                            | _                           | ns                        | _                                                     |

| SP60          | TssL2DoV             | SDOx Data Output Valid after SSx Edge              | _            | _                                            | 25                          | ns                        | _                                                     |

Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- 4: Assumes 50 pF load on all SPIx pins.

TABLE 31-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

| AC CHA        | RACTER  | ISTICS           |                     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |       |                                     |  |  |

|---------------|---------|------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------|--|--|

| Param.<br>No. | Symbol  | Charac           | teristics           | Min. <sup>(1)</sup>                                                                                                                                                                                                                            | Max. | Units | Conditions                          |  |  |

| IM40          | TAA:SCL | Output Valid     | 100 kHz mode        | _                                                                                                                                                                                                                                              | 3500 | ns    | _                                   |  |  |

|               |         | from Clock       | 400 kHz mode        | _                                                                                                                                                                                                                                              | 1000 | ns    | _                                   |  |  |

|               |         |                  | 1 MHz mode (Note 2) | _                                                                                                                                                                                                                                              | 350  | ns    | _                                   |  |  |

| IM45          | TBF:SDA | Bus Free Time    | 100 kHz mode        | 4.7                                                                                                                                                                                                                                            |      | μS    | The amount of time the              |  |  |

|               |         |                  | 400 kHz mode        | 1.3                                                                                                                                                                                                                                            | _    | μS    | bus must be free                    |  |  |

|               |         |                  | 1 MHz mode (Note 2) | 0.5                                                                                                                                                                                                                                            | _    | μS    | before a new transmission can start |  |  |

| IM50          | Св      | Bus Capacitive L | oading              | _                                                                                                                                                                                                                                              | 400  | pF    | _                                   |  |  |

| IM51          | TPGD    | Pulse Gobbler D  | elay                | 52                                                                                                                                                                                                                                             | 312  | ns    | See Note 3                          |  |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

<sup>2:</sup> Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**<sup>3:</sup>** The typical value for this parameter is 104 ns.

TABLE 31-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

| AC CHA        | ARACTER   | ISTICS                                                               | (unless | otherwise              | <b>stated)</b><br>ure -40° | C ≤ TA ≤ - | Note 4): 2.5V to 3.6V<br>+85°C for Industrial<br>+105°C for V-temp |

|---------------|-----------|----------------------------------------------------------------------|---------|------------------------|----------------------------|------------|--------------------------------------------------------------------|

| Param.<br>No. | Symbol    | Characteristics                                                      | Min.    | Typical <sup>(1)</sup> | Max.                       | Units      | Conditions                                                         |

| Clock P       | arameter  | S                                                                    |         |                        |                            |            |                                                                    |

| AD50          | TAD       | ADC Clock Period <sup>(2)</sup>                                      | 65      | _                      | _                          | ns         | See Table 31-35                                                    |

| Convers       | sion Rate |                                                                      |         |                        |                            |            |                                                                    |

| AD55          | TCONV     | Conversion Time                                                      | _       | 12 TAD                 | _                          | _          | _                                                                  |

| AD56          | FCNV      | Throughput Rate                                                      | _       | _                      | 1000                       | ksps       | AVDD = 3.0V to 3.6V                                                |

|               |           | (Sampling Speed)                                                     | _       | _                      | 400                        | ksps       | AVDD = 2.5V to 3.6V                                                |

| AD57          | TSAMP     | Sample Time                                                          | 1 TAD   | _                      | _                          | _          | Tsamp must be ≥ 132 ns                                             |

| Timing        | Paramete  | rs                                                                   |         |                        |                            |            |                                                                    |

| AD60          | TPCS      | Conversion Start from Sample Trigger <sup>(3)</sup>                  | _       | 1.0 TAD                | _                          | _          | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected          |

| AD61          | TPSS      | Sample Start from Setting Sample (SAMP) bit                          | 0.5 TAD |                        | 1.5 TAD                    | _          | _                                                                  |

| AD62          | TCSS      | Conversion Completion to Sample Start (ASAM = $1$ ) <sup>(3)</sup>   | _       | 0.5 TAD                | _                          | _          | _                                                                  |

| AD63          | TDPU      | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(3)</sup> | _       | _                      | 2                          | μS         | _                                                                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**<sup>2:</sup>** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**<sup>3:</sup>** Characterized by design but not tested.

**<sup>4:</sup>** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.