Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2000                       |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | - ·                                                                             |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx550f256lt-v-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                    | 13  |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs    |     |

| 3.0   | CPU                                                |     |

| 4.0   | Memory Organization                                |     |

| 5.0   | Interrupt Controller                               |     |

| 6.0   | Flash Program Memory                               |     |

| 7.0   | Resets                                             |     |

| 8.0   | Oscillator Configuration                           |     |

| 9.0   | Direct Memory Access (DMA) Controller              |     |

| 10.0  | USB On-The-Go (OTG)                                |     |

| 11.0  | I/O Ports                                          | 129 |

|       | Timer1                                             |     |

| 13.0  | Timer2/3, Timer4/5                                 | 163 |

| 14.0  | Watchdog Timer (WDT)                               | 169 |

| 15.0  | Input Capture                                      | 173 |

| 16.0  | Output Compare                                     | 177 |

| 17.0  | Serial Peripheral Interface (SPI)                  |     |

| 18.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        |     |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART) | 199 |

| 20.0  | Parallel Master Port (PMP)                         | 207 |

|       | Real-Time Clock and Calendar (RTCC)                |     |

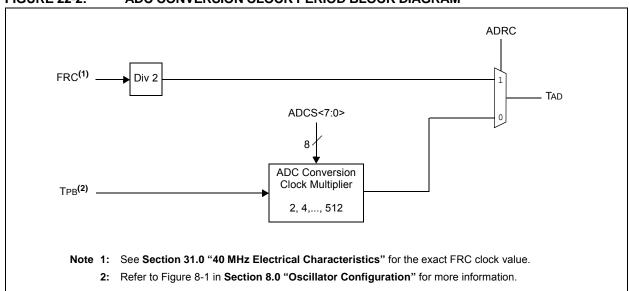

| 22.0  | 10-bit Analog-to-Digital Converter (ADC)           | 231 |

| 23.0  | Controller Area Network (CAN)                      | 243 |

| 24.0  | Comparator                                         |     |

| 25.0  | Comparator Voltage Reference (CVREF)               |     |

| 26.0  | Charge Time Measurement Unit (CTMU)                | 279 |

| 27.0  | Power-Saving Features                              | 285 |

| 28.0  | Special Features                                   | 291 |

| 29.0  | Instruction Set                                    | 303 |

| 30.0  | Development Support                                | 305 |

| 31.0  | 40 MHz Electrical Characteristics                  | 309 |

|       | 50 MHz Electrical Characteristics                  |     |

| 33.0  | DC and AC Device Characteristics Graphs            | 359 |

|       | Packaging Information                              |     |

| The M | Vicrochip Web Site                                 | 377 |

|       | omer Change Notification Service                   |     |

|       | omer Support                                       |     |

| Produ | uct Identification System                          | 378 |

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

# 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX/5XX 64/ 100-pin family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of  $0.1 \ \mu F$ (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source.For detailed information, refer to **Section 3.** "Memory Organization" (DS60001115) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, the data memory can be made executable, allowing PIC32MX1XX/2XX/5XX 64/100-pin devices to execute from data memory.

The key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1) mode address space

- Flexible program Flash memory partitioning

- Flexible data RAM partitioning for data and program space

- · Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Simple memory mapping with Fixed Mapping Translation (FMT) unit

# 4.1 Memory Layout

PIC32MX1XX/2XX/5XX 64/100-pin microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The memory maps for the PIC32MX1XX/2XX/5XX 64/ 100-pin devices are illustrated in Figure 4-1 through Figure 4-4.

| Interment Course (1)                       | (1) IRQ # Vector Interrupt Bit Location |      |               |              |              |              |           |  |  |  |  |  |

|--------------------------------------------|-----------------------------------------|------|---------------|--------------|--------------|--------------|-----------|--|--|--|--|--|

| Interrupt Source <sup>(1)</sup>            | IRQ #                                   | #    | Flag          | Enable       | Priority     | Sub-priority | Interrupt |  |  |  |  |  |

| CNA – PORTA Input Change Interrupt         | 44                                      | 33   | IFS1<12>      | IEC1<12>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |  |  |  |  |

| CNB – PORTB Input Change Interrupt         | 45                                      | 33   | IFS1<13>      | IEC1<13>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |  |  |  |  |

| CNC – PORTC Input Change Interrupt         | 46                                      | 33   | IFS1<14>      | IEC1<14>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |  |  |  |  |

| CND – PORTD Input Change Interrupt         | 47                                      | 33   | IFS1<15>      | IEC1<15>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |  |  |  |  |

| CNE – PORTE Input Change Interrupt         | 48                                      | 33   | IFS1<16>      | IEC1<16>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |  |  |  |  |

| CNF – PORTF Input Change Interrupt         | 49                                      | 33   | IFS1<17>      | IEC1<17>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |  |  |  |  |

| CNG – PORTG Input Change Interrupt         | 50                                      | 33   | IFS1<18>      | IEC1<18>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |  |  |  |  |  |

| PMP – Parallel Master Port                 | 51                                      | 34   | IFS1<19>      | IEC1<19>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |  |  |  |  |  |

| PMPE – Parallel Master Port Error          | 52                                      | 34   | IFS1<20>      | IEC1<20>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |  |  |  |  |  |

| SPI2E – SPI2 Fault                         | 53                                      | 35   | IFS1<21>      | IEC1<21>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |  |  |  |  |  |

| SPI2RX – SPI2 Receive Done                 | 54                                      | 35   | IFS1<22>      | IEC1<22>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |  |  |  |  |  |

| SPI2TX – SPI2 Transfer Done                | 55                                      | 35   | IFS1<23>      | IEC1<23>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |  |  |  |  |  |

| U2E – UART2 Error                          | 56                                      | 36   | IFS1<24>      | IEC1<24>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |  |  |  |  |  |

| U2RX – UART2 Receiver                      | 57                                      | 36   | IFS1<25>      | IEC1<25>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |  |  |  |  |  |

| U2TX – UART2 Transmitter                   | 58                                      | 36   | IFS1<26>      | IEC1<26>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |  |  |  |  |  |

| I2C2B – I2C2 Bus Collision Event           | 59                                      | 37   | IFS1<27>      | IEC1<27>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |  |  |  |  |  |

| I2C2S – I2C2 Slave Event                   | 60                                      | 37   | IFS1<28>      | IEC1<28>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |  |  |  |  |  |

| I2C2M – I2C2 Master Event                  | 61                                      | 37   | IFS1<29>      | IEC1<29>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |  |  |  |  |  |

| U3E – UART3 Error                          | 62                                      | 38   | IFS1<30>      | IEC1<30>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |  |  |  |  |  |

| U3RX – UART3 Receiver                      | 63                                      | 38   | IFS1<31>      | IEC1<31>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |  |  |  |  |  |

| U3TX – UART3 Transmitter                   | 64                                      | 38   | IFS2<0>       | IEC2<0>      | IPC9<20:18>  | IPC9<17:16>  | Yes       |  |  |  |  |  |

| U4E – UART4 Error                          | 65                                      | 39   | IFS2<1>       | IEC2<1>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |  |  |  |  |  |

| U4RX – UART4 Receiver                      | 66                                      | 39   | IFS2<2>       | IEC2<2>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |  |  |  |  |  |

| U4TX – UART4 Transmitter                   | 67                                      | 39   | IFS2<3>       | IEC2<3>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |  |  |  |  |  |

| U5E – UART5 Error <sup>(2)</sup>           | 68                                      | 40   | IFS2<4>       | IEC2<4>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |  |  |  |  |  |

| U5RX – UART5 Receiver <sup>(2)</sup>       | 69                                      | 40   | IFS2<5>       | IEC2<5>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |  |  |  |  |  |

| U5TX – UART5 Transmitter <sup>(2)</sup>    | 70                                      | 40   | IFS2<6>       | IEC2<6>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |  |  |  |  |  |

| CTMU – CTMU Event <sup>(2)</sup>           | 71                                      | 41   | IFS2<7>       | IEC2<7>      | IPC10<12:10> | IPC10<9:8>   | Yes       |  |  |  |  |  |

| DMA0 – DMA Channel 0                       | 72                                      | 42   | IFS2<8>       | IEC2<8>      | IPC10<20:18> | IPC10<17:16> | No        |  |  |  |  |  |

| DMA1 – DMA Channel 1                       | 73                                      | 43   | IFS2<9>       | IEC2<9>      | IPC10<28:26> | IPC10<25:24> | No        |  |  |  |  |  |

| DMA2 – DMA Channel 2                       | 74                                      | 44   | IFS2<10>      | IEC2<10>     | IPC11<4:2>   | IPC11<1:0>   | No        |  |  |  |  |  |

| DMA3 – DMA Channel 3                       | 75                                      | 45   | IFS2<11>      | IEC2<11>     | IPC11<12:10> | IPC11<9:8>   | No        |  |  |  |  |  |

| CMP3 – Comparator 3 Interrupt              | 76                                      | 46   | IFS2<12>      | IEC2<12>     | IPC11<20:18> | IPC11<17:16> | No        |  |  |  |  |  |

| CAN1 – CAN1 Event                          | 77                                      | 47   | IFS2<13>      | IEC2<13>     | IPC11<28:26> | IPC11<25:24> | Yes       |  |  |  |  |  |

| SPI3E – SPI3 Fault                         | 78                                      | 48   | IFS2<14>      | IEC2<14>     | IPC12<4:2>   | IPC12<1:0>   | Yes       |  |  |  |  |  |

| SPI3RX – SPI3 Receive Done                 | 79                                      | 48   | IFS2<15>      | IEC2<15>     | IPC12<4:2>   | IPC12<1:0>   | Yes       |  |  |  |  |  |

| SPI3TX – SPI3 Transfer Done                | 80                                      | 48   | IFS2<16>      | IEC2<16>     | IPC12<4:2>   | IPC12<1:0>   | Yes       |  |  |  |  |  |

| SPI4E – SPI4 Fault <sup>(2)</sup>          | 81                                      | 49   | IFS2<17>      | IEC2<17>     | IPC12<12:10> | IPC12<9:8>   | Yes       |  |  |  |  |  |

| SPI4RX – SPI4 Receive Done <sup>(2)</sup>  | 82                                      | 49   | IFS2<18>      | IEC2<18>     | IPC12<12:10> | IPC12<9:8>   | Yes       |  |  |  |  |  |

| SPI4TX – SPI4 Transfer Done <sup>(2)</sup> | 83                                      | 49   | IFS2<19>      | IEC2<19>     | IPC12<12:10> | IPC12<9:8>   | Yes       |  |  |  |  |  |

|                                            | •                                       | Lowe | st Natural Or | der Priority |              |              |           |  |  |  |  |  |

### TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 =Clock is multiplied by 17

- 001 =Clock is multiplied by 16

- 000 = Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = PLL module is in lock or PLL module start-up timer is satisfied

- 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 **CF:** Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| KE013TE      | .K 3-12. D        |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHSSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                   |                   |                   |                  |                  |

# REGISTER 9-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

#### **REGISTER 9-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   |                   |                   | CHDSIZ            | <15:8>            |                   |                  |                  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-16 Unimplemented: Read as '0'

### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet rejected due to CRC5 error

- 0 = Token packet accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = EOF error condition detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check failed

- 0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|--|

| 21.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |

| 31:24        | _                 | —                 | —                        |                   | —                     | —                     | _                | —                    |  |

| 00.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |

| 23:16        | —                 | _                 | —                        | _                 | —                     | _                     | _                | —                    |  |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |

| 15.0         | —                 | —                 | —                        | —                 | —                     | _                     |                  | —                    |  |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |  |

| 7:0          | JSTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |  |

|              | JOTATE            | 320               | TOKBUSY <sup>(1,5)</sup> | USDROI            |                       | RESUME                | FFDROI           | SOFEN <sup>(5)</sup> |  |

### REGISTER 10-11: U1CON: USB CONTROL REGISTER

# Legend:

| Logonal           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE detected on the USB

- 0 = No JSTATE detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single Ended Zero detected on the USB

0 = No Single Ended Zero detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

#### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

#### bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability enabled

- 0 = USB host capability disabled

### bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling activated

- 0 = RESUME signaling disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- **3:** Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

## TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                         |                  |           |       | Bits  |       |       |       |       |      |      |      |      |      |      |      |      |        |      |            |

|----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| 5004                       | RPG1R            | 31:16     |       | _     |       |       | —     | _     | _    |      | _    |      | —    | _    |      | _    |        | —    | 0000       |

| FC04                       | RPGIR            | 15:0      | —     | —     | _     | _     | _     | —     | —    | —    | —    | _    | _    | —    |      | RPG1 | <3:0>  |      | 0000       |

| 5000                       | DDOOD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | —    | _    | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FC98                       | RPG6R            | 15:0      | —     | —     | _     | _     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPG  | 6<3:0> |      | 0000       |

| 5000                       | 00070            | 31:16     | —     | —     | _     | _     | —     | —     | —    | —    | _    | —    | —    | —    | —    | —    | _      | —    | 0000       |

| FC9C                       | RPG7R            | 15:0      | _     | —     | _     | _     | _     | —     | —    | —    | _    | _    | _    | _    |      | RPG7 | /<3:0> |      | 0000       |

| 5040                       | DDOAD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | -    |      | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FCAU                       | RPG8R            | 15:0      | _     | —     | _     | _     | _     | —     | —    |      |      | _    | _    | —    |      | RPG8 | 3<3:0> | •    | 0000       |

| 5044                       | DDOOD            | 31:16     | _     | —     | _     | _     | _     | —     | —    | _    | -    | _    | _    | _    | _    | _    | _      | _    | 0000       |

| FCA4                       | RPG9R            | 15:0      | —     | —     | _     | _     | —     | —     | —    | _    | _    | —    | —    | —    |      | RPG9 | <3:0>  |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

| REGISTE      | _1 10-1. 12       |                   |                   |                   |                   | AND ZJ            |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | —                 | _                 | —                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   | —                 | _                 | —                 | _                 | —                | —                |

| 45.0         | R/W-0             | R/W-0 U-0         |                   | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

# **REGISTER 18-1:** I2CxCON: $I^2C'x'$ CONTROL REGISTER ('x' = 1 AND 2)

| Legend:           | HC = Cleared in Hardwar | e                        |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the I<sup>2</sup>C module; all I<sup>2</sup>C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- SCLREL: SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

bit 12

0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 =Strict I<sup>2</sup>C Reserved Address Rule not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

|                             | LE 19-1:                 | UAI       |        | THROUGH UAR 15 REGISTER MAP (CONTINUED) |        |       |        |       |       |             |                      |         |       |          |          |      |        |       |            |

|-----------------------------|--------------------------|-----------|--------|-----------------------------------------|--------|-------|--------|-------|-------|-------------|----------------------|---------|-------|----------|----------|------|--------|-------|------------|

| ess                         |                          | đ         |        |                                         |        |       |        |       |       | Bi          | ts                   |         |       |          |          |      |        |       | s          |

| Virtual Address<br>(BF80_#) | Register<br>Name         | Bit Range | 31/15  | 30/14                                   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7                 | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6440                        |                          | 31:16     | _      | —                                       | —      |       | —      |       | —     | —           |                      | —       | _     |          |          | _    |        |       | 0000       |

| 0440                        | USBRG. /                 | 15:0      |        |                                         |        |       |        |       | Bau   | d Rate Gene | erator Pres          | caler   |       |          |          |      |        |       | 0000       |

| 6600                        | U4MODE <sup>(1)</sup>    | 31:16     |        | _                                       | _      |       | _      |       | _     | _           |                      | —       | _     |          | _        | _    | _      |       | 0000       |

| 0000                        | 04IVIODL.                | 15:0      | ON     | —                                       | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE                 | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6610                        | U4STA <sup>(1)</sup>     | 31:16     | _      |                                         |        |       |        |       |       |             |                      | 0000    |       |          |          |      |        |       |            |

| 0010                        | 04017                    | 15:0      | UTXISE | EL<1:0>                                 | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI               | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6620                        | U4TXREG                  | 31:16     | —      |                                         | —      | _     | _      | _     |       | —           |                      | —       | —     | _        | —        | —    | —      | —     | 0000       |

| 0020                        | OFINICO                  | 15:0      | —      |                                         | —      | _     | _      | _     |       | TX8         |                      |         |       | Transmit | Register |      |        |       | 0000       |

| 6630                        | U4RXREG                  | 31:16     | —      |                                         | _      | _     | _      | _     |       | _           |                      | —       | _     | _        | _        | _    | _      | —     | 0000       |

| 0000                        | OHIVILO                  | 15:0      | —      |                                         | _      | _     | _      | _     |       | RX8         |                      |         |       | Receive  | Register |      |        |       | 0000       |

| 6640                        | U4BRG <sup>(1)</sup>     | 31:16     | —      | —                                       | —      | —     | —      | —     | —     | —           | —                    | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0010                        | U IBIKO                  | 15:0      |        |                                         |        |       |        |       | Bau   | d Rate Gen  | erator Pres          | caler   |       |          |          |      |        |       | 0000       |

| 6800                        | U5MODE <sup>(1,2)</sup>  | 31:16     |        | —                                       | —      |       | —      | _     | —     |             |                      | —       | —     |          | —        | —    | —      |       | 0000       |

|                             | 00111022                 | 15:0      | ON     | —                                       | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE                 | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6810                        | U5STA <sup>(1,2)</sup>   | 31:16     | —      | —                                       | —      | —     | —      | —     | —     | ADM_EN      |                      |         |       | 1        | R<7:0>   | 1    | 1      | 1     | 0000       |

|                             |                          | 15:0      | UTXISE | EL<1:0>                                 | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXIS                | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6820                        | U5TXREG <sup>(1,2)</sup> | 31:16     | _      |                                         | —      | _     | —      |       |       |             | _                    | —       | —     | —        |          | —    |        |       | 0000       |

|                             |                          | 15:0      | _      |                                         | —      | _     | —      |       |       | TX8         |                      |         |       | Transmit | Register |      |        |       | 0000       |

| 6830                        | U5RXREG <sup>(1,2)</sup> | 31:16     | _      |                                         | —      | —     | —      |       |       | —           | —                    | —       | —     | —        | —        | —    | —      | —     | 0000       |

|                             |                          | 1010      | —      |                                         | —      | —     | —      |       |       | RX8         | RX8 Receive Register |         |       |          | 0000     |      |        |       |            |

| 6840                        | U5BRG <sup>(1,2)</sup>   | 31:16     | —      | —                                       | —      | —     | —      | —     | —     |             |                      |         |       | 0000     |          |      |        |       |            |

|                             |                          | 15:0      |        | Baud Rate Generator Prescaler 0000      |        |       |        |       |       |             |                      |         |       |          |          |      |        |       |            |

## TABLE 19-1: UART1 THROUGH UART5 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register is only available on 100-pin devices.

'0' = Bit is cleared

x = Bit is unknown

| Bit<br>Range     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|

| 04.04            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 31:24            |                   | HR10              | <3:0>             |                   | HR01<3:0>                          |                   |                  |                  |

| 23:16            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

|                  |                   | MIN10             | <3:0>             |                   | MIN01<3:0>                         |                   |                  |                  |

|                  | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 15:8             | SEC10<3:0>        |                   |                   |                   | SEC01<3:0>                         |                   |                  |                  |

| 7.0              | U-0               | U-0               | U-0               | U-0               | U-0                                | U-0               | U-0              | U-0              |

| 7:0              | _                 | _                 | _                 | _                 | _                                  | _                 | _                | _                |

|                  |                   |                   |                   |                   |                                    |                   |                  |                  |

| Legend:          |                   |                   |                   |                   |                                    |                   |                  |                  |

| R = Readable bit |                   |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10s place digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10s place digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10s place digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

'1' = Bit is set

-n = Value at POR

### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC sample and hold amplifier is sampling

- 0 = The ADC sample/hold amplifier is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

Clearing this bit will not affect any operation in progress.

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     | FLTEN3            | MSEL3<1:0>        |                   | FSEL3<4:0>        |                   |                   |                  |                  |

| 22:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     | FLTEN2            | MSEL2<1:0>        |                   | FSEL2<4:0>        |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0      | FLTEN1            | MSEL1<1:0>        |                   | FSEL1<4:0>        |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN0            | MSEL              | 0<1:0>            | FSEL0<4:0>        |                   |                   |                  |                  |

## REGISTER 23-10: C1FLTCON0: CAN FILTER CONTROL REGISTER 0

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN3: Filter 3 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL3<1:0>: Filter 3 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                    |

| bit 28-24 | FSEL3<4:0>: FIFO Selection bits<br>11111 = Reserved<br>10000 = Reserved<br>01111 = Message matching filter is stored in FIFO buffer 15<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN2: Filter 2 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                       |

| bit 22-21 | MSEL2<1:0>: Filter 2 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                    |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | FLTEN7            | MSEL7<1:0>        |                   | FSEL7<4:0>        |                   |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN6            | MSEL6<1:0>        |                   | FSEL6<4:0>        |                   |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FLTEN5            | MSEL5<1:0>        |                   | FSEL5<4:0>        |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN4            | MSEL              | 4<1:0>            | FSEL4<4:0>        |                   |                   |                  |                  |

### **REGISTER 23-11: C1FLTCON1: CAN FILTER CONTROL REGISTER 1**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | <b>FLTEN7:</b> Filter 7 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                    |

| bit 28-24 | FSEL7<4:0>: FIFO Selection bits<br>11111 = Reserved<br>10000 = Reserved<br>01111 = Message matching filter is stored in FIFO buffer 15<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN6: Filter 6 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                       |

| bit 22-21 | <b>MSEL6&lt;1:0&gt;:</b> Filter 6 Mask Select bits<br>11 = Acceptance Mask 3 selected                                                                                                                |

- - 10 = Acceptance Mask 2 selected

- 01 = Acceptance Mask 1 selected

- 00 = Acceptance Mask 0 selected

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|

| 31:24        | R/W-0              | R/W-0              |  |  |

| 31.24        | C1FIFOBA<31:24>   |                   |                   |                   |                   |                   |                    |                    |  |  |

| 23:16        | R/W-0              | R/W-0              |  |  |

| 23.10        | C1FIFOBA<23:16>   |                   |                   |                   |                   |                   |                    |                    |  |  |

| 15:8         | R/W-0              | R/W-0              |  |  |

| 10.0         | C1FIFOBA<15:8>    |                   |                   |                   |                   |                   |                    |                    |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |

| 7:0          |                   |                   |                   | C1FIFO            | BA<7:0>           |                   |                    |                    |  |  |

#### REGISTER 23-15: C1FIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

#### Legend:

| Logonal                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-0 C1FIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Bits <1:0> are read-only and read as '0', forcing the messages to be 32-bit word-aligned in device RAM.

**Note 1:** This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (C1CON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                   | —                 | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | —                 | —                 | —                 | —                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 10.0         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | —                 | —                 | —                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

|              | EVPOL             | _<1:0>            | _                   | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |

|-------------------|---------------------------------|----------------------|------------------------------------|--|--|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

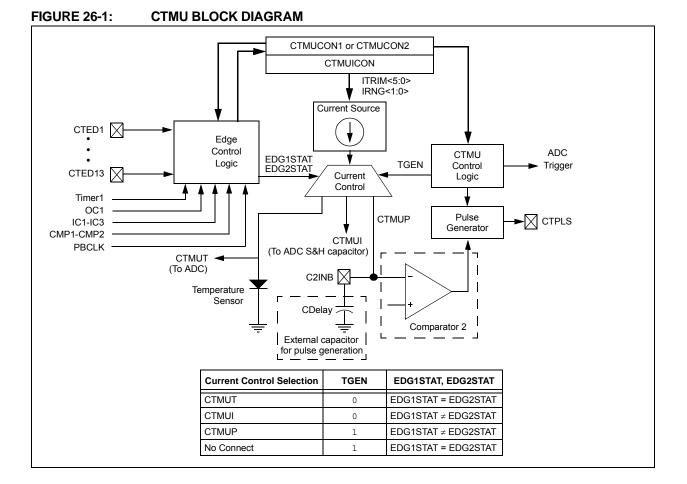

# 26.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167) in the "PIC32 Family Reference Manual", which is available the site from Microchip web (www.microchip.com).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The CTMU module includes the following key features:

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 26-1.

© 2014-2016 Microchip Technology Inc.

# 27.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes power-saving features for the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. These PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 27.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

# 27.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

# 27.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

## 27.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is Halted.

- The system clock source is typically shutdown. See Section 27.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection.

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode.

- The BOR circuit remains operative during Sleep mode.

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode.

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep.

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption.