Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| /oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 48x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx550f256lt-v-pt |

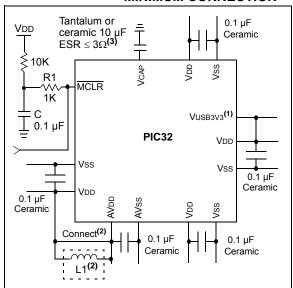

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

Note 1: If the USB module is not used, this pin must be connected to VDD.

2: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than  $3\Omega$  and the inductor capacity greater than 10 mA.

Where:

$$f=\frac{FCNV}{2} \qquad \text{(i.e., ADC conversion rate/2)}$$

$$f=\frac{1}{(2\pi\sqrt{LC})}$$

$$L=\left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

Aluminum or electrolytic capacitors should not be used. ESR ≤ 3Ω from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F. This capacitor should be located as close to the device as possible.

# 2.3 Capacitor on Internal Voltage Regulator (VCAP)

### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0 "40 MHz Electrical Characteristics"** for additional information on CEFC specifications.

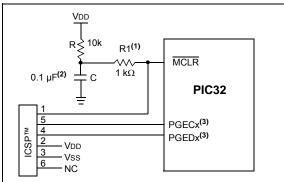

## 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- · Device Reset

- · Device programming and debugging

Pulling The MCLR pin low generates a device Reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

# FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

- Note 1:  $\frac{470\Omega \leq R1 \leq 1\Omega}{MCLR} \text{ from the external capacitor C, in the event of } \frac{MCLR}{MCLR} \text{ pin breakdown, due to Electrostatic Discharge} \\ \frac{(ESD)}{MCLR} \text{ pin VIH} \text{ and VIL specifications are met without interfering with the Debug/Programmer tools.}$

- 2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

- No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

### REGISTER 5-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | _                 | _                 | _                 |                   | IP3<2:0>          |                   | IS3<             | :1:0>            |

| 22:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | _                 |                   | IP2<2:0>          |                   | IS2<             | :1:0>            |

| 15.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | IP1<2:0>          |                   |                   | IS1<             | :1:0>            |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 |                   | IP0<2:0>          |                   | IS0<             | 1:0>             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-26 IP3<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 25-24 IS3<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 23-21 Unimplemented: Read as '0'

bit 20-18 IP2<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

.

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 17-16 IS2<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 15-13 Unimplemented: Read as '0'

bit 12-10 IP1<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

.

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 5-1 for the exact bit definitions.

TABLE 9-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP (CONTINUED)

| SS                          |                                 | _             |             |       |       |            |         |       |      | Bi          | ts                   | -          |        |              |            |         |         |              |              |

|-----------------------------|---------------------------------|---------------|-------------|-------|-------|------------|---------|-------|------|-------------|----------------------|------------|--------|--------------|------------|---------|---------|--------------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14 | 29/13 | 28/12      | 27/11   | 26/10 | 25/9 | 24/8        | 23/7                 | 22/6       | 21/5   | 20/4         | 19/3       | 18/2    | 17/1    | 16/0         | All Resets   |

| 3170                        | DCH1SSIZ                        | 31:16         | _           | _     | _     | _          | _       |       | _    | _           | _                    | -          | _      | _            | _          | _       | _       | _            | 0000         |

| 3170                        | DOITIOGIZ                       | 15:0          |             |       |       |            |         |       |      | CHSSIZ      | <b>'&lt;15:0&gt;</b> |            |        |              |            |         |         |              | 0000         |

| 3180                        | DCH1DSIZ                        | 31:16         | _           | -     | _     | _          | -       | _     | _    | _           | _                    | _          | _      | _            | _          | _       | _       | _            | 0000         |

| 0100                        |                                 | 15:0          | 1           |       |       |            |         |       | I    | CHDSIZ      | <b>2</b> <15:0>      |            |        |              |            |         |         | 1            | 0000         |

| 3190                        | DCH1SPTR                        | 31:16         | _           | _     | _     | _          | _       | _     | _    | _           | _                    | _          | _      | _            | _          | _       | _       | _            | 0000         |

| 0.00                        |                                 | 15:0          |             |       |       |            |         |       | 1    | CHSPTF      | R<15:0>              |            |        |              |            | 1       |         | ı            | 0000         |

| 31A0                        | DCH1DPTR                        | 31:16         | _           | _     | _     | _          | _       | _     | _    | _           | _                    | _          | _      | _            |            | _       | _       | _            | 0000         |

|                             |                                 | 15:0          |             |       |       |            |         |       |      | CHDPT       | R<15:0>              |            |        |              |            |         |         | 1            | 0000         |

| 31B0                        | DCH1CSIZ                        | 31:16         | _           | _     | _     | _          | _       | _     | _    |             |                      | _          | _      | _            | _          | _       | _       | _            | 0000         |

|                             |                                 | 15:0          |             |       |       |            |         |       |      | CHCSIZ      | 2<15:0>              |            |        |              |            |         |         |              | 0000         |

| 31C0                        | DCH1CPTR                        | 31:16         | _           | _     | _     | _          | _       | _     | _    |             |                      | _          | _      | _            |            | _       | _       | _            | 0000         |

|                             |                                 | 15:0          |             |       |       |            |         |       |      | CHCPTF      |                      |            |        |              |            |         |         |              | 0000         |

| 31D0                        | DCH1DAT                         | 31:16         |             | _     | _     | _          | _       | _     | _    | _           | _                    | _          | _      | —<br>OUIDD 4 | —<br>T-70: | _       | _       | _            | 0000         |

|                             |                                 | 15:0          | _           |       | _     |            |         |       | _    | _           |                      |            |        | CHPDA        | 1<7:0>     |         |         |              | 0000         |

| 31E0                        | DCH2CON                         | 31:16<br>15:0 | —<br>CHBUSY |       | _     |            |         |       | _    | —<br>CHCHNS | —<br>CHEN            | —<br>CHAED | CHCHN  | CHAEN        |            | CHEDET  | - CLIDE | —<br>!I<1:0> | 0000         |

|                             |                                 | 31:16         | —           |       |       |            |         |       | _    | —           | CHEN                 | CHAED      | СПСПІ  | CHAIR        |            | CHEDET  | СПРК    | 1<1.0>       | 0000<br>00FF |

| 31F0                        | DCH2ECON                        | 15:0          | _           |       | _     | —<br>CHSIR |         | _     | _    | _           | CFORCE               | CABORT     | PATEN  | SIRQEN       | AIRQEN     | _       | _       |              | FFF8         |

|                             |                                 | 31:16         | _           |       |       | -          | Q \1.0> |       |      | _           | CHSDIE               | CHSHIE     | CHDDIE | CHDHIE       | CHBCIE     | CHCCIE  | CHTAIE  | CHERIE       | 0000         |

| 3200                        | DCH2INT                         | 15:0          |             |       |       |            |         |       |      | _           | CHSDIF               | CHSHIF     | CHDDIF | CHDHIF       | CHBCIE     | CHCCIF  | CHTAIF  | CHERIF       | 0000         |

|                             |                                 | 31:16         |             |       |       |            |         |       |      |             |                      | 01101111   | OHBBII | OHBIIII      | OHBOH      | 0110011 | OTTIVAL | OTILITAI     | 0000         |

| 3210                        | DCH2SSA                         | 15:0          |             |       |       |            |         |       |      | CHSSA       | <31:0>               |            |        |              |            |         |         |              | 0000         |

|                             |                                 | 31:16         |             |       |       |            |         |       |      |             |                      |            |        |              |            |         |         |              | 0000         |

| 3220                        | DCH2DSA                         | 15:0          |             |       |       |            |         |       |      | CHDSA       | <31:0>               |            |        |              |            |         |         |              | 0000         |

|                             |                                 | 31:16         | _           | _     | _     | _          | _       | _     | _    | _           | _                    | _          | _      | _            | _          | _       | _       | _            | 0000         |

| 3230                        | DCH2SSIZ                        | 15:0          |             |       |       |            |         |       |      | CHSSIZ      | <b>'&lt;15:0&gt;</b> |            |        |              |            |         |         |              | 0000         |

| 20.45                       | D 01 10 D 0: -                  | 31:16         | _           | _     | _     | _          | _       | _     | _    | _           | _                    | _          | _      | _            | _          | _       | _       | _            | 0000         |

| 3240                        | DCH2DSIZ                        | 15:0          |             |       |       |            |         |       |      | CHDSIZ      | ː<15:0>              |            |        |              |            |         |         |              | 0000         |

| 0050                        | DOLLOODED                       | 31:16         | _           | _     | _     | _          | _       | _     | _    | _           | _                    | _          | _      | _            | _          | _       | _       | _            | 0000         |

| 3250                        | DCH2SPTR                        | 15:0          |             |       |       |            |         |       |      | CHSPTE      | R<15:0>              |            |        |              |            |         |         |              | 0000         |

| 2260                        | DCLINDDID                       | 31:16         | _           | _     | _     | _          | _       | _     | _    | _           | _                    | _          | _      | _            | _          | _       | _       | _            | 0000         |

| 3200                        | DCH2DPTR                        | 15:0          |             |       |       |            |         |       |      | CHDPT       | R<15:0>              |            |        |              |            |         |         |              | 0000         |

| 3270                        | DCH2CS17                        | 31:16         | _           | _     | _     | _          | _       | _     |      |             | _                    | _          | _      | _            |            | _       | _       | _            | 0000         |

| 3210                        | DCH2CSIZ                        | 15:0          |             |       |       |            |         |       |      | CHCSIZ      | <b>2</b> <15:0>      |            |        |              |            |         |         |              | 0000         |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

### REGISTER 10-16: U1SOF: USB SOF THRESHOLD REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | -                 | -                 | -                 | -                | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 | -                 | -                 | -                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 CNT<7:0>: SOF Threshold Value bits

Typical values of the threshold are:

01001010 = **64-byte** packet

00101010 = 32-byte packet

00011010 =16-byte packet

00010010 =8-byte packet

## REGISTER 10-17: U1BDTP1: USB BDT PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | -                 | _                 |                   |                   | -                 | _                 | -                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         | -                 | _                 | -                 | -                 | -                 | _                 | -                | _                |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |  |

| 7.0          | BDTPTRL<15:9>     |                   |                   |                   |                   |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-1 BDTPTRL<15:9>: BDT Base Address bits

This 7-bit value provides address bits 15 through 9 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

bit 0 **Unimplemented:** Read as '0'

TABLE 11-2: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |

|----------------------|----------|-------------|----------------------------------------------|

| RPD9                 | RPD9R    | RPD9R<3:0>  | 0000 = No Connect                            |

| RPG6                 | RPG6R    | RPG6R<3:0>  | 0001 = U3RTS                                 |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0010 = U4TX                                  |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = REFCLKO<br>0100 = U5TX <sup>(3)</sup> |

| RPD4                 | RPD4R    | RPD4R<3:0>  | 0101 = Reserved                              |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0110 = Reserved                              |

| RPE3                 | RPE3R    | RPE3R<3:0>  | 0111 = SS1                                   |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 1000 = SDO1                                  |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 1001 = Reserved                              |

| RPF12 <sup>(3)</sup> | RPF12R   | RPF12R<3:0> | 1010 = Reserved                              |

| RPD12 <sup>(3)</sup> | RPD12R   | RPD12R<3:0> | 1011 = OC5<br>1100 = Reserved                |

| RPF8 <sup>(3)</sup>  | RPF8R    | RPF8R<3:0>  | 1101 = C1OUT                                 |

| RPC3 <sup>(3)</sup>  | RPC3R    | RPC3R<3:0>  | 1110 = <del>SS3</del>                        |

| RPE9 <sup>(3)</sup>  | RPE9R    | RPE9R<3:0>  | 1111 = SS4 <sup>(3)</sup>                    |

| RPD1                 | RPD1R    | RPD1R<3:0>  | 0000 = <u>No Con</u> nect                    |

| RPG9                 | RPG9R    | RPG9R<3:0>  | 0001 = <u>U2RTS</u>                          |

| RPB14                | RPB14R   | RPB14R<3:0> | 0010 = Reserved<br>0011 = U1RTS              |

| RPD0                 | RPD0R    | RPD0R<3:0>  | 0100 = U5TX <sup>(3)</sup>                   |

| RPD8                 | RPD8R    | RPD8R<3:0>  | 0101 = Reserved                              |

| RPB6                 | RPB6R    | RPB6R<3:0>  | 0110 = SS2                                   |

| RPD5                 | RPD5R    | RPD5R<3:0>  | 0111 = Reserved<br>1000 = SDO1               |

| RPF3 <sup>(1)</sup>  | RPF3R    | RPF3R<3:0>  | 1001 = Reserved                              |

| RPF6 <sup>(2)</sup>  | RPF6R    | RPF6R<3:0>  | 1010 = Reserved                              |

| RPF13 <sup>(3)</sup> | RPF13R   | RPF13R<3:0> | 1011 = OC2                                   |

| RPC2 <sup>(3)</sup>  | RPC2R    | RPC2R<3:0>  | 1100 = OC1<br>1101 = Reserved                |

| RPE8 <sup>(3)</sup>  | RPE8R    | RPE8R<3:0>  | 1110 = Reserved                              |

| RPF2 <sup>(1)</sup>  | +        |             | 1111 = Reserved                              |

Note 1: This selection is not available on 64-pin USB devices.

- 2: This selection is only available on 100-pin General Purpose devices.

- 3: This selection is not available on 64-pin devices.

- 4: This selection is not available when USBID functionality is used on USB devices.

- 5: This selection is not available on devices without a CAN module.

- 6: This selection is not available on USB devices.

- 7: This selection is not available when VBUSON functionality is used on USB devices.

TABLE 11-11: PORTF REGISTER MAP FOR PIC32MX130F128L, PIC32MX150F256L, AND PIC32MX170F512L DEVICES ONLY

| ess                         |                                 |           | Bits  |       |               |               |       |       |      |              |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6500                        | ANSELF                          | 31:16     | _     | _     | _             | _             | _     | _     | -    | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0300                        | ANOLLI                          | 15:0      | _     |       | ANSELE13      | ANSELE12      | _     | _     |      | ANSELE8      |              | _            | _            | _            | _            | ANSELE2      | ANSELE1      | ANSELE0      | 3107          |

| 6510                        | TRISF                           | 31:16     | _     | _     | _             | _             | _     | _     | _    | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0010                        |                                 | 15:0      | _     | _     | TRISF13       | TRISF12       | _     | _     | _    | TRISF8       | TRISF7       | TRISF6       | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | 31FF          |

| 6520                        | PORTF                           | 31:16     | _     | _     | _             | _             | _     | _     | _    | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0020                        | TOITH                           | 15:0      | _     | _     | RF13          | RF12          | _     | _     | _    | RF8          | RF7          | RF6          | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | _     |       | _             | _             | _     | _     | _    | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | D(II)                           | 15:0      | _     |       | LATF13        | LATF12        | _     | _     | _    | LATF8        | LATF7        | LATF6        | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | _     |       | _             | _             | _     | _     | _    | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 00+0                        | ODOI                            | 15:0      | _     | _     | ODCF13        | ODCF12        | _     | _     | -    | ODCF8        | ODCF7        | ODCF6        | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | 0000          |

| 6550                        | CNPUF                           | 31:16     | _     | _     | _             | _             | _     | _     | -    | _            | _            | _            | _            | _            | _            | _            | -            | _            | 0000          |

| 0000                        | CIVI OI                         | 15:0      | _     | _     | CNPUF13       | CNPUF12       | _     | _     | -    | CNPUF8       | CNPUF7       | CNPUF6       | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | 0000          |

| 6560                        | CNPDF                           | 31:16     | _     | _     | _             | _             | _     | _     | -    | _            | _            | _            | _            | _            | _            | _            | -            | _            | 0000          |

| 0300                        | CIVI DI                         | 15:0      | _     | _     | CNPDF13       | CNPDF12       | _     | _     | -    | CNPDF8       | CNPDF7       | CNPDF6       | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | 0000          |

| 6570                        | CNCONF                          | 31:16     | _     | _     | _             | _             | _     | _     | -    | _            | _            | _            | _            | _            | _            | _            | -            | _            | 0000          |

| 0370                        | CINCOIN                         | 15:0      | ON    | _     | SIDL          | _             | _     | _     | -    | _            | _            | _            | _            | _            | _            | _            | -            | _            | 0000          |

| 6580                        | CNENF                           | 31:16     | _     | _     | _             | _             | _     | _     | -    | _            | _            | _            | _            | _            | _            | _            | -            | _            | 0000          |

| 0300                        | CINCINI                         | 15:0      | _     | _     | CNIEF13       | CNIEF12       | _     | 1     | -    | CNIEF8       | CNIEF7       | CNIEF6       | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _             | _             | _     | 1     | -    | -            | _            | _            | 1            | -            | _            | _            | 1            | _            | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | _     | CN<br>STATF13 | CN<br>STATF12 | _     | _     | -    | CN<br>STATF8 | CN<br>STATF7 | CN<br>STATF6 | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | 0000          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

TABLE 11-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| SS                          |                  |               | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |        |            |      |            |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|--------|------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2   | 17/1       | 16/0 | All Resets |

| FB38                        | RPA14R           | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | 1    | _    | _    | _    | _      | _          | _    | 0000       |

| 1 000                       | 1(17(14)(        | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA14  | 1<3:0>     |      | 0000       |

| FB3C                        | RPA15R           | 31:16         | _     |       | _     | _     |       | _     | _    |      |      |      | _    | _    | _    | _      | _          | _    | 0000       |

| . 500                       |                  | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA1   | 5<3:0>     |      | 0000       |

| FB40                        | RPB0R            | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |        | _          | _    | 0000       |

|                             |                  | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB0   | <3:0>      |      | 0000       |

| FB44                        | RPB1R            | 31:16         |       | _     | _     | _     |       | _     | _    |      |      |      | _    | _    | _    |        |            |      | 0000       |

|                             |                  | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    |      | _    | _    |      | RPB1   | <3:0>      |      | 0000       |

| FB48                        | RPB2R            | 31:16         |       |       |       |       |       |       | _    |      |      |      |      | _    | _    | _      | _          |      | 0000       |

|                             |                  | 15:0          |       |       | _     |       | _     | _     |      | _    |      |      | _    |      |      | RPB2   | <3:0>      |      | 0000       |

| FB4C                        | RPB3R            | 31:16         | _     |       | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |        |            |      | 0000       |

|                             |                  | 15:0<br>31:16 | _     |       |       | _     | _     | _     | _    | _    | _    |      | _    | _    |      | RPB3   | <3:0>      |      | 0000       |

| FB54                        | RPB5R            |               | _     | _     | _     | _     | _     | _     | _    |      | _    |      | _    | _    | _    | RPB5   |            |      | 0000       |

|                             |                  | 15:0<br>31:16 |       |       | _     |       | _     |       | _    |      |      |      | _    |      |      | — RPB0 |            |      | 0000       |

| FB58                        | RPB6R            | 15:0          | _     |       |       | _     |       |       | _    | _    |      |      |      | _    |      | RPB6   | -<br><3:0> |      | 0000       |

|                             |                  | 31:16         |       |       |       |       |       |       |      |      |      |      |      |      | _    | _      | _          | _    | 0000       |

| FB5C                        | RPB7R            | 15:0          |       |       |       |       |       |       |      |      |      |      |      |      | _    | RPB7   |            |      | 0000       |

|                             |                  | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _      | _          | _    | 0000       |

| FB60                        | RPB8R            | 15:0          | _     | _     | _     | _     | _     | _     | _    |      |      |      | _    | _    |      | RPB8   |            |      | 0000       |

|                             |                  | 31:16         | _     | _     | _     | _     | _     | _     | _    |      |      |      | _    | _    | _    | -      | _          |      | 0000       |

| FB64                        | RPB9R            | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    |      | RPB9   | <3:0>      |      | 0000       |

|                             |                  | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _      | _          | _    | 0000       |

| FB68                        | RPB10R           | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    |      | _    | _    |      | RPB10  | )<3:0>     |      | 0000       |

|                             | DDD 4 4 D        | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _      | _          | _    | 0000       |

| FB78                        | RPB14R           | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB1   | 1<3:0>     |      | 0000       |

| ED76                        | DDD45D           | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _      | _          | _    | 0000       |

| FB7C                        | RPB15R           | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB1   | 5<3:0>     |      | 0000       |

| ED04                        | DDC4D            | 31:16         | _     | _     | _     | _     | -     | _     | _    | _    | _    |      | _    | _    | -    | _      | _          | _    | 0000       |

| FB84                        | RPC1R            | 15:0          | _     | -     | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    |      | RPC1   | <3:0>      |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available if the associated RPx function is not present on the device. Refer to the pin table for the specific device to determine availability.

# REGISTER 13-1: TxCON: TYPE B TIMER 'x' CONTROL REGISTER (CONTINUED)('x' = 2 THROUGH 5)

bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

1 = Odd numbered and even numbered timers form a 32-bit timer

0 = Odd numbered and even numbered timers form a separate 16-bit timer

bit 2 Unimplemented: Read as '0'

bit 1 TCS: Timer Clock Source Select bit<sup>(3)</sup>

1 = External clock from TxCK pin

0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- **4:** While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

## REGISTER 18-1: $12CxCON: 1^2C'x' CONTROL REGISTER ('x' = 1 AND 2)$

|              |                   |                   |                   |                   | ,                 |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

**Legend:** HC = Cleared in Hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: I<sup>2</sup>C Enable bit<sup>(1)</sup>

1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

$0 = \text{Disables the } 1^2\text{C module}$ ; all  $1^2\text{C pins are controlled by PORT functions}$

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

## If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4   | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|---------------------|---------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0                 | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                   | _                  | _                   | _                   |                   | _                | _                |

| 22:46        | R/W-0, HC         | U-0                 | U-0                | U-0                 | U-0                 | U-0               | R/W-0            | U-0              |

| 23:16        | RDSTART           | _                   | _                  | _                   | _                   | _                 | DUALBUF          | _                |

| 15:0         | R/W-0             | U-0                 | R/W-0              | R/W-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                   | SIDL               | ADRMU               | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7:0          | R/W-0             | R/W-0               | R/W-0              | R/W-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | CS2P <sup>(2)</sup> | CS1P <sup>(2)</sup> |                   | WRSP             | RDSP             |

Legend:HC = Hardware clearedR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23 RDSTART: Start a Read on the PMP Bus bit (3)

1 = Start a read cycle on the PMP bus

0 = No effect

This bit is cleared by hardware at the end of the read cycle when the BUSY bit (PMMODE<15>) = 0.

bit 22-18 Unimplemented: Read as '0'

bit 17 **DUALBUF:** Parallel Master Port Dual Read/Write Buffer Enable bit

This bit is only valid in Master mode.

1 = PMP uses separate registers for reads and writes

Reads: PMRADDR and PMRDIN Writes: PMRWADDR and PMDOUT

0 = PMP uses legacy registers for reads and writes

Reads/Writes: PMADDR and PMRDIN

bit 16 Unimplemented: Read as '0'

bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

1 = PMP enabled

0 = PMP disabled, no off-chip access performed

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

11 = Lower 8 bits of address are multiplexed on PMD<15:0> pins

10 = All 16 bits of address are multiplexed on PMD<7:0> pins

01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

00 = Address and data appear on separate pins

bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

1 = PMP module uses TTL input buffers

0 = PMP module uses Schmitt Trigger input buffer

bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

1 = PMWR/PMENB port enabled

0 = PMWR/PMENB port disabled

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

2: These bits have no effect when their corresponding pins are used as address lines.

## 21.1 Control Registers

## TABLE 21-1: RTCC REGISTER MAP

| ess                         |                                 |           |        |       |         |          |            |       |        |              | Bits      |          |        |              |         |         |         |       |            |

|-----------------------------|---------------------------------|-----------|--------|-------|---------|----------|------------|-------|--------|--------------|-----------|----------|--------|--------------|---------|---------|---------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13   | 28/12    | 27/11      | 26/10 | 25/9   | 24/8         | 23/7      | 22/6     | 21/5   | 20/4         | 19/3    | 18/2    | 17/1    | 16/0  | All Resets |

| 0200                        | DTCCON                          | 31:16     | _      | _     | _       | _        | _          | _     |        |              |           |          | CAL<   | 9:0>         |         |         |         |       | 0000       |

| 0200                        | RTCCON                          | 15:0      | ON     | _     | SIDL    | _        | _          | RTSEC |        |              |           | RTCCLKON | _      | _            | RTCWREN | RTCSYNC | HALFSEC | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | _      | _     | _       | _        |            |       |        |              |           | _        | 0000   |              |         |         |         |       |            |

| 0210                        | KTOALKW                         | 15:0      | ALRMEN | CHIME | PIV     | ALRMSYNC |            | AMAS  | K<3:0> |              | ARPT<7:0> |          |        |              |         |         | 0000    |       |            |

| 0220                        | RTCTIME                         | 31:16     |        | HR1   | 0<3:0>  |          |            | HR01  | <3:0>  |              |           | MIN10<   | 3:0>   |              |         | MIN01   | <3:0>   |       | xxxx       |

| 0220                        | KICIIWL                         | 15:0      |        | SEC1  | 0<3:0>  |          |            | SEC0  | 1<3:0> |              |           | _        | _      | _            | _       | _       | _       | _     | xx00       |

| 0230                        | RTCDATE                         | 31:16     |        | YEAR  | 10<3:0> |          |            | YEARO | 1<3:0> |              |           | MONTH10  | )<3:0> |              |         | MONTH   | 01<3:0> |       | xxxx       |

| 0230                        | KICDAIE                         | 15:0      |        | DAY1  | 0<3:0>  |          |            | DAY0  | 1<3:0> |              | _         | _        | _      | _            |         | WDAY0   | 1<3:0>  |       | xx00       |

| 0240                        | ALRMTIME                        | 31:16     |        | HR1   | 0<3:0>  |          |            | HR01  | <3:0>  |              |           | MIN10<   | 3:0>   |              |         | MIN01   | <3:0>   |       | xxxx       |

| 0240                        | ALKIVITIVIE                     | 15:0      |        | SEC1  | 0<3:0>  |          |            | SEC0  | 1<3:0> |              | _         | _        | _      | _            | _       | _       | _       | _     | xx00       |

| 0250                        | ALRMDATE                        | 31:16     | _      | _     | _       | _        |            |       |        | MONTH10<3:0> |           |          |        | MONTH01<3:0> |         |         |         | 00xx  |            |

| 0250                        | ALKIVIDAIE                      | 15:0      |        | DAY1  | 0<3:0>  |          | DAY01<3:0> |       |        | _            | _         | _        | _      |              | WDAY0   | 1<3:0>  |         | xx0x  |            |

.egend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information

PIC32MX1XX/2XX/5XX 64/100-PIN FAMILY

#### RTCTIME: RTC TIME VALUE REGISTER REGISTER 21-3:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   | HR10              | <3:0>             |                   |                   | HR01              | <3:0>            |                  |

| 22.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MIN10             | <3:0>             |                   |                   | MIN01             | <3:0>            |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | SEC10<3           |                   | <3:0>             |                   |                   | SEC01             | <3:0>            |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 |                   |                  | _                |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10s place digits; contains a value from 0 to 2 bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9 bit 23-20 MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digits; contains a value from 0 to 5 bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9 bit 15-12 SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digits; contains a value from 0 to 5 bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9 bit 7-0

Note: This register is only writable when RTCWREN = 1 (RTCCON<3>).

Unimplemented: Read as '0'

#### **REGISTER 22-2:** AD1CON2: ADC CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 13.6         |                   | VCFG<2:0>         |                   | OFFCAL            | _                 | CSCNA             | _                | _                |

| 7:0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | BUFS              |                   |                   | SMP               | I<3:0>            |                   | BUFM             | ALTS             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVDD               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVdd               | AVss               |

bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

bit 11 Unimplemented: Read as '0'

bit 10 **CSCNA:** Input Scan Select bit

1 = Scan inputs

0 = Do not scan inputs

bit 9-8 Unimplemented: Read as '0'

bit 7 BUFS: Buffer Fill Status bit Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

bit 6 Unimplemented: Read as '0'

bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence 1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

bit 1 BUFM: ADC Result Buffer Mode Select bit

1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

bit 0 **ALTS:** Alternate Input Sample Mode Select bit

> 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

0 = Always use Sample A input multiplexer settings

### REGISTER 23-1: C1CON: CAN MODULE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                                      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------------------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0                                                                 | R/W-0            |

| 31.24        | _                 | _                 | _                 | _                 | ABAT REQOP<2      |                   |                                                                       | >                |

| 23:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0                                                                   | U-0              |

| 23.10        | C                 | DPMOD<2:0>        | ı                 | CANCAP            | _                 | _                 | 0/2 25/17/9/1 24/16  R/W-0 R/W  REQOP<2:0>  U-0 U-1  U-0 U-1  U-0 U-1 | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0                                                                   | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDLE             | _                 | CANBUSY           | _                 | _                                                                     | _                |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                                                                 | R/W-0            |

| 7.0          | _                 | _                 | _                 |                   |                   |                   |                                                                       |                  |

Legend:HC = Hardware ClearS = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-28 Unimplemented: Read as '0'

bit 27 ABAT: Abort All Pending Transmissions bit

1 = Signal all transmit buffers to abort transmission

0 = Module will clear this bit when all transmissions aborted

bit 26-24 **REQOP<2:0>:** Request Operation Mode bits

111 = Set Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Set Configuration mode

011 = Set Listen Only mode

010 = Set Loopback mode

001 = Set Disable mode

000 = Set Normal Operation mode

bit 23-21 OPMOD<2:0>: Operation Mode Status bits

111 = Module is in Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Module is in Configuration mode

011 = Module is in Listen Only mode

010 = Module is in Loopback mode

001 = Module is in Disable mode

000 = Module is in Normal Operation mode

bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

1 = CANTMR value is stored on valid message reception and is stored with the message

0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

bit 19-16 Unimplemented: Read as '0'

bit 15 **ON:** CAN On bit<sup>(1)</sup>

1 = CAN module is enabled

0 = CAN module is disabled

bit 14 Unimplemented: Read as '0'

**Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

### REGISTER 23-10: C1FLTCON0: CAN FILTER CONTROL REGISTER 0 (CONTINUED)

```

bit 20-16

FSEL2<4:0>: FIFO Selection bits

11111 = Reserved

10000 = Reserved

01111 = Message matching filter is stored in FIFO buffer 15

00000 = Message matching filter is stored in FIFO buffer 0

FLTEN1: Filter 1 Enable bit

bit 15

1 = Filter is enabled

0 = Filter is disabled

bit 14-13

MSEL1<1:0>: Filter 1 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

FSEL1<4:0>: FIFO Selection bits

bit 12-8

11111 = Reserved

10000 = Reserved

01111 = Message matching filter is stored in FIFO buffer 15

00000 = Message matching filter is stored in FIFO buffer 0

bit 7

FLTEN0: Filter 0 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 6-5

MSEL0<1:0>: Filter 0 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

FSEL0<4:0>: FIFO Selection bits

bit 4-0

11111 = Reserved

10000 = Reserved

01111 = Message matching filter is stored in FIFO buffer 15

00000 = Message matching filter is stored in FIFO buffer 0

```

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

### 30.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 30.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 30.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 30.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

### **30.10 MPLAB PM3 Device Programmer**

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

**TABLE 31-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS**

| DC CHA        | RACTERIS        | STICS                                                        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +105^{\circ}\text{C}$ for V-temp |      |                    |       |                                                                  |  |

|---------------|-----------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|------------------------------------------------------------------|--|

| Param.<br>No. | Symbol          | Characteristics                                              | Min.                                                                                                                                                                                                                                               | Тур. | Max.               | Units | Comments                                                         |  |

| D312          | TSET            | Internal 4-bit DAC<br>Comparator Reference<br>Settling time. | _                                                                                                                                                                                                                                                  | _    | 10                 | μs    | See Note 1                                                       |  |

| D313          | DACREFH         | CVREF Input Voltage                                          | AVss                                                                                                                                                                                                                                               | _    | AVDD               | V     | CVRSRC with CVRSS = 0                                            |  |

|               | Reference Range | Reference Range                                              | VREF-                                                                                                                                                                                                                                              | _    | VREF+              | V     | CVRSRC with CVRSS = 1                                            |  |

| D314          | DVREF           | CVREF Programmable Output Range                              | 0                                                                                                                                                                                                                                                  | _    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with DACREFH/24 step size                     |  |

|               |                 |                                                              | 0.25 x<br>DACREFH                                                                                                                                                                                                                                  | _    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/<br>32 step size |  |

| D315          | DACRES          | Resolution                                                   | _                                                                                                                                                                                                                                                  | _    | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                         |  |

|               |                 |                                                              | _                                                                                                                                                                                                                                                  | _    | DACREFH/32         |       | CVRCON <cvrr> = 0</cvrr>                                         |  |

| D316          | DACACC          | ACC Absolute Accuracy <sup>(2)</sup>                         | _                                                                                                                                                                                                                                                  | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                          |  |

|               |                 |                                                              | _                                                                                                                                                                                                                                                  | _    | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                          |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

### **TABLE 31-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS**