Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

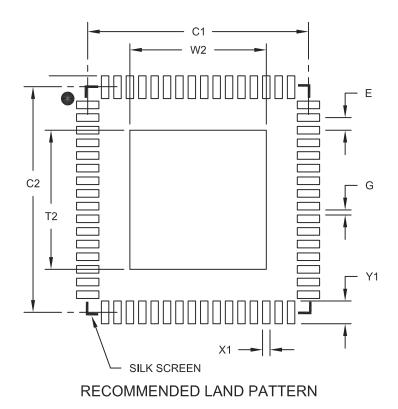

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx570f512ht-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)**

| bin<br>N/<br>FP<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S | 100-pin<br>TQFP                       | Pin<br>Type                                | Buffer                                                                                                                                     |                                                                                                                                |  |  |  |  |  |

|---------------------------------------------------------|---------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| rs<br>rs<br>rs                                          | 550                                   |                                            | Туре                                                                                                                                       | Description                                                                                                                    |  |  |  |  |  |

| rs<br>rs                                                | PPS                                   | Ι                                          | ST                                                                                                                                         | UART3 Clear to Send                                                                                                            |  |  |  |  |  |

| S                                                       | PPS                                   | 0                                          | _                                                                                                                                          | UART3 Ready to Send                                                                                                            |  |  |  |  |  |

|                                                         | PPS                                   | Ι                                          | ST                                                                                                                                         | UART3 Receive                                                                                                                  |  |  |  |  |  |

| S                                                       | PPS                                   | 0                                          | _                                                                                                                                          | UART3 Transmit                                                                                                                 |  |  |  |  |  |

| 5                                                       | PPS                                   | Ι                                          | ST                                                                                                                                         | UART4 Clear to Send                                                                                                            |  |  |  |  |  |

| S                                                       | PPS                                   | 0                                          | _                                                                                                                                          | UART4 Ready to Send                                                                                                            |  |  |  |  |  |

| S                                                       | PPS                                   | Ι                                          | ST                                                                                                                                         | UART4 Receive                                                                                                                  |  |  |  |  |  |

| S                                                       | PPS                                   | 0                                          | _                                                                                                                                          | UART4 Transmit                                                                                                                 |  |  |  |  |  |

| -                                                       | PPS                                   | Ι                                          | ST                                                                                                                                         | UART5 Clear to Send                                                                                                            |  |  |  |  |  |

| -                                                       | PPS                                   | 0                                          |                                                                                                                                            | UART5 Ready to Send                                                                                                            |  |  |  |  |  |

|                                                         | PPS                                   | Ι                                          | ST                                                                                                                                         | UART5 Receive                                                                                                                  |  |  |  |  |  |

| -                                                       | PPS                                   | 0                                          | _                                                                                                                                          | UART5 Transmit                                                                                                                 |  |  |  |  |  |

| 50 <b>(2)</b>                                           | 55 <sup>(1)</sup> , 70 <sup>(2)</sup> | I/O                                        | ST                                                                                                                                         | Synchronous Serial Clock Input/Output for SPI1                                                                                 |  |  |  |  |  |

| S                                                       | PPS                                   | Ι                                          | _                                                                                                                                          | SPI1 Data In                                                                                                                   |  |  |  |  |  |

| S                                                       | PPS                                   | 0                                          | ST                                                                                                                                         | SPI1 Data Out                                                                                                                  |  |  |  |  |  |

| S                                                       | PPS                                   | I/O                                        | _                                                                                                                                          | SPI1 Slave Synchronization for Frame Pulse I/O                                                                                 |  |  |  |  |  |

|                                                         | 10                                    | I/O                                        | ST                                                                                                                                         | Synchronous Serial Clock Input/Output for SPI2                                                                                 |  |  |  |  |  |

| S                                                       | PPS                                   | Ι                                          | _                                                                                                                                          | SPI2 Data In                                                                                                                   |  |  |  |  |  |

| S                                                       | PPS                                   | 0                                          | ST                                                                                                                                         | SPI2 Data Out                                                                                                                  |  |  |  |  |  |

| S                                                       | PPS                                   | I/O                                        | _                                                                                                                                          | SPI2 Slave Synchronization for Frame Pulse I/O                                                                                 |  |  |  |  |  |

| 9                                                       | 39                                    | I/O                                        | ST                                                                                                                                         | Synchronous Serial Clock Input/Output for SPI3                                                                                 |  |  |  |  |  |

| S                                                       | PPS                                   | Ι                                          | _                                                                                                                                          | SPI3 Data In                                                                                                                   |  |  |  |  |  |

| S                                                       | PPS                                   | 0                                          | ST                                                                                                                                         | SPI3 Data Out                                                                                                                  |  |  |  |  |  |

| S                                                       | PPS                                   | I/O                                        | _                                                                                                                                          | SPI3 Slave Synchronization for Frame Pulse I/O                                                                                 |  |  |  |  |  |

| -                                                       | 48                                    | I/O                                        | ST                                                                                                                                         | Synchronous Serial Clock Input/Output for SPI4                                                                                 |  |  |  |  |  |

| -                                                       | PPS                                   | Ι                                          |                                                                                                                                            | SPI4 Data In                                                                                                                   |  |  |  |  |  |

|                                                         | PPS                                   | 0                                          | ST                                                                                                                                         | SPI4 Data Out                                                                                                                  |  |  |  |  |  |

| -                                                       | PPS                                   | I/O                                        | _                                                                                                                                          | SPI4 Slave Synchronization for Frame Pulse I/O                                                                                 |  |  |  |  |  |

|                                                         |                                       | I/O                                        | ST                                                                                                                                         | Synchronous Serial Clock Input/Output for I2C1                                                                                 |  |  |  |  |  |

| 43 <b>(2)</b>                                           | 56 <sup>(1)</sup> , 67 <sup>(2)</sup> | I/O                                        | ST                                                                                                                                         | Synchronous Serial Data Input/Output for I2C1                                                                                  |  |  |  |  |  |

| 2                                                       | 58                                    | I/O                                        | ST                                                                                                                                         | Synchronous Serial Clock Input/Output for I2C2                                                                                 |  |  |  |  |  |

| 1                                                       | 59                                    | I/O                                        | ST                                                                                                                                         | Synchronous Serial Data Input/Output for I2C2                                                                                  |  |  |  |  |  |

| 3                                                       | 17                                    | Ι                                          | ST                                                                                                                                         | JTAG Test Mode Select Pin                                                                                                      |  |  |  |  |  |

| 7                                                       | 38                                    | I                                          | ST                                                                                                                                         | JTAG Test Clock Input Pin                                                                                                      |  |  |  |  |  |

| 3                                                       | 60                                    | I                                          | _                                                                                                                                          | JTAG Test Clock Input Pin                                                                                                      |  |  |  |  |  |

| 4                                                       | 61                                    | 0                                          | _                                                                                                                                          | JTAG Test Clock Output Pin                                                                                                     |  |  |  |  |  |

| 1<br>7<br>3<br>4                                        |                                       | 59<br>17<br>38<br>60<br>61<br>CMOS compati | 59         I/O           17         I           38         I           60         I           61         O           CMOS compatible input | 59         I/O         ST           17         I         ST           38         I         ST           60         I         — |  |  |  |  |  |

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices with a USB module.

4: This pin is only available on 100-pin devices without a USB module.

## 3.2 Architecture Overview

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

# 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/<br/>DIVIDE UNIT LATENCIES AND REPEAT RATES

| Op code                 | Operand Size (mul rt) (div rs) | Latency                                                                                                                                            | Repeat Rate |  |  |  |  |  |

|-------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1                                                                                                                                                  | 1           |  |  |  |  |  |

| MSUB/MSUBU              | 32 bits                        | 2                                                                                                                                                  | 2           |  |  |  |  |  |

| MUL                     | 16 bits                        | 1         1           2         2           2         1           3         2           12         1           19         1           26         2 | 1           |  |  |  |  |  |

|                         | 32 bits                        | 3                                                                                                                                                  | 2           |  |  |  |  |  |

| DIV/DIVU                | 8 bits                         | 12                                                                                                                                                 | 11          |  |  |  |  |  |

|                         | 16 bits                        | 19                                                                                                                                                 | 18          |  |  |  |  |  |

|                         | 24 bits                        | 26                                                                                                                                                 | 25          |  |  |  |  |  |

|                         | 32 bits                        | 33                                                                                                                                                 | 32          |  |  |  |  |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 04.04        | U-0               | U-0                  | R/W-y             | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |

| 31:24        | _                 | —                    | Р                 | LLODIV<2:0>       | >                 | FRCDIV<2:0>           |                  |                  |

| 22.16        | U-0               | R-0                  | R-1               | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDI∖             | /<1:0>            | PLLMULT<2:0>          |                  |                  |

| 15.0         | U-0               | R-0                  | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |

| 15:8         | _                 |                      | COSC<2:0>         |                   | _                 | NOSC<2:0>             |                  |                  |

| 7.0          | R/W-0             | R-0                  | R-0               | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

#### Legend:

bit 22

#### y = Value set from Configuration bits on POR

| •                                 | •                | •                                  |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-30 Unimplemented: Read as '0'

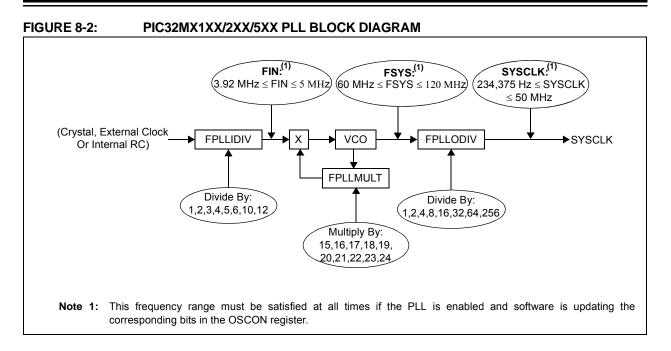

bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- SOSCRDY: Secondary Oscillator (SOSC) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 =Clock is multiplied by 17

- 001 =Clock is multiplied by 16

- 000 = Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = PLL module is in lock or PLL module start-up timer is satisfied

- 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 **CF:** Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- Note 1: This bit is available on PIC32MX2XX/5XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected</li> <li>Either the source or the destination address is invalid.</li> </ul>                                                        |

0 = No interrupt is pending

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6               | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|---------------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                             | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | —                 | —                               | _                       |                   | —                    | —                 | —                     | —                       |

| 23:16        | U-0               | U-0                             | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | —                 | —                               | _                       |                   | —                    | _                 | _                     | —                       |

| 15:8         | U-0               | U-0                             | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.6         | —                 | —                               | _                       |                   | —                    | —                 | —                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS                      | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | STALLIF ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | UIALLII           |                                 |                         | IULLII            |                      | 00111             |                       | DETACHIF <sup>(6)</sup> |

|              | •                 | •                               |                         |                   |                      |                   |                       |                         |

## REGISTER 10-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settal | ble bit            |

|-------------------|-------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented b  | vit, read as '0'   |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 |    | STALLIF: STALL Handshake Interrupt bit                                                                                                                                                 |

|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |    | 1 = In Host mode, a STALL handshake was received during the handshake phase of the transaction                                                                                         |

|       |    | In Device mode, a STALL handshake was transmitted during the handshake phase of the transaction                                                                                        |

|       |    | 0 = STALL handshake has not been sent                                                                                                                                                  |

| bit 6 |    | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup>                                                                                                                               |

|       |    | 1 = Peripheral attachment was detected by the USB module                                                                                                                               |

|       |    | 0 = Peripheral attachment was not detected                                                                                                                                             |

| bit 5 |    | RESUMEIF: Resume Interrupt bit <sup>(2)</sup>                                                                                                                                          |

|       |    | 1 = K-State is observed on the D+ or D- pin for 2.5 $\mu$ s                                                                                                                            |

|       |    | 0 = K-State is not observed                                                                                                                                                            |

| bit 4 |    | IDLEIF: Idle Detect Interrupt bit                                                                                                                                                      |

|       |    | 1 = Idle condition detected (constant Idle state of 3 ms or more)                                                                                                                      |

|       |    | 0 = No Idle condition detected                                                                                                                                                         |

| bit 3 |    | <b>TRNIF:</b> Token Processing Complete Interrupt bit <sup>(3)</sup>                                                                                                                   |

|       |    | <ul> <li>1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information</li> <li>0 = Processing of current token not complete</li> </ul> |

| h:+ 0 |    |                                                                                                                                                                                        |

| bit 2 |    | <b>SOFIF:</b> SOF Token Interrupt bit<br>1 = SOF token received by the peripheral or the SOF threshold reached by the host                                                             |

|       |    | 0 = SOF token was not received nor threshold reached                                                                                                                                   |

| bit 1 |    | <b>UERRIF:</b> USB Error Condition Interrupt bit <sup>(4)</sup>                                                                                                                        |

| DICT  |    | 1 = Unmasked error condition has occurred                                                                                                                                              |

|       |    | 0 = Unmasked error condition has not occurred                                                                                                                                          |

| bit 0 |    | URSTIF: USB Reset Interrupt bit (Device mode) <sup>(5)</sup>                                                                                                                           |

| 2.00  |    | 1 = Valid USB Reset has occurred                                                                                                                                                       |

|       |    | 0 = No USB Reset has occurred                                                                                                                                                          |

| bit 0 |    | DETACHIF: USB Detach Interrupt bit (Host mode) <sup>(6)</sup>                                                                                                                          |

|       |    | 1 = Peripheral detachment was detected by the USB module                                                                                                                               |

|       |    | 0 = Peripheral detachment was not detected                                                                                                                                             |

| Note  | 1. | This bit is valid only if the HOSTEN bit is set (see Register 10-11), there is no activity on the USB for                                                                              |

| noto  | •• | $2.5 \mu$ s, and the current bus state is not SE0.                                                                                                                                     |

|       | 2: | When not in Suspend mode, this interrupt should be disabled.                                                                                                                           |

|       | 3: | Clearing this bit will cause the STAT FIFO to advance.                                                                                                                                 |

|       | 4: | Only error conditions enabled through the U1EIE register will set this bit.                                                                                                            |

|       | 5: | Device mode.                                                                                                                                                                           |

|       | 6: | Host mode.                                                                                                                                                                             |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | _                 | —                 | _                 | —                 | _                 | _                 | _                | -                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | _                 |                   | _                 | _                 | -                 | -                | -                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         |                   | _                 |                   | _                 | _                 | -                 | -                | -                |  |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |  |

### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| 9                                 |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device enabled

- 0 = Direct connection to a low-speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

#### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive enabled

- 0 = Endpoint n receive disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit enabled

- 0 = Endpoint n transmit disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake enabled

- 0 = Endpoint Handshake disabled (typically used for isochronous endpoints)

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------|

| 21.24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 31:24        | _                    | —                 | —                 | —                 | —                        | _                 | -                | _                |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0              |

| 23.10        | —                    | _                 | —                 | —                 | —                        | —                 | _                | —                |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | SPISGNEXT            | _                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR           |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0            |

|              | AUDEN <sup>(1)</sup> |                   |                   |                   | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | )<1:0>(1,2)      |

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| ı' |

|----|

| ļ  |

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extened

#### bit 14-13 Unimplemented: Read as '0'

- bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit 1 = Frame Error overflow generates error events 0 = Frame Error does not generate error events bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit 1 = Receive overflow generates error events 0 = Receive overflow does not generate error events bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit 1 = Transmit Underrun Generates Error Events 0 = Transmit Underrun Does Not Generates Error Events bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions) 1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data 0 = A ROV is a critical error which stop SPI operation bit 8 IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions) 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty 0 = A TUR is a critical error which stop SPI operation AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup> bit 7 1 = Audio protocol enabled 0 = Audio protocol disabled bit 6-5 Unimplemented: Read as '0' AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup> bit 3 1 = Audio data is mono (Each data word is transmitted on both left and right channels) 0 = Audio data is stereo bit 2 Unimplemented: Read as '0' AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup> bit 1-0 11 = PCM/DSP mode 10 = Right Justified mode 01 = Left Justified mode  $00 = I^2 S \mod I$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

## REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER (CONTINUED)

bit 3 SPITBE: SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB. bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPI Transmit Buffer Full Status bit 1 = Transmit not yet started, SPITXB is full 0 = Transmit buffer is not full Standard Buffer Mode: Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR. Enhanced Buffer Mode: Set when CWPTR + 1 = SRPTR; cleared otherwise bit 0 SPIRBF: SPI Receive Buffer Full Status bit 1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

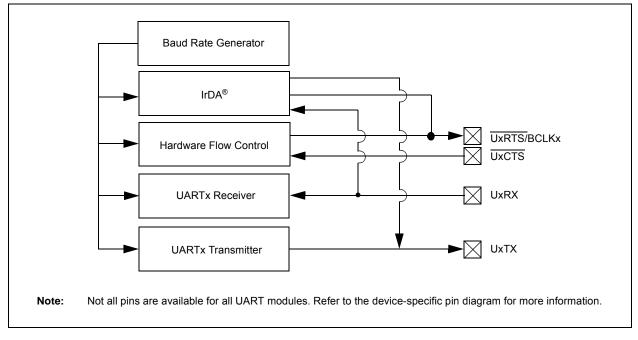

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX/5XX 64/100-pin family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, odd or no parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9<sup>th</sup> bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART.

#### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

|                             | LE 19-1:                 | UAI       |        | ROUGE   | UARTS    |       |           |       |       | (ש.         |             |         |       |          |          |      |        |       |            |

|-----------------------------|--------------------------|-----------|--------|---------|----------|-------|-----------|-------|-------|-------------|-------------|---------|-------|----------|----------|------|--------|-------|------------|

| ess                         |                          | đ         |        |         |          |       |           |       |       | Bi          | ts          |         |       |          |          |      |        |       | s          |

| Virtual Address<br>(BF80_#) | Register<br>Name         | Bit Range | 31/15  | 30/14   | 29/13    | 28/12 | 27/11     | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6440                        |                          | 31:16     | _      | —       | —        |       | —         |       | —     | —           |             | —       | _     |          | _        | _    | _      |       | 0000       |

| 0440                        | USBRG. /                 | 15:0      |        |         |          |       |           |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 6600                        | U4MODE <sup>(1)</sup>    | 31:16     | _      | _       | _        |       | _         |       | _     | _           |             | —       | _     |          | _        | _    | _      |       | 0000       |

| 0000                        | 04IVIODL.                | 15:0      | ON     | —       | SIDL     | IREN  | RTSMD     | —     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6610                        | U4STA <sup>(1)</sup>     | 31:16     | _      | —       | —        | -     | —         | _     | —     | ADM_EN      |             |         |       | ADDF     | R<7:0>   |      | -      |       | 0000       |

| 0010                        | 04017                    | 15:0      | UTXISE | EL<1:0> | UTXINV   | URXEN | UTXBRK    | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6620                        | U4TXREG                  | 31:16     | —      |         | —        | _     | _         | _     |       | —           |             | —       | —     | _        | —        | —    | —      | —     | 0000       |

| 0020                        | OFINICO                  | 15:0      | —      |         | —        | _     | _         | _     |       | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 6630                        | U4RXREG                  | 31:16     | —      |         | —        | _     | _         | _     |       | _           |             | —       | _     | _        | _        | _    | _      | —     | 0000       |

| 0000                        | OHIVILO                  | 15:0      | —      |         | —        | _     | _         | _     |       | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 6640                        | U4BRG <sup>(1)</sup>     | 31:16     | —      | —       | —        | —     | —         | —     | —     | —           | —           | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0010                        | U IBIKO                  | 15:0      |        |         |          |       |           |       | Bau   | d Rate Gen  | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 6800                        | U5MODE <sup>(1,2)</sup>  | 31:16     |        | —       | —        |       | —         | _     | —     |             |             | —       | —     |          | —        | —    | —      |       | 0000       |

|                             | 00111022                 | 15:0      | ON     | —       | SIDL     | IREN  | RTSMD     | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6810                        | U5STA <sup>(1,2)</sup>   | 31:16     | —      | —       | —        | —     | —         | —     | —     | ADM_EN      |             |         |       | 1        | R<7:0>   | 1    | 1      | 1     | 0000       |

|                             |                          | 15:0      | UTXISE | EL<1:0> | UTXINV   | URXEN | UTXBRK    | UTXEN | UTXBF | TRMT        | URXIS       | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | FFFF       |

| 6820                        | U5TXREG <sup>(1,2)</sup> | 31:16     | _      |         | —        | _     | —         |       |       |             | _           | —       | —     | —        |          | —    |        |       | 0000       |

|                             |                          | 15:0      | _      |         | —        | _     | —         |       |       | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 6830                        | U5RXREG <sup>(1,2)</sup> | 31:16     | _      |         | —        | —     | —         |       |       | —           | —           | —       | —     | —        | —        | —    | —      | —     | 0000       |

|                             |                          | 1010      | —      |         | <u> </u> |       |           |       |       | 0000        |             |         |       |          |          |      |        |       |            |

| 6840                        | U5BRG <sup>(1,2)</sup>   | 31:16     | —      | —       | —        | —     | —         | —     | —     | —           | —           | —       | —     | —        | —        | —    | —      |       | 0000       |

|                             |                          | 15:0      |        |         |          |       | 'o' Booot |       |       | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

## TABLE 19-1: UART1 THROUGH UART5 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register is only available on 100-pin devices.

| bit 8   | ER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)<br>PTRDEN: Read/Write Strobe Port Enable bit |

|---------|---------------------------------------------------------------------------------------------------------|

|         | 1 = PMRD/PMWR port enabled                                                                              |

|         | 0 = PMRD/PMWR port disabled                                                                             |

| bit 7-6 | CSF<1:0>: Chip Select Function bits <sup>(2)</sup>                                                      |

|         | 11 = Reserved                                                                                           |

|         | 10 = PMCS1 and PMCS2 function as Chip Select                                                            |

|         | 01 = PMCS1 functions as address bit 14; PMCS2 functions as Chip Select                                  |

|         | 00 = PMCS1 and PMCS2 function as address bits 14 and 15, respectively                                   |

| bit 5   | ALP: Address Latch Polarity bit <sup>(2)</sup>                                                          |

|         | <ul> <li>1 = Active-high (PMALL and PMALH)</li> <li>0 = Active-low (PMALL and PMALH)</li> </ul>         |

| bit 4   | CS2P: Chip Select 0 Polarity bit <sup>(2)</sup>                                                         |

|         | 1 = Active-high (PMCS2)                                                                                 |

|         | $0 = \text{Active-low}(\overline{\text{PMCS2}})$                                                        |

| bit 3   | CS1P: Chip Select 0 Polarity bit <sup>(2)</sup>                                                         |

|         | 1 = Active-high (PMCS1)                                                                                 |

|         | $0 = \text{Active-low}(\overline{\text{PMCS1}})$                                                        |

| bit 2   | Unimplemented: Read as '0'                                                                              |

| bit 1   | WRSP: Write Strobe Polarity bit                                                                         |

|         | For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):                                               |

|         | 1 = Write strobe active-high (PMWR)                                                                     |

|         | 0 = Write strobe active-low (PMWR)                                                                      |

|         | For Master mode 1 (MODE<1:0> = $11$ ):                                                                  |

|         | 1 = Enable strobe active-high (PMENB)                                                                   |

|         | 0 = Enable strobe active-low (PMENB)                                                                    |

| bit 0   | RDSP: Read Strobe Polarity bit                                                                          |

|         | For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):                                               |

|         | 1 = Read Strobe active-high (PMRD)                                                                      |

|         | 0 = Read Strobe active-low (PMRD)                                                                       |

|         | For Master mode 1 (MODE<1:0> = 11):                                                                     |

|         | 1 = Read/write strobe active-high (PMRD/PMWR)                                                           |

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- **2:** These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5         | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|---------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 51.24        | —                 | _                 | _                         | _                 | —                 | _                 | —                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | —                         | —                 | —                 | —                 | —                | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0                       | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15.0         | —                 | —                 | —                         |                   |                   | FILHIT<4:0>       |                  |                  |  |  |  |  |

| 7:0          | U-0               | R-1               | R-0                       | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7.0          | _                 |                   | ICODE<6:0> <sup>(1)</sup> |                   |                   |                   |                  |                  |  |  |  |  |

## REGISTER 23-4: C1VEC: CAN INTERRUPT CODE REGISTER

#### Legend:

| R = Rea   | dable bit | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-----------|-----------|------------------|--------------------------|--------------------|--|

| -n = Valu | le at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-13 Unimplemented: Read as '0'

```

bit 12-8 FILHIT<4:0>: Filter Hit Number bit

11111 = Reserved

10000 = Reserved

01111 = Filter 15

00000 = Filter 0

bit 7

Unimplemented: Read as '0'

ICODE<6:0>: Interrupt Flag Code bits<sup>(1)</sup>

bit 6-0

1111111 = Reserved

1001001 = Reserved

1001000 = Invalid message received (IVRIF)

1000111 = CAN module mode change (MODIF)

1000110 = CAN timestamp timer (CTMRIF)

1000101 = Bus bandwidth error (SERRIF)

1000100 = Address error interrupt (SERRIF)

1000011 = Receive FIFO overflow interrupt (RBOVIF)

1000010 = Wake-up interrupt (WAKIF)

1000001 = Error Interrupt (CERRIF)

1000000 = No interrupt

0111111 = Reserved

0010000 = Reserved

0001111 = FIFO15 Interrupt (C1FSTAT<15> set)

0000000 = FIFO0 Interrupt (C1FSTAT<0> set)

```

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 |                   | —                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 |                   | —                 | _                 | _                | -                |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | RXOVF15           | RXOVF14           | RXOVF13           | RXOVF12           | RXOVF11           | RXOVF10           | RXOVF9           | RXOVF8           |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | RXOVF7            | RXOVF6            | RXOVF5            | RXOVF4            | RXOVF3            | RXOVF2            | RXOVF1           | RXOVF0           |

## REGISTER 23-7: C1RXOVF: CAN RECEIVE FIFO OVERFLOW STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 RXOVF<15:0>: FIFOx Receive Overflow Interrupt Pending bit

1 = FIFO has overflowed

0 = FIFO has not overflowed

## REGISTER 23-8: C1TMR: CAN TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 51.24        |                   |                   |                   | CANTS<            | :15:8>            |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | CANTS<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         | CANTSPRE<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                   | CANTSPRE<7:0>     |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 CANTS<15:0>: CAN Time Stamp Timer bits

This is a free-running timer that increments every CANTSPRE system clocks when the CANCAP bit (C1CON<20>) is set.

# bit 15-0 CANTSPRE<15:0>: CAN Time Stamp Timer Prescaler bits 1111 1111 1111 1111 = CAN time stamp timer (CANTS) increments every 65,535 system clocks . . 0000 0000 0000 = CAN time stamp timer (CANTS) increments every system clock

**Note 1:** C1TMR will be paused when CANCAP = 0.

2: The C1TMR prescaler count will be reset on any write to C1TMR (CANTSPRE will be unaffected).

# 25.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

This data sheet summarizes the features Note: of the PIC32MX1XX/2XX/5XX 64/100-pin family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

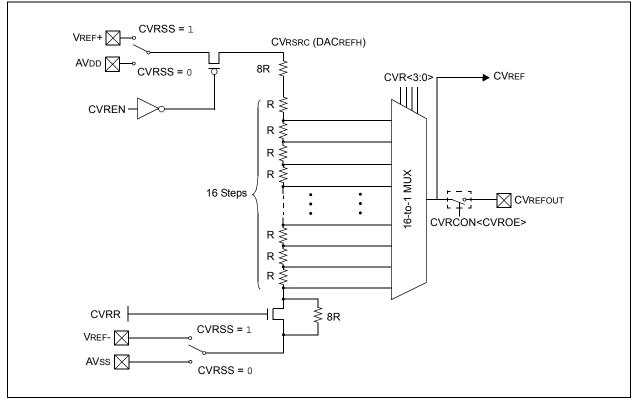

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 25-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The CVREF module has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

#### FIGURE 25-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

# 27.4.1 CONTROLLING CONFIGURATION CHANGES