Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 81                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx570f512l-50i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4: PIN NAMES FOR 100-PIN GENERAL PURPOSE DEVICES (CONTINUED)

| 10    | 100-PIN TQFP (TOP VIEW)                               |       |                           |  |  |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------------------|-------|---------------------------|--|--|--|--|--|--|--|--|--|--|--|

|       | PIC32MX130F128L<br>PIC32MX150F256L<br>PIC32MX170F512L |       |                           |  |  |  |  |  |  |  |  |  |  |  |

|       |                                                       |       | 100 1                     |  |  |  |  |  |  |  |  |  |  |  |

| Pin # | Full Pin Name                                         | Pin # | Full Pin Name             |  |  |  |  |  |  |  |  |  |  |  |

| 71    | RPD11/PMA14/RD11                                      | 86    | Vdd                       |  |  |  |  |  |  |  |  |  |  |  |

| 72    | RPD0/RD0                                              | 87    | AN44/C3INA/RPF0/PMD11/RF0 |  |  |  |  |  |  |  |  |  |  |  |

| 73    | SOSCI/RPC13/RC13                                      | 88    | AN45/RPF1/PMD10/RF1       |  |  |  |  |  |  |  |  |  |  |  |

| 74    | SOSCO/RPC14/T1CK/RC14                                 | 89    | RPG1/PMD9/RG1             |  |  |  |  |  |  |  |  |  |  |  |

| 75    | Vss                                                   | 90    | RPG0/PMD8/RG0             |  |  |  |  |  |  |  |  |  |  |  |

| 76    | AN24/RPD1/RD1                                         | 91    | RA6                       |  |  |  |  |  |  |  |  |  |  |  |

| 77    | AN25/RPD2/RD2                                         | 92    | CTED8/RA7                 |  |  |  |  |  |  |  |  |  |  |  |

|       | AN26/C3IND/RPD3/RD3                                   | 93    | AN46/PMD0/RE0             |  |  |  |  |  |  |  |  |  |  |  |

|       | AN40/RPD12/PMD12/RD12                                 | 94    | AN47/PMD1/RE1             |  |  |  |  |  |  |  |  |  |  |  |

|       | AN41/PMD13/RD13                                       | 95    | RG14                      |  |  |  |  |  |  |  |  |  |  |  |

| -     | RPD4/PMWR/RD4                                         | 96    | RG12                      |  |  |  |  |  |  |  |  |  |  |  |

| 02    | RPD5/PMRD/RD5                                         | 97    | RG13                      |  |  |  |  |  |  |  |  |  |  |  |

|       | AN42/C3INC/PMD14/RD6                                  | 98    | AN20/PMD2/RE2             |  |  |  |  |  |  |  |  |  |  |  |

|       | AN43/C3INB/PMD15/RD7                                  | 99    | RPE3/CTPLS/PMD3/RE3       |  |  |  |  |  |  |  |  |  |  |  |

| 85    | VCAP                                                  | 100   | AN21/PMD4/RE4             |  |  |  |  |  |  |  |  |  |  |  |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

#### TABLE 5: PIN NAMES FOR 100-PIN USB DEVICES

#### **100-PIN TQFP (TOP VIEW)**

PIC32MX230F128L PIC32MX530F128L PIC32MX250F256L PIC32MX550F256L PIC32MX270F512L PIC32MX570F512L

100

| Pin # | Full Pin Name                         | Div | n #  | Full Pin Name                   |

|-------|---------------------------------------|-----|------|---------------------------------|

|       |                                       |     |      |                                 |

| 1     | AN28/RG15                             |     | -    | /ss                             |

| 2     | VDD                                   | -   |      |                                 |

| 3     | AN22/RPE5/PMD5/RE5                    | 3   | .0   | ICK/CTED2/RA1                   |

| 4     | AN23/PMD6/RE6                         | 3   | -    | AN34/RPF13/SCK3/RF13            |

| 5     | AN27/PMD7/RE7                         | 4   | .0 A | AN35/RPF12/RF12                 |

| 6     | AN29/RPC1/RC1                         | 4   | -1 A | AN12/PMA11/RB12                 |

| 7     | AN30/RPC2/RC2                         | 4   | -2 A | AN13/PMA10/RB13                 |

| 8     | AN31/RPC3/RC3                         | 4   | -3 A | AN14/RPB14/CTED5/PMA1/RB14      |

| 9     | RPC4/CTED7/RC4                        | 4   | 4 A  | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 10    | AN16/C1IND/RPG6/SCK2/PMA5/RG6         | 4   | ·5 \ | /ss                             |

| 11    | AN17/C1INC/RPG7/PMA4/RG7              | 4   | ·6 \ | /DD                             |

| 12    | AN18/C2IND/RPG8/PMA3/RG8              | 4   | ·7 A | AN36/RPD14/RD14                 |

| 13    | MCLR                                  | 4   | -8 A | AN37/RPD15/SCK4/RD15            |

| 14    | AN19/C2INC/RPG9/PMA2/RG9              | 4   | .9 F | RPF4/PMA9/RF4                   |

| 15    | Vss                                   | 5   | 60 F | RPF5/PMA8/RF5                   |

| 16    | Vdd                                   | 5   | i1 L | JSBID/RPF3/RF3                  |

| 17    | TMS/CTED1/RA0                         | 5   | 2 A  | AN38/RPF2/RF2                   |

| 18    | AN32/RPE8/RE8                         | 5   | 3 A  | AN39/RPF8/RF8                   |

| 19    | AN33/RPE9/RE9                         | 5   | i4 \ | /BUS                            |

| 20    | AN5/C1INA/RPB5/VBUSON/RB5             | 5   | 5 \  | /USB3V3                         |

| 21    | AN4/C1INB/RB4                         | 5   | 6 E  | )-                              |

| 22    | PGED3/AN3/C2INA/RPB3/RB3              | 5   | 7 E  | )+                              |

| 23    | PGEC3/AN2/CTCMP/C2INB/RPB2/CTED13/RB2 | 5   | 8 5  | SCL2/RA2                        |

| 24    | PGEC1/AN1/RPB1/CTED12/RB1             | 5   | 9 5  | SDA2/RA3                        |

| 25    | PGED1/AN0/RPB0/RB0                    | 6   | т 0  | IDI/CTED9/RA4                   |

| 26    | PGEC2/AN6/RPB6/RB6                    | 6   | i1 T | IDO/RA5                         |

| 27    | PGED2/AN7/RPB7/CTED3/RB7              | 6   | i2 \ | /DD                             |

| 28    | VREF-/PMA7/RA9                        | 6   | i3 ( | DSC1/CLKI/RC12                  |

| 29    | VREF+/PMA6/RA10                       | 6   | i4 ( | DSC2/CLKO/RC15                  |

| 30    | AVdd                                  | 6   | i5 Ν | /ss                             |

| 31    | AVss                                  | 6   | 6 F  | RPA14/SCL1/RA14                 |

| 32    | AN8/RPB8/CTED10/RB8                   | 6   | 57 F | RPA15/SDA1/RA15                 |

| 33    | AN9/RPB9/CTED4/RB9                    | 6   | i8 F | RPD8/RTCC/RD8                   |

| 34    | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 6   | ;9 F | RPD9/RD9                        |

| 35    | AN11/PMA12/RB11                       | 7   | '0 F | RPD10/SCK1/PMA15/RD10           |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

#### TABLE 5-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

|                                     |       | Vector |               | Persistent   |             |              |           |

|-------------------------------------|-------|--------|---------------|--------------|-------------|--------------|-----------|

| Interrupt Source <sup>(1)</sup>     | IRQ # | #      | Flag          | Enable       | Priority    | Sub-priority | Interrupt |

|                                     | 1     | Highe  | st Natural Or | der Priority | l.          | 1            |           |

| CT – Core Timer Interrupt           | 0     | 0      | IFS0<0>       | IEC0<0>      | IPC0<4:2>   | IPC0<1:0>    | No        |

| CS0 – Core Software Interrupt 0     | 1     | 1      | IFS0<1>       | IEC0<1>      | IPC0<12:10> | IPC0<9:8>    | No        |

| CS1 – Core Software Interrupt 1     | 2     | 2      | IFS0<2>       | IEC0<2>      | IPC0<20:18> | IPC0<17:16>  | No        |

| INT0 – External Interrupt           | 3     | 3      | IFS0<3>       | IEC0<3>      | IPC0<28:26> | IPC0<25:24>  | No        |

| T1 – Timer1                         | 4     | 4      | IFS0<4>       | IEC0<4>      | IPC1<4:2>   | IPC1<1:0>    | No        |

| IC1E – Input Capture 1 Error        | 5     | 5      | IFS0<5>       | IEC0<5>      | IPC1<12:10> | IPC1<9:8>    | Yes       |

| IC1 – Input Capture 1               | 6     | 5      | IFS0<6>       | IEC0<6>      | IPC1<12:10> | IPC1<9:8>    | Yes       |

| OC1 – Output Compare 1              | 7     | 6      | IFS0<7>       | IEC0<7>      | IPC1<20:18> | IPC1<17:16>  | No        |

| INT1 – External Interrupt 1         | 8     | 7      | IFS0<8>       | IEC0<8>      | IPC1<28:26> | IPC1<25:24>  | No        |

| T2 – Timer2                         | 9     | 8      | IFS0<9>       | IEC0<9>      | IPC2<4:2>   | IPC2<1:0>    | No        |

| IC2E – Input Capture 2              | 10    | 9      | IFS0<10>      | IEC0<10>     | IPC2<12:10> | IPC2<9:8>    | Yes       |

| IC2 – Input Capture 2               | 11    | 9      | IFS0<11>      | IEC0<11>     | IPC2<12:10> | IPC2<9:8>    | Yes       |

| OC2 – Output Compare 2              | 12    | 10     | IFS0<12>      | IEC0<12>     | IPC2<20:18> | IPC2<17:16>  | No        |

| INT2 – External Interrupt 2         | 13    | 11     | IFS0<13>      | IEC0<13>     | IPC2<28:26> | IPC2<25:24>  | No        |

| T3 – Timer3                         | 14    | 12     | IFS0<14>      | IEC0<14>     | IPC3<4:2>   | IPC3<1:0>    | No        |

| IC3E – Input Capture 3              | 15    | 13     | IFS0<15>      | IEC0<15>     | IPC3<12:10> | IPC3<9:8>    | Yes       |

| IC3 – Input Capture 3               | 16    | 13     | IFS0<16>      | IEC0<16>     | IPC3<12:10> | IPC3<9:8>    | Yes       |

| OC3 – Output Compare 3              | 17    | 14     | IFS0<17>      | IEC0<17>     | IPC3<20:18> | IPC3<17:16>  | No        |

| INT3 – External Interrupt 3         | 18    | 15     | IFS0<18>      | IEC0<18>     | IPC3<28:26> | IPC3<25:24>  | No        |

| T4 – Timer4                         | 19    | 16     | IFS0<19>      | IEC0<19>     | IPC4<4:2>   | IPC4<1:0>    | No        |

| IC4E – Input Capture 4 Error        | 20    | 17     | IFS0<20>      | IEC0<20>     | IPC4<12:10> | IPC4<9:8>    | Yes       |

| IC4 – Input Capture 4               | 21    | 17     | IFS0<21>      | IEC0<21>     | IPC4<12:10> | IPC4<9:8>    | Yes       |

| OC4 – Output Compare 4              | 22    | 18     | IFS0<22>      | IEC0<22>     | IPC4<20:18> | IPC4<17:16>  | No        |

| INT4 – External Interrupt 4         | 23    | 19     | IFS0<23>      | IEC0<23>     | IPC4<28:26> | IPC4<25:24>  | No        |

| T5 – Timer5                         | 24    | 20     | IFS0<24>      | IEC0<24>     | IPC5<4:2>   | IPC5<1:0>    | No        |

| IC5E – Input Capture 5 Error        | 25    | 21     | IFS0<25>      | IEC0<25>     | IPC5<12:10> | IPC5<9:8>    | Yes       |

| IC5 – Input Capture 5               | 26    | 21     | IFS0<26>      | IEC0<26>     | IPC5<12:10> | IPC5<9:8>    | Yes       |

| OC5 – Output Compare 5              | 27    | 22     | IFS0<27>      | IEC0<27>     | IPC5<20:18> | IPC5<17:16>  | No        |

| AD1 – ADC1 Convert done             | 28    | 23     | IFS0<28>      | IEC0<28>     | IPC5<28:26> | IPC5<25:24>  | Yes       |

| FSCM – Fail-Safe Clock Monitor      | 29    | 24     | IFS0<29>      | IEC0<29>     | IPC6<4:2>   | IPC6<1:0>    | No        |

| RTCC – Real-Time Clock and Calendar | 30    | 25     | IFS0<30>      | IEC0<30>     | IPC6<12:10> | IPC6<9:8>    | No        |

| FCE – Flash Control Event           | 31    | 26     | IFS0<31>      | IEC0<31>     | IPC6<20:18> | IPC6<17:16>  | No        |

| CMP1 – Comparator Interrupt         | 32    | 27     | IFS1<0>       | IEC1<0>      | IPC6<28:26> | IPC6<25:24>  | No        |

| CMP2 – Comparator Interrupt         | 33    | 28     | IFS1<1>       | IEC1<1>      | IPC7<4:2>   | IPC7<1:0>    | No        |

| USB – USB Interrupts                | 34    | 29     | IFS1<2>       | IEC1<2>      | IPC7<12:10> | IPC7<9:8>    | Yes       |

| SPI1E – SPI1 Fault                  | 35    | 30     | IFS1<3>       | IEC1<3>      | IPC7<20:18> | IPC7<17:16>  | Yes       |

| SPI1RX – SPI1 Receive Done          | 36    | 30     | IFS1<4>       | IEC1<4>      | IPC7<20:18> | IPC7<17:16>  | Yes       |

| SPI1TX – SPI1 Transfer Done         | 37    | 30     | IFS1<5>       | IEC1<5>      | IPC7<20:18> | IPC7<17:16>  | Yes       |

| U1E – UART1 Fault                   | 38    | 31     | IFS1<6>       | IEC1<6>      | IPC7<28:26> | IPC7<25:24>  | Yes       |

| U1RX – UART1 Receive Done           | 39    | 31     | IFS1<7>       | IEC1<7>      | IPC7<28:26> | IPC7<25:24>  | Yes       |

| U1TX – UART1 Transfer Done          | 40    | 31     | IFS1<8>       | IEC1<8>      | IPC7<28:26> | IPC7<25:24>  | Yes       |

| I2C1B – I2C1 Bus Collision Event    | 41    | 32     | IFS1<9>       | IEC1<9>      | IPC8<4:2>   | IPC8<1:0>    | Yes       |

| I2C1S – I2C1 Slave Event            | 42    | 32     | IFS1<10>      | IEC1<10>     | IPC8<4:2>   | IPC8<1:0>    | Yes       |

| 2C1M – I2C1 Master Event            | 43    | 32     | IFS1<11>      | IEC1<11>     | IPC8<4:2>   | IPC8<1:0>    | Yes       |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX/2XX/5XX 64/100-pin Controller Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | _                 | _                 | -                 | _                | —                    |

| 00.40        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | —                 | _                 | _                 | —                 | _                 |                   |                  | _                    |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 10.0         | —                 | _                 |                   | —                 | _                 |                   | —                | _                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | SWRST <sup>(1)</sup> |

#### REGISTER 7-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | HC = Cleared by hardware |                      |                    |  |  |  |  |  |  |  |

|-------------------|--------------------------|----------------------|--------------------|--|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bi | t, read as '0'     |  |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup>

- 1 = Enable software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section

6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bit  | s    |      |          |        |        |         |        | (0         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     |       | —     | _     | _     | —    | _    |      | _    | —    | —        | -      | -      | —       |        | 0000       |

| 5390                        | UIEF9                           | 15:0      |       |       |       | _     | _     | _     | —    | _    | -    |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | _     |       | _     |       |       | _    |      | _    |      | _    | —        | -      |        | —       |        | 0000       |

| 53A0 l                      | UIEFIU                          | 15:0      | Ι     | Ι     |       | _     | -     | -     | _    | _    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     | _     | _     | _     |       | _     | _     | —    | _    | _    | _    | —    | —        | _      | _      | —       | _      | 0000       |

| 53BU                        |                                 | 15:0      | _     | _     | _     |       | _     | _     | —    | _    | _    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     | _     | _     | _     |       | _     | _     | —    | _    | _    | _    | —    | —        | _      | _      | —       | _      | 0000       |

| 5500                        | UIEF12                          | 15:0      | Ι     | _     | —     | _     | —     | —     | _    | —    | —    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     | Ι     | _     | —     | _     | —     | —     | _    | —    | —    | _    | _    | —        | —      | —      | —       | —      | 0000       |

| 55D0                        | UIEF 13                         | 15:0      | Ι     | _     | —     | _     | —     | —     | _    | —    | —    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     |       |       | _     | _     | _    | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    |      |      | _    | _    |          | -      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    |      |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

|              | Bit |                       |     |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

|--------------|-----------------------------------------|-----------------------|-----|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                       | 31/23/15/7 30/22/14/6 |     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

| 31:24        | U-0                                     | U-0                   | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |

| 31.24        | _                                       | —                     | _   | —                 | _                 | _                 | _                | -                |  |  |  |  |  |  |  |

| 23:16        | U-0 U-0                                 |                       | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |

| 23.10        |                                         | _                     |     | _                 | _                 | -                 | -                | -                |  |  |  |  |  |  |  |

| 15:8         | U-0                                     | U-0                   | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |

| 15.0         |                                         | _                     |     | _                 | _                 | -                 | -                | -                |  |  |  |  |  |  |  |

| 7:0          | R/W-0                                   | R/W-0                 | U-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7.0          | LSPD                                    | RETRYDIS              | _   | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |  |  |  |  |  |  |  |

#### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| 9                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device enabled

- 0 = Direct connection to a low-speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

#### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive enabled

- 0 = Endpoint n receive disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit enabled

- 0 = Endpoint n transmit disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake enabled

- 0 = Endpoint Handshake disabled (typically used for isochronous endpoints)

#### 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

#### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 11.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

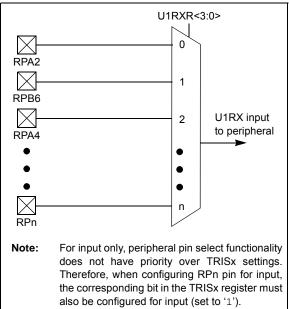

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

### FIGURE 11-2: REI

REMAPPABLE INPUT EXAMPLE FOR U1RX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | _                 | —                 | _                 | _                 |                   |                  | _                |  |  |  |  |

| 00.40        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | —                 |                   | _                 | _                 | —                 | -                | —                |  |  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | ON                | —                 | SIDL              | _                 | _                 | —                 | _                | —                |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          | _                 | _                 | _                 |                   |                   |                   | _                | _                |  |  |  |  |

#### **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A – G)

#### Legend:

| · J · · ·         |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = CPU Idle Mode halts CN operation

- 0 = CPU Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

#### 15.1 Control Registers

#### TABLE 15-1: INPUT CAPTURE 1 THROUGH INPUT CAPTURE 5 REGISTER MAP

| ess                         |                       | â             |                                                        |              |       |       |       |       |       | Bi     | s      |      |              |      |       |      |          |      |            |

|-----------------------------|-----------------------|---------------|--------------------------------------------------------|--------------|-------|-------|-------|-------|-------|--------|--------|------|--------------|------|-------|------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15                                                  | 30/14        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8   | 23/7   | 22/6 | 21/5         | 20/4 | 19/3  | 18/2 | 17/1     | 16/0 | All Resets |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         |                                                        | —            | _     | —     | —     | _     |       |        |        | -    | _            | —    |       |      | _        |      | 0000       |

| 2000                        | 1010011               | 15:0          | ON                                                     | —            | SIDL  | —     | —     | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0>         | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2010                        | IC1BUF                | 31:16         |                                                        |              |       |       |       |       |       | IC1BUF | <31:0> |      |              |      |       |      |          |      | xxxx       |

|                             |                       | 15:0          |                                                        |              |       |       |       |       |       |        |        |      |              | -    |       |      |          |      | xxxx       |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         | —                                                      |              | _     | —     | —     |       | —     |        | _      | —    | —            | —    |       |      | —        | —    | 0000       |

|                             |                       | 15:0          | ON - SIDL FEDGE C32 ICTMR ICI<1:0> ICOV ICBNE ICM<2:0> |              |       |       |       |       |       |        |        | 0000 |              |      |       |      |          |      |            |

| 2210                        | IC2BUF                | 31:16<br>15:0 |                                                        | IC2BUF<31:0> |       |       |       |       |       |        |        |      | xxxx<br>xxxx |      |       |      |          |      |            |

|                             | (1)                   | 31:16         | _                                                      |              | _     |       |       | _     |       | _      | _      | _    | _            | _    | _     | _    | _        | _    | 0000       |

| 2400                        | IC3CON <sup>(1)</sup> | 15:0          | ON                                                     | _            | SIDL  | _     | _     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0>         | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

|                             |                       | 31:16         |                                                        |              |       |       |       |       | 1 1   |        |        |      |              |      |       |      |          |      | xxxx       |

| 2410                        | IC3BUF                | 15:0          |                                                        |              |       |       |       |       |       | IC3BUF | <31:0> |      |              |      |       |      |          |      | xxxx       |

| 0000                        | 104001(1)             | 31:16         | —                                                      | —            | —     | —     | —     | —     | —     | _      | —      | —    | —            | _    | —     | —    | _        | —    | 0000       |

| 2600                        | IC4CON <sup>(1)</sup> | 15:0          | ON                                                     | _            | SIDL  | _     |       |       | FEDGE | C32    | ICTMR  | ICI< | 1:0>         | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 0040                        |                       | 31:16         |                                                        |              |       |       |       |       |       |        | 101.05 |      |              | •    |       |      |          |      | xxxx       |

| 2610                        | IC4BUF IC4BUF<31:0>   |               |                                                        |              |       |       |       |       |       |        | xxxx   |      |              |      |       |      |          |      |            |

| 2000                        |                       | 31:16         | _                                                      | _            | _     | _     | _     | _     | —     | _      | —      | —    | _            | _    | _     | _    | —        | _    | 0000       |

| 2000                        | IC5CON <sup>(1)</sup> | 15:0          | ON                                                     | —            | SIDL  | —     | —     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0>         | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2810                        | IC5BUF                | 31:16         |                                                        |              |       |       |       |       |       | IC5BUF | <31.0> |      |              |      |       |      |          |      | xxxx       |

| 2010                        | ICODOF                | 15:0          |                                                        |              |       |       |       |       |       | IC3B0F | -01.02 |      |              |      |       |      |          |      | xxxx       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Registers" for more information.

#### **Control Registers** 17.1

#### TABLE 17-1: SPI1 THROUGH SPI4 REGISTER MAP

| ess                         |                                 | <i>a</i>      |                                                                                       | Bits       |        |              |              |              |           |        |         |        |        |          |             |          |        |         |            |

|-----------------------------|---------------------------------|---------------|---------------------------------------------------------------------------------------|------------|--------|--------------|--------------|--------------|-----------|--------|---------|--------|--------|----------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                                                                                 | 30/14      | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6   | 21/5   | 20/4     | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16         | FRMEN                                                                                 | FRMSYNC    | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —      | —      |          |             |          | SPIFE  | ENHBUF  | 0000       |

| 5000                        | SITICON                         | 15:0          | ON - SIDL DISSDO MODE32 MODE16 SMP CKE SSEN CKP MSTEN DISSDI STXISEL<1:0> SRXISEL<1:0 |            |        |              |              |              |           |        | EL<1:0> | 0000   |        |          |             |          |        |         |            |

| 5810                        | SPI1STAT                        | 31:16         | <u> RXBUFELM&lt;4:0&gt; TXBUFELM&lt;4:0&gt;</u>                                       |            |        |              |              |              |           |        | 0000    |        |        |          |             |          |        |         |            |

| 3010                        | 011101/1                        | 15:0          |                                                                                       | —          | —      | FRMERR       | SPIBUSY      |              | —         | SPITUR | SRMT    | SPIROV | SPIRBE | —        | SPITBE      |          | SPITBF | SPIRBF  | 19EB       |

| 5820                        | SPI1BUF                         | 31:16<br>15:0 |                                                                                       | DATA<31:0> |        |              |              |              |           |        |         | 0000   |        |          |             |          |        |         |            |

| 5830                        | SPI1BRG                         | 31:16         | _                                                                                     | _          | —      | —            | —            | —            | —         | —      | —       | —      | —      | —        | —           | _        | —      | _       | 0000       |

| 5630                        | SFIIDKG                         | 15:0          |                                                                                       | -          | _      | _            | —            | _            | -         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         |                                                                                       | —          | —      |              | —            |              |           |        | _       | _      | _      |          |             |          | _      | _       | 0000       |

| 5840                        | SPI1CON2                        | 15:0          | SPI<br>SGNEXT                                                                         | —          | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —      | _      | _        | AUD<br>MONO | -        | AUDMO  | )D<1:0> | 0000       |

| 5A00                        | SPI2CON                         | 31:16         | FRMEN                                                                                 | FRMSYNC    | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:0 | )>     | MCLKSEL | _      | _      |          |             |          | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | 0112001                         | 15:0          | ON                                                                                    | —          | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5A10                        | SPI2STAT                        | 31:16         |                                                                                       | —          | —      |              |              | UFELM<4:     | 0>        |        | —       | —      | —      |          | TX          | BUFELM<4 |        | -       | 0000       |

| 5410                        | 01 120 17 11                    | 15:0          | _                                                                                     | —          | —      | FRMERR       | SPIBUSY      | —            | —         | SPITUR | SRMT    | SPIROV | SPIRBE | _        | SPITBE      | —        | SPITBF | SPIRBF  | 19EB       |

| 5A20                        | SPI2BUF                         | 31:16<br>15:0 |                                                                                       |            |        |              |              |              |           | DATA<  | 31:0>   |        |        |          |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16         |                                                                                       | —          | —      |              | —            |              |           |        | _       | _      | _      |          |             |          | _      | _       | 0000       |

| 5A30                        |                                 | 15:0          | -                                                                                     | —          | —      | -            | —            | —            | _         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         |                                                                                       | —          | —      |              | —            |              |           |        | _       | _      | _      |          |             |          | _      | _       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0          | SPI<br>SGNEXT                                                                         | —          | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —      | _      | _        | AUD<br>MONO | -        | AUDMO  | )D<1:0> | 0000       |

| 5000                        | SPI3CON                         | 31:16         | FRMEN                                                                                 | FRMSYNC    | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:( | )>     | MCLKSEL | —      | _      |          |             |          | SPIFE  | ENHBUF  | 0000       |

| 5C00                        | SPISCON                         | 15:0          | ON                                                                                    | —          | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5010                        | SPI3STAT                        | 31:16         |                                                                                       | -          | _      |              | RXB          | UFELM<4:     | 0>        |        | —       | _      | —      |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| 5C10                        | 3F 133 IAI                      | 15:0          | -                                                                                     | —          | —      | FRMERR       | SPIBUSY      |              | -         | SPITUR | SRMT    | SPIROV | SPIRBE | -        | SPITBE      |          | SPITBF | SPIRBF  | 19EB       |

| 5C20                        | SPI3BUF                         | 31:16<br>15:0 |                                                                                       |            |        |              |              |              |           | DATA<  | 31:0>   |        |        |          |             |          |        |         | 0000       |

|                             |                                 | 31:16         | _                                                                                     | —          | —      | _            | —            | —            | —         | —      | —       | —      | —      | —        | —           | _        | —      | _       | 0000       |

| 5C30                        | SPI3BRG                         | 15:0          | _                                                                                     | _          | —      | _            | _            | _            | _         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

| Legen                       |                                 |               |                                                                                       |            |        |              |              |              |           |        |         |        |        |          |             |          |        |         |            |

All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET, and INV Note 1: Registers" for more information.

2: This register is only available on 100-pin devices.

| REGISTE | ER 18-1: I2CxCON: I <sup>2</sup> C 'x' CONTROL REGISTER (CONTINUED)('x' = 1 AND 2)                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | GCEN: General Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                                             |

|         | <ul> <li>1 = Enable interrupt when a general call address is received in the I2CxRSR<br/>(module is enabled for reception)</li> <li>0 = General call address disabled</li> </ul>                                     |

| bit 6   | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                               |

|         | Used in conjunction with SCLREL bit.<br>1 = Enable software or receive clock stretching<br>0 = Disable software or receive clock stretching                                                                          |

| bit 5   | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                     |

|         | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                |

| bit 4   | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                                                               |

|         | (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                        |

|         | <ul> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br/>Hardware clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3   | <b>RCEN:</b> Receive Enable bit (when operating as $I^2C$ master)                                                                                                                                                    |

|         | 1 = Enables Receive mode for $I^2C$ . Hardware clear at end of eighth bit of master receive data byte.<br>0 = Receive sequence not in progress                                                                       |

| bit 2   | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                    |

|         | <ul><li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.</li><li>0 = Stop condition not in progress</li></ul>                                                       |

| bit 1   | RSEN: Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                |

|         | <ul> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of<br/>master Repeated Start sequence.</li> </ul>                                                                        |

|         | 0 = Repeated Start condition not in progress                                                                                                                                                                         |

| bit 0   | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                          |

|         | <ul> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.</li> <li>0 = Start condition not in progress</li> </ul>                                                 |

|         |                                                                                                                                                                                                                      |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| GISTER 20-3. FINIRADDR. FARALLEL FORTI READ ADDRESS REGISTER |                                                                                   |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>31/23/15/7                                            | Bit<br>30/22/14/6                                                                 | Bit<br>29/21/13/5                                                                                                                                                                                                                                             | Bit<br>28/20/12/4                                                                                                                                                                                                                                                                                                                   | Bit<br>27/19/11/3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit<br>26/18/10/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| U-0                                                          | U-0                                                                               | U-0                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                              | _                                                                                 |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| U-0                                                          | U-0                                                                               | U-0                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |