#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | ·                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 12x14b; D/A 4x9b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c29466-24sxit |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article "How to Design with PSoC<sup>®</sup> 1, PowerPSoC<sup>®</sup>, and PLC – KBA88292". Following is an abbreviated list for PSoC 1:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP

- In addition, PSoC Designer includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 1 are:

- □ Getting Started with PSoC<sup>®</sup> 1 AN75320

- □ PSoC<sup>®</sup> 1 Getting Started with GPIO AN2094

- □ PSoC<sup>®</sup> 1 Analog Structure and Configuration AN74170

- □ PSoC<sup>®</sup> 1 Switched Capacitor Analog Blocks AN2041

- Selecting Analog Ground and Reference AN2219

**Note:** For CY8C29X66 devices related Application note please click here.

- Development Kits:

- CY3210-PSoCEval1 supports all PSoC 1 Mixed-Signal Array families, including automotive, except CY8C25/26xxx devices. The kit includes an LCD module, potentiometer, LEDs, and breadboarding space.

- CY3214-PSoCEvalUSB features a development board for the CY8C24x94 PSoC device. Special features of the board include USB and CapSense development and debugging support.

**Note:** For CY8C29X66 devices related Development Kits please click here.

The MiniProg1 and MiniProg3 devices provide interfaces for flash programming and debug.

# **PSoC Designer**

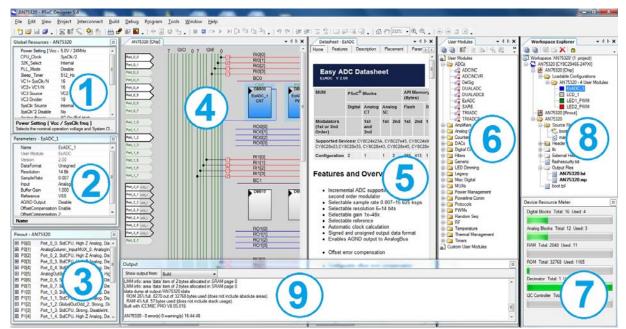

PSoC Designer is a free Windows-based Integrated Design Environment (IDE). Develop your applications using a library of pre-characterized analog and digital peripherals in a drag-and-drop design environment. Then, customize your design leveraging the dynamically generated API libraries of code. Figure 1 shows PSoC Designer windows. **Note:** This is not the default view.

- 1. Global Resources all device hardware settings.

- 2. **Parameters** the parameters of the currently selected User Modules.

- 3. Pinout information related to device pins.

- 4. **Chip-Level Editor** a diagram of the resources available on the selected chip.

- 5. Datasheet the datasheet for the currently selected UM

- 6. User Modules all available User Modules for the selected device.

- 7. **Device Resource Meter** device resource usage for the current project configuration.

- 8. Workspace a tree level diagram of files associated with the project.

- 9. Output output from project build and debug operations.

**Note:** For detailed information on PSoC Designer, go to PSoC<sup>®</sup> Designer > Help > Documentation > Designer Specific Documents > IDE User Guide.

## Figure 1. PSoC Designer Layout

Digital peripheral configurations include:

- PWMs (8- and 16-bit)

- PWMs with dead band (8- and 16-bit)

- Counters (8- to 32-bit)

- Timers (8- to 32-bit)

- UART 8-bit with selectable parity (up to 2)

- SPI slave and master (up to 2)

- I<sup>2</sup>C slave and multi-master (one available as a system resource)

- CRC generator (8- to 32-bit)

- IrDA (up to 2)

- PRS generators (8- to 32-bit)

The digital blocks can be connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also allow for signal multiplexing and for performing logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

Digital blocks are provided in rows of four, where the number of blocks varies by PSoC device family. This allows you the optimum choice of system resources for your application. Family resources are shown in the table titled "PSoC Device Characteristics" on page 6.

# Analog System

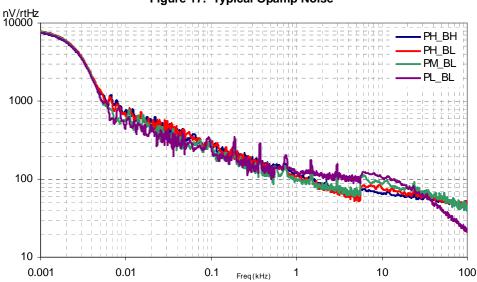

The analog system is composed of 12 configurable blocks, each containing an opamp circuit that allows the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are:

- ADCs (up to 4, with 6- to 14-bit resolution; selectable as incremental, delta sigma, and SAR)

- Filters (2-, 4-, 6-, and 8-pole band pass, low pass, and notch)

- Amplifiers (up to 4, with selectable gain to 48x)

- Instrumentation amplifiers (up to 2, with selectable gain to 93x)

- Comparators (up to 4, with 16 selectable thresholds)

- DACs (up to 4, with 6-bit to 9-bit resolution)

- Multiplying DACs (up to 4, with 6-bit to 9-bit resolution)

- High current output drivers (four with 30-mA drive as a core resource)

- 1.3-V reference (as a system resource)

- DTMF Dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

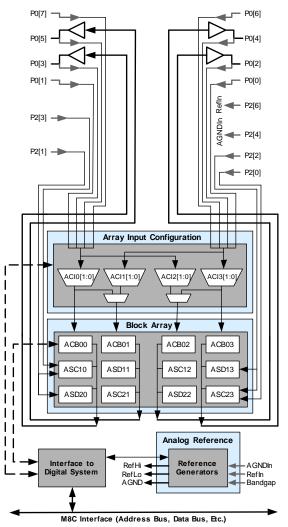

Analog blocks are provided in columns of three, which includes one continuous time (CT) and two switched capacitor (SC) blocks, as shown in Figure 3.

## Figure 3. Analog System Block Diagram

## Organize and Connect

You build signal chains at the chip level by interconnecting user modules to each other and the I/O pins. You perform the selection, configuration, and routing so that you have complete control over all on-chip resources.

#### Generate, Verify, and Debug

When you are ready to test the hardware configuration or move on to developing code for the project, you perform the "Generate Configuration Files" step. This causes PSoC Designer to generate source code that automatically configures the device to your specification and provides the software for the system. The generated code provides application programming interfaces (APIs) with high-level functions to control and respond to hardware events at run time and interrupt service routines that you can adapt as needed. A complete code development environment allows you to develop and customize your applications in either C, assembly language, or both.

The last step in the development process takes place inside PSoC Designer's debugger (access by clicking the Connect icon). PSoC Designer downloads the HEX image to the ICE where it runs at full speed. PSoC Designer debugging capabilities rival those of systems costing many times more. In addition to traditional single-step, run-to-breakpoint and watch-variable features, the debug interface provides a large trace buffer and allows you to define complex breakpoint events that include monitoring address and data bus values, memory locations and external signals.

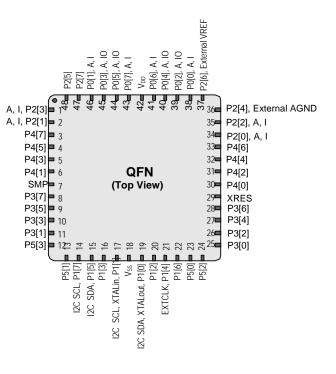

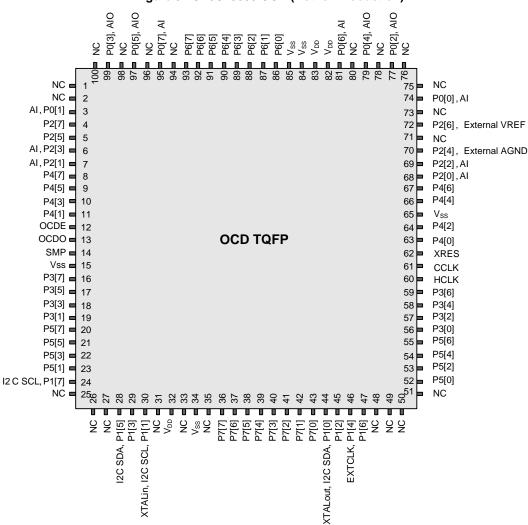

## Table 5. 48-Pin Part Pinout (QFN) <sup>[9]</sup>

| No.         Digital         Analog         Name         Description           1         I/O         I         P2[3]         Direct switched capacitor block input           2         I/O         I         P2[1]         Direct switched capacitor block input           3         I/O         P4[7]         Direct switched capacitor block input           3         I/O         P4[1]         Direct switched capacitor block input           5         I/O         P4[3]         External components required           6         I/O         P4[1]         Switch mode pump (SMP) connection to external components required           8         I/O         P3[7]         Power         SMP           9         I/O         P3[5]         Image: State Sta |           |     |     |             |                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|-------------|------------------------------------------------------------------|

| Disk         Product           1         I/O         I         P2[1]         Direct switched capacitor block input           3         I/O         P4[7]         Direct switched capacitor block input           3         I/O         P4[7]         Patent           4         I/O         P4[7]         Patent           5         I/O         P4[7]         Patent           6         I/O         P4[7]         Patent           7         Power         SMP         Switch mode pump (SMP) connection to external components required           8         I/O         P3[7]         Patent         Patent           9         I/O         P3[3]         Patent         Patent           10         I/O         P3[1]         Patent         Patent           12         I/O         P5[3]         Patent         Patent           13         I/O         P1[7]         I <sup>2</sup> C SCL         Patent           14         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>18</sup> 15         I/O         P1[1]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]         Optional EXTCLK           21                                                                                                                                                                                                                                                                                                                                                                                              | Pin<br>No | -   | -   | Pin<br>Name | Description                                                      |

| 2         I/O         I         P2[1]         Direct switched capacitor block input           3         I/O         P4[7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |     | -   |             | Direct switched consoiter block input                            |

| 3         I/O         P4[7]           4         I/O         P4[5]           5         I/O         P4[3]           6         I/O         P4[1]           7         Power         SMP           8         I/O         P3[7]           9         I/O         P3[5]           10         I/O         P3[3]           11         I/O         P3[3]           12         I/O         P5[3]           13         I/O         P5[1]           14         I/O         P1[7]           15         I/O         P1[8]           16         I/O         P1[1]           17         I/O         P1[1]           18         Power         V <sub>SS</sub> 18         Power         V <sub>SS</sub> 19         I/O         P1[6]           23 <tdi o<="" td="">         P5[0]           24         I/O         P1[6]           23         I/O         P5[0]           24         I/O         P3[4]           28         I/O         P3[4]           29         Input         XRES           XRES         Active high</tdi>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |     |     |             |                                                                  |

| 4         I/O         P4[5]           5         I/O         P4[3]           6         I/O         P4[1]           7         Power         SW         Switch mode pump (SMP) connection to external components required           8         I/O         P3[7]         9           9         I/O         P3[3]         11           10         I/O         P3[3]         11           12         I/O         P3[1]         11           12         I/O         P3[1]         11           12         I/O         P3[1]         11           14         I/O         P1[7]         I <sup>2</sup> C SCL           15         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>I8</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALun), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[4]         Optional EXTCLK           21         I/O         P1[4]         Optional EXTCLK           22         I/O         P3[0]         24           23         I/O         P3[2]         25           24         I/O         P3[6] </td <td></td> <td></td> <td>1</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                 |           |     | 1   |             |                                                                  |

| 5         I/O         P4[3]           6         I/O         P4[1]           7         Power         SMP         Switch mode pump (SMP) connection to external components required           8         I/O         P3[7]         Power         SMP           9         I/O         P3[5]         10         I/O           10         I/O         P3[3]         11         I/O           11         I/O         P3[1]         12         I/O         P5[3]           13         I/O         P5[1]         14         I/O         P1[7]         I <sup>2</sup> C SCL           15         I/O         P1[5]         I <sup>2</sup> C SDA         16         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>I8</sup> 18         Power         V <sub>SS</sub> Ground connection         19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[1]         Optional EXTCLK         22         I/O         P1[4]         Optional EXTCLK           21         I/O         P1[4]         Optional EXTCLK         22         I/O         P3[0]         24         I/O         P5[2]         25         I/O         P3[0]         24         I/O                                                                                                                                                                                                                                                                                                                                                  |           |     |     |             |                                                                  |

| 6         I/O         P4[1]           7         Power         SMP         Switch mode pump (SMP) connection to external components required           8         I/O         P3[7]         9           9         I/O         P3[5]         10           10         I/O         P3[3]         11           11         I/O         P3[3]         11           12         I/O         P5[3]         11           14         I/O         P1[7]         I <sup>2</sup> C SCL           15         I/O         P1[5]         I <sup>2</sup> C SDA           16         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>I8</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[4]         Optional EXTCLK           21         I/O         P1[4]         Optional EXTCLK           22         I/O         P1[6]         23           23         I/O         P5[0]         24           24         I/O         P5[2]         25           25         I/O         P3[4]         23           <                                                                                                                                                                                                                                                                                                                                                                                                                        |           |     |     |             |                                                                  |

| 7         Power         SMP         Switch mode pump (SMP) connection to external components required           8         I/O         P3[7]         9         I/O         P3[6]           10         I/O         P3[3]         1         1           11         I/O         P3[1]         1         1           12         I/O         P5[3]         1         1           14         I/O         P1[7]         I <sup>2</sup> C SCL         1           15         I/O         P1[5]         I <sup>2</sup> C SDA         1           16         I/O         P1[3]         1         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>18</sup> 18         Power         V <sub>SS</sub> Ground connection         1           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[6]         2         1           21         I/O         P1[6]         2         1           22         I/O         P3[2]         2         2           23         I/O         P3[6]         2         2           24         I/O         P3[2]         2         2           25         I/O         P3[4                                                                                                                                                                                                                                                                                                                                                                                                                       |           |     |     |             |                                                                  |

| external components required           8         I/O         P3[7]           9         I/O         P3[5]           10         I/O         P3[3]           11         I/O         P3[1]           12         I/O         P5[3]           13         I/O         P5[1]           14         I/O         P1[5]         I <sup>2</sup> C SCL           15         I/O         P1[5]         I <sup>2</sup> C SDA           16         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[1]         Crystal (XTALut), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]            21         I/O         P1[4]         Optional EXTCLK           22         I/O         P1[6]            23         I/O         P5[2]            24         I/O         P3[4]            25         I/O         P3[6]            29         Input         XRES         Active high external reset with internal pull-down           30         I/O         P4[6] </td <td></td> <td></td> <td></td> <td></td> <td>Quitebarada auror (QMD) areas atian ta</td>                                                                                                                                                                                                                                                                                                                                                                                          |           |     |     |             | Quitebarada auror (QMD) areas atian ta                           |

| 8         I/O         P3[7]           9         I/O         P3[5]           10         I/O         P3[3]           11         I/O         P3[1]           12         I/O         P5[3]           13         I/O         P5[1]           14         I/O         P1[7]         I <sup>2</sup> C SCL           15         I/O         P1[5]         I <sup>2</sup> C SDA           16         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLKI <sup>8</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[2]         Crystal (XTALin), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[4]         Optional EXTCLK           22         I/O         P1[6]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           23         I/O         P5[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           24         I/O         P5[2]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           25         I/O         P3[6]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           26         I/O         P3[6]         Crystal (XTALout), I <sup>2</sup> C                                                                                                                                                                                                                                                                                    | ′         | PO  | wer | SIVIP       |                                                                  |

| 10         I/O         P3[3]           11         I/O         P3[1]           12         I/O         P5[3]           13         I/O         P5[1]           14         I/O         P1[7]         I <sup>2</sup> C SCL           15         I/O         P1[5]         I <sup>2</sup> C SDA           16         I/O         P1[3]         I/C           17         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]            21         I/O         P1[4]         Optional EXTCLK           22         I/O         P1[6]            23         I/O         P5[2]            24         I/O         P3[4]            25         I/O         P3[6]            29         Input         XRES         Active high external reset with internal pull-down           30         I/O         P4[6]            31         I/O         P4[6]       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8         | I/O |     | P3[7]       |                                                                  |

| 10         I/O         P3[3]           11         I/O         P3[1]           12         I/O         P5[3]           13         I/O         P5[1]           14         I/O         P1[7]         I <sup>2</sup> C SCL           15         I/O         P1[5]         I <sup>2</sup> C SDA           16         I/O         P1[3]         I/C           17         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]            21         I/O         P1[4]         Optional EXTCLK           22         I/O         P1[6]            23         I/O         P5[2]            24         I/O         P3[4]            25         I/O         P3[6]            29         Input         XRES         Active high external reset with internal pull-down           30         I/O         P4[6]            31         I/O         P4[6]       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9         | I/O |     | P3[5]       |                                                                  |

| 11         I/O         P3[1]           12         I/O         P5[3]           13         I/O         P5[1]           14         I/O         P1[7]         I <sup>2</sup> C SCL           15         I/O         P1[5]         I <sup>2</sup> C SDA           16         I/O         P1[3]         I/O           17         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]         P1[2]           21         I/O         P1[4]         Optional EXTCLK           22         I/O         P1[6]         P1[2]           23         I/O         P5[0]         P1[4]           24         I/O         P5[2]         P1[2]           25         I/O         P3[4]         P1[2]           28         I/O         P3[6]         P1[2]           29         Input         XRES         Active high external reset with internal pull-down           30         I/O         P4[4]         P1[2]         P1[2]           32                                                                                                                                                                                                                                                                                                                                                                                                                              | 10        | I/O |     | P3[3]       |                                                                  |

| 12       I/O       P5[3]         13       I/O       P5[1]         14       I/O       P1[7]       I <sup>2</sup> C SCL         15       I/O       P1[5]       I <sup>2</sup> C SDA         16       I/O       P1[3]       I/O         17       I/O       P1[1]       Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>18</sup> 18       Power       V <sub>SS</sub> Ground connection         19       I/O       P1[0]       Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT         20       I/O       P1[2]       I/O         21       I/O       P1[4]       Optional EXTCLK         22       I/O       P1[6]       I/O         23       I/O       P5[0]       I/O         24       I/O       P5[2]       I/O         25       I/O       P3[4]       I/O         26       I/O       P3[4]       I/O         28       I/O       P3[6]       I/O         29       Input       XRES       Active high external reset with internal pull-down         30       I/O       P4[0]       I/O       I/O         31       I/O       P4[2]       I/O       I/O         33       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11        | I/O |     |             |                                                                  |

| 13         I/O         P5[1]           14         I/O         P1[7]         I <sup>2</sup> C SCL           15         I/O         P1[5]         I <sup>2</sup> C SDA           16         I/O         P1[3]         I           17         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>I8</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]         I/O           21         I/O         P1[6]         II/O           23         I/O         P5[0]         II/O           24         I/O         P5[2]         II/O           25         I/O         P3[0]         II/O           26         I/O         P3[4]         III           28         I/O         P3[6]         III           30         I/O         P4[0]         III           31         I/O         P4[0]         III           33         I/O         P4[6]         III           34         I/O         I         P2[2]         Direct switched capacitor block input           35                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12        | I/O |     |             |                                                                  |

| 14       I/O       P1[7]       I <sup>2</sup> C SCL         15       I/O       P1[5]       I <sup>2</sup> C SDA         16       I/O       P1[3]         17       I/O       P1[1]       Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>I8</sup> 18       Power       V <sub>SS</sub> Ground connection         19       I/O       P1[0]       Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT         20       I/O       P1[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13        | I/O |     |             |                                                                  |

| 15         I/O         P1[5]         I <sup>2</sup> C SDA           16         I/O         P1[3]         I/O         P1[3]           17         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>I8</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]         I/O         P1[4]           21         I/O         P1[6]         I/O           22         I/O         P1[6]         I/O           23         I/O         P5[0]         I/O           24         I/O         P5[2]         I/O           25         I/O         P3[4]         I/O           26         I/O         P3[4]         I/O           28         I/O         P3[6]         I/O           29         Input         XRES         Active high external reset with internal pull-down           30         I/O         P4[0]         I/O           31         I/O         P4[2]         I/O           32         I/O         P4[6]         I/O           34         I/O         I         P2[2                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14        | I/O |     |             | I <sup>2</sup> C SCL                                             |

| 16         I/O         P1[3]           17         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>18</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |     |     |             |                                                                  |

| 17         I/O         P1[1]         Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>I8</sup> 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |     |     |             |                                                                  |

| 18         Power         V <sub>SS</sub> Ground connection           19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]           21         I/O         P1[4]         Optional EXTCLK           22         I/O         P1[6]         23           23         I/O         P5[0]         24           24         I/O         P5[2]         25           25         I/O         P3[0]         26           26         I/O         P3[4]         27           27         I/O         P3[6]         29           29         Input         XRES         Active high external reset with internal pull-down           30         I/O         P4[0]         21         22           31         I/O         P4[2]         22         23           33         I/O         P4[6]         23         24           34         I/O         I         P2[0]         Direct switched capacitor block input           35         I/O         I         P2[2]         Direct switched capacitor block input           35         I/O         I         P2[2]         Direct switched capacitor bl                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |     |     |             | Crystal (XTALin), I <sup>2</sup> C SCL, ISSP-SCLK <sup>[8]</sup> |

| 19         I/O         P1[0]         Crystal (XTALout), I <sup>2</sup> C SDA, ISSP-SDAT           20         I/O         P1[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |     | wer |             |                                                                  |

| 20         I/O         P1[2]           21         I/O         P1[4]         Optional EXTCLK           22         I/O         P1[6]            23         I/O         P5[0]            24         I/O         P5[2]            25         I/O         P3[0]            26         I/O         P3[2]            27         I/O         P3[4]            28         I/O         P3[6]            29         Input         XRES         Active high external reset with internal pull-down           30         I/O         P4[0]            31         I/O         P4[2]            32         I/O         P4[6]            33         I/O         P4[6]            34         I/O         I         P2[0]         Direct switched capacitor block input           35         I/O         I         P2[2]         Direct switched capacitor block input           36         I/O         P2[4]         External analog ground (AGND)           37         I/O         P2[6]         External voltage reference (VREF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -         |     |     |             |                                                                  |

| 21         I/O         P1[4]         Optional EXTCLK           22         I/O         P1[6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |     |     |             |                                                                  |

| 22         I/O         P1[6]           23         I/O         P5[0]           24         I/O         P5[2]           25         I/O         P3[0]           26         I/O         P3[2]           27         I/O         P3[4]           28         I/O         P3[6]           29         Input         XRES           Active high external reset with internal pull-down           30         I/O         P4[0]           31         I/O         P4[4]           33         I/O         P4[4]           33         I/O         P4[6]           34         I/O         I           7         I/O         P2[2]           Direct switched capacitor block input           35         I/O         I           7         I/O         P2[4]         External analog ground (AGND)           37         I/O         P2[6]         External voltage reference (VREF)           38         I/O         I         P0[0]         Analog column mux input           39         I/O         I/O         P0[4]         Analog column mux input and column ou           40         I/O         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |     |     |             | Optional EXTCLK                                                  |

| 23         I/O         P5[0]           24         I/O         P5[2]           25         I/O         P3[0]           26         I/O         P3[2]           27         I/O         P3[4]           28         I/O         P3[6]           29         Input         XRES           Active high external reset with internal pull-down           30         I/O         P4[0]           31         I/O         P4[2]           32         I/O         P4[4]           33         I/O         P4[6]           34         I/O         I           35         I/O         I           36         I/O         P2[4]           External analog ground (AGND)         37           37         I/O         P2[6]           8         I/O         I           99         I/O         P0[0]         Analog column mux input           39         I/O         I         P0[2]         Analog column mux input and column ou           40         I/O         I         P0[6]         Analog column mux input and column ou           41         I/O         I         P0[6]         Analog column                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |     |     |             |                                                                  |

| 24         I/O         P5[2]           25         I/O         P3[0]           26         I/O         P3[2]           27         I/O         P3[4]           28         I/O         P3[6]           29         Input         XRES           Active high external reset with internal pull-down           30         I/O         P4[0]           31         I/O         P4[2]           32         I/O         P4[4]           33         I/O         P4[6]           34         I/O         I           35         I/O         I           36         I/O         P2[2]           Direct switched capacitor block input           35         I/O         I           7         I/O         P2[4]           External analog ground (AGND)           37         I/O         P2[6]           8         I/O         I         P0[0]           38         I/O         I         P0[2]           39         I/O         I/O         P0[4]           39         I/O         I/O         P0[4]           41         I/O         I         P0[6] <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |     |     |             |                                                                  |

| 25         I/O         P3[0]           26         I/O         P3[2]           27         I/O         P3[4]           28         I/O         P3[6]           29         Input         XRES           Active high external reset with internal pull-down           30         I/O         P4[0]           31         I/O         P4[2]           32         I/O         P4[6]           33         I/O         P4[6]           34         I/O         I           35         I/O         I           36         I/O         P2[4]           26         I/O         P4[6]           34         I/O         I           7         I/O         P2[2]         Direct switched capacitor block input           36         I/O         I         P2[2]         Direct switched capacitor block input           36         I/O         P2[6]         External analog ground (AGND)           37         I/O         P2[6]         External voltage reference (VREF)           38         I/O         I         P0[0]         Analog column mux input           39         I/O         I/O         P0[4] <td< td=""><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |     |     |             |                                                                  |

| 26         I/O         P3[2]           27         I/O         P3[4]           28         I/O         P3[6]           29         Input         XRES           30         I/O         P4[0]           31         I/O         P4[2]           32         I/O         P4[4]           33         I/O         P4[6]           34         I/O         I           35         I/O         I           36         I/O         P2[2]           Direct switched capacitor block input           35         I/O         I           36         I/O         P2[4]           External voltage reference (VREF)           38         I/O         I           39         I/O         I           39         I/O         I           39         I/O         I           40         I/O         P0[6]           Analog column mux input and column ou           41         I/O         I           42         Power         V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |     |     |             |                                                                  |

| 27         I/O         P3[4]           28         I/O         P3[6]           29         Input         XRES         Active high external reset with internal pull-down           30         I/O         P4[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |     |     |             |                                                                  |

| 28         I/O         P3[6]           29         Input         XRES         Active high external reset with internal pull-down           30         I/O         P4[0]         pull-down           31         I/O         P4[2]         pull-down           32         I/O         P4[2]         pull-down           33         I/O         P4[6]         pull-down           34         I/O         P4[6]         pull-down           35         I/O         P4[6]         pull-down           36         I/O         P4[6]         pull-down           36         I/O         P2[2]         Direct switched capacitor block input           36         I/O         P2[4]         External analog ground (AGND)           37         I/O         P2[6]         External voltage reference (VREF)           38         I/O         I         P0[0]         Analog column mux input           39         I/O         I/O         P0[2]         Analog column mux input and column ou           40         I/O         I         P0[6]         Analog column mux input           42         Power         V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -         |     |     |             |                                                                  |

| 29InputXRESActive high external reset with internal<br>pull-down30I/OP4[0]31I/OP4[2]32I/OP4[4]33I/OP4[6]34I/OIP2[0]Direct switched capacitor block input35I/OI36I/OP2[4]86I/OP2[6]87I/OP2[6]88I/OI99I/OI/O90Analog column mux input39I/OI/O40I/OI90I41I/OI42PowerV <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |     |     |             |                                                                  |

| pull-down           30         I/O         P4[0]           31         I/O         P4[2]           32         I/O         P4[4]           33         I/O         P4[6]           34         I/O         I         P2[0]           35         I/O         I         P2[2]           36         I/O         P2[4]         External analog ground (AGND)           37         I/O         P2[6]         External voltage reference (VREF)           38         I/O         I         P0[0]         Analog column mux input           39         I/O         I/O         P0[2]         Analog column mux input and column ou           40         I/O         I/O         P0[6]         Analog column mux input           42         Power         V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |     |     |             | Active high external reset with internal                         |

| 31         I/O         P4[2]           32         I/O         P4[4]           33         I/O         P4[6]           34         I/O         I         P2[0]         Direct switched capacitor block input           35         I/O         I         P2[2]         Direct switched capacitor block input           36         I/O         P2[4]         External analog ground (AGND)           37         I/O         P2[6]         External voltage reference (VREF)           38         I/O         I         P0[0]         Analog column mux input           39         I/O         I/O         P0[2]         Analog column mux input and column ou           40         I/O         I/O         P0[6]         Analog column mux input           42         Power         V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23        |     | Jui | ANEO        |                                                                  |

| 32         I/O         P4[4]           33         I/O         P4[6]           34         I/O         I         P2[0]         Direct switched capacitor block input           35         I/O         I         P2[2]         Direct switched capacitor block input           36         I/O         P2[4]         External analog ground (AGND)           37         I/O         P2[6]         External voltage reference (VREF)           38         I/O         I         P0[0]         Analog column mux input           39         I/O         I/O         P0[2]         Analog column mux input and column ou           40         I/O         I/O         P0[6]         Analog column mux input and column ou           41         I/O         I         P0[6]         Analog column mux input           42         Power         V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30        | I/O |     | P4[0]       |                                                                  |

| 33     I/O     P4[6]       34     I/O     I     P2[0]     Direct switched capacitor block input       35     I/O     I     P2[2]     Direct switched capacitor block input       36     I/O     P2[4]     External analog ground (AGND)       37     I/O     P2[6]     External voltage reference (VREF)       38     I/O     I     P0[0]     Analog column mux input       39     I/O     I/O     P0[2]     Analog column mux input and column ou       40     I/O     I/O     P0[6]     Analog column mux input       42     Power     V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31        | I/O |     | P4[2]       |                                                                  |

| 34     I/O     I     P2[0]     Direct switched capacitor block input       35     I/O     I     P2[2]     Direct switched capacitor block input       36     I/O     P2[4]     External analog ground (AGND)       37     I/O     P2[6]     External voltage reference (VREF)       38     I/O     I     P0[0]     Analog column mux input       39     I/O     I/O     P0[2]     Analog column mux input and column ou       40     I/O     I/O     P0[6]     Analog column mux input       42     Power     V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32        | I/O |     | P4[4]       |                                                                  |

| 35     I/O     I     P2[2]     Direct switched capacitor block input       36     I/O     P2[4]     External analog ground (AGND)       37     I/O     P2[6]     External voltage reference (VREF)       38     I/O     I     P0[0]     Analog column mux input       39     I/O     I/O     P0[2]     Analog column mux input and column ou       40     I/O     I/O     P0[4]     Analog column mux input and column ou       41     I/O     I     P0[6]     Analog column mux input       42     Power     V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33        | I/O |     | P4[6]       |                                                                  |

| 36     I/O     P2[4]     External analog ground (AGND)       37     I/O     P2[6]     External voltage reference (VREF)       38     I/O     I     P0[0]     Analog column mux input       39     I/O     I/O     P0[2]     Analog column mux input and column ou       40     I/O     I/O     P0[4]     Analog column mux input and column ou       41     I/O     I     P0[6]     Analog column mux input       42     Power     V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34        | I/O | I   | P2[0]       | Direct switched capacitor block input                            |

| 36     I/O     P2[4]     External analog ground (AGND)       37     I/O     P2[6]     External voltage reference (VREF)       38     I/O     I     P0[0]     Analog column mux input       39     I/O     I/O     P0[2]     Analog column mux input and column ou       40     I/O     I/O     P0[4]     Analog column mux input and column ou       41     I/O     I     P0[6]     Analog column mux input       42     Power     V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35        | I/O | 1   | P2[2]       | Direct switched capacitor block input                            |

| 37     I/O     P2[6]     External voltage reference (VREF)       38     I/O     I     P0[0]     Analog column mux input       39     I/O     I/O     P0[2]     Analog column mux input and column ou       40     I/O     I/O     P0[4]     Analog column mux input and column ou       41     I/O     I     P0[6]     Analog column mux input       42     Power     V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36        | I/O |     |             | External analog ground (AGND)                                    |

| 39         I/O         I/O         P0[2]         Analog column mux input and column ou           40         I/O         I/O         P0[4]         Analog column mux input and column ou           41         I/O         I         P0[6]         Analog column mux input           42         Power         V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37        | I/O |     | P2[6]       |                                                                  |