Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•**X**F

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                  |

| Number of I/O              | 15                                                                             |

| Program Memory Size        | 12KB (12K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 4x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 20-PDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc201-e-p |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

Note: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ12MC201/202 family of 16-bit Digital Signal Controllers (DSC) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The   | AVDD    | and     | AVss   | pins | mus | st be |

|-------|-------|---------|---------|--------|------|-----|-------|

|       | conn  | ected   | indep   | endent | of   | the | ADC   |

|       | volta | ge refe | source. |        |      |     |       |

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD, and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                   |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                 |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                |

- Note 1: This bit can be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

NOTES:

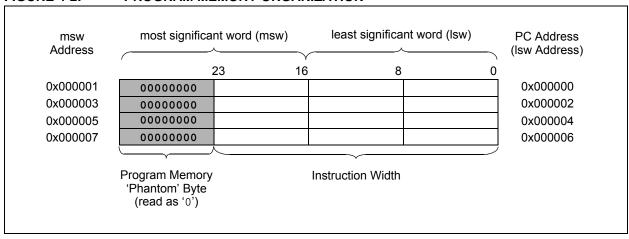

### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ12MC201/202 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJ12MC201/202 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

### Т

| TABLE 4-5: TIMER REGISTER MAP |  |

|-------------------------------|--|

|-------------------------------|--|

| SFR<br>Name | SFR<br>Addr | Bit 15                                                     | Bit 14                                     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7      | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|------------------------------------------------------------|--------------------------------------------|--------|--------|--------|--------|-------|----------|------------|-------|-------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100        | Timer1 Register                                            |                                            |        |        |        |        |       |          |            |       |       | 0000   |       |       |       |       |               |

| PR1         | 0102        | Period Register 1                                          |                                            |        |        |        |        |       |          |            |       | FFFF  |        |       |       |       |       |               |

| T1CON       | 0104        | TON                                                        | TON - TSIDL TGATE TCKPS<1:0> - TSYNC TCS - |        |        |        |        |       |          | 0000       |       |       |        |       |       |       |       |               |

| TMR2        | 0106        | Timer2 Register                                            |                                            |        |        |        |        |       |          |            |       | 0000  |        |       |       |       |       |               |

| TMR3HLD     | 0108        | Timer3 Holding Register (for 32-bit timer operations only) |                                            |        |        |        |        |       |          |            |       | xxxx  |        |       |       |       |       |               |

| TMR3        | 010A        |                                                            |                                            |        |        |        |        |       | Timer3   | Register   |       |       |        |       |       |       |       | 0000          |

| PR2         | 010C        |                                                            |                                            |        |        |        |        |       | Period F | Register 2 |       |       |        |       |       |       |       | FFFF          |

| PR3         | 010E        |                                                            |                                            |        |        |        |        |       | Period F | Register 3 |       |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON                                                        | _                                          | TSIDL  | _      | -      | -      | -     |          | —          | TGATE | TCKP  | S<1:0> | T32   | _     | TCS   |       | 0000          |

| T3CON       | 0112        | TON                                                        | _                                          | TSIDL  | -      | _      | _      | _     |          | —          | TGATE | TCKP  | S<1:0> | —     | _     | TCS   | -     | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### **TABLE 4-6: INPUT CAPTURE REGISTER MAP**

| SFR Name | SFR<br>Addr | Bit 15                   | Bit 14  | Bit 13 | Bit 12    | Bit 11     | Bit 10     | Bit 9       | Bit 8       | Bit 7        | Bit 6                           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------------------------|---------|--------|-----------|------------|------------|-------------|-------------|--------------|---------------------------------|-------|-------|-------|-------|----------|-------|---------------|

| IC1BUF   | 0140        | Input 1 Capture Register |         |        |           |            |            |             |             |              |                                 |       |       | xxxx  |       |          |       |               |

| IC1CON   | 0142        | _                        | _       | ICSIDL | _         | _          | _          | _           | _           | ICTMR        | IR ICI<1:0> ICOV ICBNE ICM<2:0> |       |       |       |       | 0000     |       |               |

| IC2BUF   | 0144        | Input 2 Capture Register |         |        |           |            |            |             |             |              |                                 | xxxx  |       |       |       |          |       |               |

| IC2CON   | 0146        |                          | —       | ICSIDL |           |            | -          |             |             | ICTMR        | ICI<                            | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |                          |         |        |           |            |            |             | Input 7 Ca  | pture Regist | ter                             |       |       |       |       |          |       | xxxx          |

| IC7CON   | 015A        |                          | —       | ICSIDL |           |            | -          |             |             | ICTMR        | ICI<                            | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        | Input 8Capture Register  |         |        |           |            |            |             |             |              |                                 | xxxx  |       |       |       |          |       |               |

| IC8CON   | 015E        | _                        | —       | ICSIDL |           |            | -          | _           | _           | ICTMR        | ICI<                            | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| Legend:  |             |                          | n Reset |        | amontod r | and as '0' | Posot valu | los aro sho | wn in hovar | locimal      |                                 |       |       |       |       |          |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-7: **OUTPUT COMPARE REGISTER MAP**

| SFR Name                                       | SFR<br>Addr | Bit 15                    | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7      | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|------------------------------------------------|-------------|---------------------------|--------|--------|--------|--------|--------|-------|------------|------------|--------------|-------|-------|--------|-------|----------|-------|---------------|

| OC1RS 0180 Output Compare 1 Secondary Register |             |                           |        |        |        |        |        |       |            |            |              | xxxx  |       |        |       |          |       |               |

| OC1R                                           | 0182        | Output Compare 1 Register |        |        |        |        |        |       |            |            | xxxx         |       |       |        |       |          |       |               |

| OC1CON                                         | 0184        | _                         | _      | OCSIDL | _      | _      | _      | _     | _          | _          | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC2RS                                          | 0186        |                           |        |        |        |        |        | Out   | put Compar | e 2 Second | ary Register |       |       |        |       |          |       | xxxx          |

| OC2R                                           | 0188        | Output Compare 2 Register |        |        |        |        |        |       |            |            | xxxx         |       |       |        |       |          |       |               |

| OC2CON                                         | 018A        | _                         | _      | OCSIDL | _      |        | —      | _     |            | —          | —            | —     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

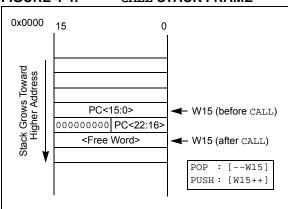

### 4.2.6 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the dsPIC33FJ12MC201/202 devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-4. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSb |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word aligned.

Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. However, the stack error trap will occur on a subsequent push operation. For example, to cause a stack error trap when the stack grows beyond address 0x0C00 in RAM, initialize the SPLIM with the value 0x0BFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### FIGURE 4-4: CALL STACK FRAME

### 4.2.7 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code, when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code, when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

### 4.3 Instruction Addressing Modes

The addressing modes shown in Table 4-26 form the basis of the addressing modes that are optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those provided in other instruction types.

### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (near data space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

### 4.3.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 < function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be register direct), which is referred to as Wb. Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

| Note: | Not all instructions support all the         |

|-------|----------------------------------------------|

|       | addressing modes given above.                |

|       | Individual instructions can support          |

|       | different subsets of these addressing modes. |

| TABLE 7-1: | INTERRUPT VECTORS (CONTINUED) |

|------------|-------------------------------|

|------------|-------------------------------|

| Vector<br>Number<br>Number |        | IVT Address           | AIVT Address          | Interrupt Source               |  |  |

|----------------------------|--------|-----------------------|-----------------------|--------------------------------|--|--|

| 54                         | 46     | 0x000070              | 0x000170              | Reserved                       |  |  |

| 55                         | 47     | 0x000072              | 0x000172              | Reserved                       |  |  |

| 56                         | 48     | 0x000074              | 0x000174              | Reserved                       |  |  |

| 57                         | 49     | 0x000076              | 0x000176              | Reserved                       |  |  |

| 58                         | 50     | 0x000078              | 0x000178              | Reserved                       |  |  |

| 59                         | 51     | 0x00007A              | 0x00017A              | Reserved                       |  |  |

| 60                         | 52     | 0x00007C              | 0x00017C              | Reserved                       |  |  |

| 61                         | 53     | 0x00007E              | 0x00017E              | Reserved                       |  |  |

| 62                         | 54     | 0x000080              | 0x000180              | Reserved                       |  |  |

| 63                         | 55     | 0x000082              | 0x000182              | Reserved                       |  |  |

| 64                         | 56     | 0x000084              | 0x000184              | Reserved                       |  |  |

| 65                         | 57     | 0x000086              | 0x000186              | PWM1 – PWM1 Period Match       |  |  |

| 66                         | 58     | 0x000088              | 0x000188              | QEI – Position Counter Compare |  |  |

| 67                         | 59     | 0x00008A              | 0x00018A              | Reserved                       |  |  |

| 68                         | 60     | 0x00008C              | 0x00018C              | Reserved                       |  |  |

| 69                         | 61     | 0x00008E              | 0x00018E              | Reserved                       |  |  |

| 70                         | 62     | 0x000090              | 0x000190              | Reserved                       |  |  |

| 71                         | 63     | 0x000092              | 0x000192              | FLTA1 – PWM1 Fault A           |  |  |

| 72                         | 64     | 0x000094              | 0x000194              | Reserved                       |  |  |

| 73                         | 65     | 0x000096              | 0x000196              | U1E – UART1 Error              |  |  |

| 74                         | 66     | 0x000098              | 0x000198              | Reserved                       |  |  |

| 75                         | 67     | 0x00009A              | 0x00019A              | Reserved                       |  |  |

| 76                         | 68     | 0x00009C              | 0x00019C              | Reserved                       |  |  |

| 77                         | 69     | 0x00009E              | 0x00019E              | Reserved                       |  |  |

| 78                         | 70     | 0x0000A0              | 0x0001A0              | Reserved                       |  |  |

| 79                         | 71     | 0x0000A2              | 0x0001A2              | Reserved                       |  |  |

| 80                         | 72     | 0x0000A4              | 0x0001A4              | Reserved                       |  |  |

| 81                         | 73     | 0x0000A6              | 0x0001A6              | PWM2 – PWM2 Period Match       |  |  |

| 82                         | 74     | 0x0000A8              | 0x0001A8              | FLTA2 – PWM2 Fault A           |  |  |

| 83-125                     | 75-117 | 0x0000AA-<br>0x0000FE | 0x0001AA-<br>0x0001FE | Reserved                       |  |  |

### TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000104     | Reserved           |

| 1             | 0x000006    | 0x000106     | Oscillator Failure |

| 2             | 0x00008     | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x00000C    | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | Reserved           |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 0x000012    | 0x000112     | Reserved           |

| R/W-0        | R/W-0         | U-0                                | U-0            | U-0               | U-0  | R/W-0           | R/W-0 |

|--------------|---------------|------------------------------------|----------------|-------------------|------|-----------------|-------|

| IC8MD        | IC7MD         | —                                  | —              | _                 | _    | IC2MD           | IC1MD |

| bit 15       | 1             |                                    |                |                   |      |                 | bit   |

|              |               |                                    |                |                   |      |                 |       |

| U-0          | U-0           | U-0                                | U-0            | U-0               | U-0  | R/W-0           | R/W-0 |

| _            | _             | <u> </u>                           | _              |                   | —    | OC2MD           | OC1MD |

| bit 7        |               |                                    |                |                   |      |                 | bit   |

|              |               |                                    |                |                   |      |                 |       |

| Legend:      |               |                                    |                |                   |      |                 |       |

| R = Readabl  |               | W = Writable I                     | bit            | U = Unimplen      |      | id as '0'       |       |

| n = Value at | POR           | '1' = Bit is set                   |                | '0' = Bit is clea | ared | x = Bit is unkr | nown  |

|              |               | _                                  |                |                   |      |                 |       |

| bit 15       | •             | Capture 8 Moc                      |                | t                 |      |                 |       |

|              |               | ture 8 module i<br>ture 8 module i |                |                   |      |                 |       |

| bit 14       | • •           | Capture 2 Moc                      |                | ŀ                 |      |                 |       |

|              |               | ture 7 module i                    |                | L .               |      |                 |       |

|              |               | ture 7 module i                    |                |                   |      |                 |       |

| bit 13-10    | Unimplemen    | ted: Read as 'd                    | )'             |                   |      |                 |       |

| bit 9        | IC2MD: Input  | Capture 2 Mod                      | ule Disable bi | t                 |      |                 |       |

|              |               | ture 2 module i                    |                |                   |      |                 |       |

|              | • •           | ture 2 module i                    |                |                   |      |                 |       |

| bit 8        | -             | Capture 1 Moc                      |                | t                 |      |                 |       |

|              |               | ture 1 module i<br>ture 1 module i |                |                   |      |                 |       |

| bit 7-2      | • •           | ted: Read as '0                    |                |                   |      |                 |       |

| bit 1        | -             | out Compare 2                      |                | le bit            |      |                 |       |

|              | •             | ompare 2 modu                      |                |                   |      |                 |       |

|              |               | mpare 2 modu                       |                |                   |      |                 |       |

| bit 0        | OC1MD: Outp   | out Compare 1                      | Module Disabl  | le bit            |      |                 |       |

|              | 1 = Output Co | ompare 1 modu                      | le is disabled |                   |      |                 |       |

|              |               | ompare 1 modu                      |                |                   |      |                 |       |

### REGISTER 10-20: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0     | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|---------|-----|-----|-------|-------|------------|-------|-------|

| —       | _   | —   |       |       | RP13R<4:0> |       |       |

| bit 15  |     | •   |       |       |            |       | bit 8 |

|         |     |     |       |       |            |       |       |

| U-0     | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

| _       | _   | —   |       |       | RP12R<4:0> |       |       |

| bit 7   |     | •   | •     |       |            |       | bit 0 |

|         |     |     |       |       |            |       |       |

| Legend: |     |     |       |       |            |       |       |

|         |     |     |       |       |            |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

- bit 12-8 **RP13R<4:0>:** Peripheral Output Function is Assigned to RP13 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP12R<4:0>:** Peripheral Output Function is Assigned to RP12 Output Pin bits (see Table 10-2 for peripheral function numbers)

### REGISTER 10-21: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP15R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| —     | —   | —   |       |       | RP14R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP15R<4:0>:** Peripheral Output Function is Assigned to RP15 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP14R<4:0>:** Peripheral Output Function is Assigned to RP14 Output Pin bits (see Table 10-2 for peripheral function numbers)

| R/W-0        | U-0                                         | R/W-0                                 | U-0            | U-0              | U-0              | U-0                 | U-0    |

|--------------|---------------------------------------------|---------------------------------------|----------------|------------------|------------------|---------------------|--------|

| PTEN         |                                             | PTSIDL                                |                | —                |                  | —                   | _      |

| bit 15       |                                             |                                       |                |                  |                  |                     | bit 8  |

|              |                                             |                                       |                |                  |                  |                     |        |

| R/W-0        | R/W-0                                       | R/W-0                                 | R/W-0          | R/W-0            | R/W-0            | R/W-0               | R/W-0  |

| L:1 7        | PTOPS                                       | 5<3:0>                                |                | PICK             | PS<1:0>          | PTMOD               | -      |

| bit 7        |                                             |                                       |                |                  |                  |                     | bit 0  |

| Legend:      |                                             |                                       |                |                  |                  |                     |        |

| R = Readat   | ole bit                                     | W = Writable I                        | oit            | U = Unimpler     | nented bit, read | d as '0'            |        |

| -n = Value a | at POR                                      | '1' = Bit is set                      |                | '0' = Bit is cle | ared             | x = Bit is unkno    | own    |

|              |                                             |                                       |                |                  |                  |                     |        |

| bit 15       | PTEN: PWM                                   | Time Base Tim                         | er Enable bit  |                  |                  |                     |        |

|              | 1 = PWM tim                                 |                                       |                |                  |                  |                     |        |

|              | 0 = PWM tim                                 |                                       |                |                  |                  |                     |        |

| bit 14       | -                                           | ted: Read as '0                       |                |                  |                  |                     |        |

| bit 13       | PTSIDL: PWM Time Base Stop in Idle Mode bit |                                       |                |                  |                  |                     |        |

|              |                                             | e base halts in (<br>e base runs in ( |                |                  |                  |                     |        |

| bit 12-8     |                                             | ted: Read as '0                       |                |                  |                  |                     |        |

| bit 7-4      | •                                           | ·: PWM Time Ba                        |                | ostscale Select  | bits             |                     |        |

|              | 1111 <b>= 1:16</b>                          |                                       | •              |                  |                  |                     |        |

|              | •                                           |                                       |                |                  |                  |                     |        |

|              | •                                           |                                       |                |                  |                  |                     |        |

|              | •                                           |                                       |                |                  |                  |                     |        |

|              | 0001 = 1:2 p<br>0000 = 1:1 p                |                                       |                |                  |                  |                     |        |

| bit 3-2      | PTCKPS<1:0                                  | D>: PWM Time I                        | Base Input C   | lock Prescale S  | elect bits       |                     |        |

|              | 11 = PWM tir                                | me base input c                       | ock period is  | 64 TCY (1:64 p   | orescale)        |                     |        |

|              |                                             | me base input c                       |                |                  |                  |                     |        |

|              |                                             | me base input c<br>me base input c    | •              | • •              | ,                |                     |        |

| bit 1-0      |                                             | >: PWM Time B                         | •              | • •              | ale)             |                     |        |

| bit 1-0      |                                             | me base operate                       |                |                  | n Count mode v   | vith interrupts for | double |

|              | 10 = PWM tir                                | ne base operate                       |                |                  | n Count mode     |                     |        |

|              |                                             | ne base operate                       | •              |                  |                  |                     |        |

|              | 00 = PWM tir                                | ne base operate                       | es in a Free-l | Running mode     |                  |                     |        |

### REGISTER 15-1: PxTCON: PWM TIME BASE CONTROL REGISTER

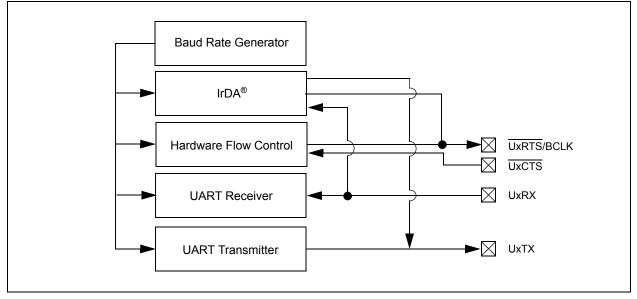

### 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70188) of the *"dsPIC33F/PIC24H Family Reference Manual"*, which is available on the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33FJ12MC201/202 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, and RS-232, and RS-485 interfaces. The module <u>also supports a hardware flow</u> control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-bit or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd, or No Parity Options (for 8-bit data)

- One or two stop bits

- Hardware flow control option with UxCTS and UxRTS pins

- Fully integrated Baud Rate Generator with 16-bit prescaler

- Baud rates ranging from 10 Mbps to 38 bps at 40 MIPS

- 4-deep First-In First-Out (FIFO) Transmit Data buffer

- 4-deep FIFO Receive Data buffer

- Parity, framing and buffer overrun error detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive interrupts

- · A separate interrupt for all UART error conditions

- · Loopback mode for diagnostic support

- · Support for sync and break characters

- · Support for automatic baud rate detection

- IrDA<sup>®</sup> encoder and decoder logic

- 16x baud clock output for IrDA<sup>®</sup> support

A simplified block diagram of the UART module is shown in Figure 19-1. The UART module consists of these key hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

### REGISTER 20-6: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

| U-0            | U-0 | U-0            | U-0   | U-0          | U-0             | U-0      | U-0   |

|----------------|-----|----------------|-------|--------------|-----------------|----------|-------|

| —              | _   | —              | _     | —            | —               | —        | —     |

| bit 15         |     |                |       |              |                 |          | bit 8 |

|                |     |                |       |              |                 |          |       |

| U-0            | U-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

| —              | _   | CSS5           | CSS4  | CSS3         | CSS2            | CSS1     | CSS0  |

| bit 7          |     |                |       |              |                 | ·        | bit 0 |

|                |     |                |       |              |                 |          |       |

| Legend:        |     |                |       |              |                 |          |       |

| R = Readable I | oit | W = Writable b | bit   | U = Unimplei | mented bit, rea | d as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **CSS<5:0>:** ADC Input Scan Selection bits

1 = Select ANx for input scan

0 = Skip ANx for input scan

**2:** CSSx = ANx, where x = 0 through 5.

### **REGISTER 20-7:** AD1PCFGL: ADC1 PORT CONFIGURATION REGISTER LOW<sup>(1,2,3)</sup>

| U-0                               | U-0 | U-0   | U-0                                | U-0   | U-0   | U-0   | U-0   |

|-----------------------------------|-----|-------|------------------------------------|-------|-------|-------|-------|

| —                                 | —   | —     | _                                  | —     | —     | —     | —     |

| bit 15                            |     |       |                                    |       |       |       | bit 8 |

|                                   |     |       |                                    |       |       |       |       |

| U-0                               | U-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| _                                 | —   | PCFG5 | PCFG4                              | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7                             |     |       |                                    |       |       |       | bit 0 |

|                                   |     |       |                                    |       |       |       |       |

| Legend:                           |     |       |                                    |       |       |       |       |

| R = Readable bit W = Writable bit |     | oit   | U = Unimplemented bit, read as '0' |       |       |       |       |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **PCFG<5:0>:** ADC Port Configuration Control bits

'1' = Bit is set

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss 0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

'0' = Bit is cleared

### **Note 1:** On devices without 6 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

- **2:** PCFGx = ANx, where x = 0 through 5.

- **3:** PCFGx bits have no effect if the ADC module is disabled by setting ADxMD bit in the PMDx register. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

-n = Value at POR

x = Bit is unknown

**Note 1:** On devices without 6 analog inputs, all AD1CSSL bits can be selected by user application. However, inputs selected for scan without a corresponding input on device converts VREFL.

### 23.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 23.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 23.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 23.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 24.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ12MC201/202 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJ12MC201/202 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

### Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                | 40°C to +125°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                            | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(4)}$  | -0.3V to +5.6V       |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD < 3.0V^{(4)}$    | 0.3V to (VDD + 0.3V) |

| Maximum current out of Vss pin                                                |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                   | 250 mA               |

| Maximum output current sunk by any I/O pin <sup>(3)</sup>                     | 4 mA                 |

| Maximum output current sourced by any I/O pin <sup>(3)</sup>                  | 4 mA                 |

| Maximum current sunk by all ports                                             | 200 mA               |

| Maximum current sourced by all ports <sup>(2)</sup>                           | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 24-2).

- **3:** Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx, and PGEDx pins, which are able to sink/source 12 mA.

- 4: See the "Pin Diagrams" section for 5V tolerant pins.

### TABLE 24-31: QEI INDEX PULSE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                  | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |     |     |                                                         |            |

|--------------------|--------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------------------------------------------|------------|

| Param<br>No.       | Symbol | Characteristic                                   | ;(1)                                                                                                                                                                                                     | Min | Max | Units                                                   | Conditions |

| TQ50               | TqIL   | Filter Time to Recognize with Digital Filter     | 3 * N * Tcy                                                                                                                                                                                              |     | ns  | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |            |

| TQ51               | TqiH   | Filter Time to Recognize with Digital Filter     | 3 * N * Tcy                                                                                                                                                                                              |     | ns  | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |            |

| TQ55               | Tqidxr | Index Pulse Recognized<br>Counter Reset (ungated | 3 TCY                                                                                                                                                                                                    |     | ns  | —                                                       |            |

Note 1: These parameters are characterized by similarity, but are not tested in manufacturing.

Alignment of index pulses to QEA and QEB is shown for position counter Reset timing only. Shown for forward direction only (QEA leads QEB). Same timing applies for reverse direction (QEA lags QEB) but index pulse recognition occurs on falling edge.

### 25.0 PACKAGING INFORMATION

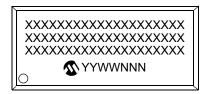

### 25.1 Package Marking Information

### 20-Lead PDIP

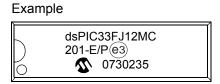

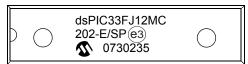

### 20-Lead SSOP

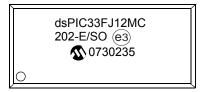

### 20-Lead SOIC

### 28-Lead SPDIP

### 28-Lead SOIC

### Example

### Example

### Example

### Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |  |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Note:  |                                          |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

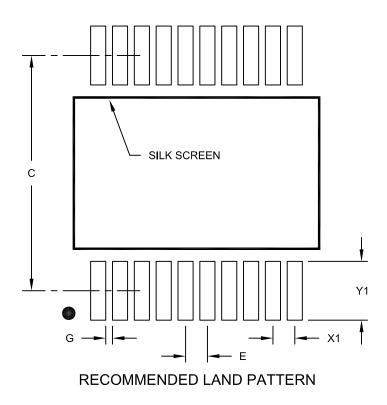

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimension                | MIN         | NOM  | MAX      |      |

| Contact Pitch            | E           |      | 0.65 BSC |      |

| Contact Pad Spacing      | С           |      | 7.20     |      |

| Contact Pad Width (X20)  | X1          |      |          | 0.45 |

| Contact Pad Length (X20) | Y1          |      |          | 1.75 |

| Distance Between Pads    | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A

### TABLE 25-1: MAJOR SECTION UPDATES

| Section Name                                                         | Update Description                                                                                                                                                                                                                                                              |  |  |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

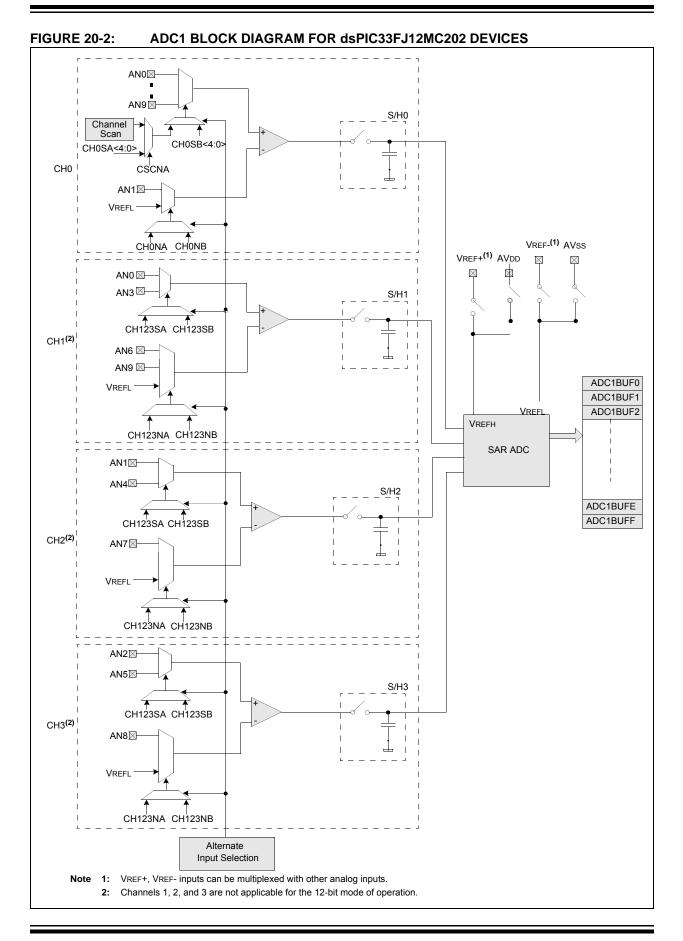

| Section 19.0 "10-bit/12-bit<br>Analog-to-Digital Converter<br>(ADC)" | Updated ADC Conversion Clock Select bits in the AD1CON3 register from ADCS<5:0> to ADCS<7:0>. Any references to these bits have also been updated throughout this data sheet (Register 19-3).                                                                                   |  |  |

|                                                                      | Replaced Figure 19-1 (ADC1 Module Block Diagram for dsPIC33FJ12MC201) and added Figure 19-2 (ADC1 Block Diagram for dsPIC33FJ12MC202).                                                                                                                                          |  |  |

|                                                                      | Removed Equation 19-1: ADC Conversion Clock Period and Figure 19-2: ADC Transfer Function (10-Bit Example).                                                                                                                                                                     |  |  |

|                                                                      | Added Note 2 to Figure 19-2: ADC Conversion Clock Period Block Diagram.                                                                                                                                                                                                         |  |  |

|                                                                      | Updated ADC1 Input Channel 1, 2, 3 Select Register (see Register 19-4) as follows:                                                                                                                                                                                              |  |  |

|                                                                      | <ul> <li>Changed bit 10-9 (CH123NB - dsPIC33FJ12MC201 devices only)<br/>description for bit value of 10 (if AD12B = 0).</li> </ul>                                                                                                                                              |  |  |

|                                                                      | <ul> <li>Updated bit 8 (CH123SB) to reflect device-specific information.</li> <li>Updated bit 0 (CH123SA) to reflect device-specific information.</li> <li>Changed bit 2-1 (CH123NA - dsPIC33FJ12MC201 devices only) description for bit value of 10 (if AD12B = 0).</li> </ul> |  |  |

|                                                                      | <ul> <li>Updated ADC1 Input Channel 0 Select Register (see Register 19-5) as follows:</li> <li>Changed bit value descriptions for bits 12-8</li> <li>Changed bit value descriptions for bits 4-0 (dsPIC33FJ12MC201 devices)</li> </ul>                                          |  |  |

|                                                                      | Modified Notes 1 and 2 in the ADC1 Input Scan Select Register Low (see Register 19-6)                                                                                                                                                                                           |  |  |

|                                                                      | Modified Notes 1 and 2 in the ADC1 Port Configuration Register Low (see Register 19-7)                                                                                                                                                                                          |  |  |

| Section 20.0 "Special Features"                                      | Added FICD register information for address 0xF8000E in the Device Configuration Register Map (see Table 20-1).                                                                                                                                                                 |  |  |

|                                                                      | Added FICD register content (BKBUG, COE, JTAGEN, and ICS<1:0> to the dsPIC33FJ12MC201/202 Configuration Bits Description (see Table 20-2).                                                                                                                                      |  |  |

|                                                                      | Added a note regarding the placement of low-ESR capacitors, after the second paragraph of <b>Section 20.2</b> " <b>On-Chip Voltage Regulator</b> " and to Figure 20-2.                                                                                                          |  |  |

|                                                                      | Removed the words "if enabled" from the second sentence in the fifth paragraph of <b>Section 20.3 "BOR: Brown-out Reset"</b>                                                                                                                                                    |  |  |

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

|                                      |                                            | d                | sPIC 33 FJ 12 MC2 02 T                                                                                   | Examples:                                                                                                                                           |

|--------------------------------------|--------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Tape and Reel Fla<br>Temperature Ran | amily –<br>/ Size (<br><br>ag (if a<br>age | KB)<br>ppli      |                                                                                                          | <ul> <li>a) dsPIC33FJ12MC202-E/SP:<br/>Motor Control dsPIC33, 12 KB program<br/>memory, 28-pin, Extended temperature,<br/>SPDIP package.</li> </ul> |

| Architecture:                        | 33                                         | =                | 16-bit Digital Signal Controller                                                                         |                                                                                                                                                     |

| Flash Memory Family:                 | FJ                                         | =                | Flash program memory, 3.3V                                                                               |                                                                                                                                                     |

| Product Group:                       | MC2                                        | =                | Motor Control family                                                                                     |                                                                                                                                                     |

| Pin Count:                           | 01<br>02                                   | =<br>=           | 20-pin<br>28-pin                                                                                         |                                                                                                                                                     |

| Temperature Range:                   | I<br>E                                     | =<br>=           | -40° C to+85° C (Industrial)<br>-40° C to+125° C (Extended)                                              |                                                                                                                                                     |

| Package:                             | P<br>SP<br>SO<br>ML<br>SS                  | =<br>=<br>=<br>= | Skinny Plastic Dual In-Line - 300 mil body (SPDIP)<br>Plastic Small Outline - Wide, 7.50 mil body (SOIC) |                                                                                                                                                     |