Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

• **X** F

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

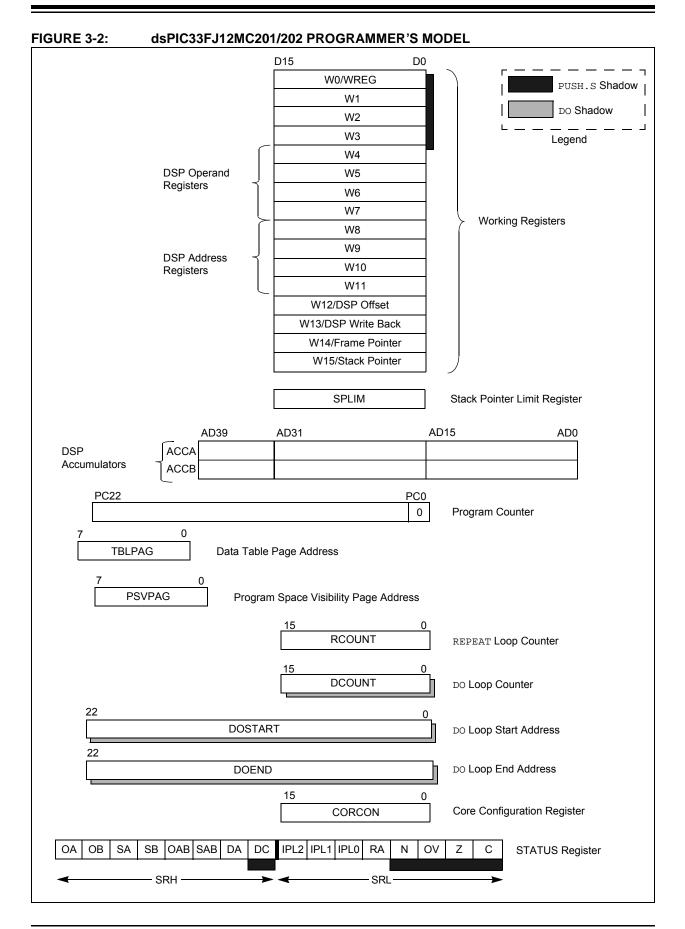

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                  |

| Number of I/O              | 15                                                                             |

| Program Memory Size        | 12KB (12K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 4x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 20-PDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc201-i-p |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                                           |  |  |  |  |  |

|----------|-------------|----------------|-----|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| INDX     | Ι           | ST             | Yes | Quadrature Encoder Index Pulse input.                                                                 |  |  |  |  |  |

| QEA      | I.          | ST             | Yes | Quadrature Encoder Phase A input in QEI mode.                                                         |  |  |  |  |  |

|          |             |                |     | Auxiliary Timer External Clock/Gate input in Timer mode.                                              |  |  |  |  |  |

| QEB      | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI mode.                                                         |  |  |  |  |  |

| UPDN     | 0           | CMOS           | Yes | Auxiliary Timer External Clock/Gate input in Timer mode.<br>Position Up/Down Counter Direction State. |  |  |  |  |  |

| FLTA1    | 1           | ST             |     | PWM1 Fault A input.                                                                                   |  |  |  |  |  |

| PWM1L1   | Ó           |                |     | PWM1 Low output 1                                                                                     |  |  |  |  |  |

| PWM1H1   | ŏ           |                |     | PWM1 High output 1                                                                                    |  |  |  |  |  |

| PWM1L2   | 0           | _              |     | PWM1 Low output 2                                                                                     |  |  |  |  |  |

| PWM1H2   | 0           | _              | No  | PWM1 High output 2                                                                                    |  |  |  |  |  |

| PWM1L3   | 0           | —              |     | PWM1 Low output 3                                                                                     |  |  |  |  |  |

| PWM1H3   | 0           | —              |     | PWM1 High output 3                                                                                    |  |  |  |  |  |

| FLTA2    |             | ST             |     | PWM2 Fault A input.                                                                                   |  |  |  |  |  |

| PWM2L1   | 0           | —              |     | PWM2 Low output 1                                                                                     |  |  |  |  |  |

| PWM2H1   | 0           | —              | No  | PWM2 High output 1                                                                                    |  |  |  |  |  |

| PGED1    | I/O         | ST             | No  | Data I/O pin for programming/debugging communication channel 1.                                       |  |  |  |  |  |

| PGEC1    | I           | ST             | No  | Clock input pin for programming/debugging communication channel 1.                                    |  |  |  |  |  |

| PGED2    | I/O         | ST             | No  | Data I/O pin for programming/debugging communication channel 2.                                       |  |  |  |  |  |

| PGEC2    | I.          | ST             | No  | Clock input pin for programming/debugging communication channel 2.                                    |  |  |  |  |  |

| PGED3    | I/O         | ST             | No  | Data I/O pin for programming/debugging communication channel 3.                                       |  |  |  |  |  |

| PGEC3    | I.          | ST             | No  | Clock input pin for programming/debugging communication channel 3.                                    |  |  |  |  |  |

| MCLR     | I/P         | ST             | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device.                            |  |  |  |  |  |

| AVdd     | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times.                          |  |  |  |  |  |

| AVss     | Р           | Р              | No  | Ground reference for analog modules.                                                                  |  |  |  |  |  |

| Vdd      | Р           | _              | No  | Positive supply for peripheral logic and I/O pins.                                                    |  |  |  |  |  |

| Vcap     | Р           | _              | No  | CPU logic filter capacitor connection.                                                                |  |  |  |  |  |

| Vss      | Р           |                | No  | Ground reference for logic and I/O pins.                                                              |  |  |  |  |  |

| VREF+    | Ι           | Analog         | No  | Analog voltage reference (high) input.                                                                |  |  |  |  |  |

| Vref-    | I           | Analog         | No  | Analog voltage reference (low) input.                                                                 |  |  |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog input O = Output

P = Power I = Input

#### 4.6 Interfacing Program and Data Memory Spaces

The dsPIC33FJ12MC201/202 architecture uses a 24bit-wide program space and a 16-bit-wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ12MC201/ 202 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes, or words, anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for lookups from a large table of static data. The application can only access the lsw of the program word.

### 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the MSb of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-28 and Figure 4-7 show how the program EA is created for table operations and remapping accesses from the data EA.

|                          | Access        | Program Space Address    |            |                                    |               |                   |  |  |

|--------------------------|---------------|--------------------------|------------|------------------------------------|---------------|-------------------|--|--|

| Access Type              | Space         | <23>                     | <22:16>    | <15>                               | <14:1>        | <0>               |  |  |

| Instruction Access       | User          | 0                        |            | PC<22:1>                           |               | 0                 |  |  |

| (Code Execution)         |               |                          | 0xx xxxx x | xxx xxx                            | x xxxx xxx0   |                   |  |  |

| TBLRD/TBLWT              | User          | TBLPAG<7:0>              |            | Data EA<15:0>                      |               |                   |  |  |

| (Byte/Word Read/Write)   |               | 0xxx xxxx xxxx xxxx xxxx |            |                                    |               |                   |  |  |

|                          | Configuration | TB                       | LPAG<7:0>  | PAG<7:0> Data EA<15:0>             |               |                   |  |  |

|                          |               | 1                        | xxx xxxx   | XXXX X                             | xxx xxxx xxxx |                   |  |  |

| Program Space Visibility | User          | 0 PSVPAG<7               |            | <7:0> Data EA<14:0> <sup>(1)</sup> |               | 0> <sup>(1)</sup> |  |  |

| (Block Remap/Read)       |               | 0                        | XXXX XXXX  | 2                                  | xxx xxxx xxxx | xxxx              |  |  |

#### TABLE 4-28: PROGRAM SPACE ADDRESS CONSTRUCTION

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

# 8.1 CPU Clocking System

The dsPIC33FJ12MC201/202 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- FRC Oscillator with postscaler

#### 8.1.1 SYSTEM CLOCK SOURCES

#### 8.1.1.1 Fast RC

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

#### 8.1.1.2 Primary

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

#### 8.1.1.3 Secondary

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

#### 8.1.1.4 Low-Power RC

The Low-Power RC (LPRC) internal oscIllator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

## 8.1.1.5 FRC

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase-Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 8.1.3 "PLL Configuration**".

The FRC frequency depends on the FRC accuracy (see Table 24-18) and the value of the FRC Oscillator Tuning register (see Register 8-4).

#### 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 21.1 "Configuration Bits" for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) Fosc is divided by 2 to generate the device instruction clock (FcY) and the peripheral clock time base (FP). FcY defines the operating speed of the device, and speeds up to 40 MHz are supported by the dsPIC33FJ12MC201/202 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

#### EQUATION 8-1: DEVICE OPERATING FREQUENCY

$FCY = \frac{FOSC}{2}$

| REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3 |                                   |     |                                     |                                    |     |       |       |

|------------------------------------------------------------------|-----------------------------------|-----|-------------------------------------|------------------------------------|-----|-------|-------|

| U-0                                                              | U-0                               | U-0 | U-0                                 | U-0                                | U-0 | R/W-0 | U-0   |

| —                                                                | —                                 | —   |                                     | —                                  | —   | —     | —     |

| bit 15                                                           |                                   |     |                                     |                                    |     |       | bit 8 |

|                                                                  |                                   |     |                                     |                                    |     |       |       |

| U-0                                                              | U-0                               | U-0 | R/W-0                               | U-0                                | U-0 | U-0   | U-0   |

| —                                                                | —                                 | —   | PWM2MD                              | —                                  | —   | —     | —     |

| bit 7                                                            |                                   |     |                                     |                                    |     |       | bit 0 |

|                                                                  |                                   |     |                                     |                                    |     |       |       |

| Legend:                                                          |                                   |     |                                     |                                    |     |       |       |

| R = Readable                                                     | R = Readable bit W = Writable bit |     | bit                                 | U = Unimplemented bit, read as '0' |     |       |       |

| -n = Value at POR '1' = Bit is set                               |                                   |     | '0' = Bit is cleared x = Bit is unl |                                    |     | iown  |       |

|                                                                  |                                   |     |                                     |                                    |     |       |       |

bit 15-5 Unimplemented: Read as '0'

bit 4 PWM2MD: PWM2 Module Disable bit

1 = PWM2 module is disabled

0 = PWM2 module is enabled

bit 3-0 Unimplemented: Read as '0'

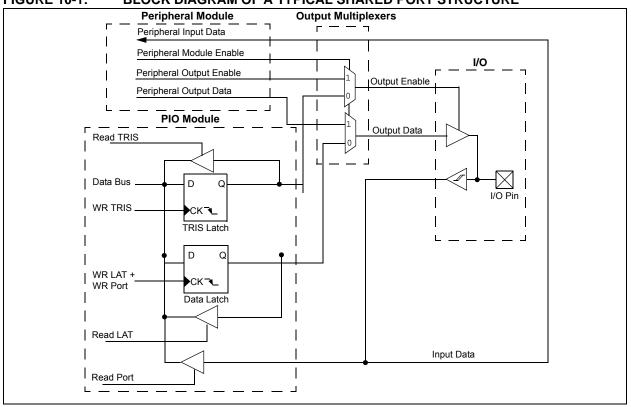

### 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 10.** "I/O Ports" (DS70193) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR, and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 10.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. This means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

© 2007-2011 Microchip Technology Inc.

NOTES:

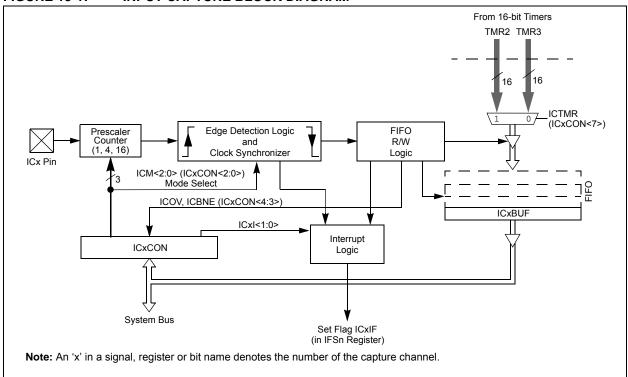

## 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "Input Capture" (DS70198) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJ12MC201/202 devices support up to eight input capture channels.

The Input Capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- 1. Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- 2. Capture timer value on every edge (rising and falling)

- 3. Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each Input Capture channel can select one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on Input Capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Use of Input Capture to provide additional sources of external interrupts

### FIGURE 13-1: INPUT CAPTURE BLOCK DIAGRAM

# 13.1 Input Capture Registers

# REGISTER 13-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0           | U-0                                                                                                              | R/W-0                                                                                                                   | U-0                                                                                                                                 | U-0                         | U-0             | U-0                    | U-0   |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|------------------------|-------|--|--|--|--|

|               | _                                                                                                                | ICSIDL                                                                                                                  | _                                                                                                                                   |                             |                 | _                      | _     |  |  |  |  |

| bit 15        |                                                                                                                  |                                                                                                                         |                                                                                                                                     |                             |                 |                        | bit 8 |  |  |  |  |

|               |                                                                                                                  |                                                                                                                         |                                                                                                                                     |                             |                 |                        |       |  |  |  |  |

| R/W-0         | R/W-0                                                                                                            | R/W-0                                                                                                                   | R-0, HC                                                                                                                             | R-0, HC                     | R/W-0           | R/W-0                  | R/W-0 |  |  |  |  |

| ICTMR         | ICI<                                                                                                             | :1:0>                                                                                                                   | ICOV                                                                                                                                | ICBNE                       |                 | ICM<2:0>               |       |  |  |  |  |

| bit 7         |                                                                                                                  |                                                                                                                         |                                                                                                                                     |                             |                 |                        | bit ( |  |  |  |  |

| Legend:       |                                                                                                                  |                                                                                                                         |                                                                                                                                     |                             |                 |                        |       |  |  |  |  |

| R = Readabl   | e bit                                                                                                            | W = Writable                                                                                                            | bit                                                                                                                                 | U = Unimplen                | nented bit, rea | d as '0'               |       |  |  |  |  |

| -n = Value at | POR                                                                                                              | '1' = Bit is set                                                                                                        |                                                                                                                                     | '0' = Bit is clea           | ared            | x = Bit is unkn        | own   |  |  |  |  |

|               |                                                                                                                  |                                                                                                                         |                                                                                                                                     |                             |                 |                        |       |  |  |  |  |

| bit 15-14     | Unimplemen                                                                                                       | ted: Read as '                                                                                                          | 0'                                                                                                                                  |                             |                 |                        |       |  |  |  |  |

| bit 13        | ICSIDL: Inpu                                                                                                     | t Capture Mod                                                                                                           | ule Stop in Idle                                                                                                                    | e Control bit               |                 |                        |       |  |  |  |  |

|               |                                                                                                                  | 1 = Input capture module will halt in CPU Idle mode                                                                     |                                                                                                                                     |                             |                 |                        |       |  |  |  |  |

|               |                                                                                                                  |                                                                                                                         |                                                                                                                                     | operate in CPU              | Idle mode       |                        |       |  |  |  |  |

| bit 12-8      | -                                                                                                                | ted: Read as '                                                                                                          |                                                                                                                                     |                             |                 |                        |       |  |  |  |  |

| bit 7         | ICTMR: Input Capture Timer Select bits<br>1 = TMR2 contents are captured on capture event                        |                                                                                                                         |                                                                                                                                     |                             |                 |                        |       |  |  |  |  |

|               |                                                                                                                  | ntents are capt<br>ntents are capt                                                                                      |                                                                                                                                     |                             |                 |                        |       |  |  |  |  |

| bit 6-5       | ICI<1:0>: Sel                                                                                                    | CI<1:0>: Select Number of Captures per Interrupt bits                                                                   |                                                                                                                                     |                             |                 |                        |       |  |  |  |  |

|               | 10 = Interrupt<br>01 = Interrupt                                                                                 | t on every four<br>t on every third<br>t on every seco<br>t on every capt                                               | capture event                                                                                                                       | t                           |                 |                        |       |  |  |  |  |

| bit 4         | ICOV: Input C                                                                                                    | Capture Overflo                                                                                                         | w Status Flag                                                                                                                       | bit (read-only)             |                 |                        |       |  |  |  |  |

|               |                                                                                                                  | ture overflow o<br>capture overflo                                                                                      |                                                                                                                                     |                             |                 |                        |       |  |  |  |  |

| bit 3         | ICBNE: Input                                                                                                     | Capture Buffe                                                                                                           | r Empty Status                                                                                                                      | s bit (read-only            | )               |                        |       |  |  |  |  |

|               |                                                                                                                  | ture buffer is n<br>ture buffer is e                                                                                    |                                                                                                                                     | ast one more c              | apture value c  | an be read             |       |  |  |  |  |

| bit 2-0       | ICM<2:0>: In                                                                                                     | put Capture M                                                                                                           | ode Select bits                                                                                                                     | 3                           |                 |                        |       |  |  |  |  |

|               | (Rising<br>110 = Unuse<br>101 = Captur<br>100 = Captur<br>011 = Captur<br>010 = Captur<br>001 = Captur<br>(ICI<1 | g edge detect of<br>d (module disa<br>e mode, every<br>e mode, every<br>e mode, every<br>e mode, every<br>e mode, every | only, all other on<br>bled)<br>16th rising ed<br>4th rising edg<br>rising edge<br>falling edge<br>edge (rising a<br>control interru | control bits are<br>ge<br>e | not applicable  | eep or Idle mode<br>.) |       |  |  |  |  |

### 14.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode (OCM<2:0>) bits in the Output Compare Control (OCxCON<2:0>) register. Table 14-1 lists the different bit settings for the Output Compare modes. Figure 14-2 illustrates the output compare operation for various modes. The user application must disable the associated timer when writing to the output compare control registers to avoid malfunctions.

Note: See Section 13. "Output Compare" in the "dsPIC33F/PIC24H Family Reference Manual" (DS70209) for OCxR and OCxRS register restrictions.

| TABLE 14-1: | <b>OUTPUT COMPARE MODES</b> |

|-------------|-----------------------------|

|-------------|-----------------------------|

| OCM<2:0> | Mode                                 | OCx Pin Initial State                        | OCx Interrupt Generation         |

|----------|--------------------------------------|----------------------------------------------|----------------------------------|

| 000      | Module Disabled                      | Controlled by GPIO register                  | —                                |

| 001      | Active-Low One-Shot                  | 0                                            | OCx Rising edge                  |

| 010      | Active-High One-Shot                 | 1                                            | OCx Falling edge                 |

| 011      | Toggle Mode                          | Current output is maintained                 | OCx Rising and Falling edge      |

| 100      | Delayed One-Shot                     | 0                                            | OCx Falling edge                 |

| 101      | Continuous Pulse mode                | 0                                            | OCx Falling edge                 |

| 110      | PWM mode without fault<br>protection | 0, if OCxR is zero<br>1, if OCxR is non-zero | No interrupt                     |

| 111      | PWM mode with fault protection       | 0, if OCxR is zero<br>1, if OCxR is non-zero | OCFA Falling edge for OC1 to OC4 |

| R/W-0  | U-0   | R/W-0   | R/W-1 HC | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|--------|-------|---------|----------|----------|----------|----------|----------|

| I2CEN  | —     | I2CSIDL | SCLREL   | IPMIEN   | A10M     | DISSLW   | SMEN     |

| bit 15 |       |         |          |          |          |          | bit 8    |

|        |       |         |          |          |          |          |          |

| R/W-0  | R/W-0 | R/W-0   | R/W-0 HC |

| R/W-0 | R/W-U | R/VV-U | R/W-U TC |      |     | R/W-U TC |       |

|-------|-------|--------|----------|------|-----|----------|-------|

| GCEN  | STREN | ACKDT  | ACKEN    | RCEN | PEN | RSEN     | SEN   |

| bit 7 |       |        |          |      |     |          | bit 0 |

| Legend:           |                                                                                                                                                                                  | U = Unimplemented bit, read as '0'                                                  |                                                                   |                               |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------|--|--|--|--|

| R = Readable      | bit                                                                                                                                                                              | W = Writable bit                                                                    | HS = Set in hardware                                              | HC = Cleared in hardware      |  |  |  |  |

| -n = Value at POR |                                                                                                                                                                                  | '1' = Bit is set                                                                    | '0' = Bit is cleared                                              | x = Bit is unknown            |  |  |  |  |

|                   |                                                                                                                                                                                  |                                                                                     |                                                                   |                               |  |  |  |  |

| bit 15            | 12CEN: 12Cx                                                                                                                                                                      |                                                                                     |                                                                   |                               |  |  |  |  |

|                   |                                                                                                                                                                                  |                                                                                     | figures the SDAx and SCLx pin<br>pins are controlled by port func |                               |  |  |  |  |

| bit 14            | Unimplemen                                                                                                                                                                       | ted: Read as '0'                                                                    |                                                                   |                               |  |  |  |  |

| bit 13            | I2CSIDL: Sto                                                                                                                                                                     | p in Idle Mode bit                                                                  |                                                                   |                               |  |  |  |  |

|                   |                                                                                                                                                                                  | ue module operation whe<br>module operation in Idle                                 | n device enters an Idle mode mode                                 |                               |  |  |  |  |

| bit 12            | SCLREL: SC                                                                                                                                                                       | Lx Release Control bit (w                                                           | /hen operating as I <sup>2</sup> C slave)                         |                               |  |  |  |  |

|                   | 1 = Release S<br>0 = Hold SCL                                                                                                                                                    | SCLx clock<br>x clock low (clock stretch                                            | )                                                                 |                               |  |  |  |  |

|                   | at beginning of If STREN = 0                                                                                                                                                     | , software can write '0' t<br>of slave transmission. Ha                             | rdware clear at end of slave re                                   |                               |  |  |  |  |

|                   | Bit is R/S (i.e. transmission.                                                                                                                                                   | , software can only write                                                           | '1' to release clock). Hardware                                   | e clear at beginning of slave |  |  |  |  |

| bit 11            |                                                                                                                                                                                  |                                                                                     | ment Interface (IPMI) Enable t                                    | pit                           |  |  |  |  |

|                   | 1 = IPMI mod<br>0 = IPMI mod                                                                                                                                                     | e is enabled; all address<br>e disabled                                             | es Acknowledged                                                   |                               |  |  |  |  |

| bit 10            | A10M: 10-bit                                                                                                                                                                     | Slave Address bit                                                                   |                                                                   |                               |  |  |  |  |

|                   |                                                                                                                                                                                  | is a 10-bit slave address is a 7-bit slave address                                  |                                                                   |                               |  |  |  |  |

| bit 9             | DISSLW: Disa                                                                                                                                                                     | able Slew Rate Control b                                                            | it                                                                |                               |  |  |  |  |

|                   |                                                                                                                                                                                  | control disabled<br>control enabled                                                 |                                                                   |                               |  |  |  |  |

| bit 8             | SMEN: SMBu                                                                                                                                                                       | is Input Levels bit                                                                 |                                                                   |                               |  |  |  |  |

|                   |                                                                                                                                                                                  | D pin thresholds compliar<br>MBus input thresholds                                  | nt with SMBus specification                                       |                               |  |  |  |  |

| bit 7 GCEN: Gene  |                                                                                                                                                                                  | ral Call Enable bit (when                                                           | operating as I <sup>2</sup> C slave)                              |                               |  |  |  |  |

|                   | <ul> <li>1 = Enable interrupt when a general call address is received in the I2CxRSR<br/>(module is enabled for reception)</li> <li>0 = General call address disabled</li> </ul> |                                                                                     |                                                                   |                               |  |  |  |  |

| bit 6             | STREN: SCL                                                                                                                                                                       | x Clock Stretch Enable b                                                            | it (when operating as I <sup>2</sup> C slave                      | )                             |  |  |  |  |

|                   | Used in conju<br>1 = Enable so                                                                                                                                                   | nction with SCLREL bit.<br>oftware or receive clock s<br>oftware or receive clock s | tretching                                                         | ·                             |  |  |  |  |

### REGISTER 18-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                       |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as $I^2C$ slave)                                                                                                                                                                      |

| SR 2  | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul>             |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit<br>1 = Receive complete, I2CxRCV is full<br>0 = Receive not complete, I2CxRCV is empty<br>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV. |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit<br>1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.         |

### TABLE 22-2: INSTRUCTION SET OVERVIEW

| 2 | ADD  | ADD<br>ADD<br>ADD | Acc<br>f            | Add Accumulators                         | - | T      | · · · · · · · · · · · · · · · · · · · |

|---|------|-------------------|---------------------|------------------------------------------|---|--------|---------------------------------------|

| 2 |      | ADD               | f                   |                                          | 1 | 1      | OA,OB,SA,SB                           |

| 2 |      |                   |                     | f = f + WREG                             | 1 | 1      | C,DC,N,OV,Z                           |

| 2 |      |                   | f,WREG              | WREG = f + WREG                          | 1 | 1      | C,DC,N,OV,Z                           |

| 2 |      | ADD               | #lit10,Wn           | Wd = lit10 + Wd                          | 1 | 1      | C,DC,N,OV,Z                           |

| 2 |      | ADD               | Wb,Ws,Wd            | Wd = Wb + Ws                             | 1 | 1      | C,DC,N,OV,Z                           |

| 2 |      | ADD               | Wb,#lit5,Wd         | Wd = Wb + lit5                           | 1 | 1      | C,DC,N,OV,Z                           |

| 2 |      | ADD               | Wso,#Slit4,Acc      | 16-bit Signed Add to Accumulator         | 1 | 1      | OA,OB,SA,SB                           |

|   | ADDC | ADDC              | f                   | f = f + WREG + (C)                       | 1 | 1      | C,DC,N,OV,Z                           |

|   |      | ADDC              | f,WREG              | WREG = $f + WREG + (C)$                  | 1 | 1      | C,DC,N,OV,Z                           |

|   |      | ADDC              | #lit10,Wn           | Wd = Iit10 + Wd + (C)                    | 1 | 1      | C,DC,N,OV,Z                           |

|   |      | ADDC              | Wb,Ws,Wd            | Wd = Wb + Ws + (C)                       | 1 | 1      | C,DC,N,OV,Z                           |

|   |      | ADDC              | Wb,#lit5,Wd         | Wd = Wb + lit5 + (C)                     | 1 | 1      | C,DC,N,OV,Z                           |

| 3 | AND  | AND               | f                   | f = f .AND. WREG                         | 1 | 1      | N,Z                                   |

|   |      | AND               | f,WREG              | WREG = f .AND. WREG                      | 1 | 1      | N,Z                                   |

|   |      | AND               | #lit10,Wn           | Wd = lit10 .AND. Wd                      | 1 | 1      | N,Z                                   |

|   |      | AND               | Wb,Ws,Wd            | Wd = Wb .AND. Ws                         | 1 | 1      | N,Z                                   |

|   |      | AND               | Wb,#lit5,Wd         | Wd = Wb .AND. lit5                       | 1 | 1      | N,Z                                   |

| 4 | ASR  | ASR               | f                   | f = Arithmetic Right Shift f             | 1 | 1      | C,N,OV,Z                              |

|   |      | ASR               | f,WREG              | WREG = Arithmetic Right Shift f          | 1 | 1      | C,N,OV,Z                              |

|   |      | ASR               | Ws,Wd               | Wd = Arithmetic Right Shift Ws           | 1 | 1      | C,N,OV,Z                              |

|   |      | ASR               | Wb,Wns,Wnd          | Wnd = Arithmetic Right Shift Wb by Wns   | 1 | 1      | N,Z                                   |

|   |      | ASR               | Wb,#lit5,Wnd        | Wnd = Arithmetic Right Shift Wb by lit5  | 1 | 1      | N,Z                                   |

| 5 | BCLR | BCLR              | f,#bit4             | Bit Clear f                              | 1 | 1      | None                                  |

|   |      | BCLR              | Ws,#bit4            | Bit Clear Ws                             | 1 | 1      | None                                  |

| 6 | BRA  | BRA               | C,Expr              | Branch if Carry                          | 1 | 1 (2)  | None                                  |

|   |      | BRA               | GE, Expr            | Branch if greater than or equal          | 1 | 1 (2)  | None                                  |

|   |      | BRA               | GEU, Expr           | Branch if unsigned greater than or equal | 1 | 1 (2)  | None                                  |

|   |      | BRA               | GT, Expr            | Branch if greater than                   | 1 | 1 (2)  | None                                  |

|   |      | BRA               | GTU, Expr           | Branch if unsigned greater than          | 1 | 1 (2)  | None                                  |

|   |      | BRA               | LE, Expr            | Branch if less than or equal             | 1 | 1 (2)  | None                                  |

|   |      | BRA               | LEU, Expr           | Branch if unsigned less than or equal    | 1 | 1 (2)  | None                                  |

|   |      | BRA               | LT, Expr            | Branch if less than                      | 1 | 1 (2)  | None                                  |

|   |      | BRA               | LTU, Expr           | Branch if unsigned less than             | 1 | 1 (2)  | None                                  |

|   |      | BRA               | N,Expr              | Branch if Negative                       | 1 | 1 (2)  | None                                  |

|   |      | BRA               | NC, Expr            | Branch if Not Carry                      | 1 | 1 (2)  | None                                  |

|   |      | BRA               | NN, Expr            | Branch if Not Negative                   | 1 | 1 (2)  | None                                  |

|   |      | BRA               | NOV, Expr           | Branch if Not Overflow                   | 1 | 1 (2)  | None                                  |

|   |      | BRA               | NZ, Expr            | Branch if Not Zero                       | 1 | 1 (2)  | None                                  |

|   |      | BRA               | OA, Expr            | Branch if Accumulator A overflow         | 1 | 1 (2)  | None                                  |

|   |      | BRA               | OB, Expr            | Branch if Accumulator B overflow         | 1 | 1 (2)  | None                                  |

|   |      | BRA               | OV, Expr            | Branch if Overflow                       | 1 | 1 (2)  | None                                  |

|   |      | BRA               | SA, Expr            | Branch if Accumulator A saturated        | 1 | 1 (2)  | None                                  |

| 7 |      | BRA               | SB, Expr            | Branch if Accumulator B saturated        | 1 | 1 (2)  | None                                  |

|   |      | BRA               | Expr                | Branch Unconditionally                   | 1 | 2      | None                                  |

|   |      |                   |                     | Branch if Zero                           | 1 | 1 (2)  | None                                  |

|   |      | BRA               | Z,Expr<br>Wn        | Computed Branch                          | 1 | 2      | None                                  |

|   | BSET | BRA               |                     | Bit Set f                                | 1 | 2<br>1 | None                                  |

|   | 1460 | BSET              | f,#bit4             | Bit Set Ws                               | 1 | 1      | None                                  |

| 8 | DCW  | BSET              | Ws,#bit4            |                                          |   |        |                                       |

| D | BSW  | BSW.C             | Ws,Wb               | Write C bit to Ws <wb></wb>              | 1 | 1      | None                                  |

|   | DEC  | BSW.Z             | Ws,Wb               | Write Z bit to Ws <wb></wb>              | 1 | 1      | None                                  |

| 9 | BTG  | BTG<br>BTG        | f,#bit4<br>Ws,#bit4 | Bit Toggle f<br>Bit Toggle Ws            | 1 | 1      | None<br>None                          |

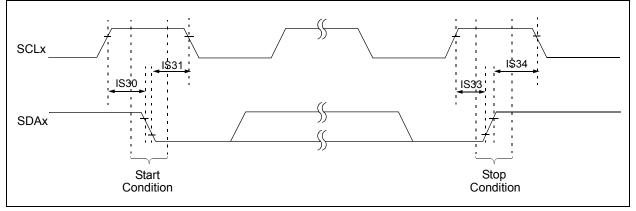

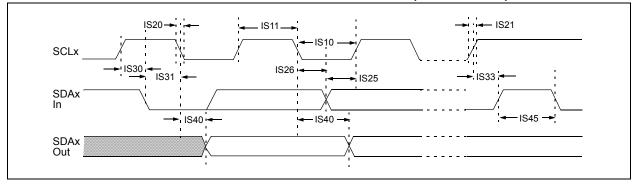

#### TABLE 24-40: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHARACTERISTICS |                   |                               |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                        |  |  |

|--------------------|-------------------|-------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|--|

| Param<br>No.       | Symbol<br>TLO:SCL | Characteristic <sup>(3)</sup> |                           | Min <sup>(1)</sup>                                                                                                                                                                                                                                                                      | Max  | Units | Conditions             |  |  |

| IM10               |                   | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | _                      |  |  |

|                    |                   |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | _                      |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         |      | μs    | —                      |  |  |

| IM11               | THI:SCL           | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         |      | μs    | —                      |  |  |

|                    |                   |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         |      | μs    | —                      |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         |      | μs    | —                      |  |  |

| IM20               | TF:SCL            | SDAx and SCLx<br>Fall Time    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                       | 300  | ns    | CB is specified to be  |  |  |

|                    |                   |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300  | ns    | from 10 to 400 pF      |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                       | 100  | ns    |                        |  |  |

| IM21               | TR:SCL            | SDAx and SCLx                 | 100 kHz mode              | —                                                                                                                                                                                                                                                                                       | 1000 | ns    | CB is specified to be  |  |  |

|                    |                   | Rise Time                     | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300  | ns    | from 10 to 400 pF      |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                                                                                                         | 300  | ns    |                        |  |  |

| IM25               | TSU:DAT           | Data Input                    | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                     |      | ns    | _                      |  |  |

|                    |                   | Setup Time                    | 400 kHz mode              | 100                                                                                                                                                                                                                                                                                     |      | ns    |                        |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                                                                                                                                                      | —    | ns    |                        |  |  |

| IM26               | THD:DAT           | Data Input                    | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                       | —    | μs    | _                      |  |  |

|                    |                   | Hold Time                     | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                       | 0.9  | μs    |                        |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                                                                                                                                                     |      | μs    |                        |  |  |

| IM30               | TSU:STA           | Start Condition<br>Setup Time | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | Only relevant for      |  |  |

|                    |                   |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | Repeated Start         |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | condition              |  |  |

| IM31               | THD:STA           | Start Condition<br>Hold Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | After this period the  |  |  |

|                    |                   |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | first clock pulse is   |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | generated              |  |  |

| IM33               | Tsu:sto           | Stop Condition                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | μs    | _                      |  |  |

|                    |                   | Setup Time                    | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         |      | μs    |                        |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         |      | μs    |                        |  |  |

| IM34               | THD:STO           | Stop Condition                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         |      | ns    | —                      |  |  |

|                    |                   | Hold Time                     | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | ns    | -                      |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                                                                                                         | —    | ns    | -                      |  |  |

| IM40               | TAA:SCL           | Output Valid<br>From Clock    | 100 kHz mode              | — 3500 ns                                                                                                                                                                                                                                                                               |      | —     |                        |  |  |

|                    |                   |                               | 400 kHz mode              | —                                                                                                                                                                                                                                                                                       | 1000 | ns    | —                      |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                       | 400  | ns    | —                      |  |  |

| IM45               | TBF:SDA           | Bus Free Time                 | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                     | —    | μs    | Time the bus must be   |  |  |

|                    |                   |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                     | _    | μs    | free before a new      |  |  |

|                    |                   |                               | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                                                                                                                     | —    | μs    | transmission can start |  |  |

| IM50               | Св                | Bus Capacitive L              | oading                    | —                                                                                                                                                                                                                                                                                       | 400  | pF    | —                      |  |  |

| IM51               | Pgd               | Pulse Gobbler De              | elav                      | 65                                                                                                                                                                                                                                                                                      | 390  | ns    | See Note 4             |  |  |