Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc202-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33FJ12MC201/202

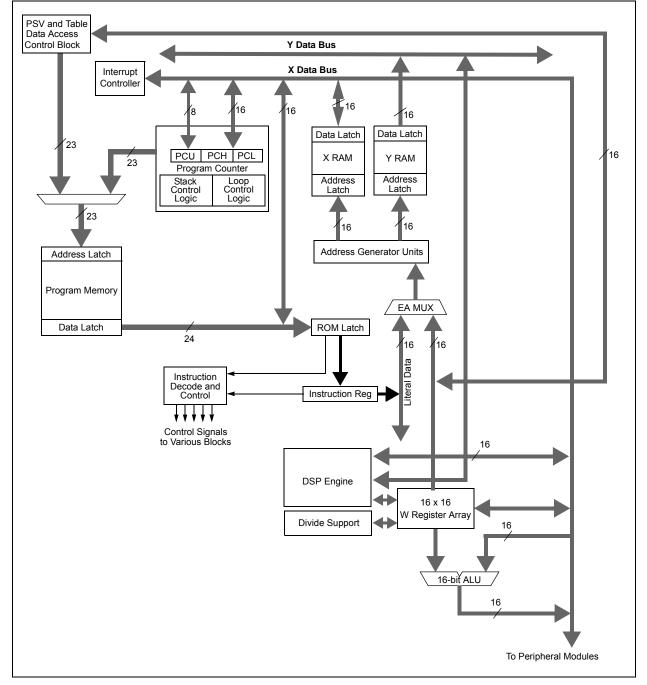

The dsPIC33FJ12MC201/202 supports 16/16 and 32/ 16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data. A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

## FIGURE 3-1: dsPIC33FJ12MC201/202 CPU CORE BLOCK DIAGRAM

## TABLE 4-19: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ12MC201

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All Resets |

|--------------|------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|------------|

| RPOR0        | 06C0 | _      | _      | —      |        |        | RP1R<4:0> | •     |       | —     | _     | —     |       |       | RP0R<4:0>  |       |       | 0000       |

| RPOR2        | 06C4 | _      | _      | _      | _      | _      | _         | _     | _     | _     | _     | _     |       |       | RP4R<4:0>  |       |       | 0000       |

| RPOR3        | 06C6 | _      | _      | _      |        |        | RP7R<4:0> | •     |       | _     | _     | _     | _     | _     | _          | _     | _     | 0000       |

| RPOR4        | 06C8 | _      | _      | _      |        |        | RP9R<4:0> | •     |       | _     | _     | _     |       |       | RP8R<4:0>  |       |       | 0000       |

| RPOR6        | 06CC | _      | _      | _      |        |        | RP13R<4:0 | >     |       | _     | _     | _     |       | F     | RP12R<4:0> |       |       | 0000       |

| RPOR7        | 06CE | _      | _      | _      |        |        | RP15R<4:0 | >     |       | _     | —     | _     |       | F     | RP14R<4:0> |       |       | 0000       |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: PORTA REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|------------|

| TRISA        | 02C0 | -      | _      |        | _      | _      | _      | -     | _     |       |       | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F       |

| PORTA        | 02C2 | _      | _      | -      |        | _      | _      | -     | -     | -     | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx       |

| LATA         | 02C4 | -      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx       |

| ODCA         | 02C6 | _      | —      | _      | _      | _      | _      | _     | _     | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000       |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-21: PORTB REGISTER MAP FOR dsPIC33FJ12MC202

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|--------------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF       |

| PORTB        | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx       |

| LATB         | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx       |

| ODCB         | 02CE | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: PORTB REGISTER MAP FOR dsPIC33FJ12MC201

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|------------|

| TRISB     | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | _      | _      | TRISB9 | TRISB8 | TRISB7 | —     | —     | TRISB4 | _     | _     | TRISB1 | TRISB0 | F393       |

| PORTB     | 02CA | RB15    | RB14    | RB13    | RB12    | -      | _      | RB9    | RB8    | RB7    | —     | —     | RB4    | _     | —     | RB1    | RB0    | xxxx       |

| LATB      | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | -      | _      | LATB9  | LATB8  | LATB7  | —     | —     | LATB4  | _     | —     | LATB1  | LATB0  | xxxx       |

| ODCB      | 02CE | ODCB15  | ODCB14  | ODCB13  | ODCB12  | _      | _      | ODCB9  | ODCB8  | ODCB7  | _     | _     | ODCB4  | —     | _     | ODCB1  | ODCB0  | 0000       |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal

| U-0    | U-0 | U-0 | U-0  | U-0     | U-0 | U-0 | U-0   |

|--------|-----|-----|------|---------|-----|-----|-------|

| —      | —   | —   | —    | —       | —   | —   | —     |

| bit 15 |     |     |      |         |     |     | bit 8 |

|        |     |     |      |         |     |     |       |

| W-0    | W-0 | W-0 | W-0  | W-0     | W-0 | W-0 | W-0   |

|        |     |     | NVMK | EY<7:0> |     |     |       |

#### REGISTER 5-2: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| Legend:           | SO = Settable only bit |                       |                    |

|-------------------|------------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7

bit 7-0 NVMKEY<7:0>: Key Register (write-only) bits

bit 0

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| R/W-0        | R-0         | U-0                                     | U-0               | U-0              | U-0              | U-0             | U-0    |

|--------------|-------------|-----------------------------------------|-------------------|------------------|------------------|-----------------|--------|

| ALTIVT       | DISI        | _                                       |                   |                  |                  | _               |        |

| oit 15       | ·           |                                         |                   |                  |                  | ·               | bit 8  |

|              |             |                                         |                   |                  |                  |                 |        |

| U-0          | U-0         | U-0                                     | U-0               | U-0              | R/W-0            | R/W-0           | R/W-0  |

|              |             | _                                       |                   |                  | INT2EP           | INT1EP          | INT0EP |

| bit 7        |             |                                         |                   |                  |                  |                 | bit (  |

|              |             |                                         |                   |                  |                  |                 |        |

| Legend:      | L- L-14     |                                         | L 14              |                  |                  |                 |        |

| R = Readab   |             | W = Writable                            |                   |                  | mented bit, read |                 |        |

| -n = Value a | t POR       | '1' = Bit is set                        |                   | '0' = Bit is cle | eared            | x = Bit is unkı | nown   |

| bit 15       |             |                                         | to mu unt \/o oto | r Tabla bit      |                  |                 |        |

|              |             | able Alternate In<br>ernate vector tab  | •                 |                  |                  |                 |        |

|              |             | ndard (default) v                       | -                 |                  |                  |                 |        |

| bit 14       |             | Instruction Statu                       |                   |                  |                  |                 |        |

|              | 1 = DISI in | struction is active                     | е                 |                  |                  |                 |        |

|              | 0 = DISI in | struction is not a                      | ctive             |                  |                  |                 |        |

| bit 13-3     | Unimpleme   | ented: Read as '                        | 0'                |                  |                  |                 |        |

| bit 2        | INT2EP: Ex  | ternal Interrupt 2                      | 2 Edge Detec      | t Polarity Selec | t bit            |                 |        |

|              |             | t on negative ed                        |                   |                  |                  |                 |        |

|              | •           | t on positive edg                       |                   |                  |                  |                 |        |

| bit 1        |             | ternal Interrupt 1                      | •                 | t Polarity Selec | t bit            |                 |        |

|              |             | t on negative edg                       | •                 |                  |                  |                 |        |

| bit 0        | •           | t on positive edg                       |                   | t Dolority Soloo | st hit           |                 |        |

|              |             | ternal Interrupt 0<br>t on negative edg | •                 |                  |                  |                 |        |

|              |             |                                         |                   |                  |                  |                 |        |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

## REGISTER 7-9: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled0 = Interrupt request not enabled

- bit 0 **INTOIE:** External Interrupt 0 Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

## 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ12MC201/202 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJ12MC201/202 devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## 9.1 Clock Frequency and Clock Switching

dsPIC33FJ12MC201/202 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

#### 9.2 Instruction-Based Power-Saving Modes

dsPIC33FJ12MC201/202 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

#### 9.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV#SLEEP\_MODE; Put the device into Sleep modePWRSAV#IDLE\_MODE; Put the device into Idle mode

## 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 10.** "I/O Ports" (DS70193) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR, and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

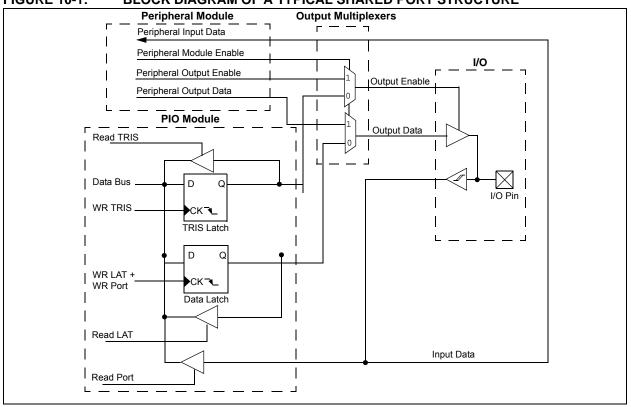

## 10.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. This means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

© 2007-2011 Microchip Technology Inc.

| U-0          | U-0                          | U-0                                              | R/W-1          | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|--------------|------------------------------|--------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|

|              |                              | —                                                |                |                  | T3CKR<4:0>      | •               |       |

| bit 15       |                              |                                                  |                |                  |                 |                 | bit 8 |

| U-0          | U-0                          | U-0                                              | R/W-1          | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|              |                              | _                                                |                | 1011 1           | T2CKR<4:0>      |                 |       |

| bit 7        |                              |                                                  |                |                  |                 |                 | bit 0 |

|              |                              |                                                  |                |                  |                 |                 |       |

| Legend:      |                              |                                                  |                |                  |                 |                 |       |

| R = Readab   | le bit                       | W = Writable                                     | bit            | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value a | t POR                        | '1' = Bit is set                                 | t              | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| bit 7 5      | 00001 = Inpu<br>00000 = Inpu | t tied to RP15<br>t tied to RP1<br>t tied to RP0 | o'             |                  |                 |                 |       |

| bit 7-5      | •                            | ted: Read as '                                   |                |                  |                 | <b>DD</b> .     |       |

| bit 4-0      | 11111 <b>= Inpu</b>          | •                                                | 2 External Clo | ck (T2CK) to t   | he correspondi  | ng RPn pin      |       |

#### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0          | U-0               | R/W-0                                  | U-0             | U-0              | U-0             | U-0             | U-0   |

|--------------|-------------------|----------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

|              |                   | OCSIDL                                 |                 |                  | _               | _               |       |

| bit 15       |                   | -<br>-                                 |                 |                  |                 |                 | bit   |

|              |                   |                                        |                 |                  |                 |                 |       |

| U-0          | U-0               | U-0                                    | R-0 HC          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|              |                   |                                        | OCFLT           | OCTSEL           |                 | OCM<2:0>        |       |

| bit 7        |                   |                                        |                 |                  |                 |                 | bit   |

| Legend:      |                   | HC = Cleared i                         | n Hardware      | HS = Set in F    | lardware        |                 |       |

| R = Readab   | le bit            | W = Writable b                         | it              | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR             | '1' = Bit is set                       |                 | '0' = Bit is cle |                 | x = Bit is unkr | iown  |

|              |                   |                                        |                 |                  |                 |                 |       |

| bit 15-14    | Unimpleme         | nted: Read as '0                       | ,               |                  |                 |                 |       |

| bit 13       | OCSIDL: Sto       | op Output Compa                        | are in Idle Moo | de Control bit   |                 |                 |       |

|              |                   | compare x will ha                      |                 |                  |                 |                 |       |

|              | -                 | Compare x will co                      | -               | ate in CPU Idle  | mode            |                 |       |

| bit 12-5     | •                 | nted: Read as '0                       |                 |                  |                 |                 |       |

| bit 4        |                   | M Fault Condition                      |                 |                  |                 |                 |       |

|              |                   | ult condition has<br>I Fault condition |                 | ared in hardwar  | e only)         |                 |       |

|              |                   | nly used when O                        |                 | L1.)             |                 |                 |       |

| bit 3        | OCTSEL: O         | utput Compare T                        | imer Select bi  | t                |                 |                 |       |

|              |                   | s the clock sourc                      |                 |                  |                 |                 |       |

|              | 0 = Timer2 is     | s the clock sourc                      | e for Compare   | х                |                 |                 |       |

| bit 2-0      |                   | Output Compare                         |                 |                  |                 |                 |       |

|              |                   | mode on OCx, F                         |                 |                  |                 |                 |       |

|              |                   | mode on OCx, F<br>ze OCx pin low, g    |                 |                  | ulses on OCx    | nin             |       |

|              |                   | ze OCx pin low,                        |                 |                  |                 | pin             |       |

|              | 011 <b>= Comp</b> | are event toggle                       | s OCx pin       |                  |                 |                 |       |

|              |                   | ze OCx pin high,                       | aomnara ava     | nt forooo OCV n  |                 |                 |       |

|              |                   | ze OCx pin high,<br>ze OCx pin low,    |                 |                  |                 |                 |       |

### REGISTER 14-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER

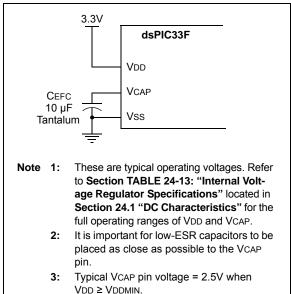

## 21.2 On-Chip Voltage Regulator

All of the dsPIC33FJ12MC201/202 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ12MC201/202 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 21-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 24-13 located in **Section 24.1** "**DC Characteristics**".

| Note: | It is important for low-ESR capacitors to  |

|-------|--------------------------------------------|

|       | be placed as close as possible to the VCAP |

|       | pin.                                       |

On a POR, it takes approximately 20 µs for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 21-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

## 21.3 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

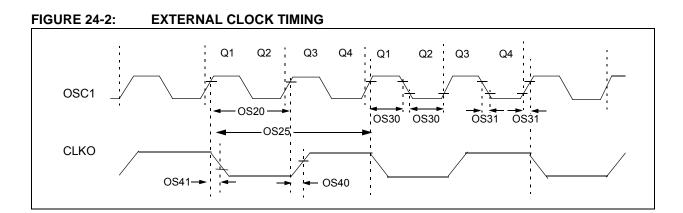

| AC CHA       | RACTER        | RISTICS                                                                            | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                    |                |                   |                          |  |  |  |  |  |

|--------------|---------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|-------------------|--------------------------|--|--|--|--|--|

| Param<br>No. | Symb          | Characteristic                                                                     | Min                                                                                                                                                                                                  | Typ <sup>(1)</sup> | Мах            | Units             | Conditions               |  |  |  |  |  |

| OS10         | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                                                                                   | _                  | 40             | MHz               | EC                       |  |  |  |  |  |

|              |               | Oscillator Crystal Frequency                                                       | 3.5<br>10<br>—                                                                                                                                                                                       |                    | 10<br>40<br>33 | MHz<br>MHz<br>kHz | XT<br>HS<br>SOSC         |  |  |  |  |  |

| OS20         | Tosc          | Tosc = 1/Fosc                                                                      | 12.5                                                                                                                                                                                                 |                    | DC             | ns                |                          |  |  |  |  |  |

| OS25         | TCY           | Instruction Cycle Time <sup>(2,4)</sup>                                            | 25                                                                                                                                                                                                   |                    | DC             | ns                |                          |  |  |  |  |  |

| OS30         | TosL,<br>TosH | External Clock in (OSC1) <sup>(5)</sup><br>High or Low Time                        | 0.375 x Tosc                                                                                                                                                                                         | —                  | 0.625 x Tosc   | ns                | EC                       |  |  |  |  |  |

| OS31         | TosR,<br>TosF | External Clock in (OSC1) <sup>(5)</sup><br>Rise or Fall Time                       | _                                                                                                                                                                                                    | —                  | 20             | ns                | EC                       |  |  |  |  |  |

| OS40         | TckR          | CLKO Rise Time <sup>(3,5)</sup>                                                    | _                                                                                                                                                                                                    | 5.2                |                | ns                | —                        |  |  |  |  |  |

| OS41         | TckF          | CLKO Fall Time <sup>(3,5)</sup>                                                    | _                                                                                                                                                                                                    | 5.2                | —              | ns                | —                        |  |  |  |  |  |

| OS42         | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14                                                                                                                                                                                                   | 16                 | 18             | mA/V              | VDD = 3.3V<br>TA = +25°C |  |  |  |  |  |

#### TABLE 24-16: EXTERNAL CLOCK TIMING REQUIREMENTS

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Instruction cycle period (TCY) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: These parameters are characterized by similarity, but are tested in manufacturing at FIN = 40 MHz only.

- 5: These parameters are characterized by similarity, but are not tested in manufacturing.

- 6: Data for this parameter is Preliminary. This parameter is characterized, but not tested in manufacturing.

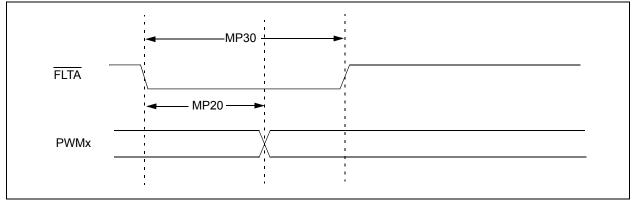

#### TABLE 24-28: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                  | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |     |          |       |            |

|--------------------|--------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>    | Min                                                                                                                                                                                                      | Тур | Max      | Units | Conditions |

| OC15               | Tfd    | Fault Input to PWM I/O<br>Change |                                                                                                                                                                                                          | _   | Tcy + 20 | ns    |            |

| OC20               | TFLT   | Fault Input Pulse Width          | Tcy + 20                                                                                                                                                                                                 |     | —        | ns    |            |

**Note 1:** These parameters are characterized by similarity, but are not tested in manufacturing.

#### FIGURE 24-10: MOTOR CONTROL PWM MODULE FAULT TIMING CHARACTERISTICS

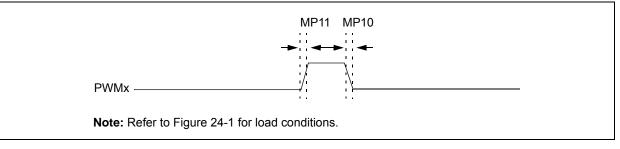

### FIGURE 24-11: MOTOR CONTROL PWM MODULE TIMING CHARACTERISTICS

## dsPIC33FJ12MC201/202

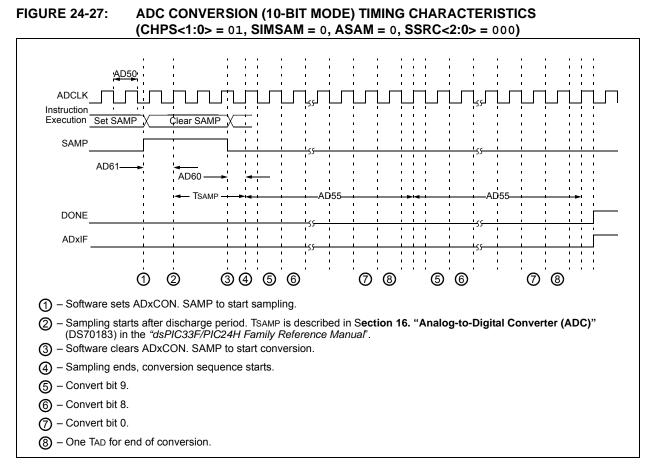

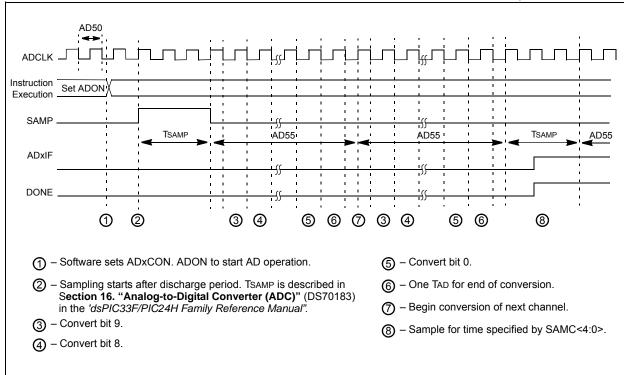

#### FIGURE 24-28: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

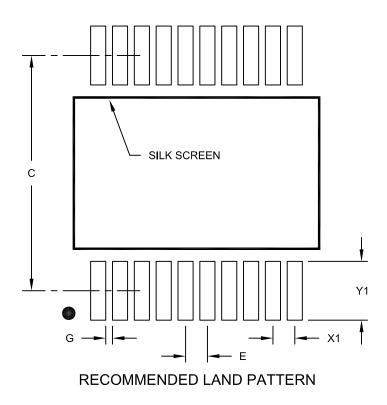

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimension Limits         |             | MIN  | NOM      | MAX  |

| Contact Pitch            |             |      | 0.65 BSC |      |

| Contact Pad Spacing      | С           |      | 7.20     |      |

| Contact Pad Width (X20)  | X1          |      |          | 0.45 |

| Contact Pad Length (X20) | Y1          |      |          | 1.75 |

| Distance Between Pads    | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A

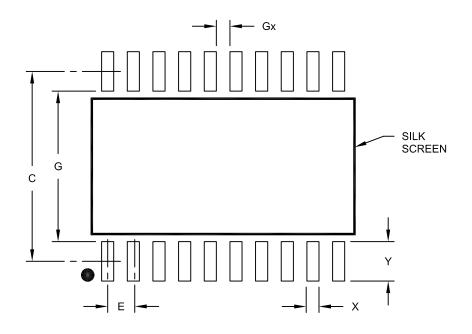

20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

| Units                    |    | MILLIMETERS |      |      |  |

|--------------------------|----|-------------|------|------|--|

| Dimension Limits         |    | MIN         | NOM  | MAX  |  |

| Contact Pitch            |    | 1.27 BSC    |      |      |  |

| Contact Pad Spacing      | С  |             | 9.40 |      |  |

| Contact Pad Width (X20)  | X  |             |      | 0.60 |  |

| Contact Pad Length (X20) | Y  |             |      | 1.95 |  |

| Distance Between Pads    | Gx | 0.67        |      |      |  |

| Distance Between Pads    | G  | 7.45        |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2094A

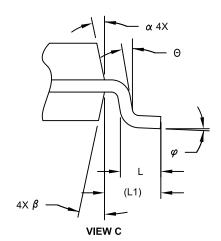

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |

|--------------------------|-------------|-----------|-----|------|--|

| Dimension                | Limits      | MIN       | NOM | MAX  |  |

| Number of Pins           | N           | 28        |     |      |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |

| Overall Height           | A           | -         | -   | 2.65 |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |

| Overall Length           | D           | 17.90 BSC |     |      |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |

| Foot Angle               | φ           | 0°        | -   | 8°   |  |

| Lead Thickness           | С           | 0.18      | -   | 0.33 |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

#### TABLE 25-1: MAJOR SECTION UPDATES

| Section Name                                                | Update Description                                                                                                                             |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 9.0 "I/O Ports"                                     | Added paragraph and Table 9-1 to <b>Section 9.1.1 "Open-Drain Configuration</b> ", which provides details on I/O pins and their functionality. |

|                                                             | Removed the following sections, which are now available in the related section of the dsPIC33F Family Reference Manual:                        |

|                                                             | 9.4.2 "Available Peripherals"                                                                                                                  |

|                                                             | • 9.4.3.3 "Mapping"                                                                                                                            |

|                                                             | 9.4.5 "Considerations for Peripheral Pin Selection"                                                                                            |

| Section 13.0 "Output Compare"                               | Replaced sections 13.1, 13.2, and 13.3 and related figures and tables with entirely new content.                                               |

| Section 14.0 "Motor Control<br>PWM Module"                  | Removed the following sections, which are now available in the related section of the dsPIC33F Family Reference Manual:                        |

|                                                             | <ul> <li>14.3 "PWM Time Base</li> <li>14.4 "PWM Period"</li> </ul>                                                                             |

|                                                             | <ul> <li>14.4 FWW Fenda</li> <li>14.5 "Edge-Aligned PWM"</li> </ul>                                                                            |

|                                                             | <ul> <li>14.5 Edge-Alighed PWM</li> <li>14.6 "Center-Aligned PWM"</li> </ul>                                                                   |

|                                                             | <ul> <li>14.7 "PWM Duty Cycle Comparison Units"</li> </ul>                                                                                     |

|                                                             | <ul> <li>14.8 "Complementary PWM Operation"</li> </ul>                                                                                         |

|                                                             | 14.9 "Dead-Time Generators"                                                                                                                    |

|                                                             | 14.10 "Independent PWM Output"                                                                                                                 |

|                                                             | 14.11 "Single Pulse PWM Operation"                                                                                                             |

|                                                             | 14.12 "PWM Output Override"                                                                                                                    |

|                                                             | <ul> <li>14.13 "PWM Output and Polarity Control</li> </ul>                                                                                     |

|                                                             | 14.14 "PWM Fault Pins"                                                                                                                         |

|                                                             | 14.15 "PWM Update Lockout"                                                                                                                     |

|                                                             | <ul> <li>14.16 "PWM Special Event Trigger"</li> </ul>                                                                                          |

|                                                             | <ul> <li>14.17 "PWM Operation During CPU Sleep Mode"</li> </ul>                                                                                |

|                                                             | 14.18 "PWM Operation During CPU Idle Mode                                                                                                      |

| Section 15.0 "Quadrature<br>Encoder Interface (QEI) Module" | Removed the following sections, which are now available in the related section of the dsPIC33F Family Reference Manual:                        |

|                                                             | <ul> <li>15.1 "Quadrature Encoder Interface Logic"</li> </ul>                                                                                  |

|                                                             | 15.2 "16-bit Up/Down Position Counter Mode"                                                                                                    |

|                                                             | 15.3 "Position Measurement Mode"                                                                                                               |

|                                                             | 15.4 "Programmable Digital Noise Filters"                                                                                                      |

|                                                             | 15.5 "Alternate 16-bit Timer/Counter"                                                                                                          |

|                                                             | 15.6 QEI Module Operation During CPU Sleep Mode"                                                                                               |

|                                                             | 15.7 "QEI Module Operation During CPU Idle Mode"                                                                                               |

|                                                             | 15.8 "Quadrature Encoder Interface Interrupts"                                                                                                 |

| Section 16.0 "Serial Peripheral<br>Interface (SPI)"         | Removed the following sections, which are now available in the related section of the dsPIC33F Family Reference Manual:                        |

|                                                             | • 16.1 "Interrupts"                                                                                                                            |

|                                                             | • 16.2 "Receive Operations"                                                                                                                    |

|                                                             | 16.3 "Transmit Operations"                                                                                                                     |

|                                                             | • 16.4 "SPI Setup: Master Mode"                                                                                                                |

|                                                             | <ul> <li>16.5 "SPI Setup: Slave Mode" (retained Figure 16-1: SPI Module Block<br/>Diagram)</li> </ul>                                          |

## dsPIC33FJ12MC201/202

NOTES:

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3180 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung Tel: 886-7-213-7830 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

05/02/11