Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

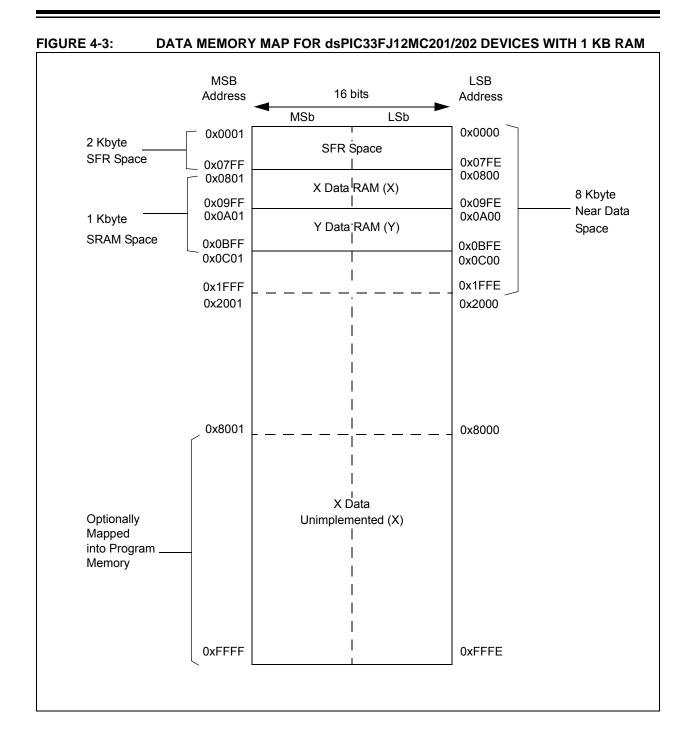

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc202-e-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

DS70265E-page 34

TABLE 4-15: ADC1 REGISTER MAP FOR dsPIC33FJ12MC202

| File Name | Addr | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9 | Bit 8    | Bit 7       | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|------|--------|-------------------|--------|--------|--------|----------|-------|----------|-------------|-----------|-------|-------|--------|----------|---------|---------|---------------|

| ADC1BUF0  | 0300 |        |                   |        |        |        |          |       | ADC Dat  | ta Buffer 0 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF1  | 0302 |        |                   |        |        |        |          |       | ADC Dat  | ta Buffer 1 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF2  | 0304 |        |                   |        |        |        |          |       | ADC Dat  | ta Buffer 2 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF3  | 0306 |        | ADC Data Buffer 3 |        |        |        |          |       |          |             |           |       |       | xxxx   |          |         |         |               |

| ADC1BUF4  | 0308 |        | ADC Data Buffer 4 |        |        |        |          |       |          |             |           |       | xxxx  |        |          |         |         |               |

| ADC1BUF5  | 030A |        |                   |        |        |        |          |       | ADC Dat  | ta Buffer 5 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF6  | 030C |        |                   |        |        |        |          |       | ADC Dat  | ta Buffer 6 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF7  | 030E |        |                   |        |        |        |          |       | ADC Dat  | ta Buffer 7 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF8  | 0310 |        |                   |        |        |        |          |       | ADC Dat  | ta Buffer 8 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF9  | 0312 |        |                   |        |        |        |          |       | ADC Dat  | ta Buffer 9 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFA  | 0314 |        |                   |        |        |        |          |       | ADC Data | a Buffer 10 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFB  | 0316 |        |                   |        |        |        |          |       | ADC Data | a Buffer 11 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFC  | 0318 |        |                   |        |        |        |          |       | ADC Data | a Buffer 12 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFD  | 031A |        |                   |        |        |        |          |       | ADC Data | a Buffer 13 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFE  | 031C |        |                   |        |        |        |          |       | ADC Data | a Buffer 14 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFF  | 031E |        |                   |        |        |        |          |       | ADC Data | a Buffer 15 |           |       |       |        |          |         |         | xxxx          |

| AD1CON1   | 0320 | ADON   | _                 | ADSIDL | -      | _      | AD12B    | FOR   | M<1:0>   | ;           | SSRC<2:0> | >     | _     | SIMSAM | ASAM     | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322 | ,      | VCFG<2:0          | >      | _      | _      | CSCNA    | CHP   | S<1:0>   | BUFS        | _         |       | SMP   | l<3:0> |          | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | _                 | _      |        |        | SAMC<4:0 | >     | _        |             |           |       | ADCS  | S<7:0> |          |         |         | 0000          |

| AD1CHS123 | 0326 | _      |                   | _      | _      | _      | CH123N   |       | CH123SB  | _           | _         | _     | _     | _      | CH123N   | NA<1:0> | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  |                   | _      |        | С      | H0SB<4:0 | >     |          | CH0NA       |           | _     |       | _      | H0SA<4:0 |         | Г       | 0000          |

| AD1PCFGL  | 032C | _      |                   | _      |        | _      |          |       | _        |             |           | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1   | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      | _                 | _      |        | _      | _        | _     | _        | _           | _         | CSS5  | CSS4  | CSS3   | CSS2     | CSS1    | CSS0    | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10     | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|------------|-------|-------|-------|-------|-------|-------|-------|------------|-------|-------|---------------|

| RPINR0       | 0680 | _      | _      | _      |        | ı      | NT1R<4:0>  |       |       | _     | _     | _     | _     | _     | _          | _     | _     | 1F00          |

| RPINR1       | 0682 | _      | _      | -      | _      | _      | _          | _     | _     | _     | _     | _     |       | ı     | NT2R<4:0>  |       |       | 001F          |

| RPINR3       | 0686 | _      | _      | -      |        | Т      | 3CKR<4:0>  |       |       | _     | _     | _     |       | Т     | 2CKR<4:0>  |       |       | 1F1F          |

| RPINR7       | 068E | -      | _      | 1      |        |        | IC2R<4:0>  |       |       | _     | _     | _     |       |       | IC1R<4:0>  |       |       | 1F1F          |

| RPINR10      | 0694 | _      | _      | _      |        |        | IC8R<4:0>  |       |       | _     | _     | _     |       |       | IC7R<4:0>  |       |       | 1F1F          |

| RPINR11      | 0696 | _      | _      | _      | _      | _      | _          | _     | _     | _     | _     | _     |       | C     | )CFAR<4:0> | •     |       | 001F          |

| RPINR12      | 0698 | _      | _      | _      | _      | _      | _          | _     | _     | _     | _     | _     |       | F     | LTA1R<4:0> | •     |       | 001F          |

| RPINR13      | 069A | _      | _      | _      | _      | _      | _          | _     | _     | _     | _     | _     |       | F     | LTA2R<4:0> | •     |       | 001F          |

| RPINR14      | 069C | -      | _      | 1      |        | C      | QEB1R<4:0> |       |       | _     | _     | _     |       | G     | QEA1R<4:0> | ,     |       | 1F1F          |

| RPINR15      | 069E | _      | _      | _      | _      | _      | _          | _     | _     | _     | _     | _     |       | 11    | NDX1R<4:0> | >     |       | 001F          |

| RPINR18      | 06A4 | -      | _      | 1      |        | U      | 1CTSR<4:0> | •     |       | _     | _     | _     |       | L     | J1RXR<4:0> | ,     |       | 1F1F          |

| RPINR20      | 06A8 | _      | _      | _      |        | S      | SCK1R<4:0> |       |       | _     | _     | _     |       | Ç     | SDI1R<4:0> |       |       | 1F1F          |

| RPINR21      | 06AA | _      | _      | _      | _      | _      | _          | _     | _     | _     | -     | -     |       | ;     | SS1R<4:0>  |       |       | 001F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ12MC202

| .,           |      |        | —      | •      |        | ••••   |           |       | •     |       | ·· • · <b>-</b> · · | <b></b> |       |       |            |       |       |               |

|--------------|------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|---------------------|---------|-------|-------|------------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6               | Bit 5   | Bit 4 | Bit 3 | Bit 2      | Bit 1 | Bit 0 | AII<br>Resets |

| RPOR0        | 06C0 | _      | _      | _      |        |        | RP1R<4:0> |       |       | _     | _                   | _       |       |       | RP0R<4:0>  |       |       | 0000          |

| RPOR1        | 06C2 | _      | _      | _      |        |        | RP3R<4:0> | •     |       | _     | _                   | _       |       |       | RP2R<4:0>  |       |       | 0000          |

| RPOR2        | 06C4 | _      | _      | _      |        |        | RP5R<4:0> | •     |       | _     | _                   | _       |       |       | RP4R<4:0>  |       |       | 0000          |

| RPOR3        | 06C6 | _      | _      | _      |        |        | RP7R<4:0> | •     |       | _     | _                   | _       |       |       | RP6R<4:0>  |       |       | 0000          |

| RPOR4        | 06C8 | _      | _      | _      |        |        | RP9R<4:0> | •     |       | _     | _                   | _       |       |       | RP8R<4:0>  |       |       | 0000          |

| RPOR5        | 06CA | _      | _      | _      |        |        | RP11R<4:0 | >     |       | _     | _                   | _       |       |       | RP10R<4:0> |       |       | 0000          |

| RPOR6        | 06CC | _      | _      | _      |        |        | RP13R<4:0 | >     | •     | _     | _                   | _       |       |       | RP12R<4:0> |       |       | 0000          |

| RPOR7        | 06CE |        | _      | _      |        |        | RP15R<4:0 | >     |       | _     | _                   | _       |       |       | RP14R<4:0> |       |       | 0000          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

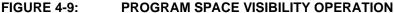

# 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL and TBLRDH).

Program space access through the data space occurs if the MSb of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 0x8000 and higher maps directly into a corresponding program memory address (see Figure 4-9), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

**Note:** PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| _      | _   | INT2IF | _   | _   | _   | _   | _     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | U-0 | R/W-0  | R/W-0 | U-0 | R/W-0   | R/W-0   |

|-------|-------|-----|--------|-------|-----|---------|---------|

| IC8IF | IC7IF | _   | INT1IF | CNIF  | _   | MI2C1IF | SI2C1IF |

| bit 7 |       |     |        |       |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 INT2IF: External Interrupt 2 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 12-8 **Unimplemented:** Read as '0'

bit 7 IC8IF: Input Capture Channel 8 Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 6 IC7IF: Input Capture Channel 7 Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 5 **Unimplemented:** Read as '0'

bit 4 INT1IF: External Interrupt 1 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 3 CNIF: Input Change Notification Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 2 Unimplemented: Read as '0'

bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

### REGISTER 7-15: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0    | R/W-1 | R/W-0       | R/W-0 | U-0 | R/W-1 | R/W-0       | R/W-0 |

|--------|-------|-------------|-------|-----|-------|-------------|-------|

| _      |       | U1RXIP<2:0> |       | _   |       | SPI1IP<2:0> |       |

| bit 15 |       |             |       |     |       |             | bit 8 |

| U-0   | R/W-1 | R/W-0        | R/W-0 | U-0 | R/W-1 | R/W-0     | R/W-0 |

|-------|-------|--------------|-------|-----|-------|-----------|-------|

| _     |       | SPI1EIP<2:0> |       | _   |       | T3IP<2:0> |       |

| bit 7 |       |              |       |     |       |           | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 U1RXIP<2:0>: UART1 Receiver Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 **SPI1IP<2:0>:** SPI1 Event Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 SPI1EIP<2:0>: SPI1 Error Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 T3IP<2:0>: Timer3 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

### 8.1 CPU Clocking System

The dsPIC33FJ12MC201/202 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- · FRC Oscillator with PLL

- · Primary (XT, HS or EC) Oscillator

- · Primary Oscillator with PLL

- · Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- · FRC Oscillator with postscaler

### 8.1.1 SYSTEM CLOCK SOURCES

#### 8.1.1.1 Fast RC

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

### 8.1.1.2 Primary

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

### 8.1.1.3 Secondary

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

#### 8.1.1.4 Low-Power RC

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

#### 8.1.1.5 FRC

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase-Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 8.1.3** "PLL Configuration".

The FRC frequency depends on the FRC accuracy (see Table 24-18) and the value of the FRC Oscillator Tuning register (see Register 8-4).

### 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 21.1 "Configuration Bits" for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) Fosc is divided by 2 to generate the device instruction clock (FcY) and the peripheral clock time base (FP). FcY defines the operating speed of the device, and speeds up to 40 MHz are supported by the dsPIC33FJ12MC201/202 architecture.

Instruction execution speed or device operating frequency, Fcy, is given by:

# EQUATION 8-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

### REGISTER 10-1: RPINRO: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   |     |       |       | INT1R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | -   |     | _   |     | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 INT1R<4:0>: Assign External Interrupt 1 (INTR1) to the corresponding RPn pin

11111 = Input tied Vss 01111 = Input tied to RP15

:

00001 = Input tied to RP1 00000 = Input tied to RP0

bit 7-0 **Unimplemented:** Read as '0'

### **REGISTER 12-2: T3CON CONTROL REGISTER**

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(2)</sup> | _   | TSIDL <sup>(1)</sup> | _   | _   | _   | _   | _     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0 | R/W-0                | U-0 | U-0 | R/W-0              | U-0   |

|-------|----------------------|-------|----------------------|-----|-----|--------------------|-------|

| _     | TGATE <sup>(2)</sup> | TCKPS | <1:0> <sup>(2)</sup> | _   | _   | TCS <sup>(2)</sup> | _     |

| bit 7 |                      |       |                      |     |     |                    | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timer3 On bit<sup>(2)</sup>

1 = Starts 16-bit Timer3

0 = Stops 16-bit Timer3

bit 14 Unimplemented: Read as '0'

bit 13 **TSIDL:** Stop in Idle Mode bit<sup>(1)</sup>

1 = Discontinue timer operation when device enters Idle mode

0 = Continue timer operation in Idle mode

bit 12-7 **Unimplemented:** Read as '0'

bit 6 **TGATE:** Timer3 Gated Time Accumulation Enable bit<sup>(2)</sup>

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation enabled 0 = Gated time accumulation disabled

bit 5-4 TCKPS<1:0>: Timer3 Input Clock Prescale Select bits<sup>(2)</sup>

11 = 1:256 prescale value

10 = 1:64 prescale value

01 = 1:8 prescale value

00 = 1:1 prescale value

bit 3-2 **Unimplemented:** Read as '0'

bit 1 TCS: Timer3 Clock Source Select bit<sup>(2)</sup>

1 = External clock from T3CK pin

0 = Internal clock (Fosc/2)

bit 0 **Unimplemented:** Read as '0'

**Note 1:** When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (T2CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (T2CON<3>), these bits have no effect.

### REGISTER 15-5: PWMxCON1: PWM CONTROL REGISTER 1<sup>(2)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-------|-------|-------|

| _      | _   | _   | _   | _   | PMOD3 | PMOD2 | PMOD1 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | R/W-1                | R/W-1                | R/W-1                | U-0 | R/W-1                | R/W-1                | R/W-1                |

|-------|----------------------|----------------------|----------------------|-----|----------------------|----------------------|----------------------|

| _     | PEN3H <sup>(1)</sup> | PEN2H <sup>(1)</sup> | PEN1H <sup>(1)</sup> | _   | PEN3L <sup>(1)</sup> | PEN2L <sup>(1)</sup> | PEN1L <sup>(1)</sup> |

| bit 7 |                      |                      |                      |     |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10-8 PMOD4:PMOD1: PWM I/O Pair Mode bits

1 = PWM I/O pin pair is in the Independent PWM Output mode 0 = PWM I/O pin pair is in the Complementary Output mode

bit 7 **Unimplemented:** Read as '0'

bit 6-4 **PEN3H:PEN1H:** PWMxH I/O Enable bits<sup>(1)</sup>

1 = PWMxH pin is enabled for PWM output

0 = PWMxH pin disabled, I/O pin becomes general purpose I/O

bit 3 **Unimplemented:** Read as '0'

bit 2-0 **PEN3L:PEN1L:** PWMxL I/O Enable bits<sup>(1)</sup>

1 = PWMxL pin is enabled for PWM output

0 = PWMxL pin disabled, I/O pin becomes general purpose I/O

**Note 1:** Reset condition of the PENxH and PENxL bits depends on the value of the PWMPIN Configuration bit in the FPOR Configuration register.

2: PWM2 supports only one PWM I/O pin pair. PWM1 on dsPIC33FJ12MC201 devices supports only two PWM I/O pin pairs.

### REGISTER 17-2: SPIXCON1: SPIX CONTROL REGISTER 1

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|-----|-----|--------|--------|--------|-------|--------------------|

| _      | _   | _   | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0                |

|---------------------|-------|-------|--------------------------|-------|-------|-------|----------------------|

| SSEN <sup>(2)</sup> | CKP   | MSTEN | SPRE<2:0> <sup>(3)</sup> |       |       | PPRE< | <1:0> <sup>(3)</sup> |

| bit 7               |       |       |                          |       |       |       | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 **DISSCK:** Disable SCKx pin bit (SPI Master modes only)

1 = Internal SPI clock is disabled, pin functions as I/O

0 = Internal SPI clock is enabled

bit 11 **DISSDO:** Disable SDOx pin bit

1 = SDOx pin is not used by module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data sampled at end of data output time

0 = Input data sampled at middle of data output time

Slave mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (see bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (see bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)(2)

$1 = \overline{SSx}$  pin used for Slave mode

0 = SSx pin not used by module. Pin controlled by port function.

bit 6 **CKP:** Clock Polarity Select bit

1 = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

**Note 1:** The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

2: This bit must be cleared when FRMEN = 1.

3: Do not set both Primary and Secondary prescalers to a value of 1:1.

### REGISTER 20-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0  | U-0 | U-0 | R/W-0 | R/W-0     | R/W-0 |

|--------|-----|--------|-----|-----|-------|-----------|-------|

| ADON   | _   | ADSIDL | _   | _   | AD12B | FORM<1:0> |       |

| bit 15 |     |        |     |     |       |           | bit 8 |

| R/W-0 | R/W-0     | R/W-0 | U-0 | R/W-0  | R/W-0 | R/W-0<br>HC,HS | R/C-0<br>HC, HS |

|-------|-----------|-------|-----|--------|-------|----------------|-----------------|

|       | SSRC<2:0> |       | _   | SIMSAM | ASAM  | SAMP           | DONE            |

| bit 7 |           |       |     |        |       |                | bit 0           |

| Legend: HC = Cleared by hardware |                  | HS = Set by hardware                            |                    |  |  |

|----------------------------------|------------------|-------------------------------------------------|--------------------|--|--|

| R = Readable bit                 | W = Writable bit | Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |

bit 15 ADON: ADC Operating Mode bit

1 = ADC module is operating

0 = ADC is off

bit 14 **Unimplemented:** Read as '0' bit 13 **ADSIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-11 Unimplemented: Read as '0'

bit 10 AD12B: 10-bit or 12-bit Operation Mode bit

1 = 12-bit, 1-channel ADC operation0 = 10-bit, 4-channel ADC operation

bit 9-8 **FORM<1:0>:** Data Output Format bits

For 10-bit operation:

11 = Signed fractional (Dout = sddd dddd dd00 0000, where s = .NOT.d<9>)

10 = Fractional (Dout = dddd dddd dd00 0000)

01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)

00 = Integer (Dout = 0000 00dd dddd dddd)

For 12-bit operation:

11 = Signed fractional (Dout = sddd dddd dddd 0000, where s = .NOT.d<11>)

10 = Fractional (Dout = dddd dddd dddd 0000)

01 = Signed Integer (Dout = ssss sddd dddd, where s = .NOT.d<11>)

00 = Integer (Dout = 0000 dddd dddd dddd)

bit 7-5 SSRC<2:0>: Sample Clock Source Select bits

111 = Internal counter ends sampling and starts conversion (auto-convert)

110 = Reserved

101 = Motor Control PWM2 interval ends sampling and starts conversion

100 = Reserved

011 = Motor Control PWM1 interval ends sampling and starts conversion

010 = GP timer 3 compare ends sampling and starts conversion

001 = Active transition on INT0 pin ends sampling and starts conversion

000 = Clearing sample bit ends sampling and starts conversion

bit 4 **Unimplemented:** Read as '0'

bit 3 SIMSAM: Simultaneous Sample Select bit (applicable only when CHPS<1:0> = 01 or 1x)

When AD12B = 1, SIMSAM is: U-0, Unimplemented, Read as '0'

1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS<1:0> = 1x); or

Samples CH0 and CH1 simultaneously (when CHPS<1:0> = 01)

0 = Samples multiple channels individually in sequence

### REGISTER 20-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

| R/W-0  | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| CH0NB  | _   | _   |       |       | CH0SB<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| CH0NA | _   | _   |       |       | CH0SA<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CHONB: Channel 0 Negative Input Select for Sample B bit

1 = Channel 0 negative input is AN10 = Channel 0 negative input is VREF-

bit 14-13 Unimplemented: Read as '0'

bit 12-8 CH0SB<4:0>: Channel 0 Positive Input Select for Sample B bits

dsPIC33FJ12MC201 devices only:

00011 = Channel 0 positive input is AN3

00010 = Channel 0 positive input is AN2

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

dsPIC33FJ12MC202 devices only:

00101 = Channel 0 positive input is AN5

00100 = Channel 0 positive input is AN4

00011 = Channel 0 positive input is AN3

00010 = Channel 0 positive input is AN2

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

bit 7 CHONA: Channel 0 Negative Input Select for Sample A bit

1 = Channel 0 negative input is AN1

0 = Channel 0 negative input is VREF-

bit 6-5 **Unimplemented:** Read as '0'

bit 4-0 CH0SA<4:0>: Channel 0 Positive Input Select for Sample A bits

dsPIC33FJ12MC201 devices only:

00011 = Channel 0 positive input is AN3

00010 = Channel 0 positive input is AN2

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

dsPIC33FJ12MC202 devices only:

00101 = Channel 0 positive input is AN5

00100 = Channel 0 positive input is AN4

00011 = Channel 0 positive input is AN3

00010 = Channel 0 positive input is AN2

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

### REGISTER 20-6: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW(1,2)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | CSS5  | CSS4  | CSS3  | CSS2  | CSS1  | CSS0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 CSS<5:0>: ADC Input Scan Selection bits

1 = Select ANx for input scan 0 = Skip ANx for input scan

**Note 1:** On devices without 6 analog inputs, all AD1CSSL bits can be selected by user application. However, inputs selected for scan without a corresponding input on device converts VREFL.

2: CSSx = ANx, where x = 0 through 5.

### REGISTER 20-7: AD1PCFGL: ADC1 PORT CONFIGURATION REGISTER LOW<sup>(1,2,3)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   |     | 1   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | PCFG5 | PCFG4 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 **PCFG<5:0>:** ADC Port Configuration Control bits

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss

0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

**Note 1:** On devices without 6 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

2: PCFGx = ANx, where x = 0 through 5.

**3:** PCFGx bits have no effect if the ADC module is disabled by setting ADxMD bit in the PMDx register. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

TABLE 24-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |           |                                                                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |                    |     |       |                         |  |

|--------------------|-----------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-------------------------|--|

| Param<br>No.       | Symbol    | Characteristic                                                            | Min                                                                                                                                                         | Typ <sup>(1)</sup> | Max | Units | Conditions              |  |

| Operati            | ng Voltag | e                                                                         |                                                                                                                                                             |                    |     |       |                         |  |

| DC10               | Supply V  | /oltage                                                                   |                                                                                                                                                             |                    |     |       |                         |  |

|                    | VDD       |                                                                           | 3.0                                                                                                                                                         | _                  | 3.6 | V     | Industrial and Extended |  |

| DC12               | VDR       | RAM Data Retention Voltage <sup>(2)</sup>                                 | 1.8                                                                                                                                                         | _                  | _   | V     | _                       |  |

| DC16               | VPOR      | VDD Start Voltage <sup>(3)</sup> to ensure internal Power-on Reset signal | _                                                                                                                                                           | _                  | Vss | V     | _                       |  |

| DC17               | SVDD      | VDD Rise Rate<br>to ensure internal<br>Power-on Reset signal              | 0.03                                                                                                                                                        | _                  | _   | V/ms  | 0-3.0V in 0.1s          |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**<sup>2:</sup>** This is the limit to which VDD may be lowered without losing RAM data.

<sup>3:</sup> VDD voltage must remain at Vss for a minimum of 200 µs to ensure POR.

TABLE 24-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

| DC CHARACTERISTICS |        |                                                                       | Standard Operating Conditions: 3.0V to 3.6V  (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |                    |                      |    |                                                                                                              |  |

|--------------------|--------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|----|--------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                        | Min                                                                                                                                                          | Typ <sup>(1)</sup> | Max Units Conditions |    |                                                                                                              |  |

| DI60a              | licl   | Input Low Injection Current                                           | 0                                                                                                                                                            | _                  | <sub>-5</sub> (5,8)  | mA | All pins except VDD, VSS, AVDD, AVSS, MCLR, VCAP, SOSCI, and SOSCO                                           |  |

| DI60b              | lich   | Input High Injection Current                                          | 0                                                                                                                                                            | _                  | +5(6,7,8)            | mA | All pins except VDD, VSS, AVDD, AVSS, MCLR, VCAP, SOSCI, SOSCO, and digital 5V-tolerant designated pins      |  |

| DI60c              | ∑lict  | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(9)</sup>                                                                                                                                           | _                  | +20(9)               | mA | Absolute instantaneous sum of all ± input injection currents from all I/O pins (   IICL +   IICH   ) ≤ ∑IICT |  |

- Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- 5: VIL source < (Vss 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

- 10: These parameters are characterized, but not tested.

**TABLE 24-26: INPUT CAPTURE TIMING REQUIREMENTS**

| AC CHARACTERISTICS |        |                     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |              |   |    |                                  |  |

|--------------------|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---|----|----------------------------------|--|

| Param<br>No.       | Symbol | Characte            | stic <sup>(1)</sup> Min Max Units Co                                                                                                                                                                                                              |              |   |    | Conditions                       |  |

| IC10               | TccL   | ICx Input Low Time  | No Prescaler                                                                                                                                                                                                                                      | 0.5 Tcy + 20 | _ | ns | _                                |  |

|                    |        |                     | With Prescaler                                                                                                                                                                                                                                    | 10           | 1 | ns |                                  |  |

| IC11               | TccH   | ICx Input High Time | No Prescaler                                                                                                                                                                                                                                      | 0.5 Tcy + 20 | _ | ns | _                                |  |

|                    |        |                     | With Prescaler                                                                                                                                                                                                                                    | 10           |   | ns |                                  |  |

| IC15               | TccP   | ICx Input Period    |                                                                                                                                                                                                                                                   | (Tcy + 40)/N | _ | ns | N = prescale<br>value (1, 4, 16) |  |

Note 1: These parameters are characterized by similarity, but are not tested in manufacturing.

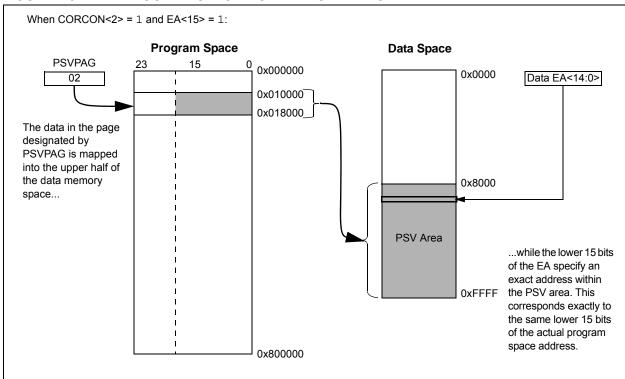

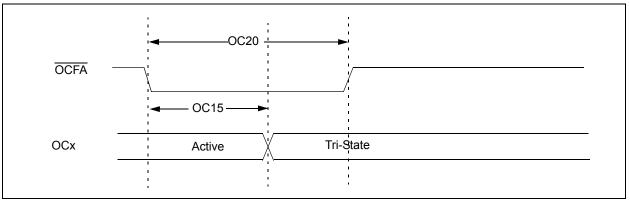

### FIGURE 24-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

TABLE 24-27: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |     |     |       |                    |  |

|--------------------|--------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min                                                                                                                                                                                                                                              | Тур | Max | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time          | _                                                                                                                                                                                                                                                | _   | _   | ns    | See parameter D032 |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                                                                                                                                                                                                                | _   | _   | ns    | See parameter D031 |  |

Note 1: These parameters are characterized by similarity, but are not tested in manufacturing.

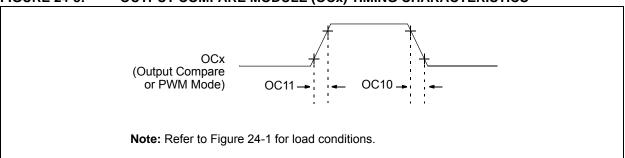

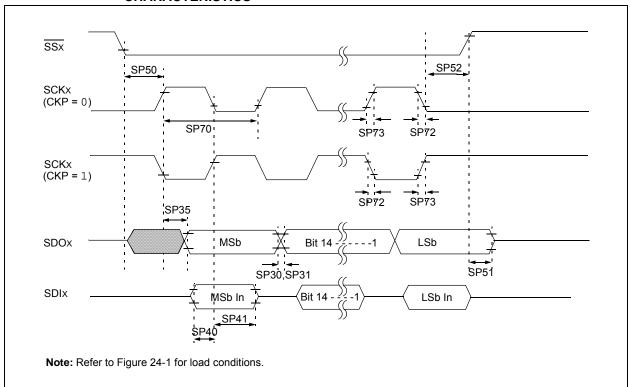

### FIGURE 24-9: OC/PWM MODULE TIMING CHARACTERISTICS

FIGURE 24-20: SPIX SLAVE MODE (FULL-DUPLEX CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

TABLE 24-46: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                      |           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |         |       |                                                           |  |  |

|--------------------|--------|----------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-----------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                                                       | Min.      | Typ <sup>(1)</sup>                                                                                                                                                                                                                                | Max.    | Units | Conditions                                                |  |  |

|                    |        | Clock                                                                | Paramet   | ers <sup>(2)</sup>                                                                                                                                                                                                                                |         |       |                                                           |  |  |

| AD50               | TAD    | ADC Clock Period                                                     | 76        |                                                                                                                                                                                                                                                   | _       | ns    | _                                                         |  |  |

| AD51               | trc    | ADC Internal RC Oscillator Period                                    | _         | 250                                                                                                                                                                                                                                               | _       | ns    | _                                                         |  |  |

|                    |        | Con                                                                  | version F | Rate                                                                                                                                                                                                                                              |         |       |                                                           |  |  |

| AD55               | tconv  | Conversion Time                                                      | _         | 12 TAD                                                                                                                                                                                                                                            | _       |       | _                                                         |  |  |

| AD56               | FCNV   | Throughput Rate                                                      | _         | _                                                                                                                                                                                                                                                 | 1.1     | Msps  | _                                                         |  |  |

| AD57               | TSAMP  | Sample Time                                                          | 2.0 TAD   |                                                                                                                                                                                                                                                   | _       |       | _                                                         |  |  |

|                    |        | Timin                                                                | g Param   | eters                                                                                                                                                                                                                                             |         |       |                                                           |  |  |

| AD60               | tPCS   | Conversion Start from Sample Trigger <sup>(1)</sup>                  | 2.0 TAD   | _                                                                                                                                                                                                                                                 | 3.0 TAD |       | Auto-Convert Trigger<br>(SSRC<2:0> = 111) not<br>selected |  |  |

| AD61               | tPSS   | Sample Start from Setting Sample (SAMP) bit <sup>(1)</sup>           | 2.0 TAD   | _                                                                                                                                                                                                                                                 | 3.0 TAD | _     | _                                                         |  |  |

| AD62               | tcss   | Conversion Completion to Sample Start (ASAM = 1) <sup>(1)</sup>      | _         | 0.5 TAD                                                                                                                                                                                                                                           | _       | _     | _                                                         |  |  |

| AD63               | tDPU   | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(1)</sup> |           | _                                                                                                                                                                                                                                                 | 20      | μs    | _                                                         |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

<sup>2:</sup> Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

### **Worldwide Sales and Service**

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3180 Fax: 86-571-2819-3189

China - Hong Kong SAR Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068 Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-213-7830 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90

Fax: 34-91-708-08-91 **UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

05/02/11