#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc202-e-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                   |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                 |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                                |

- Note 1: This bit can be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

## 3.6.3.1 Round Logic

The round logic is a combinational block that performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value that is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word (lsw) is simply discarded.

Conventional rounding will zero-extend bit 15 of the accumulator and will add it to the ACCxH word (bits 16 through 31 of the accumulator).

- If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented.

- If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged.

A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the Least Significant bit (LSb), bit 16 of the accumulator, of ACCxH is examined:

- If it is '1', ACCxH is incremented.

- If it is '0', ACCxH is not modified.

Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.6.3.2 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator writeback operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

## 3.6.3.2 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF.

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000.

The MSb of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

## 3.6.4 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts, in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 and 31 for right shifts, and between bit positions 0 and 16 for left shifts.

| <b>TABLE 4-15</b> : | ADC1 REGISTER MAP FOR dsPIC33FJ12MC202 |  |

|---------------------|----------------------------------------|--|

|---------------------|----------------------------------------|--|

| IADLE 4-1 | J. 7 |        | LOISIL            |        | FUR US | F 10331 | 0121010   | 202   |          |             |           |       |       |        |          |         |         |               |

|-----------|------|--------|-------------------|--------|--------|---------|-----------|-------|----------|-------------|-----------|-------|-------|--------|----------|---------|---------|---------------|

| File Name | Addr | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11  | Bit 10    | Bit 9 | Bit 8    | Bit 7       | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300 |        | ADC Data Buffer 0 |        |        |         |           |       |          |             |           |       | xxxx  |        |          |         |         |               |

| ADC1BUF1  | 0302 |        |                   |        |        |         |           |       | ADC Dat  | ta Buffer 1 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF2  | 0304 |        |                   |        |        |         |           |       | ADC Dat  | ta Buffer 2 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF3  | 0306 |        |                   |        |        |         |           |       | ADC Dat  | ta Buffer 3 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF4  | 0308 |        |                   |        |        |         |           |       | ADC Dat  | ta Buffer 4 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF5  | 030A |        |                   |        |        |         |           |       | ADC Dat  | ta Buffer 5 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF6  | 030C |        |                   |        |        |         |           |       | ADC Dat  | ta Buffer 6 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF7  | 030E |        |                   |        |        |         |           |       | ADC Dat  | ta Buffer 7 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF8  | 0310 |        |                   |        |        |         |           |       | ADC Dat  | ta Buffer 8 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF9  | 0312 |        |                   |        |        |         |           |       | ADC Dat  | ta Buffer 9 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFA  | 0314 |        |                   |        |        |         |           |       | ADC Data | a Buffer 10 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFB  | 0316 |        |                   |        |        |         |           |       | ADC Data | a Buffer 11 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFC  | 0318 |        |                   |        |        |         |           |       | ADC Data | a Buffer 12 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFD  | 031A |        |                   |        |        |         |           |       | ADC Data | a Buffer 13 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFE  | 031C |        |                   |        |        |         |           |       | ADC Data | a Buffer 14 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFF  | 031E |        |                   |        |        |         |           |       | ADC Data | a Buffer 15 |           |       |       |        |          |         |         | xxxx          |

| AD1CON1   | 0320 | ADON   | _                 | ADSIDL | _      | _       | AD12B     | FOR   | M<1:0>   | :           | SSRC<2:0> | >     | _     | SIMSAM | ASAM     | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322 |        | VCFG<2:0          | >      | _      | -       | CSCNA     | CHP   | S<1:0>   | BUFS        | —         |       | SMP   | <3:0>  |          | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | _                 | —      |        | 5       | SAMC<4:0> | >     |          |             |           |       | ADCS  | 6<7:0> |          |         |         | 0000          |

| AD1CHS123 | 0326 | —      | _                 | _      | —      | —       | CH123N    | -     | CH123SB  | —           | _         | _     | —     | —      |          | NA<1:0> | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _                 | _      |        | С       | CH0SB<4:0 | >     |          | CH0NA       | _         | _     |       |        | H0SA<4:0 |         |         | 0000          |

| AD1PCFGL  | 032C | —      |                   | —      |        |         | —         | —     |          | —           | —         | PCFG5 | PCFG4 | PCFG3  | PCFG2    |         | PCFG0   | 0000          |

| AD1CSSL   | 0330 | —      | —                 | —      | —      | —       | —         | —     | -        | —           | —         | CSS5  | CSS4  | CSS3   | CSS2     | CSS1    | CSS0    | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## dsPIC33FJ12MC201/202

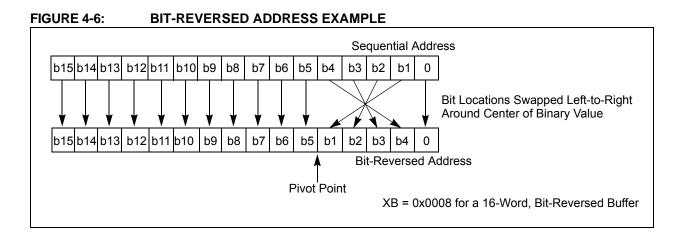

## TABLE 4-27: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

| INDEE | 4 67. |       | LIVE     |         |                      |    |    |    |         |  |  |

|-------|-------|-------|----------|---------|----------------------|----|----|----|---------|--|--|

|       |       | Norma | al Addre | SS      | Bit-Reversed Address |    |    |    |         |  |  |

| A3    | A2    | A1    | A0       | Decimal | A3                   | A2 | A1 | A0 | Decimal |  |  |

| 0     | 0     | 0     | 0        | 0       | 0                    | 0  | 0  | 0  | 0       |  |  |

| 0     | 0     | 0     | 1        | 1       | 1                    | 0  | 0  | 0  | 8       |  |  |

| 0     | 0     | 1     | 0        | 2       | 0                    | 1  | 0  | 0  | 4       |  |  |

| 0     | 0     | 1     | 1        | 3       | 1                    | 1  | 0  | 0  | 12      |  |  |

| 0     | 1     | 0     | 0        | 4       | 0                    | 0  | 1  | 0  | 2       |  |  |

| 0     | 1     | 0     | 1        | 5       | 1                    | 0  | 1  | 0  | 10      |  |  |

| 0     | 1     | 1     | 0        | 6       | 0                    | 1  | 1  | 0  | 6       |  |  |

| 0     | 1     | 1     | 1        | 7       | 1                    | 1  | 1  | 0  | 14      |  |  |

| 1     | 0     | 0     | 0        | 8       | 0                    | 0  | 0  | 1  | 1       |  |  |

| 1     | 0     | 0     | 1        | 9       | 1                    | 0  | 0  | 1  | 9       |  |  |

| 1     | 0     | 1     | 0        | 10      | 0                    | 1  | 0  | 1  | 5       |  |  |

| 1     | 0     | 1     | 1        | 11      | 1                    | 1  | 0  | 1  | 13      |  |  |

| 1     | 1     | 0     | 0        | 12      | 0                    | 0  | 1  | 1  | 3       |  |  |

| 1     | 1     | 0     | 1        | 13      | 1                    | 0  | 1  | 1  | 11      |  |  |

| 1     | 1     | 1     | 0        | 14      | 0                    | 1  | 1  | 1  | 7       |  |  |

| 1     | 1     | 1     | 1        | 15      | 1                    | 1  | 1  | 1  | 15      |  |  |

| R/W-0        | R-0                                                                 | U-0                                    | U-0             | U-0              | U-0              | U-0             | U-0    |  |  |  |

|--------------|---------------------------------------------------------------------|----------------------------------------|-----------------|------------------|------------------|-----------------|--------|--|--|--|

| ALTIVT       | DISI                                                                | _                                      |                 |                  |                  | _               |        |  |  |  |

| oit 15       | ·                                                                   |                                        |                 |                  |                  | ·               | bit 8  |  |  |  |

|              |                                                                     |                                        |                 |                  |                  |                 |        |  |  |  |

| U-0          | U-0                                                                 | U-0                                    | U-0             | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|              |                                                                     | _                                      |                 |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |

| bit 7        |                                                                     |                                        |                 |                  |                  |                 | bit (  |  |  |  |

|              |                                                                     |                                        |                 |                  |                  |                 |        |  |  |  |

| Legend:      | L- L-14                                                             |                                        | L 14            |                  |                  |                 |        |  |  |  |

| R = Readab   |                                                                     | W = Writable                           |                 |                  | mented bit, read |                 |        |  |  |  |

| -n = Value a | t POR                                                               | '1' = Bit is set                       |                 | '0' = Bit is cle | eared            | x = Bit is unkı | nown   |  |  |  |

| bit 15       |                                                                     |                                        | to muse \/o ata | r Tabla bit      |                  |                 |        |  |  |  |

|              |                                                                     | able Alternate In<br>ernate vector tab | •               |                  |                  |                 |        |  |  |  |

|              |                                                                     | ndard (default) v                      | -               |                  |                  |                 |        |  |  |  |

| bit 14       |                                                                     | Instruction Statu                      |                 |                  |                  |                 |        |  |  |  |

|              | 1 = DISI in                                                         | struction is active                    | е               |                  |                  |                 |        |  |  |  |

|              | 0 = DISI in                                                         | struction is not a                     | ctive           |                  |                  |                 |        |  |  |  |

| bit 13-3     | Unimpleme                                                           | ented: Read as '                       | 0'              |                  |                  |                 |        |  |  |  |

| bit 2        | INT2EP: Ex                                                          | ternal Interrupt 2                     | 2 Edge Detec    | t Polarity Selec | t bit            |                 |        |  |  |  |

|              |                                                                     | t on negative ed                       |                 |                  |                  |                 |        |  |  |  |

|              | •                                                                   | t on positive edg                      |                 |                  |                  |                 |        |  |  |  |

| bit 1        | <b>INT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit |                                        |                 |                  |                  |                 |        |  |  |  |

|              | 1 = Interrupt on negative edge<br>0 = Interrupt on positive edge    |                                        |                 |                  |                  |                 |        |  |  |  |

| bit 0        | •                                                                   |                                        |                 | t Dolority Soloo | st hit           |                 |        |  |  |  |

|              |                                                                     | ternal Interrupt C                     | •               |                  |                  |                 |        |  |  |  |

|              | 1 = Interrupt on negative edge<br>0 = Interrupt on positive edge    |                                        |                 |                  |                  |                 |        |  |  |  |

## REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# dsPIC33FJ12MC201/202

## TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                 | Oscillator<br>Source | POSCMD<1:0> | FNOSC<2:0> | Note |

|-------------------------------------------------|----------------------|-------------|------------|------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)   | Internal             | xx          | 111        | 1, 2 |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) | Internal             | xx          | 110        | 1    |

| Low-Power RC Oscillator (LPRC)                  | Internal             | xx          | 101        | 1    |

| Secondary (Timer1) Oscillator (SOSC)            | Secondary            | xx          | 100        | 1    |

| Primary Oscillator (HS) with PLL (HSPLL)        | Primary              | 10          | 011        | _    |

| Primary Oscillator (XT) with PLL (XTPLL)        | Primary              | 01          | 011        | _    |

| Primary Oscillator (EC) with PLL (ECPLL)        | Primary              | 00          | 011        | 1    |

| Primary Oscillator (HS)                         | Primary              | 10          | 010        | _    |

| Primary Oscillator (XT)                         | Primary              | 01          | 010        | —    |

| Primary Oscillator (EC)                         | Primary              | 00          | 010        | 1    |

| Fast RC Oscillator with PLL (FRCPLL)            | Internal             | xx          | 001        | 1    |

| Fast RC Oscillator (FRC)                        | Internal             | xx          | 000        | 1    |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

**2:** This is the default oscillator mode for an unprogrammed (erased) device.

| Input Name              | Function Name | Register | Configuration<br>Bits |

|-------------------------|---------------|----------|-----------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<4:0>            |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<4:0>            |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>            |

| Timer3 External Clock   | ТЗСК          | RPINR3   | T3CKR<4:0>            |

| Input Capture 1         | IC1           | RPINR7   | IC1R<4:0>             |

| Input Capture 2         | IC2           | RPINR7   | IC2R<4:0>             |

| Input Capture 7         | IC7           | RPINR10  | IC7R<4:0>             |

| Input Capture 8         | IC8           | RPINR10  | IC8R<4:0>             |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<4:0>            |

| PWM1 Fault              | FLTA1         | RPINR12  | FLTA1R<4:0>           |

| PWM2 Fault              | FLTA2         | RPINR13  | FLTA2R<4:0>           |

| QEI1 Phase A            | QEA           | RPINR14  | QEA1R<4:0>            |

| QEI1 Phase B            | QEB           | RPINR14  | QEB1R<4:0>            |

| QEI1 Index              | INDX          | RPINR15  | INDX1R<4:0>           |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>            |

| UART1 Clear To Send     | U1CTS         | RPINR18  | U1CTSR<4:0>           |

| SPI1 Data Input         | SDI1          | RPINR20  | SDI1R<4:0>            |

| SPI1 Clock Input        | SCK1          | RPINR20  | SCK1R<4:0>            |

| SPI1 Slave Select Input | SS1           | RPINR21  | SS1R<4:0>             |

## TABLE 10-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)<sup>(1)</sup>

Note 1: Unless otherwise noted, all inputs use the Schmitt input buffers.

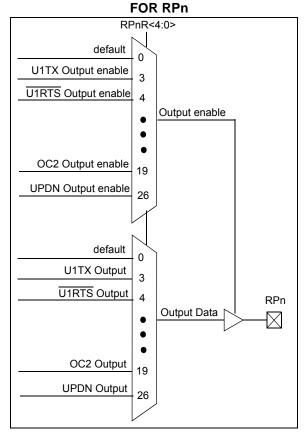

## 10.4.2.2 Output Mapping

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 5-bit fields, with each set associated with one RPn pin (see Register 10-14 through Register 10-21). The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 10-2 and Figure 10-3).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

## FIGURE 10-3:

### MULTIPLEXING OF REMAPPABLE OUTPUT

| U-0             | U-0                 | U-0              | R/W-1          | R/W-1                                   | R/W-1           | R/W-1  | R/W-1 |  |  |

|-----------------|---------------------|------------------|----------------|-----------------------------------------|-----------------|--------|-------|--|--|

|                 |                     | _                |                |                                         | INT1R<4:0>      |        |       |  |  |

| bit 15          |                     |                  |                |                                         |                 |        | bit 8 |  |  |

|                 |                     |                  |                |                                         |                 |        |       |  |  |

| U-0             | U-0                 | U-0              | U-0            | U-0                                     | U-0             | U-0    | U-0   |  |  |

| —               | _                   | —                | _              | —                                       | —               | _      | —     |  |  |

| bit 7           |                     |                  |                |                                         |                 |        | bit 0 |  |  |

|                 |                     |                  |                |                                         |                 |        |       |  |  |

| Legend:         |                     |                  |                |                                         |                 |        |       |  |  |

| R = Readable    | bit                 | W = Writable b   | oit            | U = Unimplemented bit, read as '0'      |                 |        |       |  |  |

| -n = Value at F | POR                 | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |                 |        |       |  |  |

|                 |                     |                  |                |                                         |                 |        |       |  |  |

| bit 15-13       | Unimplemen          | ted: Read as '0  | )'             |                                         |                 |        |       |  |  |

| bit 12-8        | INT1R<4:0>:         | Assign Externa   | al Interrupt 1 | (INTR1) to the                          | corresponding R | Pn pin |       |  |  |

|                 | 11111 <b>= Inpu</b> | t tied Vss       |                |                                         |                 |        |       |  |  |

|                 | 01111 <b>= Inpu</b> | t tied to RP15   |                |                                         |                 |        |       |  |  |

|                 |                     |                  |                |                                         |                 |        |       |  |  |

|                 | •                   |                  |                |                                         |                 |        |       |  |  |

|                 | •                   |                  |                |                                         |                 |        |       |  |  |

|                 | 00001 <b>= Inpu</b> |                  |                |                                         |                 |        |       |  |  |

|                 | 00000 <b>= Inpu</b> | t tied to RP0    |                |                                         |                 |        |       |  |  |

| bit 7-0         | Unimplemen          | ted: Read as '0  | )'             |                                         |                 |        |       |  |  |

## REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

#### REGISTER 10-16: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| -     -     -       bit 15       U-0       -       bit 7 | le bit U = Unimplemented bit, read as '0' |

|----------------------------------------------------------|-------------------------------------------|

| <br>bit 15                                               | bit                                       |

| <br>bit 15                                               | RP4R<4:0>                                 |

|                                                          | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0             |

|                                                          | bit                                       |

|                                                          |                                           |

| 00 00                                                    | RP5R<4:0>                                 |

| U-0 U-0 U-0                                              | R/W-0 R/W-0 R/W-0 R/W-0                   |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **RP5R<4:0>:** Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP4R<4:0>:** Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 10-2 for peripheral function numbers)

### REGISTER 10-17: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP7R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-----|-----------|-------|-------|-------|-------|--|

| —     | —   | —   | RP6R<4:0> |       |       |       |       |  |

| bit 7 |     |     |           |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **RP7R<4:0>:** Peripheral Output Function is Assigned to RP7 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP6R<4:0>:** Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 10-2 for peripheral function numbers)

## 12.0 TIMER2/3 FEATURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 feature has three 2-bit timers that can also be configured as two independent 16-bit timers with selectable operating modes.

As a 32-bit timer, the Timer2/3 feature permits operation in three modes:

- Two Independent 16-bit timers (e.g., Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer (Timer2/3)

- Single 32-bit synchronous counter (Timer2/3)

- The Timer2/3 feature also supports:

- Timer gate operation

- Selectable prescaler settings

- Timer operation during Idle and Sleep modes

- · Interrupt on a 32-bit period register match

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC1 event trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON registers. T2CON registers are shown in generic form in Register 12-1. T3CON registers are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 is the least significant word, and Timer3 is the msw of the 32-bit timers.

Note: For 32-bit operation, T3CON control bits are ignored. Only T2CON control bits are used for setup and control. Timer2 clock and gate inputs are used for the 32-bit timer modules, but an interrupt is generated with the Timer3 interrupt flags.

## 12.1 32-bit Operation

To configure the Timer2/3 feature timers for 32-bit operation:

- 1. Set the T32 control bit.

- Select the prescaler ratio for Timer2 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3 contains the msw of the value, while PR2 contains the least significant word.

- 5. If interrupts are required, set the interrupt enable bit, T3IE. Use the priority bits, T3IP<2:0>, to set the interrupt priority. While Timer2 controls the timer, the interrupt appears as a Timer3 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2, which always contains the msw of the count, while TMR2 contains the least significant word.

## 12.2 16-bit Operation

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

## 21.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*. Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

dsPIC33FJ12MC201/202 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- · In-Circuit emulation

## 21.1 Configuration Bits

dsPIC33FJ12MC201/202 devices provide nonvolatile memory implementation for device configuration bits. Refer to **Section 25. "Device Configuration"** (DS70194) of the *"dsPIC33F/PIC24H Family Reference Manual"*, for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 21-2.

Note that address 0xF80000 is beyond the user program memory space. It belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using table reads and table writes.

The Device Configuration register map is shown in Table 21-1.

| Address  | Name     | Bit 7               | Bit 6               | Bit 5   | Bit 4        | Bit 3        | Bit 2    | Bit 1    | Bit 0   |

|----------|----------|---------------------|---------------------|---------|--------------|--------------|----------|----------|---------|

| 0xF80000 | FBS      | —                   | —                   | _       | —            |              | BSS<2:0> |          | BWRP    |

| 0xF80002 | Reserved | —                   | —                   | —       | —            | -            | —        | —        | —       |

| 0xF80004 | FGS      | _                   |                     | _       | _            |              | GSS<1    | :0>      | GWRP    |

| 0xF80006 | FOSCSEL  | IESO                | _                   | _       | _            | – FNOSC<2:0> |          |          |         |

| 0xF80008 | FOSC     | FCKSM               | 1<1:0>              | IOL1WAY | —            | -            | OSCIOFNC | POSCN    | ID<1:0> |

| 0xF8000A | FWDT     | FWDTEN              | WINDIS              | —       | WDTPRE       |              | WDTPOST< | <3:0>    |         |

| 0xF8000C | FPOR     | PWMPIN              | HPOL                | LPOL    | ALTI2C       |              | FPW      | /RT<2:0> |         |

| 0xF8000E | FICD     | Reserv              | ved <sup>(1)</sup>  | JTAGEN  | —            | -            | —        | ICS<     | :1:0>   |

| 0xF80010 | FUID0    |                     |                     |         | User Unit ID | ) Byte 0     |          |          |         |

| 0xF80012 | FUID1    |                     | User Unit ID Byte 1 |         |              |              |          |          |         |

| 0xF80014 | FUID2    | User Unit ID Byte 2 |                     |         |              |              |          |          |         |

| 0xF80016 | FUID3    |                     | User Unit ID Byte 3 |         |              |              |          |          |         |

## TABLE 21-1: DEVICE CONFIGURATION REGISTER MAP

**Legend:** — = unimplemented bit, read as '0'.

Note 1: These bits are reserved for use by development tools and must be programmed as '1'.

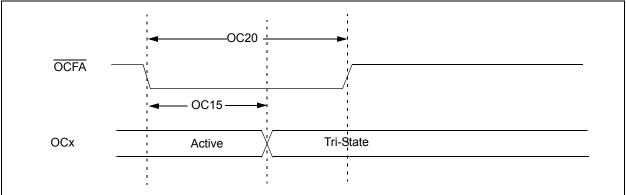

### TABLE 24-26: INPUT CAPTURE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                     | Standard Operation (unless otherwise)<br>Operating temper | <b>e stated)</b><br>ature   -40°C ≤T4 | <b>.0V to 3.6V</b><br>\≤+85°C fo<br>≤+125°C fo | r Industri |                                  |

|--------------------|--------|---------------------|-----------------------------------------------------------|---------------------------------------|------------------------------------------------|------------|----------------------------------|

| Param<br>No.       | Symbol | Characte            | ristic <sup>(1)</sup>                                     | Min                                   | Max                                            | Units      | Conditions                       |

| IC10               | TccL   | ICx Input Low Time  | No Prescaler                                              | 0.5 Tcy + 20                          |                                                | ns         | —                                |

|                    |        |                     | With Prescaler                                            | 10                                    | _                                              | ns         |                                  |

| IC11               | TccH   | ICx Input High Time | No Prescaler                                              | 0.5 Tcy + 20                          | —                                              | ns         | —                                |

|                    |        |                     | With Prescaler                                            | 10                                    | —                                              | ns         |                                  |

| IC15               | TccP   | ICx Input Period    |                                                           | (Tcy + 40)/N                          | _                                              | ns         | N = prescale<br>value (1, 4, 16) |

**Note 1:** These parameters are characterized by similarity, but are not tested in manufacturing.

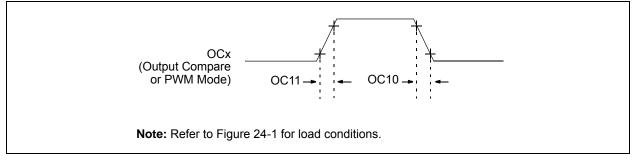

### FIGURE 24-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 24-27: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |     |     |       |                    |  |

|--------------------|--------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min                                                                                                                                                                                                      | Тур | Мах | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time          | —                                                                                                                                                                                                        | _   | _   | ns    | See parameter D032 |  |

| OC11               | TccR   | OCx Output Rise Time          | —                                                                                                                                                                                                        | _   | —   | ns    | See parameter D031 |  |

Note 1: These parameters are characterized by similarity, but are not tested in manufacturing.

## FIGURE 24-9: OC/PWM MODULE TIMING CHARACTERISTICS

© 2007-2011 Microchip Technology Inc.

|              |        |                                                    | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |                    |     |       |                                                         |

|--------------|--------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|---------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                      |                                                                                                                                                                                                          | Тур <sup>(2)</sup> | Max | Units | Conditions                                              |

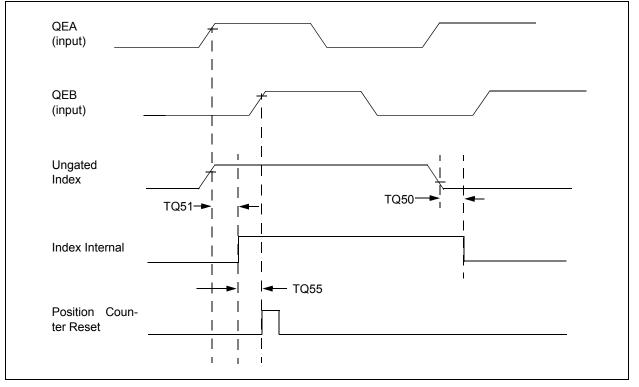

| TQ30         | TQUL   | Quadrature Input Low Time                          |                                                                                                                                                                                                          | 6 Tcy              |     | ns    | —                                                       |

| TQ31         | TQUH   | Quadrature Input High Time                         |                                                                                                                                                                                                          | 6 Tcy              | _   | ns    | —                                                       |

| TQ35         | TQUIN  | Quadrature Input Period                            |                                                                                                                                                                                                          | 12 TCY             | _   | ns    | —                                                       |

| TQ36         | ΤουΡ   | Quadrature Phase Period                            |                                                                                                                                                                                                          | 3 TCY              | —   | ns    | —                                                       |

| TQ40         | TQUFL  | Filter Time to Recognize Low, with Digital Filter  |                                                                                                                                                                                                          | 3 * N * Tcy        | —   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 3)</b> |

| TQ41         | TqufH  | Filter Time to Recognize High, with Digital Filter |                                                                                                                                                                                                          | 3 * N * Tcy        | _   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 3)</b> |

### TABLE 24-30: QUADRATURE DECODER TIMING REQUIREMENTS

**Note 1:** These parameters are characterized by similarity, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to **Section 15. "Quadrature Encoder** Interface (QEI)" (DS70208) in the *dsPIC33F/PIC24H Family Reference Manual*. Please see the Microchip (www.microchip.com) web site for the latest family reference manual chapters.

## FIGURE 24-13: QEI MODULE INDEX PULSE TIMING CHARACTERISTICS

## TABLE 24-36:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                                      |

|--------------------|-----------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                      | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70               | TscP                  | Maximum SCK Input Frequency                                  | —                                                                                                                                                                                        | _                  | 15  | MHz   | See Note 3                           |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                        |                    |     | ns    | See parameter DO32 and <b>Note 4</b> |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                                                                                                                                                                        | _                  | _   | ns    | See parameter DO31 and Note 4        |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                                                                                                                                                                        | _                  | —   | ns    | See parameter DO32 and Note 4        |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | —                                                                                                                                                                                        |                    | —   | ns    | See parameter DO31 and Note 4        |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                                                                                                                                                        | 6                  | 20  | ns    | —                                    |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                                                                                                                                                       | _                  | _   | ns    | —                                    |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                                                                                                                                                       | _                  |     | ns    | —                                    |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                                                                                                                                                       | _                  | _   | ns    | —                                    |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                      |                    | —   | ns    | _                                    |

| SP51               | TssH2doZ              | SSx                                                          | 10                                                                                                                                                                                       | _                  | 50  | ns    | _                                    |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                                                                                                                                                             | —                  | _   | ns    | See Note 4                           |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                     | —                                                                                                                                                                                        |                    | 50  | ns    | —                                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCK clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

## dsPIC33FJ12MC201/202

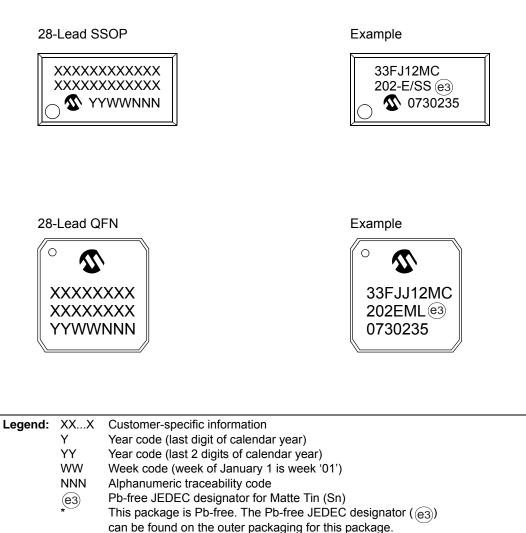

## 25.1 Package Marking Information (Continued)

**Note:** If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information.

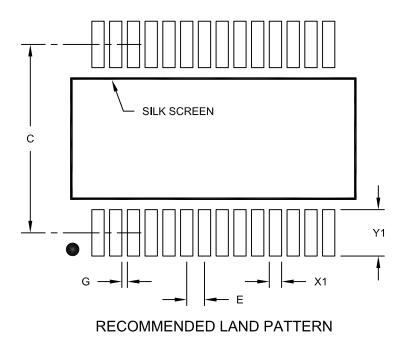

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Ν                | /ILLIMETER | S        |      |

|--------------------------|------------------|------------|----------|------|

| Dimension                | Dimension Limits |            |          | MAX  |

| Contact Pitch E          |                  |            | 0.65 BSC |      |

| Contact Pad Spacing      | С                |            | 7.20     |      |

| Contact Pad Width (X28)  | X1               |            |          | 0.45 |

| Contact Pad Length (X28) | Y1               |            |          | 1.75 |

| Distance Between Pads    | G                | 0.20       |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

## Revision C (June 2008)

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in the following table.

## TABLE 25-1: MAJOR SECTION UPDATES

| Section Name                                             | Update Description                                                                                                                                                          |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Digital Signal Controllers" | Added SSOP to list of available 28-pin packages (see " <b>Packaging:</b> " and Table 1).                                                                                    |

|                                                          | Added External Interrupts column to Remappable Peripherals in the Controller Families table and Note 2 (see Table 1).                                                       |

|                                                          | Added Note 1 to all pin diagrams, which references RPn pin usage by remappable peripherals (see " <b>Pin Diagrams</b> ").                                                   |

| Section 1.0 "Device Overview"                            | Changed Capture Input pin names from IC0-IC1 to IC1-IC2 and updated description for AVDD (see Table 1-1).                                                                   |

| Section 3.0 "Memory<br>Organization"                     | Added SFR definitions (ACCAL, ACCAH, ACCAU, ACCBL, ACCBH, and ACCBU) to the CPU Core Register Map (see Table 3-1).                                                          |

|                                                          | Updated Reset values for the following SFRs: IPC0, IPC2-IPC7, IPC16, and INTTREG (see Table 3-4).                                                                           |

|                                                          | Updated all SFR names in QEI1 Register Map (see Table 3-11).                                                                                                                |

|                                                          | The following changes were made to the ADC1 Register Maps:                                                                                                                  |

|                                                          | <ul> <li>Updated the bit range for AD1CON3 from ADCS&lt;5:0&gt; to ADCS&lt;7:0&gt;)<br/>(see Table 3-15 and Table 3-16).</li> </ul>                                         |

|                                                          | • Added Bit 6 (PCFG7) and Bit 7 (PCFG6) names to AD1PCFGL (Table 3-15).                                                                                                     |

|                                                          | Added Bit 6 (CSS7) and Bit 7 (CSS6) names to AD1CSSL (see Table 3-15).                                                                                                      |

|                                                          | • Changed Bit 5 and Bit 4 in AD1CSSL to unimplemented (see Table 3-15).                                                                                                     |

|                                                          | Updated the Reset value for CLKDIV in the System Control Register Map (see Table 3-23).                                                                                     |

| Section 4.0 "Flash Program<br>Memory"                    | Updated <b>Section 4.3 "Programming Operations"</b> with programming time formula.                                                                                          |

| Section 5.0 "Resets"                                     | Entire section was replaced to maintain consistency with other dsPIC33F data sheets.                                                                                        |

| Section 7.0 "Oscillator<br>Configuration"                | Removed the first sentence of the third clock source item (External Clock) in Section 7.1.1 "System Clock sources"                                                          |

|                                                          | Updated the default bit values for DOZE and FRCDIV in the Clock Divisor Register (see Register 7-2).                                                                        |

|                                                          | Added the center frequency in the OSCTUN register for the FRC Tuning bits (TUN<5:0>) value 011111 and updated the center frequency for bits value 011110 (see Register 7-4) |

| Section 8.0 "Power-Saving                                | Added the following three registers:                                                                                                                                        |

| Features"                                                | PMD1: Peripheral Module Disable Control Register 1                                                                                                                          |

|                                                          | PMD2: Peripheral Module Disable Control Register 2     PMD2: Peripheral Module Disable Control Register 2                                                                   |

|                                                          | PMD3: Peripheral Module Disable Control Register 3                                                                                                                          |

## TABLE 25-1: MAJOR SECTION UPDATES

| Section Name                                 | Update Description                                                                                                                                                                                                                      |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 23.0 "Electrical<br>Characteristics" | Updated Max MIPS value for -40°C to +125°C temperature range in Operating MIPS vs. Voltage (see Table 23-1).                                                                                                                            |

|                                              | Added 20-pin SOIC and 28-pin SSOP package information to Thermal Packaging Characteristics and updated Typical values for all devices (see Table 23-3).                                                                                 |

|                                              | Removed Typ value for parameter DC12 (see Table 23-4).                                                                                                                                                                                  |

|                                              | Updated Note 2 in Table 23-7: DC Characteristics: Power-Down Current (IPD).                                                                                                                                                             |

|                                              | Updated MIPS conditions for parameters DC24c, DC44c, DC72a, DC72f, and DC72g (see Table 23-5, Table 23-6, and Table 23-8).                                                                                                              |

|                                              | Added Note 4 (reference to new table containing digital-only and analog pin information to I/O Pin Input Specifications (see Table 23-9).                                                                                               |

|                                              | Updated Program Memory parameters (D136a, D136b, D137a, D137b, D138a, and D138b) and added Note 2 (see Table 23-12).                                                                                                                    |

|                                              | Updated Max value for Internal RC Accuracy parameter F21 for -40°C $\leq$ TA $\leq$ +125°C condition and added Note 2 (see Table 23-19).                                                                                                |

|                                              | Removed all values for Reset, Watchdog Timer, Oscillator Start-up Timer, and Power-up Timer parameter SY20 and updated conditions, which now refers to <b>Section 20.4 "Watchdog Timer (WDT)"</b> and LPRC parameter F21 (Table 23-21). |

|                                              | Updated Min value for Input Capture Timing Requirements parameter IC15 (see Table 23-26).                                                                                                                                               |

|                                              | The following changes were made to the ADC Module Specifications (Table 23-38):                                                                                                                                                         |

|                                              | Updated Min value for ADC Module Specification parameter AD07.                                                                                                                                                                          |

|                                              | Updated Typ value for parameter AD08                                                                                                                                                                                                    |

|                                              | <ul> <li>Added references to Note 1 for parameters AD12 and AD13</li> <li>Removed Note 2.</li> </ul>                                                                                                                                    |

|                                              | The following changes were made to the ADC Module Specifications (12-bit Mode) (Table 23-39):                                                                                                                                           |

|                                              | <ul> <li>Updated Min and Max values for both AD21a parameters (measurements<br/>with <i>internal</i> and <i>external</i> VREF+/VREF-).</li> </ul>                                                                                       |

|                                              | <ul> <li>Updated Min, Typ, and Max values for parameter AD24a.</li> <li>Updated Max value for parameter AD32a.</li> </ul>                                                                                                               |

|                                              | Removed Note 1.                                                                                                                                                                                                                         |

|                                              | <ul> <li>Removed VREFL from Conditions for parameters AD21a, AD22a, AD23a,<br/>and AD24a (measurements with <i>internal</i> VREF+/VREF-).</li> </ul>                                                                                    |

|                                              | The following changes were made to the ADC Module Specifications (10-bit Mode) (Table 23-40):                                                                                                                                           |

|                                              | <ul> <li>Updated Min and Max values for parameter AD21b (measurements with<br/>external VREF+/VREF-).</li> </ul>                                                                                                                        |

|                                              | <ul> <li>Removed ± symbol from Min, Typ, and Max values for parameters AD23b<br/>and AD24b (measurements with <i>internal</i> VREF+/VREF-).</li> </ul>                                                                                  |

|                                              | Updated Typ and Max values for parameter AD32b.     Demoved Nets 1                                                                                                                                                                      |

|                                              | <ul> <li>Removed Note 1.</li> <li>Removed VREFL from Conditions for parameters AD21a, AD22a, AD23a, and AD24a (measurements with <i>internal</i> VREF+/VREF-).</li> </ul>                                                               |

|                                              | Updated Min and Typ values for parameters AD60, AD61, AD62, and AD63 and removed Note 3 (see Table 23-41 and Table 23-42).                                                                                                              |

## TABLE 25-1: MAJOR SECTION UPDATES

| Section Name                            | Update Description                                             |

|-----------------------------------------|----------------------------------------------------------------|

| Section 24.0 "Packaging<br>Information" | Added 28-lead SSOP package marking information.                |

| "Product Identification System"         | Added Plastic Shrink Small Outline (SSOP) package information. |

## **Revision D (June 2009)**

This revision includes minor typographical and formatting changes throughout the data sheet text.

Global changes include:

- Changed all instances of OSCI to OSC1 and OSCO to OSC2

- Changed all instances of PGCx/EMUCx and PGDx/EMUDx (where x = 1, 2, or 3) to PGECx and PGEDx

Changed all instances of VDDCORE and VDDCORE/VCAP to VCAP/VDDCORE

All other major changes are referenced by their respective section in the following table.

#### TABLE 25-2: MAJOR SECTION UPDATES

| Section Name                                                                              | Update Description                                                                                                                                         |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit Digital Signal Controllers"                                     | Added Note 2 to the 28-Pin QFN-S and 44-Pin QFN pin diagrams, which references pin connections to Vss.                                                     |

| Section 2.0 "Guidelines for Getting<br>Started with 16-bit Digital Signal<br>Controllers" | Added new section to the data sheet that provides guidelines on getting started with 16-bit Digital Signal Controllers.                                    |

| Section 8.0 "Oscillator Configuration"                                                    | Updated the Oscillator System Diagram (see Figure 8-1).                                                                                                    |

|                                                                                           | Added Note 1 to the Oscillator Tuning (OSCTUN) register (see Register 8-4).                                                                                |