Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc202-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz <  $F_{IN}$  < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV, and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, MPLAB ICD 3, or MPLAB REAL ICE in-circuit emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in the register that correspond to the A/D pins that are initialized by MPLAB ICD 2, MPLAB ICD 3, or MPLAB REAL ICE in-circuit emulator, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 2, MPLAB ICD 3, or MPLAB REAL ICE in-circuit emulator is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternately, connect a 1k to 10k resistor between Vss and unused pins and drive the output to logic low.

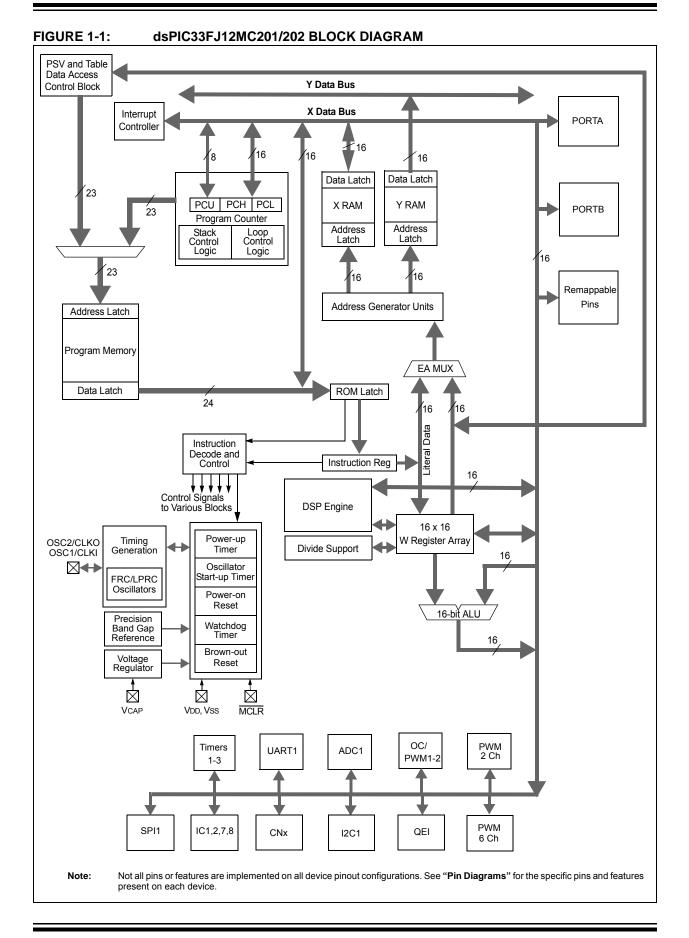

## 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ12MC201/202 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts, and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV), and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ12MC201/202 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

#### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.6 DSP Engine

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ12MC201/202 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB, and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed or unsigned DSP multiply (US)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACC-SAT)

A block diagram of the DSP engine is shown in Figure 3-3.

#### TABLE 3-1: DSP INSTRUCTIONS SUMMARY

| Instruction | Algebraic<br>Operation | ACC Write<br>Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

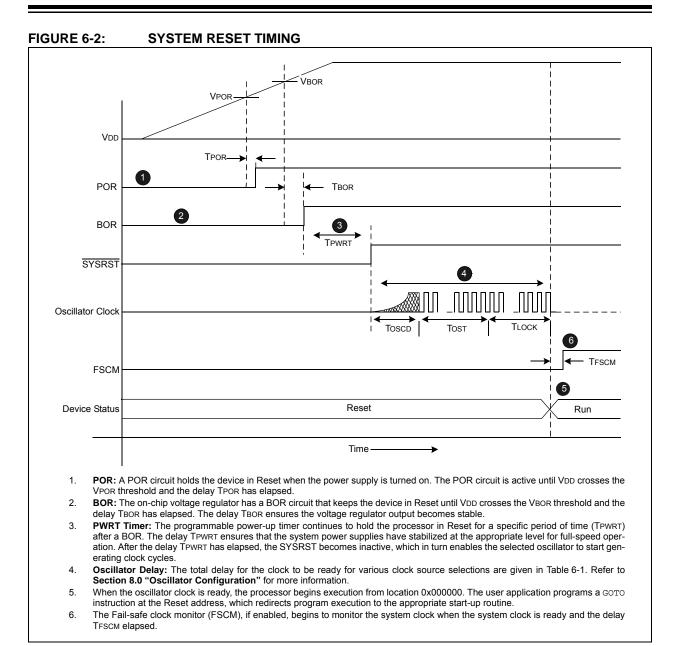

| TABLE 6-2: | <b>OSCILLATOR PARAMETERS</b> |

|------------|------------------------------|

|------------|------------------------------|

| Symbol | Parameter                           | Value            |

|--------|-------------------------------------|------------------|

| VPOR   | POR threshold                       | 1.8V nominal     |

| TPOR   | POR extension time                  | 30 μs maximum    |

| VBOR   | BOR threshold                       | 2.5V nominal     |

| TBOR   | BOR extension time                  | 100 μs maximum   |

| TPWRT  | Programmable<br>power-up time delay | 0-128 ms nominal |

| TFSCM  | Fail-safe Clock<br>Monitor Delay    | 900 μs maximum   |

| Note: | When the device exits the Reset condi-<br>tion (begins normal operation), the |

|-------|-------------------------------------------------------------------------------|

|       | device operating parameters (voltage,                                         |

|       | frequency, temperature, etc.) must be                                         |

|       | within their operating ranges, other-                                         |

|       | wise the device may not function cor-                                         |

|       | rectly. The user application must                                             |

|       | ensure that the delay between the time                                        |

|       | power is first applied, and the time                                          |

|       | SYSRST becomes inactive, is long                                              |

|       | enough to get all operating parameters within specification.                  |

|       |                                                                               |

### REGISTER 7-10: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| U-0             | U-0                               | R/W-0                              | U-0        | 11.0             | U-0             | 11.0            | 11.0    |  |

|-----------------|-----------------------------------|------------------------------------|------------|------------------|-----------------|-----------------|---------|--|

|                 |                                   |                                    | 0-0        | U-0              | 0-0             | U-0             | U-0     |  |

|                 |                                   | INT2IE                             | —          |                  | _               |                 |         |  |

| bit 15          |                                   |                                    |            |                  |                 |                 | bit 8   |  |

|                 |                                   |                                    |            |                  |                 |                 |         |  |

| R/W-0           | R/W-0                             | U-0                                | R/W-0      | R/W-0            | U-0             | R/W-0           | R/W-0   |  |

| IC8IE           | IC7IE                             | —                                  | INT1IE     | CNIE             | —               | MI2C1IE         | SI2C1IE |  |

| bit 7           |                                   |                                    |            |                  |                 |                 | bit 0   |  |

|                 |                                   |                                    |            |                  |                 |                 |         |  |

| Legend:         |                                   |                                    |            |                  |                 |                 |         |  |

| R = Readable I  | bit                               | W = Writable                       | bit        | U = Unimpler     | mented bit, rea | ad as '0'       |         |  |

| -n = Value at P | OR                                | '1' = Bit is set                   |            | '0' = Bit is cle | ared            | x = Bit is unkr | Iown    |  |

|                 |                                   |                                    |            |                  |                 |                 |         |  |

| bit 15-14       | -                                 | ted: Read as '                     |            |                  |                 |                 |         |  |

| bit 13          |                                   | rnal Interrupt 2                   |            |                  |                 |                 |         |  |

|                 |                                   | request enabled                    |            |                  |                 |                 |         |  |

| bit 12-8        | •                                 | request not ena                    |            |                  |                 |                 |         |  |

|                 | -                                 | ted: Read as '                     |            |                  |                 |                 |         |  |

| bit 7           | •                                 | Capture Channe                     |            | Enable bit       |                 |                 |         |  |

|                 |                                   | request enableo<br>request not ena |            |                  |                 |                 |         |  |

| bit 6           | -                                 | Capture Channe                     |            | Enable bit       |                 |                 |         |  |

|                 | -                                 | request enabled                    | -          |                  |                 |                 |         |  |

|                 | 0 = Interrupt i                   | request not ena                    | bled       |                  |                 |                 |         |  |

| bit 5           | Unimplemen                        | ted: Read as '                     | )'         |                  |                 |                 |         |  |

| bit 4           | INT1IE: Exter                     | rnal Interrupt 1                   | Enable bit |                  |                 |                 |         |  |

|                 |                                   | request enabled                    |            |                  |                 |                 |         |  |

|                 | •                                 | request not ena                    |            |                  |                 |                 |         |  |

| bit 3           |                                   | Change Notifica                    |            | Enable bit       |                 |                 |         |  |

|                 |                                   | request enabled                    |            |                  |                 |                 |         |  |

| <b>h</b> # 0    | 0 = Interrupt request not enabled |                                    |            |                  |                 |                 |         |  |

| bit 2           | •                                 | ted: Read as '                     |            |                  |                 |                 |         |  |

| bit 1           |                                   | 1 Master Even                      | •          | able bit         |                 |                 |         |  |

|                 |                                   | request enableo<br>request not ena |            |                  |                 |                 |         |  |

| bit 0           | -                                 | 1 Slave Events                     |            | hle hit          |                 |                 |         |  |

| Situ            |                                   | request enabled                    | •          |                  |                 |                 |         |  |

|                 |                                   | request not ena                    |            |                  |                 |                 |         |  |

|                 | ·                                 |                                    |            |                  |                 |                 |         |  |

### REGISTER 7-12: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0          | U-0             | U-0              | U-0           | U-0                                     | R/W-0            | R/W-0    | U-0   |  |

|--------------|-----------------|------------------|---------------|-----------------------------------------|------------------|----------|-------|--|

| _            | _               | _                | —             | _                                       | FLA2IE           | PWM2IE   | _     |  |

| bit 15       |                 |                  |               | ·                                       |                  | -        | bit 8 |  |

|              |                 |                  |               |                                         |                  |          |       |  |

| U-0          | U-0             | U-0              | U-0           | U-0                                     | U-0              | R/W-0    | U-0   |  |

| _            | _               | _                | —             | _                                       | _                | U1EIE    | _     |  |

| bit 7        | ·               |                  |               |                                         | ·                |          | bit 0 |  |

|              |                 |                  |               |                                         |                  |          |       |  |

| Legend:      |                 |                  |               |                                         |                  |          |       |  |

| R = Readab   | le bit          | W = Writable     | bit           | U = Unimplei                            | mented bit, read | d as '0' |       |  |

| -n = Value a | t POR           | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |

|              |                 |                  |               |                                         |                  |          |       |  |

| bit 15-11    | Unimplemen      | ted: Read as '   | 0'            |                                         |                  |          |       |  |

| bit 10       | FLA2IE: PWI     | M2 Fault A Inte  | rrupt Enable  | bit                                     |                  |          |       |  |

|              |                 | request enable   |               |                                         |                  |          |       |  |

|              | 0 = Interrupt I | request not ena  | abled         |                                         |                  |          |       |  |

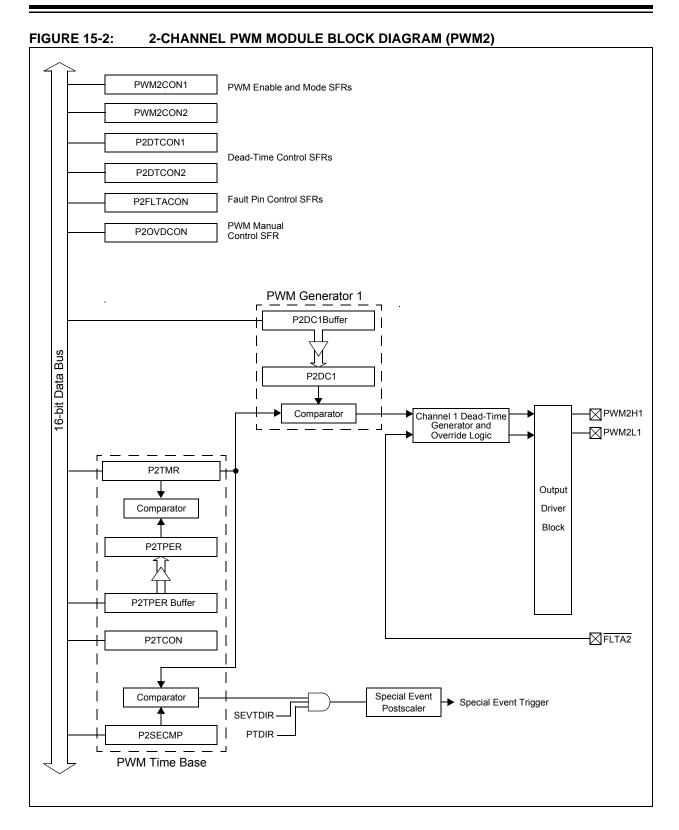

| bit 9        | PWM2IE: PW      | /M2 Error Inter  | rupt Enable b | it                                      |                  |          |       |  |

|              |                 | request enable   |               |                                         |                  |          |       |  |

|              | •               | request not ena  |               |                                         |                  |          |       |  |

| bit 8-2      | •               | ted: Read as '   |               |                                         |                  |          |       |  |

| bit 1        |                 | [1 Error Interru | •             |                                         |                  |          |       |  |

|              |                 | request enable   |               |                                         |                  |          |       |  |

|              | -               | request not ena  |               |                                         |                  |          |       |  |

| bit 0        | Unimplemen      | ted: Read as '   | 0'            |                                         |                  |          |       |  |

|              |                 |                  |               |                                         |                  |          |       |  |

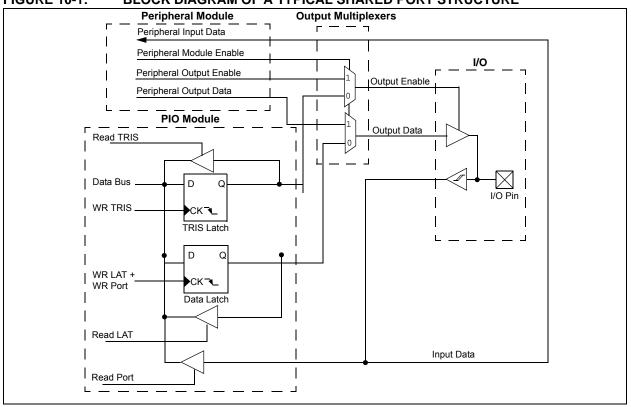

## 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 10.** "I/O Ports" (DS70193) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR, and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 10.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. This means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

© 2007-2011 Microchip Technology Inc.

| REGISTER 10-11: | <b>RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18</b> |

|-----------------|---------------------------------------------------------|

|-----------------|---------------------------------------------------------|

| U-0           | U-0                                     | U-0                               | R/W-1 | R/W-1             | R/W-1          | R/W-1           | R/W-1 |

|---------------|-----------------------------------------|-----------------------------------|-------|-------------------|----------------|-----------------|-------|

|               | _                                       | _                                 |       |                   | U1CTSR<4:(     | )>              |       |

| bit 15        |                                         |                                   |       |                   |                |                 | bit 8 |

| U-0           | U-0                                     | U-0                               | R/W-1 | R/W-1             | R/W-1          | R/W-1           | R/W-1 |

| _             |                                         | _                                 |       |                   | U1RXR<4:0      |                 |       |

| bit 7         |                                         |                                   |       |                   |                |                 | bit 0 |

| Legend:       |                                         |                                   |       |                   |                |                 |       |

| R = Readabl   | le bit                                  | W = Writable bi                   | it    | U = Unimplem      | ented bit, rea | id as '0'       |       |

| -n = Value at | t POR                                   | '1' = Bit is set                  |       | '0' = Bit is clea | red            | x = Bit is unkr | iown  |

|               | 11111 = Inpu<br>01111 = Inpu            | it tied to RP15<br>it tied to RP1 |       |                   |                |                 |       |

| bit 7-5       | •                                       | ted: Read as '0'                  |       |                   |                |                 |       |

| bit 4-0       | <b>U1RXR&lt;4:0&gt;</b><br>11111 = Inpu | : Assign UART1                    |       | IRX) to the corr  | esponding R    | Pn pin          |       |

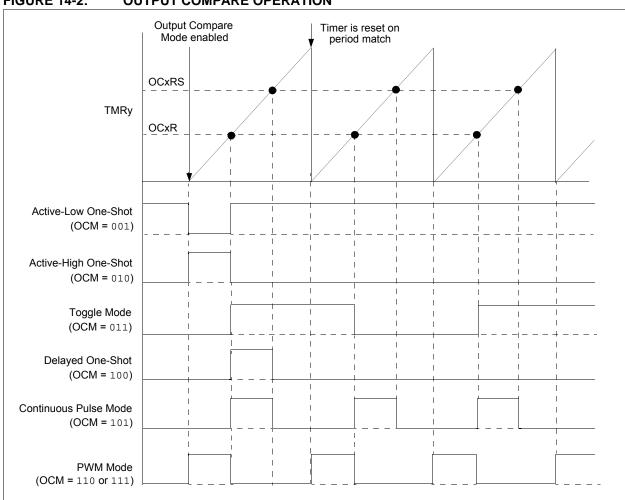

#### FIGURE 14-2: OUTPUT COMPARE OPERATION

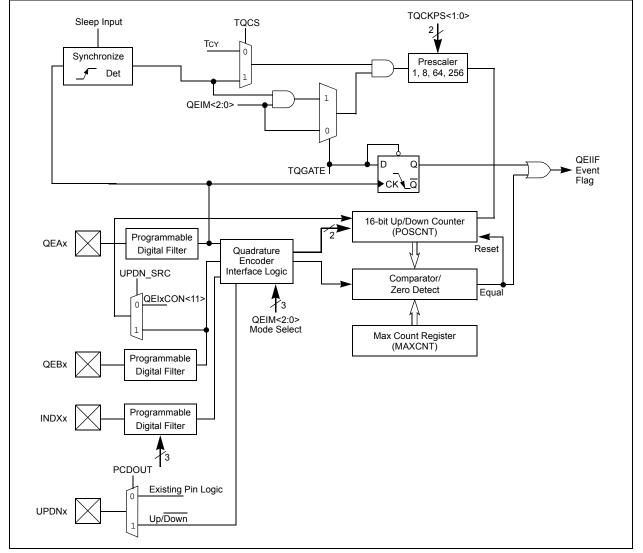

## 16.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Quadrature Encoder Interface (QEI)" (DS70208) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This section describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI include:

- Three input channels for two phase signals and index pulse

- 16-bit up/down position counter

- Count direction status

- Position Measurement (x2 and x4) mode

- · Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- Quadrature Encoder Interface interrupts

These operating modes are determined by setting the appropriate bits, QEIM<2:0> in (QEIxCON<10:8>). Figure 16-1 depicts the Quadrature Encoder Interface block diagram.

## 23.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 23.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 23.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 23.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 23.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

| DC CHARACTERISTICS |        |                                                                                | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |                |        |                        |

|--------------------|--------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|--------|------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                 | Min                                                                                                                                                                                      | Тур <sup>(1)</sup> | Max            | Units  | Conditions             |

|                    | VIL    | Input Low Voltage                                                              |                                                                                                                                                                                          |                    |                |        |                        |

| DI10               |        | I/O pins                                                                       | Vss                                                                                                                                                                                      | —                  | 0.2 Vdd        | V      |                        |

| DI15               |        | MCLR                                                                           | Vss                                                                                                                                                                                      | _                  | 0.2 VDD        | V      |                        |

| DI16               |        | I/O Pins with OSC1 or SOSCI                                                    | Vss                                                                                                                                                                                      | —                  | 0.2 VDD        | V      |                        |

| DI18               |        | SDA, SCL                                                                       | Vss                                                                                                                                                                                      | —                  | 0.3 VDD        | V      | SMBus disabled         |

| DI19               |        | SDA, SCL                                                                       | Vss                                                                                                                                                                                      | —                  | 0.8            | V      | SMBus enabled          |

|                    | Vih    | Input High Voltage <sup>(10)</sup>                                             |                                                                                                                                                                                          |                    |                |        |                        |

| DI20               |        | I/O Pins Not 5V Tolerant <sup>(4)</sup><br>I/O Pins 5V Tolerant <sup>(4)</sup> | 0.7 Vdd<br>0.7 Vdd                                                                                                                                                                       | —                  | Vdd<br>5.5     | V<br>V |                        |

| DI21               |        | I/O Pins SV Tolerant 7<br>I/O Pin with Schmitt Trigger<br>Input                | 0.7 VDD<br>0.7 VDD                                                                                                                                                                       | _                  | 5.5<br>0.8 Vdd | V<br>V |                        |

| DI25               |        | MCLR                                                                           | 0.8 Vdd                                                                                                                                                                                  | _                  | Vdd            | V      |                        |

| DI26               |        | OSC1 (in XT, HS, and LP<br>modes)                                              | 0.7 Vdd                                                                                                                                                                                  | —                  | Vdd            | V      |                        |

| DI27               |        | OSC1 (in RC mode)                                                              | 0.9 Vdd                                                                                                                                                                                  | _                  | Vdd            | V      |                        |

| DI28               |        | SDAx, SCLx                                                                     | 0.7 Vdd                                                                                                                                                                                  | —                  | Vdd            | V      | SMBus disabled         |

| DI29               |        | SDAx, SCLx                                                                     | 2.1                                                                                                                                                                                      | —                  | Vdd            | V      | SMBus enabled          |

|                    | ICNPU  | CNx Pull-up Current                                                            |                                                                                                                                                                                          |                    |                |        |                        |

| DI30               |        |                                                                                | 50                                                                                                                                                                                       | 250                | 400            | μA     | VDD = 3.3V, VPIN = VSS |

#### TABLE 24-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- **5:** VIL source < (Vss 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

- 10: These parameters are characterized, but not tested.

| DC CHA                             | DC CHARACTERISTICS |                                                                       |                    | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |                       |       |                                                                                                                                    |  |

|------------------------------------|--------------------|-----------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. Symbol Characteristic |                    |                                                                       | Min                | Typ <sup>(1)</sup>                                                                                                                                                                                       | Max                   | Units | Conditions                                                                                                                         |  |

| DI60a                              | licl               | Input Low Injection Current                                           | 0                  | _                                                                                                                                                                                                        | <sub>-5</sub> (5,8)   | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>and SOSCO                                                           |  |

| DI60b                              | Іісн               | Input High Injection Current                                          | 0                  | _                                                                                                                                                                                                        | +5 <sup>(6,7,8)</sup> | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, and digital 5V-tolerant<br>designated pins                   |  |

| DI60c                              | ∑lict              | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(9)</sup> | _                                                                                                                                                                                                        | +20 <sup>(9)</sup>    | mA    | Absolute instantaneous sum of<br>all $\pm$ input injection currents<br>from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |  |

#### TABLE 24-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- **5:** VIL source < (Vss 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

- **10:** These parameters are characterized, but not tested.

| DC CHARACTERISTICS |        |                                      | (unless | rd Opera<br>otherwi<br>ng tempe | ise state | onditions: 3.0V to 3.6V<br>ed)<br>-40°C ≤ TA ≤+85°C for Industrial<br>-40°C ≤TA ≤+125°C for Extended |                                                            |  |

|--------------------|--------|--------------------------------------|---------|---------------------------------|-----------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(3)</sup>        | Min     | Min Typ <sup>(1)</sup> Max      |           | Units                                                                                                | Conditions                                                 |  |

|                    |        | Program Flash Memory                 |         |                                 |           |                                                                                                      |                                                            |  |

| D130a              | Eр     | Cell Endurance                       | 10,000  | _                               | _         | E/W                                                                                                  | -40° C to +125° C                                          |  |

| D131               | Vpr    | VDD for Read                         | VMIN    | _                               | 3.6       | V                                                                                                    | VMIN = Minimum operating<br>voltage                        |  |

| D132B              | VPEW   | VDD for Self-Timed Write             | VMIN    | —                               | 3.6       | V                                                                                                    | VMIN = Minimum operating<br>voltage                        |  |

| D134               | TRETD  | Characteristic Retention             | 20      | —                               | —         | Year                                                                                                 | Provided no other specifications are violated              |  |

| D135               | IDDP   | Supply Current during<br>Programming | -       | 10                              | —         | mA                                                                                                   |                                                            |  |

| D136a              | Trw    | Row Write Time                       | 1.32    | —                               | 1.74      | ms                                                                                                   | Trw = 11064 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>   |  |

| D136b              | Trw    | Row Write Time                       | 1.28    | _                               | 1.79      | ms                                                                                                   | Trw = 11064 FRC cycles,<br>Ta = +125°C, See <b>Note 2</b>  |  |

| D137a              | Тре    | Page Erase Time                      | 20.1    | —                               | 26.5      | ms                                                                                                   | TPE = 168517 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>  |  |

| D137b              | TPE    | Page Erase Time                      | 19.5    | —                               | 27.3      | ms                                                                                                   | TPE = 168517 FRC cycles,<br>TA = +125°C, See <b>Note 2</b> |  |

| D138a              | Tww    | Word Write Cycle Time                | 42.3    | —                               | 55.9      | μs                                                                                                   | Tww = 355 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>     |  |

| D138b              | Tww    | Word Write Cycle Time                | 41.1    | —                               | 57.6      | μs                                                                                                   | Tww = 355 FRC cycles,<br>TA = +125°C, See <b>Note 2</b>    |  |

#### TABLE 24-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Other conditions: FRC = 7.37 MHz, TUN<5:0> = b'011111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 24-18) and the value of the FRC Oscillator Tuning register (see Register 8-4). For complete details on calculating the Minimum and Maximum time see Section 5.3 "Programming Operations".

3: These parameters are ensured by design, but are not characterized or tested in manufacturing.

#### TABLE 24-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                                                          |

|--------------------|--------|---------------------------------------------------|------------------------------------------------------|-----|-----|-------|----------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristics                                   | Min                                                  | Тур | Max | Units | Comments                                                 |

|                    | Cefc   | External Filter Capacitor<br>Value <sup>(1)</sup> | 4.7                                                  | 10  | _   | μF    | Capacitor must be low<br>series resistance<br>(< 5 ohms) |

**Note 1:** Typical VCAP pin voltage = 2.5V when VDD  $\geq$  VDDMIN.

NOTES:

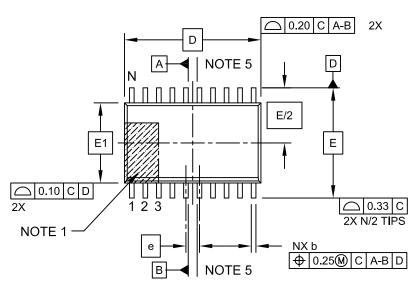

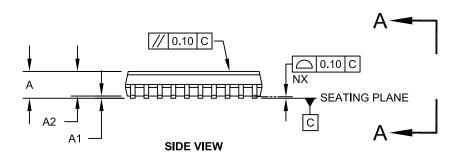

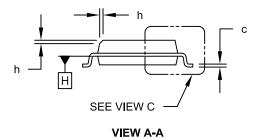

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2

#### TABLE 25-1: MAJOR SECTION UPDATES

| Section Name                                                         | Update Description                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 19.0 "10-bit/12-bit<br>Analog-to-Digital Converter<br>(ADC)" | Updated ADC Conversion Clock Select bits in the AD1CON3 register from ADCS< <b>5</b> :0> to ADCS< <b>7</b> :0>. Any references to these bits have also been updated throughout this data sheet (Register 19-3).                                                                 |

|                                                                      | Replaced Figure 19-1 (ADC1 Module Block Diagram for dsPIC33FJ12MC201) and added Figure 19-2 (ADC1 Block Diagram for dsPIC33FJ12MC202).                                                                                                                                          |

|                                                                      | Removed Equation 19-1: ADC Conversion Clock Period and Figure 19-2: ADC Transfer Function (10-Bit Example).                                                                                                                                                                     |

|                                                                      | Added Note 2 to Figure 19-2: ADC Conversion Clock Period Block Diagram.                                                                                                                                                                                                         |

|                                                                      | Updated ADC1 Input Channel 1, 2, 3 Select Register (see Register 19-4) as follows:                                                                                                                                                                                              |

|                                                                      | <ul> <li>Changed bit 10-9 (CH123NB - dsPIC33FJ12MC201 devices only)<br/>description for bit value of 10 (if AD12B = 0).</li> </ul>                                                                                                                                              |

|                                                                      | <ul> <li>Updated bit 8 (CH123SB) to reflect device-specific information.</li> <li>Updated bit 0 (CH123SA) to reflect device-specific information.</li> <li>Changed bit 2-1 (CH123NA - dsPIC33FJ12MC201 devices only) description for bit value of 10 (if AD12B = 0).</li> </ul> |

|                                                                      | <ul> <li>Updated ADC1 Input Channel 0 Select Register (see Register 19-5) as follows:</li> <li>Changed bit value descriptions for bits 12-8</li> <li>Changed bit value descriptions for bits 4-0 (dsPIC33FJ12MC201 devices)</li> </ul>                                          |

|                                                                      | Modified Notes 1 and 2 in the ADC1 Input Scan Select Register Low (see Register 19-6)                                                                                                                                                                                           |

|                                                                      | Modified Notes 1 and 2 in the ADC1 Port Configuration Register Low (see Register 19-7)                                                                                                                                                                                          |

| Section 20.0 "Special Features"                                      | Added FICD register information for address 0xF8000E in the Device Configuration Register Map (see Table 20-1).                                                                                                                                                                 |

|                                                                      | Added FICD register content (BKBUG, COE, JTAGEN, and ICS<1:0> to the dsPIC33FJ12MC201/202 Configuration Bits Description (see Table 20-2).                                                                                                                                      |

|                                                                      | Added a note regarding the placement of low-ESR capacitors, after the second paragraph of <b>Section 20.2</b> " <b>On-Chip Voltage Regulator</b> " and to Figure 20-2.                                                                                                          |

|                                                                      | Removed the words "if enabled" from the second sentence in the fifth paragraph of <b>Section 20.3 "BOR: Brown-out Reset"</b>                                                                                                                                                    |

NOTES: