#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

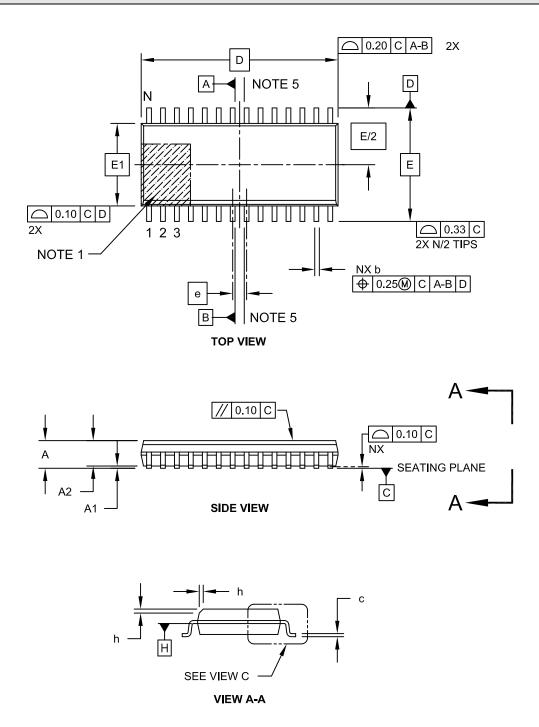

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc202-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

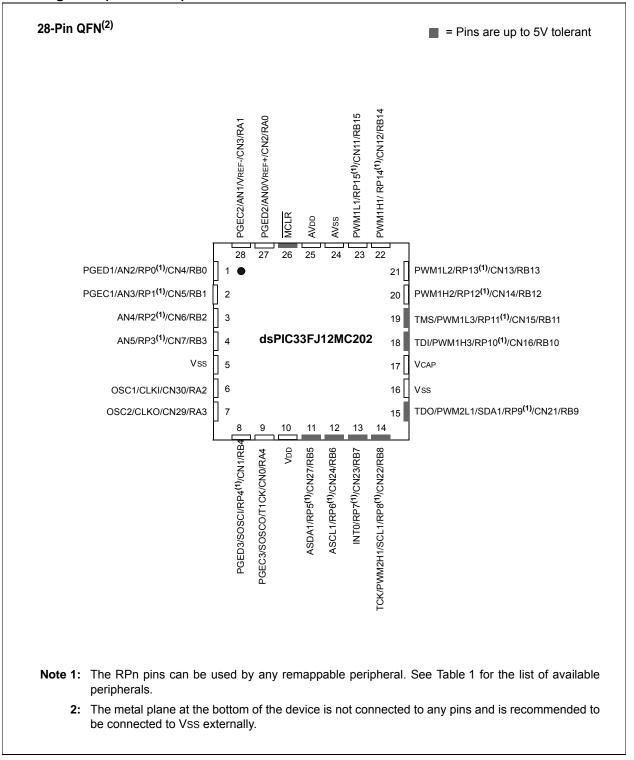

## **Pin Diagrams (Continued)**

# dsPIC33FJ12MC201/202

## 3.4 CPU Control Registers

## REGISTER 3-1: SR: CPU STATUS REGISTER

| R-0                  | R-0                                                 | R/C-0                                                                                       | R/C-0                             | R-0                    | R/C-0              | R -0              | R/W-0          |  |  |  |

|----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------|------------------------|--------------------|-------------------|----------------|--|--|--|

| OA                   | OB                                                  | SA <sup>(1)</sup>                                                                           | SB <sup>(1)</sup>                 | OAB                    | SAB                | DA                | DC             |  |  |  |

| bit 15               |                                                     |                                                                                             |                                   |                        |                    |                   | bit 8          |  |  |  |

| R/W-0 <sup>(2)</sup> | R/W-0 <sup>(3)</sup>                                | R/W-0 <sup>(3)</sup>                                                                        | R-0                               | R/W-0                  | R/W-0              | R/W-0             | R/W-0          |  |  |  |

| R/W-0                | IPL<2:0> <sup>(2)</sup>                             | K/W-0`'                                                                                     | R-0<br>RA                         | N                      | OV                 | Z                 | C              |  |  |  |

| bit 7                | IFL~2.0×()                                          |                                                                                             | RA                                | IN                     | 00                 | 2                 | bit (          |  |  |  |

| DIL 7                |                                                     |                                                                                             |                                   |                        |                    |                   |                |  |  |  |

| Legend:              |                                                     |                                                                                             |                                   |                        |                    |                   |                |  |  |  |

| C = Clear on         | ly bit                                              | R = Readable                                                                                | e bit                             | U = Unimple            | mented bit, read   | as '0'            |                |  |  |  |

| S = Set only         | bit                                                 | W = Writable                                                                                | bit                               | -n = Value at          | POR                |                   |                |  |  |  |

| '1' = Bit is set     | t                                                   | '0' = Bit is cle                                                                            | ared                              | x = Bit is unk         | nown               |                   |                |  |  |  |

| bit 15               |                                                     | ator A Overflov                                                                             | v Statua bit                      |                        |                    |                   |                |  |  |  |

| DIL 15               |                                                     | tor A overflow                                                                              |                                   |                        |                    |                   |                |  |  |  |

|                      |                                                     | tor A has not o                                                                             |                                   |                        |                    |                   |                |  |  |  |

| bit 14               | <b>OB:</b> Accumula                                 | ator B Overflow                                                                             | v Status bit                      |                        |                    |                   |                |  |  |  |

|                      | - ///                                               | <ul><li>1 = Accumulator B overflowed</li><li>0 = Accumulator B has not overflowed</li></ul> |                                   |                        |                    |                   |                |  |  |  |

| bit 13               | SA: Accumula                                        | ator A Saturatio                                                                            | on 'Sticky' Sta                   | tus bit <sup>(1)</sup> |                    |                   |                |  |  |  |

|                      | 1 = Accumula                                        |                                                                                             | ted or has bee                    | en saturated at        | some time          |                   |                |  |  |  |

| bit 12               |                                                     | ator B Saturatio                                                                            |                                   | tus bit <sup>(1)</sup> |                    |                   |                |  |  |  |

|                      | 1 = Accumula                                        |                                                                                             | ted or has bee                    | en saturated at        | some time          |                   |                |  |  |  |

| bit 11               |                                                     |                                                                                             |                                   | verflow Status         | bit                |                   |                |  |  |  |

|                      | 1 = Accumula                                        | tors A or B have ccumulators A                                                              | ve overflowed                     |                        |                    |                   |                |  |  |  |

| bit 10               | SAB: SA    SI                                       | 3 Combined A                                                                                | ccumulator 'St                    | ticky' Status bit      | I                  |                   |                |  |  |  |

|                      | 1 = Accumula<br>0 = Neither A                       | tors A or B are<br>ccumulator A c                                                           | e saturated or<br>or B are satura | have been sat          | urated at some     |                   | t              |  |  |  |

| <b>h</b> # 0         | -                                                   |                                                                                             | rea (not set).                    | Clearing this b        | it will clear SA a | na SB.            |                |  |  |  |

| bit 9                | <b>DA:</b> DO Loop<br>1 = DO loop in                |                                                                                             |                                   |                        |                    |                   |                |  |  |  |

|                      | 0 = D0 loop in                                      |                                                                                             |                                   |                        |                    |                   |                |  |  |  |

| bit 8                | DC: MCU AL                                          | J Half Carry/B                                                                              | orrow bit                         |                        |                    |                   |                |  |  |  |

|                      | •                                                   | ut from the 4th<br>sult occurred                                                            | low-order bit (                   | for byte-sized of      | data) or 8th low-o | order bit (for wo | ord-sized data |  |  |  |

|                      |                                                     | out from the 4 he result occur                                                              |                                   | oit (for byte-siz      | ed data) or 8th    | low-order bit (1  | for word-sized |  |  |  |

| Note 1: Th           | nis bit can be rea                                  | d or cleared (n                                                                             | ot set).                          |                        |                    |                   |                |  |  |  |

| Le                   | ne IPL<2:0> bits<br>evel. The value in<br>L<3> = 1. |                                                                                             |                                   |                        |                    |                   |                |  |  |  |

|                      |                                                     |                                                                                             |                                   |                        |                    |                   |                |  |  |  |

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

## TABLE 4-19: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ12MC201

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2      | Bit 1 | Bit 0 | All Resets |

|--------------|------|--------|--------|--------|--------|------------|-----------|-------|-------|-------|-------|-------|------------|-------|------------|-------|-------|------------|

| RPOR0        | 06C0 | _      | _      | —      |        |            | RP1R<4:0> | •     |       | —     | _     | —     |            |       | RP0R<4:0>  |       |       | 0000       |

| RPOR2        | 06C4 | _      | _      | _      | _      | _          | _         | _     | _     | _     | _     | _     |            |       | RP4R<4:0>  |       |       | 0000       |

| RPOR3        | 06C6 | _      | _      | _      |        |            | RP7R<4:0> | •     |       | _     | _     | _     | _          | _     | _          | _     | _     | 0000       |

| RPOR4        | 06C8 | _      | _      | _      |        |            | RP9R<4:0> | •     |       | _     | _     | _     |            |       | RP8R<4:0>  |       |       | 0000       |

| RPOR6        | 06CC | _      | _      | _      |        | RP13R<4:0> |           |       |       | _     | _     | _     | RP12R<4:0> |       |            |       | 0000  |            |

| RPOR7        | 06CE | _      | _      | _      |        | RP15R<4:0> |           |       |       | _     | —     | _     |            | F     | RP14R<4:0> |       |       | 0000       |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-20: PORTA REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|------------|

| TRISA        | 02C0 | -      | _      |        | _      | _      | _      | -     | _     |       |       | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F       |

| PORTA        | 02C2 | _      | _      | -      |        | _      | _      | -     | -     | -     | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx       |

| LATA         | 02C4 | -      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx       |

| ODCA         | 02C6 | _      | —      | _      | _      | _      | _      | _     | _     | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000       |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-21: PORTB REGISTER MAP FOR dsPIC33FJ12MC202

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|--------------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF       |

| PORTB        | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx       |

| LATB         | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx       |

| ODCB         | 02CE | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: PORTB REGISTER MAP FOR dsPIC33FJ12MC201

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|------------|

| TRISB     | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | _      | _      | TRISB9 | TRISB8 | TRISB7 | —     | —     | TRISB4 | _     | _     | TRISB1 | TRISB0 | F393       |

| PORTB     | 02CA | RB15    | RB14    | RB13    | RB12    | -      | _      | RB9    | RB8    | RB7    | —     | —     | RB4    | _     | —     | RB1    | RB0    | xxxx       |

| LATB      | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | -      | _      | LATB9  | LATB8  | LATB7  | —     | —     | LATB4  | _     | —     | LATB1  | LATB0  | xxxx       |

| ODCB      | 02CE | ODCB15  | ODCB14  | ODCB13  | ODCB12  | _      | _      | ODCB9  | ODCB8  | ODCB7  | _     | _     | ODCB4  | —     | _     | ODCB1  | ODCB0  | 0000       |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# dsPIC33FJ12MC201/202

## REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| R-0    | R-0 | R/C-0 | R/C-0 | R-0 | R/C-0 | R -0 | R/W-0 |

|--------|-----|-------|-------|-----|-------|------|-------|

| OA     | OB  | SA    | SB    | OAB | SAB   | DA   | DC    |

| bit 15 |     |       |       |     |       |      | bit 8 |

|        |     |       |       |     |       |      |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | N     | OV    | Z     | С     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(1)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

### Note 1: For complete register details, see Register 3-1: "SR: CPU Status Register".

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

## REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0              | U-0           | U-0               | R/W-0           | R/W-0                | R-0             | R-0              | R-0   |

|------------------|---------------|-------------------|-----------------|----------------------|-----------------|------------------|-------|

| _                | —             | _                 | US              | EDT                  |                 | DL<2:0>          |       |

| bit 15           |               |                   |                 |                      |                 |                  | bit 8 |

|                  |               |                   |                 |                      |                 |                  |       |

| R/W-0            | R/W-0         | R/W-1             | R/W-0           | R/C-0                | R/W-0           | R/W-0            | R/W-0 |

| SATA             | SATB          | SATDW             | ACCSAT          | IPL3 <sup>(2)</sup>  | PSV             | RND              | IF    |

| bit 7            |               |                   |                 |                      |                 |                  | bit 0 |

|                  |               |                   |                 |                      |                 |                  |       |

| Legend:          |               | C = Clear only    | y bit           |                      |                 |                  |       |

| R = Readable     | bit           | W = Writable      | bit             | -n = Value at        | POR             | '1' = Bit is set |       |

| 0' = Bit is clea | red           | 'x = Bit is unk   | nown            | U = Unimple          | mented bit, rea | d as '0'         |       |

|                  |               |                   |                 |                      |                 |                  |       |

| bit 3            | IPL3: CPU In  | terrupt Priority  | Level Status    | bit 3 <sup>(2)</sup> |                 |                  |       |

|                  | 1 = CPU inter | rupt priority lev | el is greater t | han 7                |                 |                  |       |

|                  | 0 = CPU inter | rupt priority lev | el is 7 or less | 6                    |                 |                  |       |

|                  |               |                   |                 |                      |                 |                  |       |

Note 1: For complete register details, see Register 3-2: "CORCON: Core Control Register".

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

|                         | R/W-0                           | R/W-0                               | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|-------------------------|---------------------------------|-------------------------------------|------------------|------------------|------------------|-----------------|-------|

| NSTDIS                  | OVAERR                          | OVBERR                              | COVAERR          | COVBERR          | OVATE            | OVBTE           | COVTE |

| bit 15                  |                                 |                                     |                  |                  |                  |                 | bit 8 |

|                         |                                 |                                     |                  |                  |                  |                 |       |

| R/W-0                   | R/W-0                           | U-0                                 | R/W-0            | R/W-0            | R/W-0            | R/W-0           | U-0   |

| SFTACERR                | DIV0ERR                         |                                     | MATHERR          | ADDRERR          | STKERR           | OSCFAIL         | _     |

| bit 7                   |                                 |                                     |                  |                  |                  |                 | bit 0 |

| Logondi                 |                                 |                                     |                  |                  |                  |                 |       |

| Legend:<br>R = Readable | hit                             | W = Writable                        | hit              | II = I Inimpler  | nented bit, read | l as '0'        |       |

| -n = Value at F         |                                 | '1' = Bit is set                    |                  | '0' = Bit is cle |                  | x = Bit is unkn | own   |

|                         |                                 |                                     |                  |                  | uicu             |                 | own   |

| bit 15                  | NSTDIS: Inte                    | rrupt Nesting D                     | isable bit       |                  |                  |                 |       |

|                         |                                 | nesting is disab                    |                  |                  |                  |                 |       |

|                         | 0 = Interrupt r                 | nesting is enab                     | led              |                  |                  |                 |       |

| bit 14                  |                                 | cumulator A O                       | •                | •                |                  |                 |       |

|                         |                                 | caused by ove<br>not caused by      |                  |                  |                  |                 |       |

| bit 13                  | •                               | cumulator B O                       |                  |                  |                  |                 |       |

|                         |                                 | caused by ove                       | •                | •                |                  |                 |       |

|                         | 0 = Trap was                    | not caused by                       | overflow of Ac   | cumulator B      |                  |                 |       |

| bit 12                  |                                 | Accumulator A                       | -                | -                | -                |                 |       |

|                         |                                 | caused by cata<br>not caused by     |                  |                  |                  |                 |       |

| bit 11                  | -                               | Accumulator B                       | -                |                  |                  |                 |       |

|                         |                                 | caused by cata                      | -                | •                | •                |                 |       |

|                         | 0 = Trap was                    | not caused by                       | catastrophic o   | verflow of Acc   |                  |                 |       |

| bit 10                  |                                 | imulator A Ove                      | =                | able bit         |                  |                 |       |

|                         | 1 = Trap over<br>0 = Trap disal | flow of Accumu<br>bled              | ulator A         |                  |                  |                 |       |

| bit 9                   |                                 | umulator B Ove                      | •                | able bit         |                  |                 |       |

|                         | 1 = Trap over<br>0 = Trap disal | flow of Accumu<br>bled              | ulator B         |                  |                  |                 |       |

| bit 8                   | COVTE: Cata                     | strophic Overf                      | low Trap Enab    | le bit           |                  |                 |       |

|                         | 1 = Trap on c<br>0 = Trap disal | atastrophic ove<br>bled             | erflow of Accun  | nulator A or B   | enabled          |                 |       |

| bit 7                   | SFTACERR:                       | Shift Accumula                      | ator Error Statu | s bit            |                  |                 |       |

|                         |                                 | r trap was caus<br>r trap was not o |                  |                  |                  |                 |       |

| bit 6                   | DIVOERR: Ar                     | ithmetic Error 8                    | Status bit       |                  |                  |                 |       |

|                         |                                 | r trap was caus                     |                  |                  |                  |                 |       |

| 1.1.E                   |                                 | r trap was not                      | -                | vide by zero     |                  |                 |       |

| bit 5                   | •                               | ted: Read as '                      |                  |                  |                  |                 |       |

|                         |                                 | Arithmetic Error                    |                  |                  |                  |                 |       |

| bit 4                   |                                 |                                     |                  |                  |                  |                 |       |

| bit 4                   |                                 | r trap has occu<br>r trap has not c |                  |                  |                  |                 |       |

| bit 4<br>bit 3          | 0 = Math erro                   |                                     | occurred         |                  |                  |                 |       |

## **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

| bit 3 | <b>CF:</b> Clock Fail Detect bit (read/clear by application)<br>1 = FSCM has detected clock failure<br>0 = FSCM has not detected clock failure            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Unimplemented: Read as '0'                                                                                                                                |

| bit 1 | LPOSCEN: Secondary (LP) Oscillator Enable bit<br>1 = Enable secondary oscillator<br>0 = Disable secondary oscillator                                      |

| bit 0 | <b>OSWEN:</b> Oscillator Switch Enable bit<br>1 = Request oscillator switch to selection specified by NOSC<2:0> bits<br>0 = Oscillator switch is complete |

|       |                                                                                                                                                           |

- **Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator"** (DS70186) in the *"dsPIC33F/PIC24H Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** This register is reset only on a Power-on Reset (POR).

## 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJ12MC201/202 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJ12MC201/202 devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## 9.1 Clock Frequency and Clock Switching

dsPIC33FJ12MC201/202 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

## 9.2 Instruction-Based Power-Saving Modes

dsPIC33FJ12MC201/202 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

## 9.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV#SLEEP\_MODE; Put the device into Sleep modePWRSAV#IDLE\_MODE; Put the device into Idle mode

| <b>REGISTER 9</b>                  | )-3: PMD3 | PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3 |                                         |     |     |       |       |  |

|------------------------------------|-----------|----------------------------------------------------|-----------------------------------------|-----|-----|-------|-------|--|

| U-0                                | U-0       | U-0                                                | U-0                                     | U-0 | U-0 | R/W-0 | U-0   |  |

| —                                  | —         | —                                                  |                                         | —   |     | —     | —     |  |

| bit 15                             |           |                                                    |                                         |     |     |       | bit 8 |  |

|                                    |           |                                                    |                                         |     |     |       |       |  |

| U-0                                | U-0       | U-0                                                | R/W-0                                   | U-0 | U-0 | U-0   | U-0   |  |

| —                                  | —         | —                                                  | PWM2MD                                  | —   | —   | —     | —     |  |

| bit 7                              |           |                                                    |                                         |     |     |       | bit 0 |  |

|                                    |           |                                                    |                                         |     |     |       |       |  |

| Legend:                            |           |                                                    |                                         |     |     |       |       |  |

| R = Readable bit W = Writable bit  |           | bit                                                | U = Unimplemented bit, read as '0'      |     |     |       |       |  |

| -n = Value at POR '1' = Bit is set |           |                                                    | '0' = Bit is cleared x = Bit is unknown |     |     | nown  |       |  |

|                                    |           |                                                    |                                         |     |     |       |       |  |

bit 15-5 Unimplemented: Read as '0'

bit 4 PWM2MD: PWM2 Module Disable bit

1 = PWM2 module is disabled

0 = PWM2 module is enabled

bit 3-0 Unimplemented: Read as '0'

## REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                               | U-0                | U-0             | U-0                                | U-0                  | U-0           | U-0                | U-0   |  |

|-----------------------------------|--------------------|-----------------|------------------------------------|----------------------|---------------|--------------------|-------|--|

|                                   | _                  | —               | _                                  | —                    | —             | —                  | _     |  |

| bit 15                            | ·                  |                 |                                    |                      |               |                    | bit 8 |  |

|                                   |                    |                 |                                    |                      |               |                    |       |  |

| U-0                               | U-0                | U-0             | R/W-1                              | R/W-1                | R/W-1         | R/W-1              | R/W-1 |  |

| _                                 | —                  | —               |                                    |                      | INT2R<4:0>    |                    |       |  |

| bit 7                             | ·                  |                 | •                                  |                      |               |                    | bit 0 |  |

|                                   |                    |                 |                                    |                      |               |                    |       |  |

| Legend:                           |                    |                 |                                    |                      |               |                    |       |  |

| R = Readable bit W = Writable bit |                    | bit             | U = Unimplemented bit, read as '0' |                      |               |                    |       |  |

| -n = Value at                     | t POR              | '1' = Bit is se | t                                  | '0' = Bit is cleared |               | x = Bit is unknown |       |  |

|                                   |                    |                 |                                    |                      |               |                    |       |  |

| bit 15-5                          | Unimpleme          | nted: Read as   | 0'                                 |                      |               |                    |       |  |

| bit 4-0                           | INT2R<4:0>         | : Assign Extern | al Interrupt 2                     | (INTR2) to the       | corresponding | RPn pin            |       |  |

|                                   | 11111 <b>= Inp</b> | ut tied Vss     |                                    |                      |               |                    |       |  |

|                                   | 01111 <b>= Inp</b> | ut tied to RP15 |                                    |                      |               |                    |       |  |

|                                   |                    |                 |                                    |                      |               |                    |       |  |

|                                   |                    |                 |                                    |                      |               |                    |       |  |

|                                   | •                  |                 |                                    |                      |               |                    |       |  |

|                                   | 00001 = Inp        | ut tied to RP1  |                                    |                      |               |                    |       |  |

00000 = Input tied to RP0

# dsPIC33FJ12MC201/202

| R/W-0        | U-0                           | R/W-0                                                                                                                       | U-0             | U-0             | U-0              | U-0                | U-0 |  |  |  |  |

|--------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|--------------------|-----|--|--|--|--|

| TON          |                               | TSIDL                                                                                                                       |                 | _               | —                | —                  | _   |  |  |  |  |

| bit 15       |                               |                                                                                                                             |                 |                 |                  |                    | bit |  |  |  |  |

| U-0          | R/W-0                         | R/W-0                                                                                                                       | R/W-0           | U-0             | R/W-0            | R/W-0              | U-0 |  |  |  |  |

|              | TGATE                         | TCKP                                                                                                                        | S<1:0>          |                 | TSYNC            | TCS                |     |  |  |  |  |

| bit 7        |                               |                                                                                                                             |                 |                 |                  |                    | bit |  |  |  |  |

| Legend:      |                               |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

| -            |                               | W = Writable                                                                                                                | bit             | U = Unimple     | mented bit, read | d as '0'           |     |  |  |  |  |

| -n = Value a | t POR                         | '1' = Bit is set                                                                                                            |                 | '0' = Bit is cl | eared            | x = Bit is unknown |     |  |  |  |  |

|              |                               |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

| bit 15       | TON: Timer1                   | On bit                                                                                                                      |                 |                 |                  |                    |     |  |  |  |  |

|              | 1 = Starts 16                 |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

|              | 0 = Stops 16                  |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

| bit 14       | -                             | nted: Read as '                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

| bit 13       | =                             | in Idle Mode bi                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

|              |                               | ue module ope<br>module operat                                                                                              |                 |                 | ale mode         |                    |     |  |  |  |  |

| bit 12-7     |                               | <ul> <li>0 = Continue module operation in Idle mode</li> <li>Unimplemented: Read as '0'</li> </ul>                          |                 |                 |                  |                    |     |  |  |  |  |

| bit 6        | -                             | <b>TGATE:</b> Timer1 Gated Time Accumulation Enable bit                                                                     |                 |                 |                  |                    |     |  |  |  |  |

|              | When TCS =                    |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

|              | This bit is ign               | ored.                                                                                                                       |                 |                 |                  |                    |     |  |  |  |  |

|              | When TCS =                    |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

|              |                               | ne accumulatio                                                                                                              |                 |                 |                  |                    |     |  |  |  |  |

| bit 5-4      |                               | <ul> <li>0 = Gated time accumulation disabled</li> <li>TCKPS&lt;1:0&gt;: Timer1 Input Clock Prescale Select bits</li> </ul> |                 |                 |                  |                    |     |  |  |  |  |

|              | 11 = 1:256                    |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

|              | 10 = 1:64                     |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

|              | 01 = 1:8<br>00 = 1:1          |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

| bit 3        |                               | nted: Read as '                                                                                                             | 0'              |                 |                  |                    |     |  |  |  |  |

| bit 2        | •                             | er1 External Cl                                                                                                             |                 | chronization S  | elect hit        |                    |     |  |  |  |  |

|              | When TCS =                    |                                                                                                                             | ook input oyi   |                 |                  |                    |     |  |  |  |  |

|              | 1 = Synchror                  | 1 = Synchronize external clock input                                                                                        |                 |                 |                  |                    |     |  |  |  |  |

|              | -                             | nchronize exte                                                                                                              | ernal clock inp | out             |                  |                    |     |  |  |  |  |

|              | When TCS =<br>This bit is ign |                                                                                                                             |                 |                 |                  |                    |     |  |  |  |  |

| bit 1        | -                             | Clock Source                                                                                                                | Select bit      |                 |                  |                    |     |  |  |  |  |

|              |                               | clock from pin                                                                                                              |                 | rising edge)    |                  |                    |     |  |  |  |  |

|              | 0 = Internal o                |                                                                                                                             | (* ····         | 0 0 - /         |                  |                    |     |  |  |  |  |

| bit 0        | Unimplomor                    | nted: Read as '                                                                                                             | o'              |                 |                  |                    |     |  |  |  |  |

REGISTER 16-1: QEIXCON: QEI CONTROL REGISTER

| R/W-0           | U-0                                           | R/W-0                                                                                        | R-0                                              | R/W-0             | R/W-0                               | R/W-0           | R/W-0          |

|-----------------|-----------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------|-------------------------------------|-----------------|----------------|

| CNTERR          |                                               | QEISIDL                                                                                      | INDEX                                            | UPDN              |                                     | QEIM<2:0>       |                |

| bit 15          |                                               |                                                                                              |                                                  | 1                 |                                     |                 | bit 8          |

|                 |                                               |                                                                                              |                                                  |                   |                                     |                 |                |

| R/W-0           | R/W-0                                         | R/W-0                                                                                        | R/W-0                                            | R/W-0             | R/W-0                               | R/W-0           | R/W-0          |

| SWPAB           | PCDOUT                                        | TQGATE                                                                                       | TQCK                                             | PS<1:0>           | POSRES                              | TQCS            | UPDN_SRC       |

| bit 7           |                                               |                                                                                              |                                                  |                   |                                     |                 | bit C          |

| Legend:         |                                               |                                                                                              |                                                  |                   |                                     |                 |                |

| R = Readable    | bit                                           | W = Writable                                                                                 | bit                                              | U = Unimple       | mented bit, read                    | as '0'          |                |

| -n = Value at I | POR                                           | '1' = Bit is set                                                                             |                                                  | '0' = Bit is cle  | eared                               | x = Bit is unl  | known          |

|                 |                                               |                                                                                              |                                                  |                   |                                     |                 |                |

| bit 15          |                                               | ount Error Statu                                                                             | •                                                |                   |                                     |                 |                |

|                 |                                               | count error has<br>on count error h                                                          |                                                  |                   |                                     |                 |                |

|                 |                                               |                                                                                              |                                                  |                   | - (110 <sup>2</sup> or (100         | ,               |                |

| bit 14          |                                               | -                                                                                            | • • • •                                          | en QEIIVI<2:02    | • = '110' or '100                   |                 |                |

| bit 14          | -                                             | ted: Read as '                                                                               |                                                  |                   |                                     |                 |                |

| bit 13          | 1 = Discontin                                 | op in Idle Mode<br>ue module ope<br>module operat                                            | ration when d                                    |                   | lle mode                            |                 |                |

| bit 12          |                                               | c Pin State Stat<br>is High                                                                  |                                                  |                   |                                     |                 |                |

| bit 11          | 1 = Position (<br>0 = Position (<br>(Read-onl | on Counter Dir<br>Counter Directio<br>Counter Directio<br>ly bit when QEI<br>ite bit when QE | on is positive<br>on is negative<br>M<2:0> = '1x | (+)<br>(-)<br>X') |                                     |                 |                |

| bit 10-8        | •                                             | Quadrature En                                                                                |                                                  |                   | t bits                              |                 |                |

|                 | (MAXC                                         | CNT)                                                                                         |                                                  |                   | with position co<br>with Index Puls |                 |                |

|                 | 101 = Quadra<br>(MAXC                         | ature Encoder<br>NT)                                                                         | nterface enab                                    | oled (x2 mode)    | with position co                    | ounter reset by | y match        |

|                 | 011 = Unuse                                   | d (Module disa<br>d (Module disa                                                             | bled)                                            | bled (x2 mode)    | with Index Puls                     | e reset of pos  | sition counter |

|                 | 000 = Quadra                                  | ature Encoder                                                                                | nterface/Time                                    | er off            |                                     |                 |                |

| bit 7           |                                               | ise A and Phas                                                                               | -                                                | -                 |                                     |                 |                |

|                 |                                               | and Phase B ir                                                                               |                                                  |                   |                                     |                 |                |

|                 |                                               | and Phase B ir                                                                               | •                                                | •                 |                                     |                 |                |

| bit 6           |                                               | sition Counter                                                                               |                                                  | •                 |                                     |                 |                |

|                 |                                               |                                                                                              |                                                  |                   | El logic controls                   | •               | n)             |

| 5.4 <b>C</b>    |                                               |                                                                                              |                                                  |                   | Normal I/O pin o                    | peration)       |                |

| bit 5           |                                               | ner Gated Time                                                                               |                                                  |                   |                                     |                 |                |

|                 | •                                             | ed time accum                                                                                |                                                  |                   |                                     |                 |                |

|                 | v = 1 imer gat                                | ed time accum                                                                                | uiation disable                                  | eu                |                                     |                 |                |

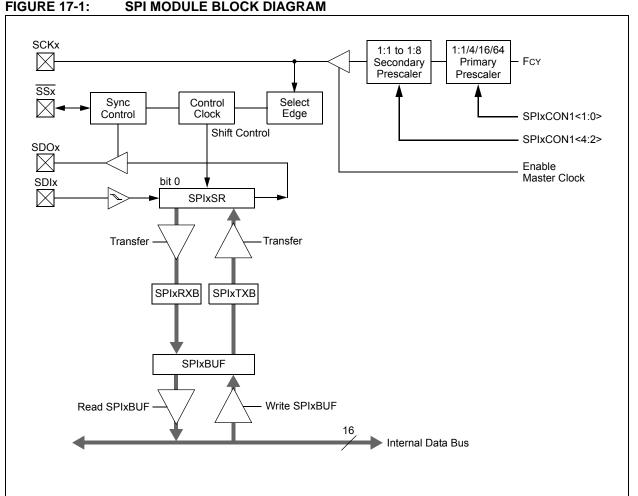

## 17.0 SERIAL PERIPHERAL **INTERFACE (SPI)**

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, analog-to-digital converters, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Each SPI module consists of a 16-bit shift register. SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of four pins:

- SDIx (serial data input)

- SDOx (serial data output)

- SCKx (shift clock input or output)

- SSx (active low slave select).

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

## SPI MODULE BLOCK DIAGRAM

## REGISTER 17-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- **Note 1:** The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both Primary and Secondary prescalers to a value of 1:1.

## TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                           | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|---------------------------------------|---------------|----------------|--------------------------|

| 66                 | RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f         | 1             | 1              | N,Z                      |

|                    |                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f      | 1             | 1              | N,Z                      |

|                    |                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws       | 1             | 1              | N,Z                      |

| 67                 | SAC                  | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                     | 1             | 1              | None                     |

|                    |                      | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator             | 1             | 1              | None                     |

| 68                 | SE                   | SE     | Ws,Wnd          | Wnd = sign-extended Ws                | 1             | 1              | C,N,Z                    |

| 69                 | SETM                 | SETM   | f               | f = 0xFFFF                            | 1             | 1              | None                     |

|                    |                      | SETM   | WREG            | WREG = 0xFFFF                         | 1             | 1              | None                     |

|                    |                      | SETM   | Ws              | Ws = 0xFFFF                           | 1             | 1              | None                     |

| 70                 | SFTAC                | SFTAC  | Acc,Wn          | Arithmetic Shift Accumulator by (Wn)  | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

|                    |                      | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6 | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

| 71                 | SL                   | SL     | f               | f = Left Shift f                      | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG          | WREG = Left Shift f                   | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd           | Wd = Left Shift Ws                    | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns            | 1             | 1              | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5           | 1             | 1              | N,Z                      |

| 72                 | SUB                  | SUB    | Асс             | Subtract Accumulators                 | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |

|                    |                      | SUB    | f               | f = f – WREG                          | 1             | 1              | C,DC,N,OV,2              |

|                    |                      | SUB    | f,WREG          | WREG = f – WREG                       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUB    | #lit10,Wn       | Wn = Wn - Iit10                       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                          | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUB    | Wb,#lit5,Wd     | Wd = Wb – lit5                        | 1             | 1              | C,DC,N,OV,               |

| 73                 | SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$       | 1             | 1              | C,DC,N,OV,2              |

|                    |                      | SUBB   | f,WREG          | WREG = f – WREG – $(\overline{C})$    | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBB   | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$    | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$     | 1             | 1              | C,DC,N,OV,               |

| 74                 | SUBR                 | SUBR   | f               | f = WREG – f                          | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBR   | f,WREG          | WREG = WREG – f                       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBR   | Wb,Ws,Wd        | Wd = Ws – Wb                          | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                        | 1             | 1              | C,DC,N,OV,               |

| 75                 | SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBBR  | f,WREG          | WREG = WREG – f – $(\overline{C})$    | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBBR  | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$       | 1             | 1              | C,DC,N,OV,               |

|                    |                      | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$     | 1             | 1              | C,DC,N,OV,               |

| 76                 | SWAP                 | SWAP.b | Wn              | Wn = nibble swap Wn                   | 1             | 1              | None                     |

|                    |                      | SWAP   | Wn              | Wn = byte swap Wn                     | 1             | 1              | None                     |

| 77                 | TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>           | 1             | 2              | None                     |

| 78                 | TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd                 | 1             | 2              | None                     |

| 79                 | TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16>          | 1             | 2              | None                     |

| 80                 | TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>                | 1             | 2              | None                     |

| 81                 | ULNK                 | ULNK   |                 | Unlink Frame Pointer                  | 1             | 1              | None                     |

| 82                 | XOR                  | XOR    | f               | f = f .XOR. WREG                      | 1             | 1              | N,Z                      |

|                    |                      | XOR    | f,WREG          | WREG = f .XOR. WREG                   | 1             | 1              | N,Z                      |

|                    |                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd                   | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws                      | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5                    | 1             | 1              | N,Z                      |

| 83                 | ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-extend Ws                  | 1             | 1              | C,Z,N                    |

| DC CHARACTERISTICS |                        |            | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                  |        |                        |  |  |

|--------------------|------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|------------------------|--|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Max        | Units                                                                                                                                                                                                | Conditions       |        |                        |  |  |

| Idle Current (I    | DLE): Core OF          | F Clock ON | Base Curren                                                                                                                                                                                          | t <sup>(2)</sup> |        |                        |  |  |

| DC40d              | 3                      | 25         | mA                                                                                                                                                                                                   | -40°C            |        |                        |  |  |

| DC40a              | 3                      | 25         | mA                                                                                                                                                                                                   | +25°C            |        | 10 MIPS <sup>(3)</sup> |  |  |

| DC40b              | 3                      | 25         | mA                                                                                                                                                                                                   | +85°C            | 3.3V   |                        |  |  |