Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 12KB (12K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

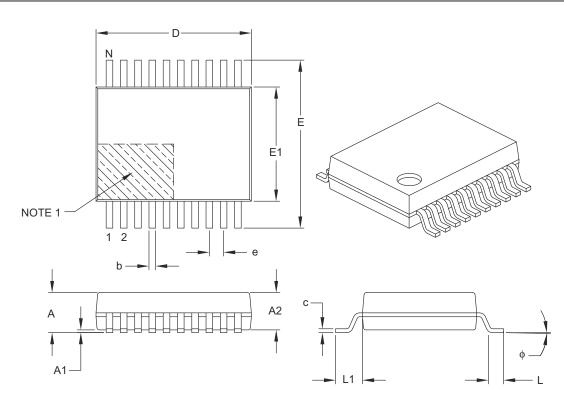

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc202t-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33FJ12MC201/202 PRODUCT FAMILIES

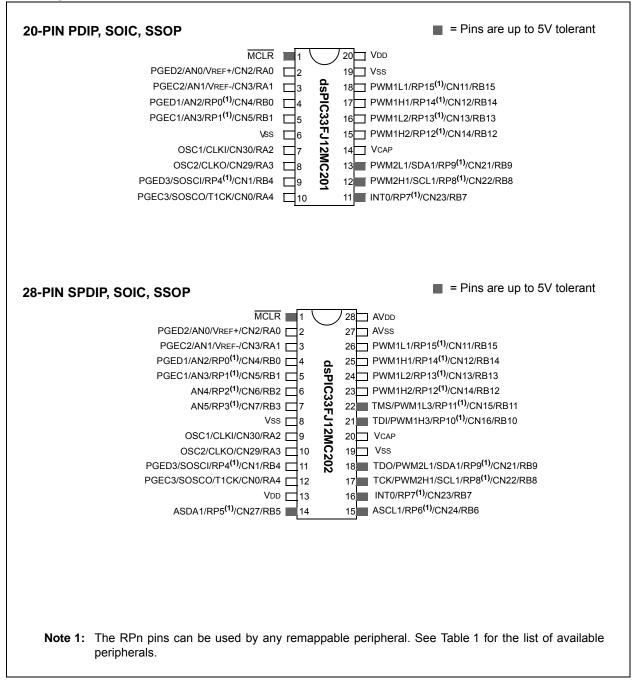

The device names, pin counts, memory sizes, and peripheral availability of each device are listed in Table 1. The following pages show their pinout diagrams.

| TABLE 1: | dsPIC33FJ12MC201/202 | CONTROLLER FAMILIES |

|----------|----------------------|---------------------|

|----------|----------------------|---------------------|

|                  |      | ٢٧                              |             |                 |                  | Re            | emapp                          | able Pe                                  | eriphera                        | als  |                                    |     |                   |       |          |                              |

|------------------|------|---------------------------------|-------------|-----------------|------------------|---------------|--------------------------------|------------------------------------------|---------------------------------|------|------------------------------------|-----|-------------------|-------|----------|------------------------------|

| Device           | Pins | Program Flash Memory<br>(Kbyte) | RAM (Kbyte) | Remappable Pins | 16-bit Timer     | Input Capture | Output Compare<br>Standard PWM | Motor Control PWM                        | Quadrature Encoder<br>Interface | UART | External Interrupts <sup>(3)</sup> | IdS | 10-Bit/12-Bit ADC | I²Стм | I/O Pins | Packages                     |

| dsPIC33FJ12MC201 | 20   | 12                              | 1           | 10              | 3 <sup>(1)</sup> | 4             | 2                              | 4ch <sup>(2)</sup><br>2ch <sup>(2)</sup> | 1                               | 1    | 3                                  | 1   | 1ADC,<br>4 ch     | 1     | 15       | PDIP<br>SOIC<br>SSOP         |

| dsPIC33FJ12MC202 | 28   | 12                              | 1           | 16              | 3(1)             | 4             | 2                              | 6ch <sup>(2)</sup><br>2ch <sup>(2)</sup> | 1                               | 1    | 3                                  | 1   | 1ADC.<br>6 ch     | 1     | 21       | SPDIP<br>SOIC<br>SSOP<br>QFN |

**Note 1:** Only two out of three timers are remappable.

2: Only PWM fault inputs are remappable.

**3:** Only two out of three interrupts are remappable.

## **Pin Diagrams**

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7        | Bit 6  | Bit 5     | Bit 4         | Bit 3        | Bit 2       | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|------------------------------|--------|--------|--------|--------|---------|---------------|--------------|--------|-----------|---------------|--------------|-------------|---------|-------|---------------|

| WREG0    | 0000        |        |                              |        |        |        |        |         | Working Re    | gister 0     |        |           |               |              |             |         |       | 0000          |

| WREG1    | 0002        |        | Working Register 1           |        |        |        |        |         |               |              |        |           |               |              |             | 0000    |       |               |

| WREG2    | 0004        |        | Working Register 2           |        |        |        |        |         |               |              |        |           |               |              |             | 0000    |       |               |

| WREG3    | 0006        |        | Working Register 3           |        |        |        |        |         |               |              |        |           |               |              |             | 0000    |       |               |

| WREG4    | 8000        |        | Working Register 4           |        |        |        |        |         |               |              |        |           |               |              | 0000        |         |       |               |

| WREG5    | 000A        |        |                              |        |        |        |        |         | Working Re    | gister 5     |        |           |               |              |             |         |       | 0000          |

| WREG6    | 000C        |        |                              |        |        |        |        |         | Working Re    | gister 6     |        |           |               |              |             |         |       | 0000          |

| WREG7    | 000E        |        |                              |        |        |        |        |         | Working Re    | gister 7     |        |           |               |              |             |         |       | 0000          |

| WREG8    | 0010        |        |                              |        |        |        |        |         | Working Re    | gister 8     |        |           |               |              |             |         |       | 0000          |

| WREG9    | 0012        |        |                              |        |        |        |        |         | Working Re    | gister 9     |        |           |               |              |             |         |       | 0000          |

| WREG10   | 0014        |        |                              |        |        |        |        |         | Working Re    | gister 10    |        |           |               |              |             |         |       | 0000          |

| WREG11   | 0016        |        |                              |        |        |        |        |         | Working Re    | gister 11    |        |           |               |              |             |         |       | 0000          |

| WREG12   | 0018        |        |                              |        |        |        |        |         | Working Re    | gister 12    |        |           |               |              |             |         |       | 0000          |

| WREG13   | 001A        |        | Working Register 13          |        |        |        |        |         |               |              |        |           | 0000          |              |             |         |       |               |

| WREG14   | 001C        |        | Working Register 14          |        |        |        |        |         |               |              |        |           | 0000          |              |             |         |       |               |

| WREG15   | 001E        |        | Working Register 15          |        |        |        |        |         |               |              |        |           | 0800          |              |             |         |       |               |

| SPLIM    | 0020        |        | Stack Pointer Limit Register |        |        |        |        |         |               |              |        |           | xxxx          |              |             |         |       |               |

| ACCAL    | 0022        |        |                              |        |        |        |        | Accum   | ulator A Low  | Word Regi    | ster   |           |               |              |             |         |       | 0000          |

| ACCAH    | 0024        |        |                              |        |        |        |        | Accum   | ulator A High | n Word Regi  | ster   |           |               |              |             |         |       | 0000          |

| ACCAU    | 0026        |        |                              |        |        |        |        | Accumu  | lator A Uppe  | er Word Reg  | jister |           |               |              |             |         |       | 0000          |

| ACCBL    | 0028        |        |                              |        |        |        |        | Accum   | ulator B Low  | Word Regi    | ster   |           |               |              |             |         |       | 0000          |

| ACCBH    | 002A        |        |                              |        |        |        |        | Accum   | ulator B High | n Word Regi  | ster   |           |               |              |             |         |       | 0000          |

| ACCBU    | 002C        |        |                              |        |        |        |        | Accumu  | lator B Uppe  | er Word Reg  | jister |           |               |              |             |         |       | 0000          |

| PCL      | 002E        |        |                              |        |        |        |        | Program | Counter Lo    | w Word Reg   | gister |           |               |              |             |         |       | 0000          |

| PCH      | 0030        | —      | _                            | _      | —      | —      | _      | —       | —             |              |        | Progra    | m Counter     | High Byte R  | Register    |         |       | 0000          |

| TBLPAG   | 0032        | —      | _                            |        | —      | —      | _      | —       |               |              |        |           | <u> </u>      | ss Pointer R | <u> </u>    |         |       | 0000          |

| PSVPAG   | 0034        | —      | —                            | —      | —      | —      | —      | —       | —             |              | Progra | am Memory | Visibility Pa | age Address  | s Pointer R | egister |       | 0000          |

| RCOUNT   | 0036        |        |                              |        |        |        |        | Repe    | eat Loop Cou  | unter Regist | er     |           |               |              |             |         |       | XXXX          |

| DCOUNT   | 0038        |        |                              |        |        |        |        |         | DCOUNT        | <15:0>       |        |           |               |              |             |         |       | xxxx          |

| DOSTARTL | 003A        |        |                              |        |        |        |        | DOS     | TARTL<15:     | 1>           |        |           |               |              |             |         | 0     | xxxx          |

| DOSTARTH | 003C        | —      | —                            | —      | —      | —      | —      | —       | —             | —            | —      |           |               | DOSTAR       | RTH<5:0>    |         |       | 00xx          |

| DOENDL   | 003E        |        |                              |        |        |        |        | DOE     | ENDL<15:1     | >            |        |           |               |              |             |         | 0     | xxxx          |

| DOENDH   | 0040        | —      | DOENDH                       |        |        |        |        |         |               |              |        | 00xx      |               |              |             |         |       |               |

| SR       | 0042        | OA     | OB                           | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2         | IPL1   | IPL0      | RA            | N            | OV          | Z       | С     | 0000          |

| CORCON   | 0044        | —      | —                            | -      | US     | EDT    |        | DL<2:0> |               | SATA         | SATB   | SATDW     | ACCSAT        | IPL3         | PSV         | RND     | IF    | 0020          |

| MODCON   | 0046        | XMODEN | YMODEN                       | —      | _      |        | BWN    | 1<3:0>  |               |              | YWM    | <3:0>     |               |              | XWM         | <3:0>   |       | 0000          |

### TABLE 4-1: CPU CORE REGISTERS MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 7-12: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0          | U-0             | U-0              | U-0              | U-0          | R/W-0            | R/W-0    | U-0   |

|--------------|-----------------|------------------|------------------|--------------|------------------|----------|-------|

| _            | _               | _                | —                | _            | FLA2IE           | PWM2IE   | _     |

| bit 15       |                 |                  |                  | ·            |                  | -        | bit 8 |

|              |                 |                  |                  |              |                  |          |       |

| U-0          | U-0             | U-0              | U-0              | U-0          | U-0              | R/W-0    | U-0   |

| _            | _               | _                | —                | _            | _                | U1EIE    | _     |

| bit 7        | ·               |                  |                  |              | ·                |          | bit 0 |

|              |                 |                  |                  |              |                  |          |       |

| Legend:      |                 |                  |                  |              |                  |          |       |

| R = Readab   | le bit          | W = Writable     | bit              | U = Unimplei | mented bit, read | d as '0' |       |

| -n = Value a | t POR           | '1' = Bit is set | '0' = Bit is cle | ared         | x = Bit is unkno | own      |       |

|              |                 |                  |                  |              |                  |          |       |

| bit 15-11    | Unimplemen      | ted: Read as '   | 0'               |              |                  |          |       |

| bit 10       | FLA2IE: PWI     | M2 Fault A Inte  | rrupt Enable     | bit          |                  |          |       |

|              |                 | request enable   |                  |              |                  |          |       |

|              | 0 = Interrupt I | request not ena  | abled            |              |                  |          |       |

| bit 9        | PWM2IE: PW      | /M2 Error Inter  | rupt Enable b    | it           |                  |          |       |

|              |                 | request enable   |                  |              |                  |          |       |

|              | •               | request not ena  |                  |              |                  |          |       |

| bit 8-2      | •               | ted: Read as '   |                  |              |                  |          |       |

| bit 1        |                 | [1 Error Interru | •                |              |                  |          |       |

|              |                 | request enable   |                  |              |                  |          |       |

|              | -               | request not ena  |                  |              |                  |          |       |

| bit 0        | Unimplemen      | ted: Read as '   | 0'               |              |                  |          |       |

|              |                 |                  |                  |              |                  |          |       |

NOTES:

## 10.4 Peripheral Pin Select

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

### 10.4.1 AVAILABLE PINS

The peripheral pin select feature is used with a range of up to 16 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

### 10.4.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

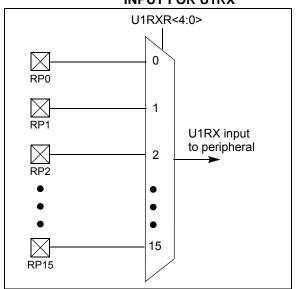

### 10.4.2.1 Input Mapping

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-13). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

Figure 10-2 Illustrates remappable pin selection for U1RX input.

| Note: | For input mapping only, the Peripheral Pin |

|-------|--------------------------------------------|

|       | Select (PPS) functionality does not have   |

|       | priority over the TRISx settings. There-   |

|       | fore, when configuring the RPx pin for     |

|       | input, the corresponding bit in the TRISx  |

|       | register must also be configured for input |

|       | (i.e., set to '1').                        |

#### FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

### REGISTER 10-14: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0           | U-0        | U-0                               | R/W-0           | R/W-0                                   | R/W-0          | R/W-0           | R/W-0    |  |  |  |  |

|---------------|------------|-----------------------------------|-----------------|-----------------------------------------|----------------|-----------------|----------|--|--|--|--|

| _             | —          | _                                 |                 |                                         | RP1R<4:0>      |                 |          |  |  |  |  |

| bit 15        |            |                                   |                 |                                         |                |                 | bit 8    |  |  |  |  |

|               |            |                                   |                 |                                         |                |                 |          |  |  |  |  |

| U-0           | U-0        | U-0                               | R/W-0           | R/W-0                                   | R/W-0          | R/W-0           | R/W-0    |  |  |  |  |

| —             | —          | —                                 |                 |                                         | RP0R<4:0>      |                 |          |  |  |  |  |

| bit 7         |            |                                   |                 |                                         |                |                 | bit 0    |  |  |  |  |

|               |            |                                   |                 |                                         |                |                 |          |  |  |  |  |

| Legend:       |            |                                   |                 |                                         |                |                 |          |  |  |  |  |

| R = Readabl   | le bit     | W = Writable                      | bit             | it U = Unimplemented bit, read as '0'   |                |                 |          |  |  |  |  |

| -n = Value at | POR        | '1' = Bit is set                  |                 | '0' = Bit is cleared x = Bit is unknown |                |                 |          |  |  |  |  |

| bit 15-13     | Unimplemen | ted: Read as '                    | 0'              |                                         |                |                 |          |  |  |  |  |

| bit 12-8      |            | Peripheral Outr<br>ction numbers) |                 | s Assigned to F                         | RP1 Output Pin | bits (see Table | 10-2 for |  |  |  |  |

| bit 7-5       | Unimplemen | ted: Read as '                    | 0'              |                                         |                |                 |          |  |  |  |  |

| bit 4-0       | RP0R<4:0>: | Peripheral Out                    | out Function is | s Assigned to F                         | RP0 Output Pin | bits (see Table | 10-2 for |  |  |  |  |

peripheral function numbers)

### REGISTER 10-15: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0                                       | U-0 | U-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 |  |  |

|-------------------------------------------|-----|-----|-------|-----------------------------------------|------------------------------------|-------|-------|--|--|

| —                                         | _   | —   |       |                                         | RP3R<4:0>                          |       |       |  |  |

| bit 15                                    |     |     |       |                                         |                                    |       | bit 8 |  |  |

|                                           |     |     |       |                                         |                                    |       |       |  |  |

| U-0                                       | U-0 | U-0 | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 |  |  |

| —                                         | _   | —   |       |                                         | RP2R<4:0>                          |       |       |  |  |

| bit 7                                     |     |     |       |                                         |                                    |       | bit 0 |  |  |

|                                           |     |     |       |                                         |                                    |       |       |  |  |

| Legend:                                   |     |     |       |                                         |                                    |       |       |  |  |

| R = Readable bit W = Writable bit U = Uni |     |     |       |                                         | U = Unimplemented bit, read as '0' |       |       |  |  |

| -n = Value at POR '1' = Bit is set        |     |     |       | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |  |  |

| R = Readable I                            |     |     |       | •                                       |                                    |       |       |  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-2 for peripheral function numbers)

### REGISTER 10-18: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0 U-0 U-0<br>— — — —            | R/W-0                                    | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-----------------------------------|------------------------------------------|-------|-----------|-------|-------|

|                                   |                                          |       |           |       |       |

| 1 1 4 5                           |                                          |       | RP9R<4:0> |       |       |

| bit 15                            |                                          |       |           |       | bit 8 |

|                                   |                                          |       |           |       |       |

| U-0 U-0 U-0                       | R/W-0                                    | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|                                   |                                          |       | RP8R<4:0> |       |       |

| bit 7                             |                                          |       |           |       | bit 0 |

|                                   |                                          |       |           |       |       |

| Legend:                           |                                          |       |           |       |       |

| R = Readable bit W = Writable bit | e bit U = Unimplemented bit, read as '0' |       |           |       |       |

'0' = Bit is cleared

| bit 15-13 | Unimplemented: Read as '0' |  |

|-----------|----------------------------|--|

'1' = Bit is set

- bit 12-8 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

-n = Value at POR

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 10-2 for peripheral function numbers)

### REGISTER 10-19: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP11R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| —     | —   | —   |       |       | RP10R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-2 for peripheral function numbers)

x = Bit is unknown

## REGISTER 15-5: PWMxCON1: PWM CONTROL REGISTER 1<sup>(2)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      | —   | —   | —   | —   | PMOD3 | PMOD2 | PMOD1 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | R/W-1                                                                | R/W-1 | R/W-1                | U-0                  | R/W-1                | R/W-1 | R/W-1 |

|-------|----------------------------------------------------------------------|-------|----------------------|----------------------|----------------------|-------|-------|

| —     | PEN3H <sup>(1)</sup> PEN2H <sup>(1)</sup> PEN1H <sup>(1)</sup> — PEI |       | PEN3L <sup>(1)</sup> | PEN2L <sup>(1)</sup> | PEN1L <sup>(1)</sup> |       |       |

| bit 7 |                                                                      |       |                      |                      |                      |       | bit 0 |

| Legend:           |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

| bit 15-11 | Unimplemented: Read as '0'                                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10-8  | PMOD4:PMOD1: PWM I/O Pair Mode bits                                                                                                              |

|           | <ul> <li>1 = PWM I/O pin pair is in the Independent PWM Output mode</li> <li>0 = PWM I/O pin pair is in the Complementary Output mode</li> </ul> |

| bit 7     | Unimplemented: Read as '0'                                                                                                                       |

| bit 6-4   | PEN3H:PEN1H: PWMxH I/O Enable bits <sup>(1)</sup>                                                                                                |

|           | <ul> <li>1 = PWMxH pin is enabled for PWM output</li> <li>0 = PWMxH pin disabled, I/O pin becomes general purpose I/O</li> </ul>                 |

| bit 3     | Unimplemented: Read as '0'                                                                                                                       |

| bit 2-0   | PEN3L:PEN1L: PWMxL I/O Enable bits <sup>(1)</sup>                                                                                                |

|           | <ul> <li>1 = PWMxL pin is enabled for PWM output</li> <li>0 = PWMxL pin disabled, I/O pin becomes general purpose I/O</li> </ul>                 |

- **Note 1:** Reset condition of the PENxH and PENxL bits depends on the value of the PWMPIN Configuration bit in the FPOR Configuration register.

- 2: PWM2 supports only one PWM I/O pin pair. PWM1 on dsPIC33FJ12MC201 devices supports only two PWM I/O pin pairs.

NOTES:

### REGISTER 20-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

|                    | U-0                                                                                                                                                | U-0                                                                                                                                                                                            | R/W-0                                                                                                                                                                  | R/W-0           | R/W-0           | R/W-0           | R/W-0          |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|----------------|--|--|--|--|

| CH0NB              |                                                                                                                                                    |                                                                                                                                                                                                |                                                                                                                                                                        |                 | CH0SB<4:0>      |                 |                |  |  |  |  |

| bit 15             |                                                                                                                                                    |                                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 | bit 8          |  |  |  |  |

|                    |                                                                                                                                                    |                                                                                                                                                                                                | <b>D</b> 444 0                                                                                                                                                         | <b>D</b> 444 0  | <b>D</b> 444 0  | <b>D</b> 444 0  | <b>D</b> 444 0 |  |  |  |  |

| R/W-0              | U-0                                                                                                                                                | U-0                                                                                                                                                                                            | R/W-0                                                                                                                                                                  | R/W-0           | R/W-0           | R/W-0           | R/W-0          |  |  |  |  |

| CHONA              | —                                                                                                                                                  | —                                                                                                                                                                                              |                                                                                                                                                                        |                 | CH0SA<4:0>      |                 |                |  |  |  |  |

| bit 7              |                                                                                                                                                    |                                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 | bit            |  |  |  |  |

| Legend:            |                                                                                                                                                    |                                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

| R = Readable       | e bit                                                                                                                                              | W = Writable                                                                                                                                                                                   | oit                                                                                                                                                                    | U = Unimple     | mented bit, rea | d as '0'        |                |  |  |  |  |

| -n = Value at      | POR                                                                                                                                                | '1' = Bit is set                                                                                                                                                                               |                                                                                                                                                                        | '0' = Bit is cl |                 | x = Bit is unkr | nown           |  |  |  |  |

|                    |                                                                                                                                                    |                                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

| bit 15             | CH0NB: Cha                                                                                                                                         | nnel 0 Negative                                                                                                                                                                                | e Input Select                                                                                                                                                         | for Sample B    | oit             |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | 0 negative inpu                                                                                                                                                                                | -                                                                                                                                                                      |                 |                 |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | 0 negative inpu                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

| bit 14-13          | Unimplemen                                                                                                                                         | ted: Read as '                                                                                                                                                                                 | )'                                                                                                                                                                     |                 |                 |                 |                |  |  |  |  |

| bit 12-8           | CH0SB<4:0>                                                                                                                                         | : Channel 0 Po                                                                                                                                                                                 | sitive Input Se                                                                                                                                                        | elect for Samp  | le B bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12                                                                                                                                        | CH0SB<4:0>: Channel 0 Positive Input Select for Sample B bits<br>dsPIC33FJ12MC201 devices only:                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

|                    | 00011 <b>= Cha</b>                                                                                                                                 | nnel 0 positive                                                                                                                                                                                | input is AN3                                                                                                                                                           |                 |                 |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | nnel 0 positive                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | 00001 = Channel 0 positive input is AN1                                                                                                                                                        |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

|                    | 00000 = Cha                                                                                                                                        | 00000 = Channel 0 positive input is AN0                                                                                                                                                        |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

|                    | dsPIC33FJ12                                                                                                                                        | 2MC202 device                                                                                                                                                                                  | es only:                                                                                                                                                               |                 |                 |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | nnel 0 positive                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | nnel 0 positive                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | nnel 0 positive                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | nnel 0 positive                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | nnel 0 positive                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

| hit 7              |                                                                                                                                                    | nnel 0 positive                                                                                                                                                                                | -                                                                                                                                                                      | for Comple A    | ait             |                 |                |  |  |  |  |

| bit 7              |                                                                                                                                                    | nnel 0 Negative                                                                                                                                                                                | -                                                                                                                                                                      | Ior Sample A    | JIL             |                 |                |  |  |  |  |

|                    |                                                                                                                                                    | 1 = Channel 0 negative input is AN1<br>0 = Channel 0 negative input is VREF-                                                                                                                   |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

|                    |                                                                                                                                                    |                                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

| bit 6-5            | •                                                                                                                                                  |                                                                                                                                                                                                |                                                                                                                                                                        |                 |                 |                 |                |  |  |  |  |

| bit 6-5<br>bit 4-0 | CH0SA-4.05                                                                                                                                         | · Channel () Po                                                                                                                                                                                |                                                                                                                                                                        | elect for Samo  | le A hite       |                 |                |  |  |  |  |

| bit 6-5<br>bit 4-0 |                                                                                                                                                    | Channel 0 Pc                                                                                                                                                                                   | sitive Input Se                                                                                                                                                        | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12                                                                                                                                        | 2MC201 device                                                                                                                                                                                  | sitive Input Se<br><b>s only:</b>                                                                                                                                      | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | <b>dsPIC33FJ1</b><br>00011 = Cha                                                                                                                   | 2MC201 device                                                                                                                                                                                  | sitive Input Se<br><b>es only:</b><br>input is AN3                                                                                                                     | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12<br>00011 = Cha<br>00010 = Cha                                                                                                          | 2MC201 device                                                                                                                                                                                  | sitive Input Se<br>es only:<br>input is AN3<br>input is AN2                                                                                                            | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12<br>00011 = Cha<br>00010 = Cha<br>00001 = Cha                                                                                           | 2MC201 device<br>Innel 0 positive<br>Innel 0 positive                                                                                                                                          | sitive Input Se<br>s only:<br>input is AN3<br>input is AN2<br>input is AN1                                                                                             | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12<br>00011 = Cha<br>00010 = Cha<br>00001 = Cha<br>00000 = Cha                                                                            | 2MC201 device<br>Innel 0 positive<br>Innel 0 positive<br>Innel 0 positive                                                                                                                      | sitive Input Se<br>s only:<br>input is AN3<br>input is AN2<br>input is AN1<br>input is AN0                                                                             | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12<br>00011 = Cha<br>00010 = Cha<br>00001 = Cha<br>00000 = Cha<br>dsPIC33FJ12<br>00101 = Cha                                              | 2MC201 device<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>2MC202 device<br>innel 0 positive                                                             | sitive Input Se<br>s only:<br>input is AN3<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:<br>input is AN5                                                 | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12<br>00011 = Cha<br>00010 = Cha<br>00001 = Cha<br>00000 = Cha<br>dsPIC33FJ12<br>00101 = Cha<br>00100 = Cha                               | 2MC201 device<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>2MC202 device<br>innel 0 positive<br>innel 0 positive                                         | sitive Input Se<br>s only:<br>input is AN3<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:<br>input is AN5<br>input is AN4                                 | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12<br>00011 = Cha<br>00010 = Cha<br>00001 = Cha<br>00000 = Cha<br>dsPIC33FJ12<br>00101 = Cha<br>00100 = Cha<br>00011 = Cha                | 2MC201 device<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>2MC202 device<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive                     | sitive Input Se<br>s only:<br>input is AN3<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:<br>input is AN5<br>input is AN4<br>input is AN3                 | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12<br>00011 = Cha<br>00010 = Cha<br>00001 = Cha<br>00000 = Cha<br>dsPIC33FJ12<br>00101 = Cha<br>00100 = Cha<br>00011 = Cha                | 2MC201 device<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>2MC202 device<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive | sitive Input Se<br>s only:<br>input is AN3<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:<br>input is AN5<br>input is AN3<br>input is AN3                 | elect for Samp  | le A bits       |                 |                |  |  |  |  |

|                    | dsPIC33FJ12<br>00011 = Cha<br>00010 = Cha<br>00001 = Cha<br>00000 = Cha<br>dsPIC33FJ12<br>00101 = Cha<br>00100 = Cha<br>00011 = Cha<br>00010 = Cha | 2MC201 device<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>2MC202 device<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive<br>innel 0 positive                     | sitive Input Se<br>s only:<br>input is AN3<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:<br>input is AN5<br>input is AN3<br>input is AN2<br>input is AN1 | elect for Samp  | le A bits       |                 |                |  |  |  |  |

| TABLE 22-1: | SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED) |

|-------------|-------------------------------------------------|

|-------------|-------------------------------------------------|

| Field | Description                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                        |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                        |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                                |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                                         |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                             |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                         |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                      |

| Wx    | X data space prefetch address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

| Wy    | Y data space prefetch address register for DSP instructions<br>∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,<br>[W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,<br>[W11 + W12], none} |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

## 23.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 23.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 23.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 23.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 23.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

| DC CHARACTERISTICS  |       | (unless                              | rd Opera<br>otherwing tempe | ise state | ed)<br>-40°C ≤ TA ≤+85°C for Industrial<br>-40°C ≤TA ≤+125°C for Extended |            |                                                            |

|---------------------|-------|--------------------------------------|-----------------------------|-----------|---------------------------------------------------------------------------|------------|------------------------------------------------------------|

| Param<br>No. Symbol |       | Characteristic <sup>(3)</sup>        | Min Typ <sup>(1)</sup> Max  |           | Units                                                                     | Conditions |                                                            |

|                     |       | Program Flash Memory                 |                             |           |                                                                           |            |                                                            |

| D130a               | Eр    | Cell Endurance                       | 10,000                      | _         | _                                                                         | E/W        | -40° C to +125° C                                          |

| D131                | Vpr   | VDD for Read                         | VMIN                        | _         | 3.6                                                                       | V          | VMIN = Minimum operating<br>voltage                        |

| D132B               | VPEW  | VDD for Self-Timed Write             | VMIN                        | —         | 3.6                                                                       | V          | VMIN = Minimum operating<br>voltage                        |

| D134                | TRETD | Characteristic Retention             | 20                          | —         | —                                                                         | Year       | Provided no other specifications are violated              |

| D135                | IDDP  | Supply Current during<br>Programming | -                           | 10        | —                                                                         | mA         |                                                            |

| D136a               | Trw   | Row Write Time                       | 1.32                        | —         | 1.74                                                                      | ms         | Trw = 11064 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>   |

| D136b               | Trw   | Row Write Time                       | 1.28                        | _         | 1.79                                                                      | ms         | Trw = 11064 FRC cycles,<br>Ta = +125°C, See <b>Note 2</b>  |

| D137a               | Тре   | Page Erase Time                      | 20.1                        | —         | 26.5                                                                      | ms         | TPE = 168517 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>  |

| D137b               | TPE   | Page Erase Time                      | 19.5                        | —         | 27.3                                                                      | ms         | TPE = 168517 FRC cycles,<br>TA = +125°C, See <b>Note 2</b> |

| D138a               | Tww   | Word Write Cycle Time                | 42.3                        | —         | 55.9                                                                      | μs         | Tww = 355 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>     |

| D138b               | Tww   | Word Write Cycle Time                | 41.1                        | —         | 57.6                                                                      | μs         | Tww = 355 FRC cycles,<br>TA = +125°C, See <b>Note 2</b>    |

### TABLE 24-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Other conditions: FRC = 7.37 MHz, TUN<5:0> = b'011111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 24-18) and the value of the FRC Oscillator Tuning register (see Register 8-4). For complete details on calculating the Minimum and Maximum time see Section 5.3 "Programming Operations".

3: These parameters are ensured by design, but are not characterized or tested in manufacturing.

### TABLE 24-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |     |     |     |       |                                                          |

|--------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|----------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristics                                                                                                                                                                                          | Min | Тур | Max | Units | Comments                                                 |

|                    | CEFC   | External Filter Capacitor<br>Value <sup>(1)</sup>                                                                                                                                                        | 4.7 | 10  | _   | μF    | Capacitor must be low<br>series resistance<br>(< 5 ohms) |

**Note 1:** Typical VCAP pin voltage = 2.5V when VDD  $\geq$  VDDMIN.

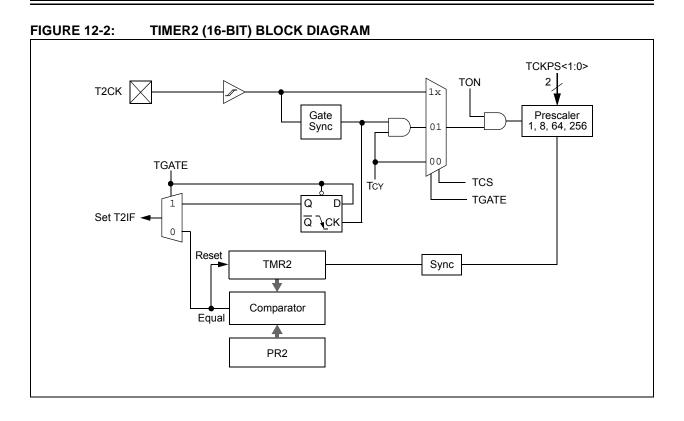

### FIGURE 24-5: TIMER1, 2, 3 AND 4 EXTERNAL CLOCK TIMING CHARACTERISTICS

| AC CHARACTERISTICS |           |                                                                        |                                |       | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |                  |       |                                          |  |

|--------------------|-----------|------------------------------------------------------------------------|--------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-------|------------------------------------------|--|

| Param<br>No.       | Symbol    | Charact                                                                | eristic                        |       | Min                                                                                                                                                                                                         | Тур | Мах              | Units | Conditions                               |  |

| TA10               | ТтхН      | TxCK High Time                                                         | Synchro<br>no preso            |       | Тсү + 20                                                                                                                                                                                                    |     |                  | ns    | Must also meet parameter TA15.           |  |

|                    |           |                                                                        | Synchro<br>with pres           |       | (Tcy + 20)/N                                                                                                                                                                                                |     | —                | ns    | N = prescale<br>value                    |  |

|                    |           |                                                                        | Asynchr                        | onous | 20                                                                                                                                                                                                          |     | —                | ns    | (1, 8, 64, 256)                          |  |

| TA11               | ΤτxL      | TxCK Low Time                                                          | Synchronous,<br>no prescaler   |       | (Tcy + 20)                                                                                                                                                                                                  | _   | —                | ns    | Must also meet parameter TA15.           |  |