Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 12KB (12K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc202t-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4 CPU Control Registers

## REGISTER 3-1: SR: CPU STATUS REGISTER

| R-0                  | R-0                                                                    | R/C-0                             | R/C-0                             | R-0                    | R/C-0              | R -0              | R/W-0          |

|----------------------|------------------------------------------------------------------------|-----------------------------------|-----------------------------------|------------------------|--------------------|-------------------|----------------|

| OA                   | OB                                                                     | SA <sup>(1)</sup>                 | SB <sup>(1)</sup>                 | OAB                    | SAB                | DA                | DC             |

| bit 15               |                                                                        |                                   |                                   |                        |                    |                   | bit 8          |

| R/W-0 <sup>(2)</sup> | R/W-0 <sup>(3)</sup>                                                   | R/W-0 <sup>(3)</sup>              | R-0                               | R/W-0                  | R/W-0              | R/W-0             | R/W-0          |

| R/W-0                | IPL<2:0> <sup>(2)</sup>                                                | K/W-0`'                           | R-0<br>RA                         | N                      | OV                 | Z                 | C              |

| bit 7                | IFL~2.0×()                                                             |                                   | RA                                | IN                     | 00                 | 2                 | bit (          |

| DIL 7                |                                                                        |                                   |                                   |                        |                    |                   |                |

| Legend:              |                                                                        |                                   |                                   |                        |                    |                   |                |

| C = Clear on         | ly bit                                                                 | R = Readable                      | e bit                             | U = Unimple            | mented bit, read   | as '0'            |                |

| S = Set only         | bit                                                                    | W = Writable                      | bit                               | -n = Value at          | POR                |                   |                |

| '1' = Bit is set     | t                                                                      | '0' = Bit is cle                  | ared                              | x = Bit is unk         | nown               |                   |                |

| bit 15               |                                                                        | ator A Overflov                   | v Statua bit                      |                        |                    |                   |                |

| DIL 15               |                                                                        | tor A overflow                    |                                   |                        |                    |                   |                |

|                      |                                                                        | tor A has not o                   |                                   |                        |                    |                   |                |

| bit 14               | <b>OB:</b> Accumula                                                    | ator B Overflow                   | v Status bit                      |                        |                    |                   |                |

|                      | - ///                                                                  | tor B overflowe                   |                                   |                        |                    |                   |                |

| bit 13               | bit 13 SA: Accumulator A Saturation 'Sticky' Status bit <sup>(1)</sup> |                                   |                                   |                        |                    |                   |                |

|                      | 1 = Accumula                                                           |                                   | ted or has bee                    | en saturated at        | some time          |                   |                |

| bit 12               |                                                                        | ator B Saturatio                  |                                   | tus bit <sup>(1)</sup> |                    |                   |                |

|                      | 1 = Accumula                                                           |                                   | ted or has bee                    | en saturated at        | some time          |                   |                |

| bit 11               |                                                                        |                                   |                                   | verflow Status         | bit                |                   |                |

|                      | 1 = Accumula                                                           | tors A or B have coumulators A    | ve overflowed                     |                        |                    |                   |                |

| bit 10               | SAB: SA    SI                                                          | 3 Combined A                      | ccumulator 'St                    | ticky' Status bit      | I                  |                   |                |

|                      | 1 = Accumula<br>0 = Neither A                                          | tors A or B are<br>ccumulator A c | e saturated or<br>or B are satura | have been sat          | urated at some     |                   | t              |

| <b>h</b> # 0         | -                                                                      |                                   | rea (not set).                    | Clearing this b        | it will clear SA a | na SB.            |                |

| bit 9                | <b>DA:</b> DO Loop<br>1 = DO loop in                                   |                                   |                                   |                        |                    |                   |                |

|                      | 0 = D0 loop in                                                         |                                   |                                   |                        |                    |                   |                |

| bit 8                | DC: MCU AL                                                             | J Half Carry/B                    | orrow bit                         |                        |                    |                   |                |

|                      | •                                                                      | ut from the 4th<br>sult occurred  | low-order bit (                   | for byte-sized of      | data) or 8th low-o | order bit (for wo | ord-sized data |

|                      | ,                                                                      | out from the 4 he result occur    |                                   | oit (for byte-siz      | ed data) or 8th    | low-order bit (1  | for word-sized |

| Note 1: Th           | nis bit can be rea                                                     | d or cleared (n                   | ot set).                          |                        |                    |                   |                |

| Le                   | ne IPL<2:0> bits<br>evel. The value in<br>L<3> = 1.                    |                                   |                                   |                        |                    |                   |                |

|                      |                                                                        |                                   |                                   |                        |                    |                   |                |

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

## 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ12MC201/202 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts, and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV), and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ12MC201/202 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

## 3.5.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

## 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.6 DSP Engine

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ12MC201/202 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB, and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed or unsigned DSP multiply (US)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACC-SAT)

A block diagram of the DSP engine is shown in Figure 3-3.

#### TABLE 3-1: DSP INSTRUCTIONS SUMMARY

| Instruction | Algebraic<br>Operation | ACC Write<br>Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJ12MC201/202 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable, and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJ12MC201/202 device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (Vss) and Master Clear (MCLR). This allows users to manufacture boards with unprogrammed devices, and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user application can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes).

## 5.1 Table Instructions and Flash Programming

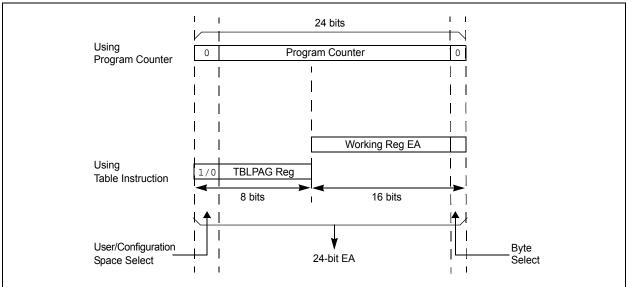

Regardless of the method used, all programming of Flash memory is done with the table-read and tablewrite instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits <7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits <15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits <23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

## FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; Se | et up NVMCO | N for row programming opera   | ations                                                                            |

|------|-------------|-------------------------------|-----------------------------------------------------------------------------------|

|      | MOV         | #0x4001, W0                   | ;                                                                                 |

|      | MOV         | W0, NVMCON                    | ; Initialize NVMCON                                                               |

| ; Se | et up a poi | nter to the first program m   | memory location to be written                                                     |

| ; pr | rogram memo | ry selected, and writes ena   | abled                                                                             |

|      | MOV         | #0x0000, W0                   | i                                                                                 |

|      | MOV         | W0, TBLPAG                    | ; Initialize PM Page Boundary SFR                                                 |

|      | MOV         | #0x6000, W0                   | ; An example program memory address                                               |

| ; Pe | erform the  | TBLWT instructions to write   | e the latches                                                                     |

| ; Ot | h_program_  | word                          |                                                                                   |

|      | MOV         | #LOW_WORD_0, W2               | i                                                                                 |

|      |             | <pre>#HIGH_BYTE_0, W3</pre>   | i                                                                                 |

|      | TBLWTL      | W2, [W0]                      | ; Write PM low word into program latch                                            |

|      | TBLWTH      | W3, [W0++]                    | ; Write PM high byte into program latch                                           |

| ; 1s | st_program_ |                               |                                                                                   |

|      |             | #LOW_WORD_1, W2               | ;                                                                                 |

|      |             | #HIGH_BYTE_1, W3              | ;                                                                                 |

|      |             | W2, [W0]                      | ; Write PM low word into program latch                                            |

|      |             | W3, [W0++]                    | ; Write PM high byte into program latch                                           |

| ; 2  | 2nd_program | —                             |                                                                                   |

|      |             | #LOW_WORD_2, W2               | i                                                                                 |

|      |             | <pre>#HIGH_BYTE_2, W3</pre>   | ;                                                                                 |

|      |             | W2, [W0]                      | ; Write PM low word into program latch                                            |

|      |             | W3, [W0++]                    | ; Write PM high byte into program latch                                           |

|      | •           |                               |                                                                                   |

|      | •           |                               |                                                                                   |

|      | •           |                               |                                                                                   |

| 1 63 | 3rd_program | —                             |                                                                                   |

|      | MOV         | #LOW_WORD_31, W2              | ;                                                                                 |

|      |             | #HIGH_BYTE_31, W3<br>W2, [W0] | /                                                                                 |

|      |             | W2, [W0]<br>W3, [W0++]        | ; Write PM low word into program latch<br>; Write PM high byte into program latch |

|      | IPTMIH      | W3, [WU++]                    | , write PM High byte into program laten                                           |

## EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | <pre>; Block all interrupts with priority &lt;7 ; for next 5 instructions</pre> |

|------|-------------|---------------------------------------------------------------------------------|

| MOV  | #0x55, W0   |                                                                                 |

| MOV  | W0, NVMKEY  | ; Write the 55 key                                                              |

| MOV  | #0xAA, W1   | ;                                                                               |

| MOV  | W1, NVMKEY  | ; Write the AA key                                                              |

| BSET | NVMCON, #WR | ; Start the erase sequence                                                      |

| NOP  |             | ; Insert two NOPs after the                                                     |

| NOP  |             | ; erase command is asserted                                                     |

|      |             |                                                                                 |

## REGISTER 7-9: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled0 = Interrupt request not enabled

- bit 0 **INTOIE:** External Interrupt 0 Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0                                | U-1                                                                                         | U-0                                                                           | U-0                                                          | U-0                      | U-1  | U-0             | U-0   |

|------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------|------|-----------------|-------|

| —                                  | —                                                                                           | —                                                                             |                                                              | —                        |      | _               | —     |

| bit 15                             |                                                                                             |                                                                               |                                                              |                          |      |                 | bit 8 |

|                                    |                                                                                             |                                                                               |                                                              |                          |      |                 |       |

| U-0                                | R/W-1                                                                                       | R/W-0                                                                         | R/W-0                                                        | U-0                      | U-0  | U-0             | U-0   |

| —                                  |                                                                                             | INT2IP<2:0>                                                                   |                                                              | —                        | —    | —               | —     |

| bit 7                              |                                                                                             |                                                                               |                                                              |                          |      |                 | bit 0 |

|                                    |                                                                                             |                                                                               |                                                              |                          |      |                 |       |

| Legend:                            |                                                                                             |                                                                               |                                                              |                          |      |                 |       |

| R = Readable                       | e bit                                                                                       | W = Writable I                                                                | W = Writable bit U = Unimplemented bit, read as '0'          |                          |      |                 |       |

| -n = Value at POR '1' = Bit is set |                                                                                             |                                                                               | '0' = Bit is cleared x = Bit is unknown                      |                          |      |                 |       |

|                                    | PUR                                                                                         | i = Bit is set                                                                |                                                              | $0^{\circ}$ = Bit is cle | ared | x = Bit is unkn | nown  |

|                                    | PUR                                                                                         | i = Bit is set                                                                |                                                              | $0^{\circ}$ = Bit is cle | ared | x = Bit is unkr | iown  |

| bit 15-7                           |                                                                                             | ted: Read as '0                                                               |                                                              | "U" = Bit is cle         | ared | x = Bit is unkr | iown  |

|                                    | Unimplemen                                                                                  |                                                                               | )'                                                           |                          | ared | x = Bit is unkr | iown  |

| bit 15-7                           | Unimplemen<br>INT2IP<2:0>:                                                                  | ted: Read as 'o                                                               | )'<br>upt 2 Priority                                         | bits                     | ared | x = Bit is unkr | iown  |

| bit 15-7                           | Unimplemen<br>INT2IP<2:0>:                                                                  | ted: Read as 'd<br>External Interr                                            | )'<br>upt 2 Priority                                         | bits                     | ared | x = Bit is unkr | iown  |

| bit 15-7                           | Unimplemen<br>INT2IP<2:0>:                                                                  | ted: Read as 'd<br>External Interr                                            | )'<br>upt 2 Priority                                         | bits                     | ared | x = Bit is unkr | iown  |

| bit 15-7                           | Unimplement<br>INT2IP<2:0>:<br>111 = Interrup<br>•<br>•                                     | ted: Read as 'o<br>External Interr<br>ot is priority 7 (h                     | )'<br>upt 2 Priority                                         | bits                     | ared | x = Bit is unkr | iown  |

| bit 15-7                           | Unimplement<br>INT2IP<2:0>:<br>111 = Interrup<br>•<br>•<br>•<br>001 = Interrup              | ted: Read as 'c<br>External Interr<br>ot is priority 7 (h<br>ot is priority 1 | <sub>o</sub> '<br>upt 2 Priority<br>nighest priorit          | bits                     | ared | x = Bit is unkr | iown  |

| bit 15-7                           | Unimplement<br>INT2IP<2:0>:<br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup | ted: Read as 'o<br>External Interr<br>ot is priority 7 (h                     | <sub>o</sub> ,<br>upt 2 Priority<br>nighest priorit<br>abled | bits                     | ared | x = Bit is unkr | iown  |

## REGISTER 7-19: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

## TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                 | Oscillator<br>Source | POSCMD<1:0> | FNOSC<2:0> | Note |

|-------------------------------------------------|----------------------|-------------|------------|------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)   | Internal             | xx          | 111        | 1, 2 |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) | Internal             | xx          | 110        | 1    |

| Low-Power RC Oscillator (LPRC)                  | Internal             | xx          | 101        | 1    |

| Secondary (Timer1) Oscillator (SOSC)            | Secondary            | xx          | 100        | 1    |

| Primary Oscillator (HS) with PLL (HSPLL)        | Primary              | 10          | 011        | _    |

| Primary Oscillator (XT) with PLL (XTPLL)        | Primary              | 01          | 011        | _    |

| Primary Oscillator (EC) with PLL (ECPLL)        | Primary              | 00          | 011        | 1    |

| Primary Oscillator (HS)                         | Primary              | 10          | 010        | _    |

| Primary Oscillator (XT)                         | Primary              | 01          | 010        | —    |

| Primary Oscillator (EC)                         | Primary              | 00          | 010        | 1    |

| Fast RC Oscillator with PLL (FRCPLL)            | Internal             | xx          | 001        | 1    |

| Fast RC Oscillator (FRC)                        | Internal             | xx          | 000        | 1    |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

**2:** This is the default oscillator mode for an unprogrammed (erased) device.

## 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 10.** "I/O Ports" (DS70193) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR, and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 10.1 Parallel I/O (PIO) Ports

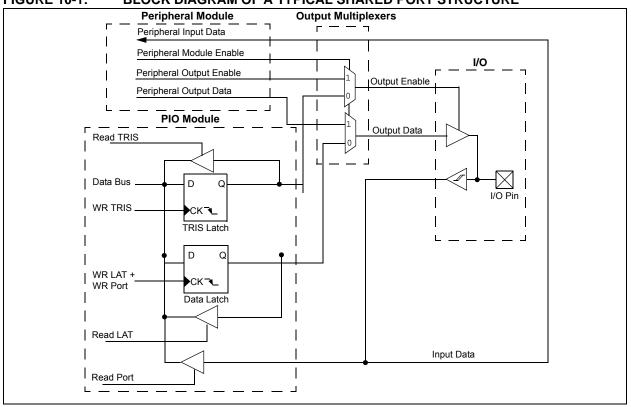

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. This means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

© 2007-2011 Microchip Technology Inc.

## 10.4 Peripheral Pin Select

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

#### 10.4.1 AVAILABLE PINS

The peripheral pin select feature is used with a range of up to 16 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

#### 10.4.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

### 10.4.2.1 Input Mapping

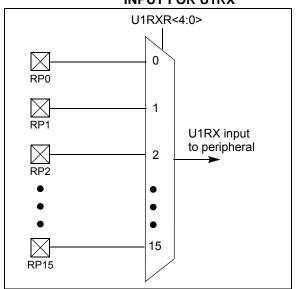

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-13). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

Figure 10-2 Illustrates remappable pin selection for U1RX input.

| Note: | For input mapping only, the Peripheral Pin |

|-------|--------------------------------------------|

|       | Select (PPS) functionality does not have   |

|       | priority over the TRISx settings. There-   |

|       | fore, when configuring the RPx pin for     |

|       | input, the corresponding bit in the TRISx  |

|       | register must also be configured for input |

|       | (i.e., set to '1').                        |

#### FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

| Function | RPnR<4:0> | Output Name                             |

|----------|-----------|-----------------------------------------|

| NULL     | 00000     | RPn tied to default port pin            |

| U1TX     | 00011     | RPn tied to UART1 Transmit              |

| U1RTS    | 00100     | RPn tied to UART1 Ready To Send         |

| SDO1     | 00111     | RPn tied to SPI1 Data Output            |

| SCK10UT  | 01000     | RPn tied to SPI1 Clock Output           |

| SS1OUT   | 01001     | RPn tied to SPI1 Slave Select Output    |

| OC1      | 10010     | RPn tied to Output Compare 1            |

| OC2      | 10011     | RPn tied to Output Compare 2            |

| UPDN     | 11010     | RPn tied to QEI direction (UPDN) status |

### TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PIN (RPn)

#### 10.4.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33FJ12MC201/202 devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit pin select lock

## 10.4.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |  |  |  |  |  |  |  |

|       | See MPLAB IDE Help for more<br>information.                                                      |  |  |  |  |  |  |  |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the peripheral pin selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

### 10.4.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset will be triggered.

#### 10.4.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<IOL1WAY>) configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

## 10.5 Peripheral Pin Select Registers

The dsPIC33FJ12MC201/202 family of devices implement 21 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (13)

- Output Remappable Peripheral Registers (8)

Note: Input and Output Register values can only be changed if OSCCON<IOLOCK> = 0. See Section 10.4.3.1 "Control Register Lock" for a specific command sequence.

## REGISTER 10-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0           | U-0                                          | U-0                             | R/W-1         | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|---------------|----------------------------------------------|---------------------------------|---------------|------------------|-----------------|-----------------|-------|

| _             | _                                            | _                               |               |                  | IC2R<4:0>       |                 |       |

| bit 15        |                                              |                                 |               |                  |                 |                 | bit 8 |

| U-0           | U-0                                          | U-0                             | R/W-1         | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| _             | _                                            | IC1R<4:0>                       |               |                  |                 |                 |       |

| bit 7         |                                              |                                 |               |                  |                 |                 | bit 0 |

| Legend:       |                                              |                                 |               |                  |                 |                 |       |

| R = Readabl   | e bit                                        | W = Writable b                  | bit           | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at | POR                                          | '1' = Bit is set                |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|               | 11111 = Inpu<br>01111 = Inpu                 | t tied to RP15<br>t tied to RP1 |               |                  |                 |                 |       |

| bit 7-5       | Unimplement                                  | ted: Read as '0                 | ,             |                  |                 |                 |       |

| bit 4-0       | IC1R<4:0>: A<br>11111 = Inpu<br>01111 = Inpu | t tied to RP15<br>t tied to RP1 | oture 1 (IC1) | to the correspo  | onding RPn pir  | 1               |       |

| R/W-0        | U-0                          | R/W-0                                 | U-0            | U-0              | U-0              | U-0                 | U-0    |

|--------------|------------------------------|---------------------------------------|----------------|------------------|------------------|---------------------|--------|

| PTEN         |                              | PTSIDL                                |                | —                |                  | —                   | _      |

| bit 15       |                              |                                       |                |                  |                  |                     | bit 8  |

|              |                              |                                       |                |                  |                  |                     |        |

| R/W-0        | R/W-0                        | R/W-0                                 | R/W-0          | R/W-0            | R/W-0            | R/W-0               | R/W-0  |

| L:1 7        | PTOPS                        | 5<3:0>                                |                | PICK             | PS<1:0>          | PTMOD               | -      |

| bit 7        |                              |                                       |                |                  |                  |                     | bit 0  |

| Legend:      |                              |                                       |                |                  |                  |                     |        |

| R = Readat   | ole bit                      | W = Writable I                        | oit            | U = Unimpler     | nented bit, read | d as '0'            |        |

| -n = Value a | at POR                       | '1' = Bit is set                      |                | '0' = Bit is cle | ared             | x = Bit is unkno    | own    |

|              |                              |                                       |                |                  |                  |                     |        |

| bit 15       | PTEN: PWM                    | Time Base Tim                         | er Enable bit  |                  |                  |                     |        |

|              | 1 = PWM tim                  |                                       |                |                  |                  |                     |        |

|              | 0 = PWM tim                  |                                       |                |                  |                  |                     |        |

| bit 14       | -                            | ted: Read as '0                       |                |                  |                  |                     |        |

| bit 13       |                              | M Time Base St                        | •              |                  |                  |                     |        |

|              |                              | e base halts in (<br>e base runs in ( |                |                  |                  |                     |        |

| bit 12-8     |                              | ted: Read as '0                       |                |                  |                  |                     |        |

| bit 7-4      | •                            | ·: PWM Time Ba                        |                | ostscale Select  | bits             |                     |        |

|              | 1111 <b>= 1:16</b>           |                                       | •              |                  |                  |                     |        |

|              | •                            |                                       |                |                  |                  |                     |        |

|              | •                            |                                       |                |                  |                  |                     |        |

|              | •                            |                                       |                |                  |                  |                     |        |

|              | 0001 = 1:2 p<br>0000 = 1:1 p |                                       |                |                  |                  |                     |        |

| bit 3-2      | PTCKPS<1:0                   | D>: PWM Time I                        | Base Input C   | lock Prescale S  | elect bits       |                     |        |

|              | 11 = PWM tir                 | me base input c                       | ock period is  | 64 TCY (1:64 p   | orescale)        |                     |        |

|              |                              | me base input c                       |                |                  |                  |                     |        |

|              |                              | me base input c<br>me base input c    | •              | • •              | ,                |                     |        |

| bit 1-0      |                              | >: PWM Time B                         | •              | • •              | ale)             |                     |        |

| bit 1-0      |                              | me base operate                       |                |                  | n Count mode v   | vith interrupts for | double |

|              | 10 = PWM tir                 | ne base operate                       |                |                  | n Count mode     |                     |        |

|              |                              | ne base operate                       | •              |                  |                  |                     |        |

|              | 00 = PWM tir                 | ne base operate                       | es in a Free-l | Running mode     |                  |                     |        |

## REGISTER 15-1: PxTCON: PWM TIME BASE CONTROL REGISTER

## REGISTER 15-4: PxSECMP: SPECIAL EVENT COMPARE REGISTER

| R/W-0                  | R/W-0      | R/W-0               | R/W-0      | R/W-0                  | R/W-0                | R/W-0           | R/W-0 |

|------------------------|------------|---------------------|------------|------------------------|----------------------|-----------------|-------|

| SEVTDIR <sup>(1)</sup> |            |                     | ;          | SEVTCMP<14:8           | <sub>}&gt;</sub> (2) |                 |       |

| bit 15                 |            |                     |            |                        |                      |                 | bit 8 |

| R/W-0                  | R/W-0      | R/W-0               | R/W-0      | R/W-0                  | R/W-0                | R/W-0           | R/W-0 |

| R/W-U                  | R/W-0      | R/W-0               | -          |                        | R/W-0                | R/W-U           | R/W-U |

|                        |            |                     | SEVTC      | MP<7:0> <sup>(2)</sup> |                      |                 |       |

| bit 7                  |            |                     |            |                        |                      |                 | bit 0 |

| Legend:                |            |                     |            |                        |                      |                 |       |

| R = Readable           | bit        | W = Writable bi     | t          | U = Unimpler           | nented bit, rea      | ad as '0'       |       |

| -n = Value at F        | POR        | '1' = Bit is set    |            | '0' = Bit is cle       | ared                 | x = Bit is unkr | nown  |

|                        |            |                     |            |                        |                      |                 |       |

| bit 15                 | SEVTDIR: S | Special Event Trigg | ger Time B | ase Direction bit      | (1)                  |                 |       |

igg

1 = A Special Event Trigger will occur when the PWM time base is counting down

0 = A Special Event Trigger will occur when the PWM time base is counting up

SEVTCMP<14:0>: Special Event Compare Value bits<sup>(2)</sup> bit 14-0

Note 1: SEVTDIR is compared with PTDIR (PxTMR<15>) to generate the Special Event Trigger.

2: PxSECMP<14:0> is compared with PxTMR<14:0> to generate the Special Event Trigger.

| DC CHARACT       | ERISTICS               |            | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |                  |        |                        |  |  |  |

|------------------|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|------------------------|--|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Max        | Units                                                                                                                                                                                                    | ts Conditions    |        |                        |  |  |  |

| Idle Current (I  | DLE): Core OF          | F Clock ON | Base Curren                                                                                                                                                                                              | t <sup>(2)</sup> |        |                        |  |  |  |

| DC40d            | 3                      | 25         | mA                                                                                                                                                                                                       | -40°C            |        |                        |  |  |  |

| DC40a            | 3                      | 25         | mA                                                                                                                                                                                                       | +25°C            |        | 10 MIPS <sup>(3)</sup> |  |  |  |

| DC40b            | 3                      | 25         | mA                                                                                                                                                                                                       | +85°C            | 3.3V   |                        |  |  |  |

| DC40c            | 3                      | 25         | mA                                                                                                                                                                                                       | +125°C           |        |                        |  |  |  |

| DC41d            | 4                      | 25         | mA                                                                                                                                                                                                       | -40°C            |        |                        |  |  |  |

| DC41a            | 4                      | 25         | mA                                                                                                                                                                                                       | +25°C            | 3.3V   | 16 MIPS <sup>(3)</sup> |  |  |  |

| DC41b            | 5                      | 25         | mA                                                                                                                                                                                                       | +85°C            |        | 10 MIPS(*)             |  |  |  |

| DC41c            | 5                      | 25         | mA                                                                                                                                                                                                       | +125°C           |        |                        |  |  |  |

| DC42d            | 6                      | 25         | mA                                                                                                                                                                                                       | -40°C            |        | 20 MIPS <sup>(3)</sup> |  |  |  |

| DC42a            | 6                      | 25         | mA                                                                                                                                                                                                       | +25°C            | 2.21/  |                        |  |  |  |

| DC42b            | 7                      | 25         | mA                                                                                                                                                                                                       | +85°C            | - 3.3V |                        |  |  |  |

| DC42c            | 7                      | 25         | mA                                                                                                                                                                                                       | +125°C           |        |                        |  |  |  |

| DC43a            | 9                      | 25         | mA                                                                                                                                                                                                       | +25°C            |        |                        |  |  |  |

| DC43d            | 9                      | 25         | mA                                                                                                                                                                                                       | -40°C            | 2.2)/  | 30 MIPS <sup>(3)</sup> |  |  |  |

| DC43b            | 9                      | 25         | mA                                                                                                                                                                                                       | +85°C            | - 3.3V | 30 MIPS(%)             |  |  |  |

| DC43c            | 9                      | 25         | mA                                                                                                                                                                                                       | +125°C           | ]      |                        |  |  |  |

| DC44d            | 10                     | 25         | mA                                                                                                                                                                                                       | -40°C            |        |                        |  |  |  |

| DC44a            | 10                     | 25         | mA                                                                                                                                                                                                       | +25°C            | 2.2)/  |                        |  |  |  |

| DC44b            | 10                     | 25         | mA                                                                                                                                                                                                       | +85°C            | - 3.3V | 40 MIPS                |  |  |  |

| DC44c            | 10                     | 25         | mA                                                                                                                                                                                                       | +125°C           | 1      |                        |  |  |  |

#### TABLE 24-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: Base IIDLE current is measured with core off, clock on and all modules turned off. Peripheral Module Disable SFR registers are zeroed. All I/O pins are configured as inputs and pulled to Vss.

3: These parameters are characterized, but not tested in manufacturing.

## TABLE 24-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |   |     |   |                           |  |

|--------------------|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|---------------------------|--|

| Param<br>No.       | Symbol | Characteristic      | Min Typ Max Units Conditions                                                                                                                                                                             |   |     |   |                           |  |

|                    | Vol    | Output Low Voltage  |                                                                                                                                                                                                          |   |     |   |                           |  |

| DO10               |        | I/O ports           | —                                                                                                                                                                                                        | — | 0.4 | V | IOL = 2 mA, VDD = 3.3V    |  |

| DO16               |        | OSC2/CLKO           | — — 0.4 V IOL = 2 mA, VDD = 3.3V                                                                                                                                                                         |   |     |   |                           |  |

|                    | Voн    | Output High Voltage |                                                                                                                                                                                                          |   |     |   |                           |  |

| DO20               |        | I/O ports           | 2.40 — V IOH = -2.3 mA, VDD = 3.3V                                                                                                                                                                       |   |     |   |                           |  |

| DO26               |        | OSC2/CLKO           | 2.41                                                                                                                                                                                                     | — | —   | V | Іон = -1.3 mA, Vdd = 3.3V |  |

## TABLE 24-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS Standard Operating temp |        |                                            |       |                    |     |                    |       |            |

|--------------------------------------------|--------|--------------------------------------------|-------|--------------------|-----|--------------------|-------|------------|

| Param<br>No.                               | Symbol | Character                                  | istic | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Units | Conditions |

| BO10                                       | VBOR   | BOR Event on VDD transition<br>high-to-low |       | 2.40               | _   | 2.55               | V     | Vdd        |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

## TABLE 24-40: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA       | RACTER  | ISTICS                       |                           | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |       |                        |  |

|--------------|---------|------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|

| Param<br>No. | Symbol  | Characte                     | eristic <sup>(3)</sup>    | Min <sup>(1)</sup>                                                                                                                                                                                   | Max  | Units | Conditions             |  |

| IM10         | TLO:SCL | Clock Low Time               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | μs    | _                      |  |

|              |         |                              | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | μs    | _                      |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                      |      | μs    | —                      |  |

| IM11         | THI:SCL | Clock High Time              | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      |      | μs    | —                      |  |

|              |         |                              | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      |      | μs    | —                      |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                      |      | μs    | —                      |  |

| IM20         | TF:SCL  | SDAx and SCLx                | 100 kHz mode              | —                                                                                                                                                                                                    | 300  | ns    | CB is specified to be  |  |

|              |         | Fall Time                    | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                          | 300  | ns    | from 10 to 400 pF      |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                    | 100  | ns    |                        |  |

| IM21         | TR:SCL  | SDAx and SCLx                | 100 kHz mode              | —                                                                                                                                                                                                    | 1000 | ns    | CB is specified to be  |  |

|              |         | Rise Time                    | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                          | 300  | ns    | from 10 to 400 pF      |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                                      | 300  | ns    |                        |  |

| IM25         | TSU:DAT | Data Input                   | 100 kHz mode              | 250                                                                                                                                                                                                  |      | ns    | _                      |  |

|              |         | Setup Time                   | 400 kHz mode              | 100                                                                                                                                                                                                  |      | ns    |                        |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                                                                   | —    | ns    |                        |  |

| IM26         | THD:DAT | Data Input<br>Hold Time      | 100 kHz mode              | 0                                                                                                                                                                                                    | —    | μs    | _                      |  |

|              |         |                              | 400 kHz mode              | 0                                                                                                                                                                                                    | 0.9  | μs    |                        |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                                                                  |      | μs    |                        |  |

| IM30         | TSU:STA | Start Condition              | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | μs    | Only relevant for      |  |

|              |         | Setup Time                   | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | μs    | Repeated Start         |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | μs    | condition              |  |

| IM31         | THD:STA | Start Condition<br>Hold Time | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | μs    | After this period the  |  |

|              |         |                              | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | μs    | first clock pulse is   |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | μs    | generated              |  |

| IM33         | Tsu:sto | Stop Condition               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | μs    | _                      |  |

|              |         | Setup Time                   | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      |      | μs    |                        |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                      |      | μs    |                        |  |

| IM34         | THD:STO | Stop Condition               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      |      | ns    | —                      |  |

|              |         | Hold Time                    | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | ns    | -                      |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                                      | —    | ns    | -                      |  |