#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 12KB (12K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

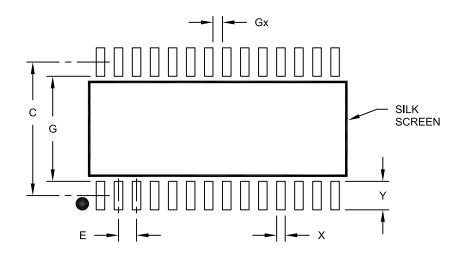

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12mc202t-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

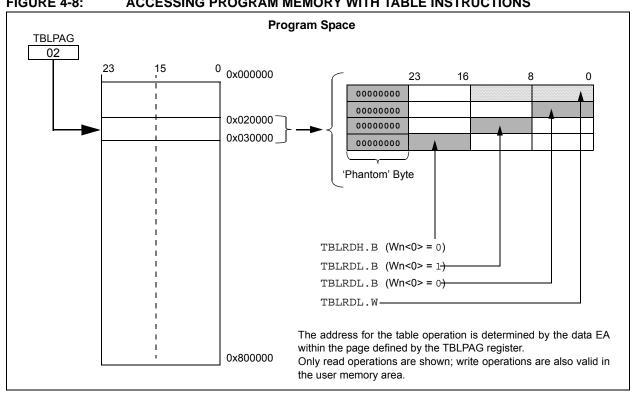

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### FIGURE 4-8: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Interrupts" (DS70184) of the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ12MC201/202 interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJ12MC201/202 CPU. It has the following features:

- Up to eight processor exceptions and software traps

- · Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

dsPIC33FJ12MC201/202 devices implement up to 26 unique interrupts and 4 nonmaskable traps. These are summarized in Table 7-1 and Table 7-2.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a way to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications to facilitate evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJ12MC201/202 device clears its registers in response to a Reset, forcing the PC to zero. The digital signal controller then begins program execution at location 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 7-10: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| U-0             | U-0             | R/W-0                              | U-0        | 11.0             | U-0             | 11.0            | 11.0    |

|-----------------|-----------------|------------------------------------|------------|------------------|-----------------|-----------------|---------|

|                 |                 |                                    | 0-0        | U-0              | 0-0             | U-0             | U-0     |

|                 |                 | INT2IE                             | —          |                  | _               |                 |         |

| bit 15          |                 |                                    |            |                  |                 |                 | bit 8   |

| r               |                 |                                    |            |                  |                 |                 |         |

| R/W-0           | R/W-0           | U-0                                | R/W-0      | R/W-0            | U-0             | R/W-0           | R/W-0   |

| IC8IE           | IC7IE           | —                                  | INT1IE     | CNIE             | —               | MI2C1IE         | SI2C1IE |

| bit 7           |                 |                                    |            |                  |                 |                 | bit 0   |

|                 |                 |                                    |            |                  |                 |                 |         |

| Legend:         |                 |                                    |            |                  |                 |                 |         |

| R = Readable I  | bit             | W = Writable                       | bit        | U = Unimpler     | mented bit, rea | ad as '0'       |         |

| -n = Value at P | OR              | '1' = Bit is set                   |            | '0' = Bit is cle | ared            | x = Bit is unkr | Iown    |

|                 |                 |                                    |            |                  |                 |                 |         |

| bit 15-14       | -               | ted: Read as '                     |            |                  |                 |                 |         |

| bit 13          |                 | rnal Interrupt 2                   |            |                  |                 |                 |         |

|                 |                 | request enabled                    |            |                  |                 |                 |         |

| bit 12-8        | •               | request not ena                    |            |                  |                 |                 |         |

|                 | -               | ted: Read as '                     |            |                  |                 |                 |         |

| bit 7           |                 | Capture Channe                     |            | Enable bit       |                 |                 |         |

|                 |                 | request enableo<br>request not ena |            |                  |                 |                 |         |

| bit 6           | -               | Capture Channe                     |            | Enable bit       |                 |                 |         |

|                 | -               | request enabled                    | -          |                  |                 |                 |         |

|                 | 0 = Interrupt i | request not ena                    | bled       |                  |                 |                 |         |

| bit 5           | Unimplemen      | ted: Read as '                     | )'         |                  |                 |                 |         |

| bit 4           | INT1IE: Exter   | rnal Interrupt 1                   | Enable bit |                  |                 |                 |         |

|                 |                 | request enabled                    |            |                  |                 |                 |         |

|                 | •               | request not ena                    |            |                  |                 |                 |         |

| bit 3           |                 | Change Notifica                    |            | Enable bit       |                 |                 |         |

|                 |                 | request enabled                    |            |                  |                 |                 |         |

| <b>h</b> # 0    | -               | request not ena                    |            |                  |                 |                 |         |

| bit 2           | •               | ted: Read as '                     |            |                  |                 |                 |         |

| bit 1           |                 | 1 Master Even                      | •          | able bit         |                 |                 |         |

|                 |                 | request enableo<br>request not ena |            |                  |                 |                 |         |

| bit 0           | -               | 1 Slave Events                     |            | hle hit          |                 |                 |         |

| Situ            |                 | request enabled                    | •          |                  |                 |                 |         |

|                 |                 | request not ena                    |            |                  |                 |                 |         |

|                 | ·               |                                    |            |                  |                 |                 |         |

#### REGISTER 7-21: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0          | R/W-1        | R/W-0                      | R/W-0          | U-0                  | U-0              | U-0                | U-0   |  |  |  |

|--------------|--------------|----------------------------|----------------|----------------------|------------------|--------------------|-------|--|--|--|

|              |              | FLTA1IP<2:0>               |                |                      | —                |                    | —     |  |  |  |

| bit 15       |              |                            |                |                      | •                |                    | bit 8 |  |  |  |

|              |              |                            |                |                      |                  |                    |       |  |  |  |

| U-0          | U-0          | U-0                        | U-0            | U-0                  | U-0              | U-0                | U-0   |  |  |  |

|              |              | _                          | _              |                      | _                |                    | _     |  |  |  |

| bit 7        |              |                            |                |                      |                  |                    | bit 0 |  |  |  |

|              |              |                            |                |                      |                  |                    |       |  |  |  |

| Legend:      |              |                            |                |                      |                  |                    |       |  |  |  |

| R = Readab   | le bit       | W = Writable               | bit            | U = Unimpler         | mented bit, read | l as '0'           |       |  |  |  |

| -n = Value a | t POR        | '1' = Bit is set           |                | '0' = Bit is cleared |                  | x = Bit is unknown |       |  |  |  |

|              |              |                            |                |                      |                  |                    |       |  |  |  |

| bit 15       | Unimpleme    | ented: Read as '           | כי             |                      |                  |                    |       |  |  |  |

| bit 14-12    | FLTA1IP<2:   | : <b>0&gt;:</b> PWM1 Fault | A Interrupt F  | riority bits         |                  |                    |       |  |  |  |

|              | 111 = Interr | upt is priority 7 (        | highest priori | y interrupt)         |                  |                    |       |  |  |  |

|              | •            |                            | •              |                      |                  |                    |       |  |  |  |

|              | •            |                            |                |                      |                  |                    |       |  |  |  |

|              | •            |                            |                |                      |                  |                    |       |  |  |  |

|              | 001 = Interr | upt is priority 1          |                |                      |                  |                    |       |  |  |  |

|              |              | upt source is dis          | abled          |                      |                  |                    |       |  |  |  |

| bit 11-0     | Unimpleme    | Unimplemented: Read as '0' |                |                      |                  |                    |       |  |  |  |

|              | Ommpicine    | meu. Noau as               | J              |                      |                  |                    |       |  |  |  |

#### REGISTER 7-22: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | U-0   | U-0                 | U-0   | U-0 | U-0 | U-0      | U-0      |

|--------|-------|---------------------|-------|-----|-----|----------|----------|

| —      | _     | —                   | _     | —   | —   | -        | —        |

| bit 15 |       |                     |       |     |     |          | bit 8    |

|        |       |                     |       |     |     |          |          |

| 11.0   |       |                     |       |     |     |          |          |

| U-0    | R/W-1 | R/W-0               | R/W-0 | U-0 | U-0 | U-0      | U-0      |

|        | R/W-1 | R/W-0<br>U1EIP<2:0> | R/W-0 |     | 0-0 | <u> </u> | <u> </u> |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

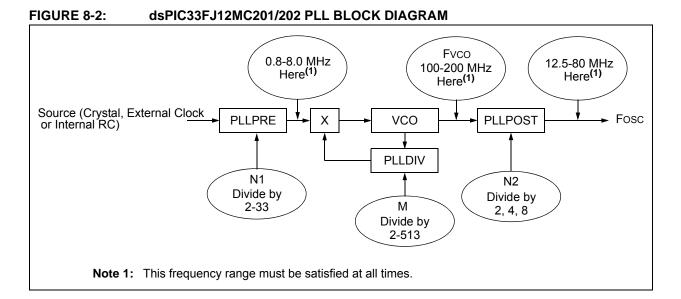

## 8.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides significant flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 8-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3,

... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected in the range of 0.8 MHz to 8 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor 'M,' by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor 'N2.' This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4, or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25 to 40 MIPS.

For output 'FIN' on a primary oscillator, or FRC oscillator, the PLL output 'FOSC' is given by Equation 8-2.

#### EQUATION 8-2: Fosc CALCULATION

$$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$$

For example, suppose a 10 MHz crystal is being used with the selected oscillator mode of XT with PLL.

- If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

- If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

#### EQUATION 8-3: XT WITH PLL MODE EXAMPLE

$$F_{CY} = \frac{F_{OSC}}{2} = \frac{1}{2} \left( \frac{10000000 \cdot 32}{2 \cdot 2} \right) = 40 \text{ MIPS}$$

## REGISTER 8-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(2)</sup>

| U-0             | U-0                       | U-0                              | U-0                       | U-0              | U-0              | U-0             | U-0   |  |  |

|-----------------|---------------------------|----------------------------------|---------------------------|------------------|------------------|-----------------|-------|--|--|

| _               | _                         | _                                |                           |                  |                  | _               |       |  |  |

| bit 15          |                           |                                  |                           |                  |                  |                 | bit 8 |  |  |

| U-0             | U-0                       | R/W-0                            | R/W-0                     | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

|                 | — TUN<5:0> <sup>(1)</sup> |                                  |                           |                  |                  |                 |       |  |  |

| bit 7           |                           |                                  |                           |                  |                  |                 | bit 0 |  |  |

|                 |                           |                                  |                           |                  |                  |                 |       |  |  |

| Legend:         |                           |                                  |                           |                  |                  |                 |       |  |  |

| R = Readable    | bit                       | W = Writable                     | bit                       | U = Unimpler     | mented bit, read | d as '0'        |       |  |  |

| -n = Value at F | POR                       | '1' = Bit is set                 |                           | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |

|                 |                           |                                  |                           |                  |                  |                 |       |  |  |

| bit 15-6        | Unimplemen                | ted: Read as '                   | o'                        |                  |                  |                 |       |  |  |

| bit 5-0         | TUN<5:0>: F               | RC Oscillator T                  | uning bits <sup>(1)</sup> |                  |                  |                 |       |  |  |

|                 |                           | nter frequency                   |                           |                  |                  |                 |       |  |  |

|                 | 011110 <b>= Ce</b>        | nter frequency                   | +11.25% (8.2              | 20 MHz)          |                  |                 |       |  |  |

|                 | •                         |                                  |                           |                  |                  |                 |       |  |  |

|                 | •                         |                                  |                           |                  |                  |                 |       |  |  |

|                 | 000001 <b>= Ce</b>        | nter frequency                   | +0.375% (7.4              | I0 MHz)          |                  |                 |       |  |  |

|                 |                           | nter frequency                   | •                         | ,                |                  |                 |       |  |  |

|                 | 111111 <b>= Ce</b>        | nter frequency                   | -0.375% (7.3              | 45 MHz)          |                  |                 |       |  |  |

|                 | •                         |                                  |                           |                  |                  |                 |       |  |  |

|                 | •                         |                                  |                           |                  |                  |                 |       |  |  |

|                 |                           | nter frequency<br>nter frequency |                           |                  |                  |                 |       |  |  |

- **Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

- 2: This register is reset only on a Power-on Reset (POR).

| Function | RPnR<4:0> | Output Name                             |

|----------|-----------|-----------------------------------------|

| NULL     | 00000     | RPn tied to default port pin            |

| U1TX     | 00011     | RPn tied to UART1 Transmit              |

| U1RTS    | 00100     | RPn tied to UART1 Ready To Send         |

| SDO1     | 00111     | RPn tied to SPI1 Data Output            |

| SCK10UT  | 01000     | RPn tied to SPI1 Clock Output           |

| SS1OUT   | 01001     | RPn tied to SPI1 Slave Select Output    |

| OC1      | 10010     | RPn tied to Output Compare 1            |

| OC2      | 10011     | RPn tied to Output Compare 2            |

| UPDN     | 11010     | RPn tied to QEI direction (UPDN) status |

#### TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PIN (RPn)

#### 10.4.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33FJ12MC201/202 devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit pin select lock

## 10.4.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |

|-------|--------------------------------------------------------------------------------------------------|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |

|       | See MPLAB IDE Help for more<br>information.                                                      |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the peripheral pin selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 10.4.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset will be triggered.

#### 10.4.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<IOL1WAY>) configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

#### 10.5 Peripheral Pin Select Registers

The dsPIC33FJ12MC201/202 family of devices implement 21 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (13)

- Output Remappable Peripheral Registers (8)

Note: Input and Output Register values can only be changed if OSCCON<IOLOCK> = 0. See Section 10.4.3.1 "Control Register Lock" for a specific command sequence.

### REGISTER 10-10: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| U-0           | U-0                                                    | U-0              | U-0         | U-0                                     | U-0            | U-0   | U-0   |  |  |

|---------------|--------------------------------------------------------|------------------|-------------|-----------------------------------------|----------------|-------|-------|--|--|

| _             | _                                                      | —                | —           | —                                       |                | —     | —     |  |  |

| bit 15        |                                                        |                  |             |                                         |                | bit 8 |       |  |  |

|               |                                                        |                  |             |                                         |                |       |       |  |  |

| U-0           | U-0                                                    | U-0              | R/W-1       | R/W-1                                   | R/W-1          | R/W-1 | R/W-1 |  |  |

| _             | _                                                      |                  |             |                                         | INDX1R<4:0>    |       |       |  |  |

| bit 7         |                                                        |                  |             |                                         |                |       | bit 0 |  |  |

|               |                                                        |                  |             |                                         |                |       |       |  |  |

| Legend:       |                                                        |                  |             |                                         |                |       |       |  |  |

| R = Readable  | e bit                                                  | W = Writable     | bit         | U = Unimplemented bit, read as '0'      |                |       |       |  |  |

| -n = Value at | POR                                                    | '1' = Bit is set |             | '0' = Bit is cleared x = Bit is unknown |                |       |       |  |  |

|               |                                                        |                  |             |                                         |                |       |       |  |  |

| bit 15-5      | Unimplemen                                             | ted: Read as '   | כ'          |                                         |                |       |       |  |  |

| bit 4-0       | INDX1R<4:0>                                            | Assign QEI1      | INDEX (INDX | (1) to the corre                        | sponding RPn p | bin   |       |  |  |

|               | 11111 <b>= Inpu</b>                                    | it tied Vss      |             |                                         |                |       |       |  |  |

|               | 01111 <b>= Inpu</b>                                    | it tied to RP15  |             |                                         |                |       |       |  |  |

|               |                                                        |                  |             |                                         |                |       |       |  |  |

|               | •                                                      |                  |             |                                         |                |       |       |  |  |

|               | 00001 = Input tied to RP1<br>00000 = Input tied to RP0 |                  |             |                                         |                |       |       |  |  |

#### REGISTER 10-14: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0           | U-0        | U-0                               | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0    |  |  |

|---------------|------------|-----------------------------------|-----------------|------------------|------------------|-----------------|----------|--|--|

| _             | —          | _                                 | RP1R<4:0>       |                  |                  |                 |          |  |  |

| bit 15        |            |                                   |                 |                  |                  |                 | bit 8    |  |  |

|               |            |                                   |                 |                  |                  |                 |          |  |  |

| U-0           | U-0        | U-0                               | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0    |  |  |

| —             | —          | —                                 |                 |                  | RP0R<4:0>        |                 |          |  |  |

| bit 7         |            |                                   |                 |                  |                  |                 | bit 0    |  |  |

|               |            |                                   |                 |                  |                  |                 |          |  |  |

| Legend:       |            |                                   |                 |                  |                  |                 |          |  |  |

| R = Readabl   | le bit     | W = Writable                      | bit             | U = Unimpler     | nented bit, read | d as '0'        |          |  |  |

| -n = Value at | POR        | '1' = Bit is set                  |                 | '0' = Bit is cle | ared             | x = Bit is unkr | iown     |  |  |

| bit 15-13     | Unimplemen | ted: Read as '                    | 0'              |                  |                  |                 |          |  |  |

| bit 12-8      |            | Peripheral Outr<br>ction numbers) |                 | s Assigned to F  | RP1 Output Pin   | bits (see Table | 10-2 for |  |  |

| bit 7-5       | Unimplemen | ted: Read as '                    | 0'              |                  |                  |                 |          |  |  |

| bit 4-0       | RP0R<4:0>: | Peripheral Out                    | out Function is | s Assigned to F  | RP0 Output Pin   | bits (see Table | 10-2 for |  |  |

peripheral function numbers)

#### REGISTER 10-15: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0             | U-0 | U-0              | R/W-0                                  | R/W-0                                   | R/W-0     | R/W-0 | R/W-0 |  |

|-----------------|-----|------------------|----------------------------------------|-----------------------------------------|-----------|-------|-------|--|

| —               | _   | —                |                                        |                                         | RP3R<4:0> |       |       |  |

| bit 15          |     |                  |                                        |                                         |           |       | bit 8 |  |

|                 |     |                  |                                        |                                         |           |       |       |  |

| U-0             | U-0 | U-0              | R/W-0                                  | R/W-0                                   | R/W-0     | R/W-0 | R/W-0 |  |

| —               | _   | —                |                                        |                                         | RP2R<4:0> |       |       |  |

| bit 7           |     |                  |                                        |                                         |           |       | bit 0 |  |

|                 |     |                  |                                        |                                         |           |       |       |  |

| Legend:         |     |                  |                                        |                                         |           |       |       |  |

| R = Readable I  | bit | W = Writable     | bit U = Unimplemented bit, read as '0' |                                         |           |       |       |  |

| -n = Value at P | OR  | '1' = Bit is set |                                        | '0' = Bit is cleared x = Bit is unknown |           |       | nown  |  |

| R = Readable I  |     |                  |                                        | •                                       |           |       | iown  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-2 for peripheral function numbers)

| R/W-0              | U-0                            | R/W-0                 | U-0              | U-0                           | U-0             | U-0                | U-0   |

|--------------------|--------------------------------|-----------------------|------------------|-------------------------------|-----------------|--------------------|-------|

| TON <sup>(2)</sup> |                                | TSIDL <sup>(1)</sup>  | _                | _                             |                 | _                  | _     |

| bit 15             |                                |                       |                  |                               |                 |                    | bit 8 |

|                    |                                |                       |                  |                               |                 |                    |       |

| U-0                | R/W-0                          | R/W-0                 | R/W-0            | U-0                           | U-0             | R/W-0              | U-0   |

|                    | TGATE <sup>(2)</sup>           | TCKPS<                | <1:0> <b>(2)</b> | —                             | _               | TCS <sup>(2)</sup> |       |

| bit 7              |                                |                       |                  |                               |                 |                    | bit C |

|                    |                                |                       |                  |                               |                 |                    |       |

| Legend:            |                                |                       |                  |                               |                 |                    |       |

| R = Readabl        |                                | W = Writable I        | oit              | •                             | mented bit, rea |                    |       |

| -n = Value at      | POR                            | '1' = Bit is set      |                  | '0' = Bit is cle              | ared            | x = Bit is unkn    | own   |

| bit 15             | TON: Timer3                    | On hit(2)             |                  |                               |                 |                    |       |

| DIL 15             | 1 = Starts 16-                 |                       |                  |                               |                 |                    |       |

|                    | 0 = Stops 16-                  |                       |                  |                               |                 |                    |       |

| bit 14             | Unimplemen                     | ted: Read as 'o       | )'               |                               |                 |                    |       |

| bit 13             | TSIDL: Stop i                  | in Idle Mode bit      | (1)              |                               |                 |                    |       |

|                    | 1 = Discontin                  | ue timer operati      | ion when dev     | vice enters Idle              | mode            |                    |       |

|                    | 0 = Continue                   | timer operation       | in Idle mode     | 9                             |                 |                    |       |

| bit 12-7           | -                              | ted: Read as '0       |                  | (-)                           |                 |                    |       |

| bit 6              |                                | er3 Gated Time        | Accumulatio      | n Enable bit <sup>(2)</sup>   |                 |                    |       |

|                    | When TCS =<br>This bit is igno |                       |                  |                               |                 |                    |       |

|                    | When TCS =                     |                       |                  |                               |                 |                    |       |

|                    |                                | <u>e</u> accumulation | enabled          |                               |                 |                    |       |

|                    | 0 = Gated tim                  | e accumulation        | disabled         |                               |                 |                    |       |

| bit 5-4            | TCKPS<1:0>                     | : Timer3 Input (      | Clock Presca     | le Select bits <sup>(2)</sup> | )               |                    |       |

|                    | 11 = 1:256 pr                  |                       |                  |                               |                 |                    |       |

|                    | 10 = 1:64 pre<br>01 = 1:8 pres |                       |                  |                               |                 |                    |       |

|                    | 00 = 1:1 pres                  |                       |                  |                               |                 |                    |       |

| bit 3-2            | -                              | ted: Read as '0       | )'               |                               |                 |                    |       |

| bit 1              | -                              | Clock Source S        |                  |                               |                 |                    |       |

|                    |                                | clock from T3Cl       |                  |                               |                 |                    |       |

|                    | 0 = Internal c                 | lock (Fosc/2)         |                  |                               |                 |                    |       |

| bit 0              | Unimplemen                     | ted: Read as '0       | )'               |                               |                 |                    |       |

|                    | /hen 32-bit timer              |                       |                  | - ) :                         | 0               |                    |       |

### REGISTER 12-2: T3CON CONTROL REGISTER

**Note 1:** When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (T2CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (T2CON<3>), these bits have no effect.

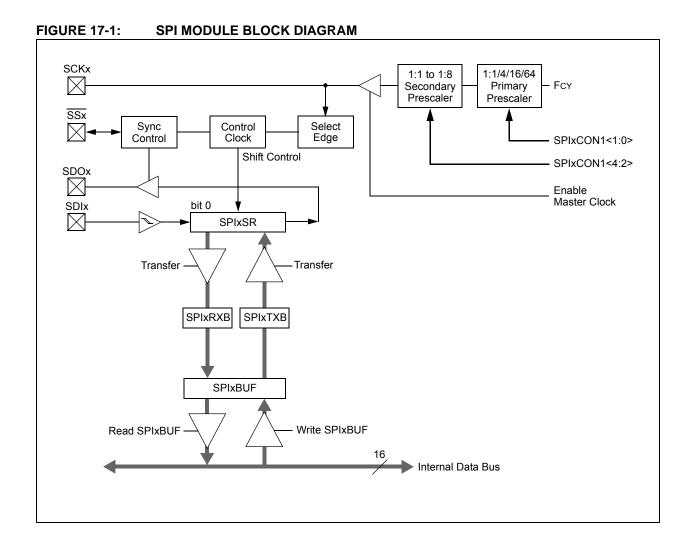

## 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12MC201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, analog-to-digital converters, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of four pins:

- · SDIx (serial data input)

- · SDOx (serial data output)

- · SCKx (shift clock input or output)

- SSx (active low slave select).

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

| R-0 HSC         | R-0 HSC                                                                                                                                                                                                                   | U-0                                                                                                 | U-0                              | U-0                       | R/C-0 HS                                       | R-0 HSC          | R-0 HSC            |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------|---------------------------|------------------------------------------------|------------------|--------------------|--|--|

| ACKSTAT         | TRSTAT                                                                                                                                                                                                                    |                                                                                                     |                                  |                           | BCL                                            | GCSTAT           | ADD10              |  |  |

| bit 15          | ·                                                                                                                                                                                                                         |                                                                                                     |                                  |                           |                                                |                  | bit 8              |  |  |

|                 |                                                                                                                                                                                                                           |                                                                                                     |                                  |                           |                                                |                  |                    |  |  |

| R/C-0 HS        | R/C-0 HS                                                                                                                                                                                                                  | R-0 HSC                                                                                             | R/C-0 HSC                        | R/C-0 HSC                 | R-0 HSC                                        | R-0 HSC          | R-0 HSC            |  |  |

| IWCOL           | I2COV                                                                                                                                                                                                                     | D_A                                                                                                 | Р                                | S                         | R_W                                            | RBF              | TBF                |  |  |

| bit 7           |                                                                                                                                                                                                                           |                                                                                                     |                                  |                           |                                                |                  | bit 0              |  |  |

|                 |                                                                                                                                                                                                                           |                                                                                                     |                                  |                           |                                                |                  |                    |  |  |

| Legend:         |                                                                                                                                                                                                                           | -                                                                                                   | nented bit, rea                  |                           |                                                |                  |                    |  |  |

| R = Readable    |                                                                                                                                                                                                                           | W = Writable                                                                                        |                                  | HS = Set in h             |                                                | HSC = Hardwa     |                    |  |  |

| -n = Value at F | POR                                                                                                                                                                                                                       | '1' = Bit is set                                                                                    |                                  | '0' = Bit is cle          | ared                                           | x = Bit is unkn  | x = Bit is unknown |  |  |

| bit 15          | (when operati<br>1 = NACK rec<br>0 = ACK rece                                                                                                                                                                             | cknowledge St<br>ng as I <sup>2</sup> C mas<br>ceived from sla<br>ived from slav<br>or clear at end | ter, applicable<br>ve<br>e       |                           | nsmit operation                                | )                |                    |  |  |

| bit 14          |                                                                                                                                                                                                                           |                                                                                                     |                                  |                           |                                                |                  |                    |  |  |

| bit 13-11       | Unimplemen                                                                                                                                                                                                                | ted: Read as '                                                                                      | 0'                               |                           |                                                |                  |                    |  |  |

| bit 10          | BCL: Master                                                                                                                                                                                                               | Bus Collision [                                                                                     | Detect bit                       |                           |                                                |                  |                    |  |  |

|                 | <ul> <li>1 = A bus collision has been detected during a master operation</li> <li>0 = No collision</li> <li>Hardware set at detection of bus collision.</li> </ul>                                                        |                                                                                                     |                                  |                           |                                                |                  |                    |  |  |

| bit 9           | GCSTAT: Ger                                                                                                                                                                                                               | neral Call Statu                                                                                    | us bit                           |                           |                                                |                  |                    |  |  |

|                 | 0 = General c                                                                                                                                                                                                             | all address wa<br>all address wa<br>when address                                                    | is not received                  |                           | ss. Hardware c                                 | lear at Stop det | ection.            |  |  |

| bit 8           | ADD10: 10-bi                                                                                                                                                                                                              | it Address Stat                                                                                     | us bit                           |                           |                                                |                  |                    |  |  |

|                 | <ul> <li>1 = 10-bit address was matched</li> <li>0 = 10-bit address was not matched</li> <li>Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.</li> </ul>                    |                                                                                                     |                                  |                           |                                                |                  |                    |  |  |

| bit 7           |                                                                                                                                                                                                                           |                                                                                                     |                                  |                           |                                                |                  |                    |  |  |

|                 | 0 = No collisio                                                                                                                                                                                                           | on                                                                                                  |                                  |                           | use the I <sup>2</sup> C mo<br>usy (cleared by |                  |                    |  |  |

| bit 6           | I2COV: Recei                                                                                                                                                                                                              | ive Overflow F                                                                                      | lag bit                          |                           |                                                |                  |                    |  |  |

|                 | <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> <li>Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).</li> </ul> |                                                                                                     |                                  |                           |                                                |                  |                    |  |  |

| bit 5           | D_A: Data/Ac                                                                                                                                                                                                              | Idress bit (whe                                                                                     | n operating as                   | s l <sup>2</sup> C slave) |                                                |                  |                    |  |  |

|                 | 1 = Indicates<br>0 = Indicates                                                                                                                                                                                            | that the last by<br>that the last by                                                                | /te received w<br>/te received w | as data<br>as device add  | ress<br>by reception of                        | slave byte.      |                    |  |  |

| bit 4           | P: Stop bit                                                                                                                                                                                                               |                                                                                                     |                                  |                           |                                                |                  |                    |  |  |

|                 | <ul> <li>P: Stop bit</li> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>     |                                                                                                     |                                  |                           |                                                |                  |                    |  |  |

REGISTER 18-2: I2CxSTAT: I2Cx STATUS REGISTER

#### **REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)**

- bit 4

URXINV: Receive Polarity Inversion bit

1 = UxRX Idle state is '0'

0

0 = UxRX Idle state is '1'

bit 3

BRGH: High Baud Rate Enable bit

1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)

0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)

bit 2-1

PDSEL<1:0>: Parity and Data Selection bits

11 = 9-bit data, no parity

10 = 8-bit data, odd parity

01 = 8-bit data, even parity

00 = 8-bit data, no parity

00 = 8-bit data, no parity

10 = 8-bit data, no parity

- bit 0 STSEL: Stop Bit Selection bit

- 1 =Two Stop bits

- 0 = One Stop bit

- **Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for inormation on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

## 23.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 23.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 23.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 23.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

| DC CHARACTERISTICS |        |                                      | (unless | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |      |       |                                                            |  |  |

|--------------------|--------|--------------------------------------|---------|---------------------------------------------------------------------------|------|-------|------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(3)</sup>        | Min     | Typ <sup>(1)</sup>                                                        | Max  | Units | Conditions                                                 |  |  |

|                    |        | Program Flash Memory                 |         |                                                                           |      |       |                                                            |  |  |

| D130a              | Eр     | Cell Endurance                       | 10,000  | _                                                                         | _    | E/W   | -40° C to +125° C                                          |  |  |

| D131               | Vpr    | VDD for Read                         | VMIN    | _                                                                         | 3.6  | V     | VMIN = Minimum operating<br>voltage                        |  |  |

| D132B              | VPEW   | VDD for Self-Timed Write             | VMIN    | —                                                                         | 3.6  | V     | VMIN = Minimum operating<br>voltage                        |  |  |

| D134               | TRETD  | Characteristic Retention             | 20      | —                                                                         | —    | Year  | Provided no other specifications are violated              |  |  |

| D135               | IDDP   | Supply Current during<br>Programming | -       | 10                                                                        | —    | mA    |                                                            |  |  |

| D136a              | Trw    | Row Write Time                       | 1.32    | —                                                                         | 1.74 | ms    | Trw = 11064 FRC cycles,<br>Ta = +85°C, See <b>Note 2</b>   |  |  |

| D136b              | Trw    | Row Write Time                       | 1.28    | —                                                                         | 1.79 | ms    | Trw = 11064 FRC cycles,<br>Ta = +125°C, See <b>Note 2</b>  |  |  |

| D137a              | Тре    | Page Erase Time                      | 20.1    | —                                                                         | 26.5 | ms    | TPE = 168517 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>  |  |  |

| D137b              | TPE    | Page Erase Time                      | 19.5    | —                                                                         | 27.3 | ms    | TPE = 168517 FRC cycles,<br>TA = +125°C, See <b>Note 2</b> |  |  |

| D138a              | Tww    | Word Write Cycle Time                | 42.3    | —                                                                         | 55.9 | μs    | Tww = 355 FRC cycles,<br>TA = +85°C, See <b>Note 2</b>     |  |  |

| D138b              | Tww    | Word Write Cycle Time                | 41.1    | —                                                                         | 57.6 | μs    | Tww = 355 FRC cycles,<br>TA = +125°C, See <b>Note 2</b>    |  |  |

#### TABLE 24-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Other conditions: FRC = 7.37 MHz, TUN<5:0> = b'011111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 24-18) and the value of the FRC Oscillator Tuning register (see Register 8-4). For complete details on calculating the Minimum and Maximum time see Section 5.3 "Programming Operations".

3: These parameters are ensured by design, but are not characterized or tested in manufacturing.

#### TABLE 24-13: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |       |                                                          |  |

|--------------------|--------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|----------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristics                                   | Min                                                                                                                                                                                                                                                                                   | Тур | Max | Units | Comments                                                 |  |

|                    | Cefc   | External Filter Capacitor<br>Value <sup>(1)</sup> | 4.7                                                                                                                                                                                                                                                                                   | 10  |     | μF    | Capacitor must be low<br>series resistance<br>(< 5 ohms) |  |

**Note 1:** Typical VCAP pin voltage = 2.5V when VDD  $\geq$  VDDMIN.

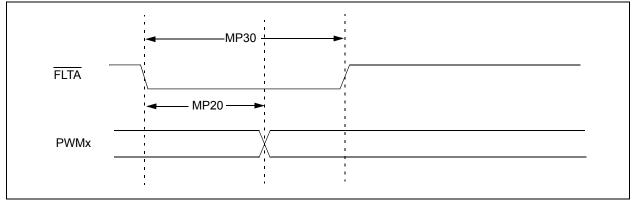

#### TABLE 24-28: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                  | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |     |          |       |            |

|--------------------|--------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>    | Min                                                                                                                                                                                                      | Тур | Max      | Units | Conditions |

| OC15               | Tfd    | Fault Input to PWM I/O<br>Change |                                                                                                                                                                                                          | _   | Tcy + 20 | ns    |            |

| OC20               | TFLT   | Fault Input Pulse Width          | Tcy + 20                                                                                                                                                                                                 |     | —        | ns    |            |

**Note 1:** These parameters are characterized by similarity, but are not tested in manufacturing.

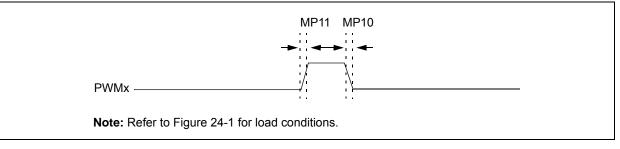

#### FIGURE 24-10: MOTOR CONTROL PWM MODULE FAULT TIMING CHARACTERISTICS

#### FIGURE 24-11: MOTOR CONTROL PWM MODULE TIMING CHARACTERISTICS

# TABLE 24-36:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                                      |  |

|--------------------|-----------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                        | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP70               | TscP                  | Maximum SCK Input Frequency                                  | —                                                                                                                                                                                          | —                  | 15  | MHz   | See Note 3                           |  |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                          | _                  |     | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                                                                                                                                                                          | —                  | —   | ns    | See parameter DO31 and Note 4        |  |