Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detalls                    |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                |

| Core Processor             | ARM® Cortex®-M0                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 50MHz                                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PS2, PWM, WDT                  |

| Number of I/O              | 31                                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | 4K x 8                                                                                  |

| RAM Size                   | 16K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |

| Data Converters            | A/D 8x12b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 48-LQFP                                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc120ld3an |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

6

7

| 5.8         | 5.7.2 Features<br>Real Time Clock (RTC)                                               |              |

|-------------|---------------------------------------------------------------------------------------|--------------|

| 0.0         | 5.8.1 Overview                                                                        |              |

|             | 5.8.2 Features                                                                        |              |

| 5.9         | Serial Peripheral Interface (SPI)                                                     |              |

|             | 5.9.1 Overview                                                                        | 45           |

|             | 5.9.2 Features                                                                        |              |

| 5.10        | Timer Controller (TMR)                                                                |              |

|             | 5.10.1 Overview                                                                       |              |

| <b>F</b> 44 | 5.10.2 Features                                                                       |              |

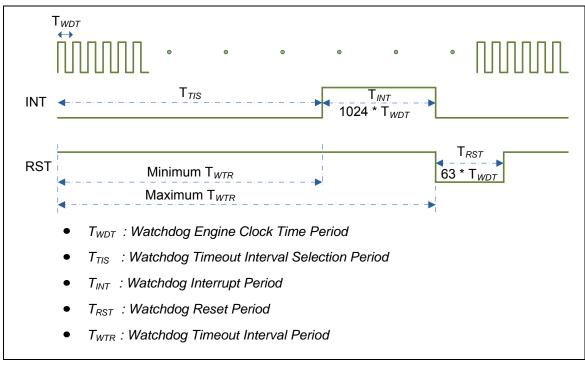

| 5.11        | Watchdog Timer (WDT)                                                                  |              |

|             | 5.11.1 Overview                                                                       |              |

| 5.12        | 5.11.2 Features<br>UART Interface Controller (UART)                                   |              |

| 5.12        | 5.12.1 Overview                                                                       |              |

|             | 5.12.2 Features                                                                       |              |

| 5.13        | PS/2 Device Controller (PS2D)                                                         | -            |

|             | 5.13.1 Overview                                                                       |              |

|             | 5.13.2 Features                                                                       |              |

| 5.14        | I <sup>2</sup> S Controller (I <sup>2</sup> S)                                        | 53           |

|             | 5.14.1 Overview                                                                       | 53           |

|             | 5.14.2 Features                                                                       | 53           |

| 5.15        | Analog-to-Digital Converter (ADC)                                                     |              |

|             | 5.15.1 Overview                                                                       | 54           |

|             | 5.15.2 Features                                                                       |              |

| 5.16        | Analog Comparator (CMP)                                                               | 55           |

|             | 5.16.1 Overview                                                                       |              |

| F 47        | 5.16.2 Features                                                                       |              |

| 5.17        | PDMA Controller (PDMA)                                                                |              |

|             | 5.17.1 Overview                                                                       |              |

| 5.18        | External Bus Interface (EBI)                                                          |              |

| 0.10        | 5.18.1 Overview                                                                       |              |

|             | 5.18.2 Features                                                                       |              |

| FLASH       | H MEMORY CONTROLLER (FMC)                                                             |              |

| 6.1         | Overview                                                                              |              |

| 6.2         | Features                                                                              |              |

| FI FC       | TRICAL CHARACTERISTICS                                                                |              |

| 7.1         | Absolute Maximum Ratings                                                              |              |

| 7.2         | DC Electrical Characteristics                                                         |              |

|             | 7.2.1 NuMicro <sup>™</sup> NUC100/NUC120 Medium Density DC Electrical Characteristics |              |

|             | 7.2.2 NuMicro <sup>™</sup> NUC100/NUC120 Low Density DC Electrical Characteristics    |              |

|             | Publication Release Date: Ja                                                          |              |

|             |                                                                                       | rision V2.03 |

### Figures

| Figure 3-1 NuMicro™ NUC100 Series selection code                   | 13 |

|--------------------------------------------------------------------|----|

| Figure 3-2 NuMicro™ NUC120 Medium Density LQFP 100-pin Pin Diagram | 14 |

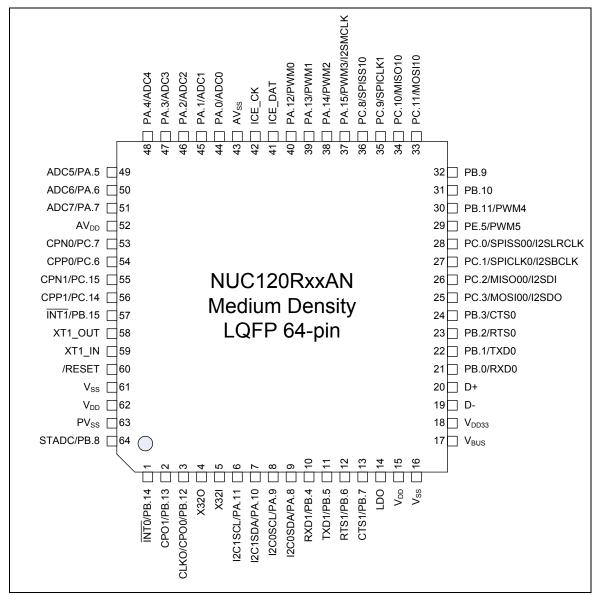

| Figure 3-3 NuMicro™ NUC120 Medium Density LQFP 64-pin Pin Diagram  | 15 |

| Figure 3-4 NuMicro™ NUC120 Medium Density LQFP 48-pin Pin Diagram  | 16 |

| Figure 3-5 NuMicro™ NUC120 Low Density LQFP 64-pin Pin Diagram     | 17 |

| Figure 3-6 NuMicro™ NUC120 Low Density LQFP 48-pin Pin Diagram     | 18 |

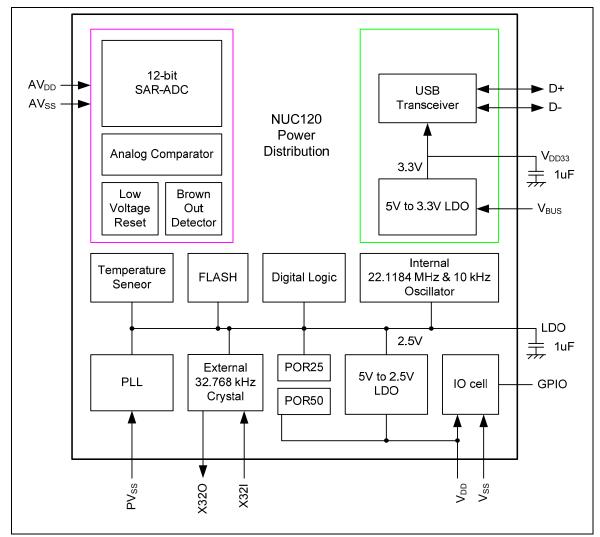

| Figure 4-1 NuMicro™ NUC120 Medium Density Block Diagram            | 19 |

| Figure 4-2 NuMicro™ NUC120 Low Density Block Diagram               | 20 |

| Figure 5-1 Functional Controller Diagram                           | 21 |

| Figure 5-2 NuMicro™ NUC120 Power Distribution Diagram              | 24 |

| Figure 5-4 Clock generator global view diagram                     | 33 |

| Figure 5-5 Clock generator block diagram                           | 34 |

| Figure 5-6 System Clock Block Diagram                              | 35 |

| Figure 5-7 SysTick Clock Control Block Diagram                     | 35 |

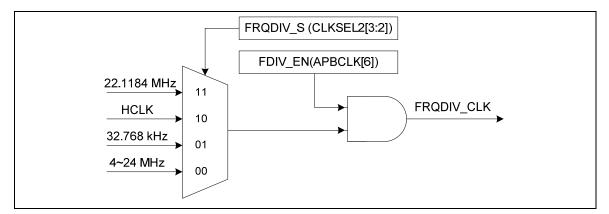

| Figure 5-8 Clock Source of Frequency Divider                       | 37 |

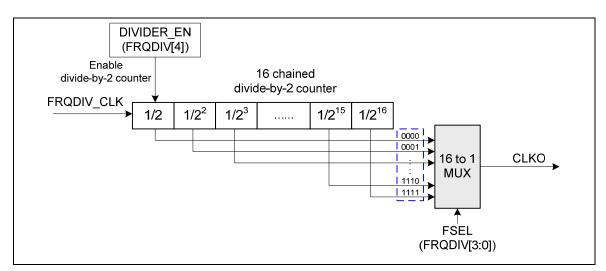

| Figure 5-9 Block Diagram of Frequency Divider                      |    |

| Figure 5-10 I <sup>2</sup> C Bus Timing                            | 40 |

| Figure 5-11 Timing of Interrupt and Reset Signal                   | 48 |

| Figure 7-1 Typical Crystal Application Circuit                     | 76 |

| Figure 7-2 SPI Master dynamic characteristics timing               | 84 |

| Figure 7-3 SPI Slave dynamic characteristics timing                | 84 |

3.2.1.2 NuMicro™ NUC120 Medium Density LQFP 64 pin

Figure 3-3 NuMicro™ NUC120 Medium Density LQFP 64-pin Pin Diagram

- Low power sleep mode entry using Wait For Interrupt (WFI), Wait For Event (WFE) instructions, or the return from interrupt sleep-on-exit feature

- NVIC that features:

- 32 external interrupt inputs, each with four levels of priority

- Dedicated Non-Maskable Interrupt (NMI) input.

- Support for both level-sensitive and pulse-sensitive interrupt lines

- Wake-up Interrupt Controller (WIC), providing ultra-low power sleep mode support.

- Debug support

- Four hardware breakpoints.

- Two watchpoints.

- Program Counter Sampling Register (PCSR) for non-intrusive code profiling.

- Single step and vector catch capabilities.

- Bus interfaces:

- Single 32-bit AMBA-3 AHB-Lite system interface that provides simple integration to all system peripherals and memory.

- Single 32-bit slave port that supports the DAP (Debug Access Port).

### 5.2 System Manager

#### 5.2.1 Overview

System management includes these following sections:

- System Resets

- System Memory Map

- System management registers for Part Number ID, chip reset and on-chip controllers reset , multi-functional pin control

- System Timer (SysTick)

- Nested Vectored Interrupt Controller (NVIC)

- System Control registers

#### 5.2.2 System Reset

The system reset can be issued by one of the below listed events. For these reset event flags can be read by RSTSRC register.

- The Power-On Reset

- The low level on the /RESET pin

- Watchdog Time Out Reset

- Low Voltage Reset

- Brown-Out Detector Reset

- CPU Reset

- System Reset

System Reset and Power-On Reset all reset the whole chip including all peripherals. The difference between System Reset and Power-On Reset is external crystal circuit and ISPCON.BS bit. System Reset doesn't reset external crystal circuit and ISPCON.BS bit, but Power-On Reset does.

### 5.2.3 System Power Distribution

In this chip, the power distribution is divided into three segments.

- Analog power from AV<sub>DD</sub> and AV<sub>SS</sub> provides the power for analog components operation.

- Digital power from V<sub>DD</sub> and V<sub>SS</sub> supplies the power to the internal regulator which provides a fixed 2.5 V power for digital operation and I/O pins.

- USB transceiver power from V<sub>BUS</sub> offers the power for operating the USB transceiver.

The outputs of internal voltage regulators, LDO and V<sub>DD33</sub>, require an external capacitor which should be located close to the corresponding pin. Analog power (AV<sub>DD</sub>) should be the same voltage level of the digital power (V<sub>DD</sub>). Figure 5-2 shows the power distribution of NuMicro<sup>TM</sup> NUC120.

Figure 5-2 NuMicro™ NUC120 Power Distribution Diagram

| Vector<br>Number | Interrupt<br>Number<br>(Bit in Interrupt<br>Registers) | Interrupt<br>Name | Source IP         | Interrupt description                                             |

|------------------|--------------------------------------------------------|-------------------|-------------------|-------------------------------------------------------------------|

| 26               | 10                                                     | TMR2_INT          | TMR2              | Timer 2 interrupt                                                 |

| 27               | 11                                                     | TMR3_INT          | TMR3              | Timer 3 interrupt                                                 |

| 28               | 12                                                     | UART02_INT        | UART0/2           | UART0 and UART2 interrupt                                         |

| 29               | 13                                                     | UART1_INT         | UART1             | UART1 interrupt                                                   |

| 30               | 14                                                     | SPI0_INT          | SPI0              | SPI0 interrupt                                                    |

| 31               | 15                                                     | SPI1_INT          | SPI1              | SPI1 interrupt                                                    |

| 32               | 16                                                     | SPI2_INT          | SPI2              | SPI2 interrupt                                                    |

| 33               | 17                                                     | SPI3_INT          | SPI3              | SPI3 interrupt                                                    |

| 34               | 18                                                     | I2C0_INT          | I <sup>2</sup> C0 | I <sup>2</sup> C0 interrupt                                       |

| 35               | 19                                                     | I2C1_INT          | I <sup>2</sup> C1 | I <sup>2</sup> C1 interrupt                                       |

| 36               | 20                                                     | Reserved          | Reserved          | Reserved                                                          |

| 37               | 21                                                     | Reserved          | Reserved          | Reserved                                                          |

| 38               | 22                                                     | Reserved          | Reserved          | Reserved                                                          |

| 39               | 23                                                     | USB_INT           | USBD              | USB 2.0 FS Device interrupt                                       |

| 40               | 24                                                     | PS2_INT           | PS/2              | PS/2 interrupt                                                    |

| 41               | 25                                                     | ACMP_INT          | ACMP              | Analog Comparator-0 or Comaprator-1 interrupt                     |

| 42               | 26                                                     | PDMA_INT          | PDMA              | PDMA interrupt                                                    |

| 43               | 27                                                     | I2S_INT           | I <sup>2</sup> S  | I <sup>2</sup> S interrupt                                        |

| 44               | 28                                                     | PWRWU_INT         | CLKC              | Clock controller interrupt for chip wake-up from power down state |

| 45               | 29                                                     | ADC_INT           | ADC               | ADC interrupt                                                     |

| 46               | 30                                                     | Reserved          | Reserved          | Reserved                                                          |

| 47               | 31                                                     | RTC_INT           | RTC               | Real time clock interrupt                                         |

Table 5-3 System Interrupt Map

#### 5.2.6.2 Vector Table

When any interrupts is accepted, the processor will automatically fetch the starting address of the interrupt service routine (ISR) from a vector table in memory. For ARMv6-M, the vector table base address is fixed at 0x00000000. The vector table contains the initialization value for the stack pointer on reset, and the entry point addresses for all exception handlers. The vector number on previous page defines the order of entries in the vector table associated with exception handler entry as illustrated in previous section.

| Vector Table Word Offset | Description                                      |

|--------------------------|--------------------------------------------------|

| 0                        | SP_main – The Main stack pointer                 |

| Vector Number            | Exception Entry Pointer using that Vector Number |

Table 5-4 Vector Table Format

#### 5.2.6.3 Operation Description

NVIC interrupts can be enabled and disabled by writing to their corresponding Interrupt Set-Enable or Interrupt Clear-Enable register bit-field. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current enabled state of the corresponding interrupts. When an interrupt is disabled, interrupt assertion will cause the interrupt to become Pending, however, the interrupt will not activate. If an interrupt is Active when it is disabled, it remains in its Active state until cleared by reset or an exception return. Clearing the enable bit prevents new activations of the associated interrupt.

NVIC interrupts can be pended/un-pended using a complementary pair of registers to those used to enable/disable the interrupts, named the Set-Pending Register and Clear-Pending Register respectively. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current pended state of the corresponding interrupts. The Clear-Pending Register has no effect on the execution status of an Active interrupt.

NVIC interrupts are prioritized by updating an 8-bit field within a 32-bit register (each register supporting four interrupts).

The general registers associated with the NVIC are all accessible from a block of memory in the System Control Space and will be described in next section.

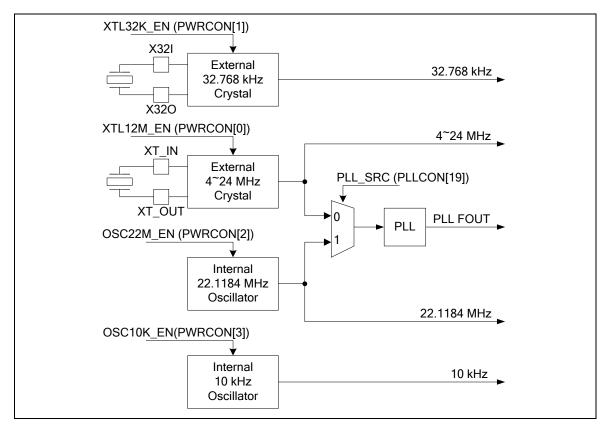

#### 5.3.2 Clock Generator

The clock generator consists of 5 clock sources which are listed below:

- One external 32.768 kHz low speed crystal

- One external 4~24 MHz high speed crystal

- One programmable PLL FOUT(PLL source consists of external 4~24 MHz high speed crystal and internal 22.1184 MHz high speed oscillator)

- One internal 22.1184 MHz high speed oscillator

- One internal 10 kHz low speed oscillator

Figure 5-4 Clock generator block diagram

#### 5.3.6 Frequency Divider Output

This device is equipped a power-of-2 frequency divider which is composed by16 chained divideby-2 shift registers. One of the 16 shift register outputs selected by a sixteen to one multiplexer is reflected to CLKO function pin. Therefore there are 16 options of power-of-2 divided clocks with the frequency from  $F_{in}/2^{16}$  where Fin is input clock frequency to the clock divider.

The output formula is  $F_{out} = F_{in}/2^{(N+1)}$ , where  $F_{in}$  is the input clock frequency,  $F_{out}$  is the clock divider output frequency and N is the 4-bit value in FSEL (FRQDIV[3:0]).

When write 1 to DIVIDER\_EN (FRQDIV[4]), the chained counter starts to count. When write 0 to DIVIDER\_EN (FRQDIV[4]), the chained counter continuously runs till divided clock reaches low state and stay in low state.

Figure 5-7 Clock Source of Frequency Divider

Figure 5-8 Block Diagram of Frequency Divider

### 5.4 USB Device Controller (USB)

#### 5.4.1 Overview

There is one set of USB 2.0 full-speed device controller and transceiver in this device. It is compliant with USB 2.0 full-speed device specification and support control/bulk/interrupt/ isochronous transfer types.

In this device controller, there are two main interfaces: the APB bus and USB bus which comes from the USB PHY transceiver. For the APB bus, the CPU can program control registers through it. There are 512 bytes internal SRAM as data buffer in this controller. For IN or OUT transfer, it is necessary to write data to SRAM or read data from SRAM through the APB interface or SIE. Users need to set the effective starting address of SRAM for each endpoint buffer through "buffer segmentation register (USB\_BUFSEGx)".

There are 6 endpoints in this controller. Each of the endpoint can be configured as IN or OUT endpoint. All the operations including Control, Bulk, Interrupt and Isochronous transfer are implemented in this block. The block of ENDPOINT CONTROL is also used to manage the data sequential synchronization, endpoint states, current start address, transaction status, and data buffer status for each endpoint.

There are four different interrupt events in this controller. They are the wake-up function, device plug-in or plug-out event, USB events, like IN ACK, OUT ACK etc, and BUS events, like suspend and resume, etc. Any event will cause an interrupt, and users just need to check the related event flags in interrupt event status register (USB\_INTSTS) to acknowledge what kind of interrupt occurring, and then check the related USB Endpoint Status Register (USB\_EPSTS) to acknowledge what kind of event occurring in this endpoint.

A software-disable function is also supported for this USB controller. It is used to simulate the disconnection of this device from the host. If user enables DRVSE0 bit (USB\_DRVSE0), the USB controller will force the output of USB\_DP and USB\_DM to level low and its function is disabled. After disable the DRVSE0 bit, host will enumerate the USB device again.

Reference: Universal Serial Bus Specification Revision 1.1

#### 5.4.2 Features

This Universal Serial Bus (USB) performs a serial interface with a single connector type for attaching all USB peripherals to the host system. Following is the feature listing of this USB.

- Compliant with USB 2.0 Full-Speed specification

- Provide 1 interrupt vector with 4 different interrupt events (WAKEUP, FLDET, USB and BUS)

- Support Control/Bulk/Interrupt/Isochronous transfer type

- Support suspend function when no bus activity existing for 3 ms

- Provide 6 endpoints for configurable Control/Bulk/Interrupt/Isochronous transfer types and maximum 512 bytes buffer size

- Provide remote wake-up capability

### 5.6 I<sup>2</sup>C Serial Interface Controller (Master/Slave) (I<sup>2</sup>C)

#### 5.6.1 Overview

$I^2C$  is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices. The  $I^2C$  standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously.

Data is transferred between a Master and a Slave synchronously to SCL on the SDA line on a byte-by-byte basis. Each data byte is 8-bit long. There is one SCL clock pulse for each data bit with the MSB being transmitted first. An acknowledge bit follows each transferred byte. Each bit is sampled during the high period of SCL; therefore, the SDA line may be changed only during the low period of SCL and must be held stable during the high period of SCL. A transition on the SDA line while SCL is high is interpreted as a command (START or STOP). Please refer to the Figure 5-9 for more detail I<sup>2</sup>C BUS Timing.

Figure 5-9 I<sup>2</sup>C Bus Timing

The device's on-chip I<sup>2</sup>C logic provides the serial interface that meets the I<sup>2</sup>C bus standard mode specification. The I<sup>2</sup>C port handles byte transfers autonomously. To enable this port, the bit ENS1 in I2CON should be set to '1'. The I<sup>2</sup>C H/W interfaces to the I<sup>2</sup>C bus via two pins: SDA and SCL. Pull up resistor is needed for I<sup>2</sup>C operation as these are open drain pins. When the I/O pins are used as I<sup>2</sup>C port, user must set the pins function to I<sup>2</sup>C in advance.

#### 5.6.2 Features

The I<sup>2</sup>C bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus. The main features of the bus are:

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Built-in a 14-bit time-out counter will request the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows.

- External pull-up are needed for high output

- Programmable clocks allow versatile rate control

- Supports 7-bit addressing mode

- I<sup>2</sup>C-bus controllers support multiple address recognition (Four slave address with mask option)

Figure 5-10 Timing of Interrupt and Reset Signal

| System clock = Internal 22.1184 MHz high speed oscillator |           |                                       |                                       |                                           |          |             |  |  |  |

|-----------------------------------------------------------|-----------|---------------------------------------|---------------------------------------|-------------------------------------------|----------|-------------|--|--|--|

| Baud rate                                                 | М         | ode0                                  | М                                     | ode1                                      | Mode2    |             |  |  |  |

| Badd fallo                                                | Parameter | Parameter Register Parameter Register |                                       | Parameter                                 | Register |             |  |  |  |

| 921600                                                    | х         | х                                     | A=0,B=11                              | 0x2B00_0000                               | A=22     | 0x3000_0016 |  |  |  |

| 460800                                                    | A=1       | 0x0000_0001                           | A=1,B=15<br>A=2,B=11                  | 0x2F00_0001<br>0x2B00_0002                | A=46     | 0x3000_002E |  |  |  |

| 230400                                                    | A=4       | 0x0000_0004                           | A=4,B=15<br>A=6,B=11                  | 0x2F00_0004<br>0x2B00_0006                | A=94     | 0x3000_005E |  |  |  |

| 115200                                                    | A=10      | 0x0000_000A                           | A=10,B=15<br>A=14,B=11                | 0x2F00_000A<br>0x2B00_000E                | A=190    | 0x3000_00BE |  |  |  |

| 57600                                                     | A=22      | 0x0000_0016                           | A=22,B=15<br>A=30,B=11                | 0x2F00_0016<br>0x2B00_001E                | A=382    | 0x3000_017E |  |  |  |

| 38400                                                     | A=34      | 0x0000_0022                           | A=62,B=8<br>A=46,B=11<br>A=34,B=15    | 0x2800_003E<br>0x2B00_002E<br>0x2F00_0022 | A=574    | 0x3000_023E |  |  |  |

| 19200                                                     | A=70      | 0x0000_0046                           | A=126,B=8<br>A=94,B=11<br>A=70,B=15   | 0x2800_007E<br>0x2B00_005E<br>0x2F00_0046 | A=1150   | 0x3000_047E |  |  |  |

| 9600                                                      | A=142     | 0x0000_008E                           | A=254,B=8<br>A=190,B=11<br>A=142,B=15 | 0x2800_00FE<br>0x2B00_00BE<br>0x2F00_008E | A=2302   | 0x3000_08FE |  |  |  |

| 4800                                                      | A=286     | 0x0000_011E                           | A=510,B=8<br>A=382,B=11<br>A=286,B=15 | 0x2800_01FE<br>0x2B00_017E<br>0x2F00_011E | A=4606   | 0x3000_11FE |  |  |  |

Table 5-7 UART Baud Rate Setting Table

The UART0 and UART1 controllers support auto-flow control function that uses two low-level signals, /CTS (clear-to-send) and /RTS (request-to-send), to control the flow of data transfer between the UART and external devices (ex: Modem). When auto-flow is enabled, the UART is not allowed to receive data until the UART asserts /RTS to external device. When the number of bytes in the RX FIFO equals the value of RTS\_TRI\_LEV (UA\_FCR [19:16]), the /RTS is deasserted. The UART sends data out when UART controller detects /CTS is asserted from external device. If a valid asserted /CTS is not detected the UART controller will not send data out.

The UART controllers also provides Serial IrDA (SIR, Serial Infrared) function (User must set IrDA\_EN (UA\_FUN\_SEL [1]) to enable IrDA function). The SIR specification defines a short-range infrared asynchronous serial transmission mode with one start bit, 8 data bits, and 1 stop bit. The maximum data rate is 115.2 Kbps (half duplex). The IrDA SIR block contains an IrDA SIR Protocol encoder/decoder. The IrDA SIR protocol is half-duplex only. So it cannot transmit and receive data at the same time. The IrDA SIR physical layer specifies a minimum 10ms transfer delay between transmission and reception. This delay feature must be implemented by software.

For NuMicro<sup>™</sup> NUC100/NUC120 Low Density, another alternate function of UART controllers is RS-485 9-bit mode function, and direction control provided by RTS pin or can program GPIO (PB.2 for RTS0 and PB.6 for RTS1) to implement the function by software. The RS-485 mode is selected by setting the UA\_FUN\_SEL register to select RS-485 function. The RS-485 driver control is implemented using the RTS control signal from an asynchronous serial port to enable the RS-485 driver. In RS-485 mode, many characteristics of the RX and TX are same as UART.

### 5.13 PS/2 Device Controller (PS2D)

#### 5.13.1 Overview

PS/2 device controller provides basic timing control for PS/2 communication. All communication between the device and the host is managed through the CLK and DATA pins. Unlike PS/2 keyboard or mouse device controller, the received/transmit code needs to be translated as meaningful code by firmware. The device controller generates the CLK signal after receiving a request to send, but host has ultimate control over communication. DATA sent from the host to the device is read on the rising edge and DATA sent from device to the host is change after rising edge. A 16 bytes FIFO is used to reduce CPU intervention. S/W can select 1 to 16 bytes for a continuous transmission.

#### 5.13.2 Features

- Host communication inhibit and request to send detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- S/W override bus

### 7 ELECTRICAL CHARACTERISTICS

### 7.1 Absolute Maximum Ratings

| SYMBOL                                    | PARAMETER                        | MIN                  | MAX                  | UNIT |

|-------------------------------------------|----------------------------------|----------------------|----------------------|------|

| DC Power Supply                           | V <sub>DD</sub> -V <sub>SS</sub> | -0.3                 | +7.0                 | V    |

| Input Voltage                             | V <sub>IN</sub>                  | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| Oscillator Frequency                      | 1/t <sub>CLCL</sub>              | 4                    | 24                   | MHz  |

| Operating Temperature                     | ТА                               | -40                  | +85                  | °C   |

| Storage Temperature                       | TST                              | -55                  | +150                 | °C   |

| Maximum Current into V <sub>DD</sub>      |                                  | -                    | 120                  | mA   |

| Maximum Current out of $V_{SS}$           |                                  |                      | 120                  | mA   |

| Maximum Current sunk by a I/O pin         |                                  |                      | 35                   | mA   |

| Maximum Current sourced by a I/O pin      |                                  |                      | 35                   | mA   |

| Maximum Current sunk by total I/O pins    |                                  |                      | 100                  | mA   |

| Maximum Current sourced by total I/O pins |                                  |                      | 100                  | mA   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the lift and reliability of the device.

| PARAMETER       | SYM.            | S    | SPECIFIC | CATION |      | TEST CONDITIONS               |

|-----------------|-----------------|------|----------|--------|------|-------------------------------|

|                 |                 | MIN. | TYP.     | MAX.   | UNIT |                               |

| Bandgap voltage | $V_{\text{BG}}$ | 1.20 | 1.26     | 1.32   | V    | V <sub>DD</sub> = 2.5 V~5.5 V |

Note:

1. /RESET pin is a Schmitt trigger input.

2. Crystal Input is a CMOS input.

3. Pins of PA, PB, PC, PD and PE can source a transition current when they are being externally driven from 1 to 0. In the condition of  $V_{DD}$ =5.5 V, 5he transition current reaches its maximum value when  $V_{IN}$  approximates to 2 V.

#### 7.4.2 Specification of LDO and Power management

| PARAMETER      | MIN. | TYP. | MAX. | UNIT | NOTE                    |

|----------------|------|------|------|------|-------------------------|

| Input Voltage  | 2.7  | 5    | 5.5  | V    | $V_{DD}$ input voltage  |

| Output Voltage | -10% | 2.5  | +10% | V    | V <sub>DD</sub> > 2.7 V |

| Temperature    | -40  | 25   | 85   | °C   |                         |

| Сbр            | -    | 1    | -    | uF   | Resr=10hm               |

Note:

1. It is recommended that a 10uF or higher capacitor and a 100nF bypass capacitor are connected between  $V_{\mbox{\tiny DD}}$  and the closest  $V_{\mbox{\tiny SS}}$  pin of the device.

2. For ensuring power stability, a 1uF or higher capacitor must be connected between LDO pin and the closest  $V_{\rm SS}$  pin of the device.

#### 7.5 **Flash DC Electrical Characteristics**

| SYMBOL             | PARAMETER             | CONDITIONS | MIN.  | TYP. | MAX. | UNIT                  |

|--------------------|-----------------------|------------|-------|------|------|-----------------------|

| N <sub>endu</sub>  | Endurance             |            | 10000 |      |      | cycles <sup>[1]</sup> |

| T <sub>ret</sub>   | Retention time        | Temp=25 ℃  | 100   |      |      | year                  |

| T <sub>erase</sub> | Page erase time       |            | 20    |      | 40   | ms                    |

| T <sub>mass</sub>  | Mass erase time       |            | 40    | 50   | 60   | ms                    |

| T <sub>prog</sub>  | Program time          |            | 35    | 40   | 55   | us                    |

| V <sub>dd</sub>    | Supply voltage        |            | 2.25  | 2.5  | 2.75 | V <sup>[2]</sup>      |

| I <sub>dd1</sub>   | Read current          |            |       |      | 14   | mA                    |

| I <sub>dd2</sub>   | Program/Erase current |            |       |      | 7    | mA                    |

| I <sub>pd</sub>    | Power down current    |            |       |      | 10   | uA                    |

Number of program/erase cycles.

V<sub>dd</sub> is source from chip LDO output voltage.

This table is guaranteed by design, not test in production.