#### STMicroelectronics - STM32F050K4U6A Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |

| Number of I/O              | 27                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                              |

| Data Converters            | A/D 10x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-UFQFN Exposed Pad                                                   |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f050k4u6a |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32F050xx family incorporates the high-performance ARM Cortex<sup>™</sup>-M0 32-bit RISC core operating at a 48 MHz maximum frequency, high-speed embedded memories (Flash memory up to 32 Kbytes and SRAM up to 4 Kbytes), and an extensive range of enhanced peripherals and I/Os. All devices offer standard communication interfaces (one I<sup>2</sup>C, one SPI, one I2S, and one USART), one 12-bit ADC, up to five general-purpose 16-bit timers, a 32-bit timer and an advanced-control PWM timer.

The STM32F050xx family operates in the -40 to +85  $^{\circ}$ C and -40 to +105  $^{\circ}$ C temperature ranges, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

The STM32F050xx family includes devices in five different packages ranging from 20 pins to 48 pins. Depending on the device chosen, different sets of peripherals are included. An overview of the complete range of peripherals proposed in this family is provided.

These features make the STM32F050xx microcontroller family suitable for a wide range of applications such as control application and user interfaces, handheld equipment, A/V receivers and digital TV, PC peripherals, gaming and GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms, and HVACs.

# 3.10 Analog to digital converter (ADC)

The 12-bit analog to digital converter has up to 16 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

#### 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\mbox{\scriptsize SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                          | Memory address            |

|------------------------|--------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 $^{\circ}$ C, V <sub>DDA</sub> = 3.3 V | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at<br>temperature of 110 °C<br>V <sub>DDA</sub> = 3.3 V     | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

### 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

#### Table 4. Temperature sensor calibration values

| Calibration value name | Description                                                              | Memory address            |

|------------------------|--------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 30 °C<br>V <sub>DDA</sub> = 3.3 V | 0x1FFF F7BA - 0x1FFF F7BB |

# 3.15 Serial peripheral interface (SPI)/Inter-integrated sound interfaces (I<sup>2</sup>S)

The SPI (SPI1) is able to communicate up to 18 Mbits/s in slave and master modes in fullduplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

One standard I<sup>2</sup>S interface (multiplexed with SPI1) supporting four different audio standards can operate as master or slave at half-duplex communication mode. It can be configured to transfer 16 and 24 or 32 bits with16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by 8-bit programmable linear prescaler. When operating in master mode it can output a clock for an external audio component at 256 times the sampling frequency.

# 3.16 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

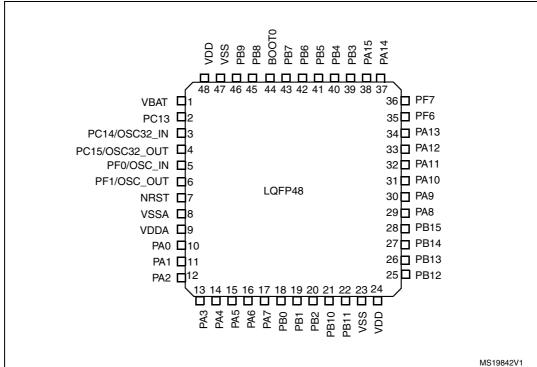

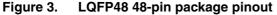

# 4 Pinouts and pin description

#### Figure 4. UFQFPN32 32-pin package pinout

|        | Pin      | numbe    | r       |                                       |          | e             |       | Pin fund                                                                       | ctions               |

|--------|----------|----------|---------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------|----------------------|

| LQFP48 | UFQFPN32 | UFQFPN28 | TSSOP20 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                            | Additional functions |

| 29     | 18       | 18       | -       | PA8                                   | I/O      | FT            |       | USART1_CK,<br>TIM1_CH1,<br>EVENTOUT,<br>MCO                                    |                      |

| 30     | 19       | 19       | 17      | PA9                                   | I/O      | FTf           |       | USART1_TX,<br>TIM1_CH2,<br>I2C1_SCL <sup>(3)</sup>                             |                      |

| 31     | 20       | 20       | 18      | PA10                                  | I/O      | FTf           |       | USART1_RX,<br>TIM1_CH3,<br>TIM17_BKIN,<br>I2C1_SDA <sup>(3)</sup>              |                      |

| 32     | 21       | -        | -       | PA11                                  | I/O      | FT            |       | USART1_CTS,<br>TIM1_CH4,<br>EVENTOUT                                           |                      |

| 33     | 22       | -        | -       | PA12                                  | I/O      | FT            |       | USART1_RTS,<br>TIM1_ETR,<br>EVENTOUT                                           |                      |

| 34     | 23       | 21       | 19      | PA13<br>(SWDAT)                       | I/O      | FT            | (4)   | IR_OUT,<br>SWDAT                                                               |                      |

| 35     | -        | -        | -       | PF6                                   | I/O      | FTf           |       | I2C1_SCL <sup>(3)</sup>                                                        |                      |

| 36     | -        | -        | -       | PF7                                   | I/O      | FTf           |       | I2C1_SDA <sup>(3)</sup>                                                        |                      |

| 37     | 24       | 22       | 20      | PA14<br>(SWCLK)                       | I/O      | FT            | (4)   | SWCLK,<br>USART1_TX <sup>(3)</sup>                                             |                      |

| 38     | 25       | 23       | -       | PA15                                  | I/O      | FT            |       | SPI1_NSS,<br>I2S1_WS,<br>TIM2_CH_ETR,<br>EVENTOUT,<br>USART1_RX <sup>(3)</sup> |                      |

| 39     | 26       | 24       | -       | PB3                                   | I/O      | FT            |       | SPI1_SCK,<br>I2S1_CK,<br>TIM2_CH2,<br>EVENTOUT                                 |                      |

| 40     | 27       | 25       | -       | PB4                                   | I/O      | FT            |       | SPI1_MISO,<br>I2S1_MCK,<br>TIM3_CH1,<br>EVENTOUT                               |                      |

# Table 8. Pin definitions (continued)

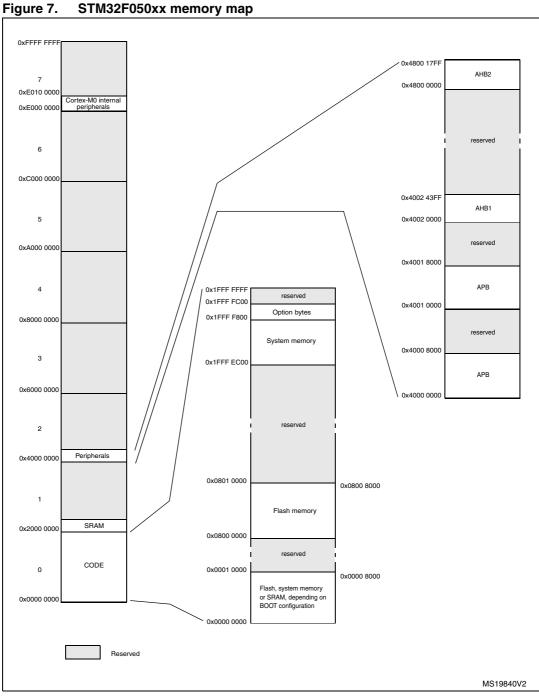

#### **Memory mapping** 5

#### **Electrical characteristics**

- 2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

- 3. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 12: Voltage characteristics* for the maximum allowed input voltage values.

- 5. A positive injection is induced by V<sub>IN</sub>>V<sub>DDA</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ</sub>(PIN) must never be exceeded. Refer also to *Table 12: Voltage characteristics* for the maximum allowed input voltage values. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 51: ADC accuracy*.

- 6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

Table 14. Thermal characteristics

| Symbol           |                                                     |                                             |                   | Ту                     | /p                      |      |

|------------------|-----------------------------------------------------|---------------------------------------------|-------------------|------------------------|-------------------------|------|

|                  | Parameter                                           | Conditions                                  | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit |

|                  |                                                     |                                             | 48 MHz            | 18.4                   | 11.4                    |      |

|                  |                                                     |                                             | 36 MHz            | 13.9                   | 8.9                     |      |

|                  |                                                     |                                             | 32 MHz            | 12.4                   | 7.9                     |      |

|                  |                                                     |                                             | 24 MHz            | 9.9                    | 6.2                     |      |

| laa              | Supply current in Run mode from V <sub>DD</sub>     |                                             | 16 MHz            | 6.6                    | 4.3                     | mA   |

| I <sub>DD</sub>  | supply                                              |                                             | 8 MHz             | 3.3                    | 2.2                     | ШA   |

|                  |                                                     | Running from<br>HSE crystal<br>clock 8 MHz, | 4 MHz             | 1.7                    | 1.6                     |      |

|                  |                                                     |                                             | 2 MHz             | 1.3                    | 1.2                     |      |

|                  |                                                     |                                             | 1 MHz             | 0.8                    | 0.7                     |      |

|                  |                                                     |                                             | 500 kHz           | 0.6                    | 0.6                     |      |

|                  |                                                     | code<br>executing                           | 48 MHz            | 140                    | 140                     |      |

|                  |                                                     | from Flash                                  | 36 MHz            | 109                    | 109                     |      |

|                  |                                                     |                                             | 32 MHz            | 96                     | 96                      |      |

|                  |                                                     |                                             | 24 MHz            | 76                     | 76                      |      |

| I <sub>DDA</sub> | Supply current in Run<br>mode from V <sub>DDA</sub> |                                             | 16 MHz            | 51                     | 51                      | μA   |

| 'DDA             | supply                                              |                                             | 8 MHz             | 1.7                    | 1.7                     | μΛ   |

|                  |                                                     |                                             | 4 MHz             | 1.6                    | 1.6                     |      |

|                  |                                                     |                                             | 2 MHz             | 1.5                    | 1.5                     |      |

|                  |                                                     |                                             | 1 MHz             | 1.1                    | 1.1                     |      |

|                  |                                                     |                                             | 500 kHz           | 1.1                    | 1.1                     |      |

# Table 25. Typical current consumption in Run mode, code with data processing running from Flash

|                  |                                 |                                             |                   | Ту                     |                         |      |

|------------------|---------------------------------|---------------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol           | Parameter                       | Conditions                                  | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit |

|                  |                                 |                                             | 48 MHz            | 10.7                   | 2.4                     |      |

|                  |                                 |                                             | 36 MHz            | 8.1                    | 1.8                     |      |

|                  |                                 |                                             | 32 MHz            | 7.1                    | 1.6                     |      |

|                  |                                 |                                             | 24 MHz            | 5.5                    | 1.3                     |      |

|                  | Supply current in               |                                             | 16 MHz            | 3.7                    | 0.9                     |      |

| I <sub>DD</sub>  | Sleep mode from V <sub>DD</sub> |                                             | 8 MHz             | 1.9                    | 0.5                     | mA   |

|                  | supply                          |                                             | 4 MHz             | 1.5                    | 0.4                     |      |

|                  |                                 | Running from<br>HSE crystal<br>clock 8 MHz, | 2 MHz             | 1.1                    | 0.3                     |      |

|                  |                                 |                                             | 1 MHz             | 0.8                    | 0.3                     |      |

|                  |                                 |                                             | 500 kHz           | 0.6                    | 0.3                     |      |

|                  |                                 |                                             | 125 kHz           | 0.5                    | 0.3                     |      |

|                  |                                 | code executing                              | 48 MHz            | 140                    | 140                     |      |

|                  |                                 | from Flash or<br>RAM                        | 36 MHz            | 109                    | 109                     |      |

|                  |                                 |                                             | 32 MHz            | 96                     | 96                      |      |

|                  |                                 |                                             | 24 MHz            | 76                     | 76                      |      |

|                  | Supply current in               |                                             | 16 MHz            | 51                     | 51                      |      |

| I <sub>DDA</sub> | Sleep mode from                 |                                             | 8 MHz             | 1.7                    | 1.7                     | μA   |

|                  | V <sub>DDA</sub> supply         |                                             | 4 MHz             | 1.6                    | 1.6                     |      |

|                  |                                 |                                             | 2 MHz             | 1.5                    | 1.5                     |      |

|                  |                                 |                                             | 1 MHz             | 1.1                    | 1.1                     |      |

|                  |                                 |                                             | 500 kHz           | 1.1                    | 1.1                     |      |

|                  |                                 |                                             | 125 kHz           | 1.1                    | 1.1                     |      |

# Table 26.Typical current consumption in Sleep mode, code running from Flash or<br/>RAM

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 28*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 12: Voltage characteristics

Table 28.Peripheral current consumption

| Peripheral         | Typical consu   | Unit             |    |

|--------------------|-----------------|------------------|----|

| renpheral          | I <sub>DD</sub> | I <sub>DDA</sub> |    |

| ADC <sup>(1)</sup> | 0.53            | 0.964            |    |

| CRC                | 0.10            | -                |    |

| DBGMCU             | 0.18            | -                |    |

| DMA                | 0.35            | -                |    |

| GPIOA              | 0.48            | -                |    |

| GPIOB              | 0.58            | -                |    |

| GPIOC              | 0.12            | -                |    |

| GPIOF              | 0.06            | -                |    |

| I2C1               | 0.43            | -                |    |

| PWR                | 0.22            | -                |    |

| SPI1/I2S1          | 0.63            | -                |    |

| SYSCFG             | 0.28            |                  |    |

| TIM1               | 1.01            | -                |    |

| TIM2               | 1.00            | -                |    |

| TIM3               | 0.78            | -                | mA |

| TIM6               | 0.32            | -                |    |

| TIM14              | 0.45            | -                |    |

| TIM16              | 0.57            | -                |    |

| TIM17              | 0.59            | -                |    |

| USART1             | 1.07            | -                |    |

| WWDG               | 0.22            | -                |    |

1. ADC is in ready state after setting the ADEN bit in the ADC\_CR register (ADRDY bit in ADC\_ISR is high).

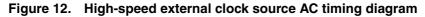

### 6.3.6 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.13*. However, the recommended clock input waveform is shown in *Figure 12: High-speed external clock source AC timing diagram*.

|                                              | nigh-speed external user clock characteristics |            |              |     |             |      |  |  |

|----------------------------------------------|------------------------------------------------|------------|--------------|-----|-------------|------|--|--|

| Symbol                                       | Parameter <sup>(1)</sup>                       | Conditions | Min          | Тур | Max         | Unit |  |  |

| f <sub>HSE_ext</sub>                         | User external clock source<br>frequency        |            | 1            | 8   | 32          | MHz  |  |  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage            |            | $0.7 V_{DD}$ | -   | $V_{DD}$    | v    |  |  |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage             |            | $V_{SS}$     | -   | $0.3V_{DD}$ |      |  |  |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time                        |            | 15           | -   | -           | ns   |  |  |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time                       |            | -            | -   | 20          | 115  |  |  |

Table 29. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

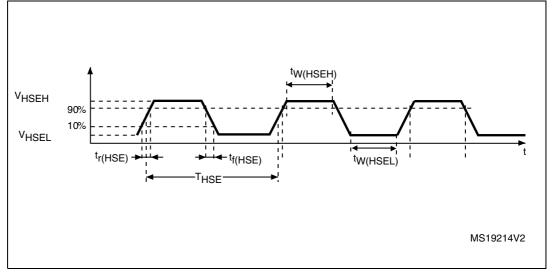

Figure 14. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 32*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter               | Conditions <sup>(1)</sup>                          | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-------------------------|----------------------------------------------------|--------------------|-----|--------------------|------|

|                                     |                         | LSEDRV[1:0]=00<br>lower driving capability         | -                  | 0.5 | 0.9                |      |

|                                     |                         | LSEDRV[1:0]= 01<br>medium low driving capability   | -                  | -   |                    |      |

| I <sub>DD</sub>                     | LSE current consumption | LSEDRV[1:0] = 10<br>medium high driving capability | -                  | -   | 1.3                | μA   |

|                                     |                         | LSEDRV[1:0]=11<br>higher driving capability        | -                  | -   | 1.6                |      |

|                                     |                         | LSEDRV[1:0]=00<br>lower driving capability         | 5                  | -   | -                  |      |

|                                     | Oscillator              | LSEDRV[1:0]= 01<br>medium low driving capability   | 8                  | -   | -                  |      |

| 9m                                  | transconductance        | LSEDRV[1:0] = 10<br>medium high driving capability | 15                 | -   | -                  | µA/V |

|                                     |                         | LSEDRV[1:0]=11<br>higher driving capability        | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time            | V <sub>DD</sub> is stabilized                      | -                  | 2   | -                  | S    |

Table 32. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 13: Current characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 13: Current characteristics*).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 15: General operating conditions*. All I/Os are CMOS and TTL compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                                                  | Min                  | Max | Unit |

|-----------------------------------|------------------------------------------------------------|-------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin                    | CMOS port <sup>(2)</sup>                                    | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -0.4 | -   | V    |

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin                    | TTL port <sup>(2)</sup>                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                   | I <sub>IO</sub> =+ 8mA<br>2.7 V < V <sub>DD</sub> < 3.6 V   | 2.4                  | -   | V    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin                    | I <sub>IO</sub> = +20 mA                                    | -                    | 1.3 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin                   | 2.7 V < V <sub>DD</sub> < 3.6 V                             | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin                    | I <sub>IO</sub> = +6 mA                                     | -                    | 0.4 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin                   | 2 V < V <sub>DD</sub> < 2.7 V                               | V <sub>DD</sub> -0.4 | -   | v    |

| V <sub>OLFM+</sub> <sup>(1)</sup> | Output low level voltage for an FTf I/O<br>pin in FM+ mode | I <sub>IO</sub> = +20 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | -                    | 0.4 | V    |

Table 46. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 13: Current characteristics* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 13: Current characteristics* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Data based on design simulation only. Not tested in production.

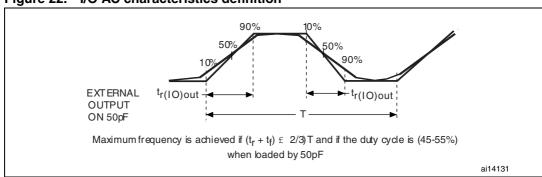

#### Figure 22. I/O AC characteristics definition

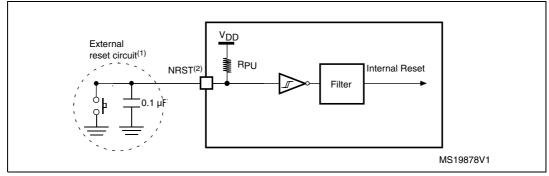

### 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see *Table 45: I/O static characteristics*).

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under ambient temperature and VDD supply voltage conditions summarized in *Table 15: General operating conditions*.

| Symbol                               | Parameter                                       | Conditions        | Min  | Тур | Max                  | Unit |

|--------------------------------------|-------------------------------------------------|-------------------|------|-----|----------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST input low level voltage                    |                   | -0.3 | -   | 0.8                  | V    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST input high level voltage                   |                   | 2    | -   | V <sub>DD</sub> +0.3 | ~    |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage<br>hysteresis      |                   | -    | 200 | -                    | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 25   | 40  | 55                   | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST input filtered pulse                       |                   | -    | -   | 100                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST input not filtered pulse                   |                   | 300  | -   | -                    | ns   |

| Table 48. | <b>NRST</b> pin | characteristics |

|-----------|-----------------|-----------------|

|-----------|-----------------|-----------------|

1. Guaranteed by design, not tested in production.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

#### Figure 23. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 48. Otherwise the reset will not be taken into account by the device.

## 6.3.16 Temperature sensor characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>25</sub>                       | Voltage at 25 °C                               | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>     | Startup time                                   | 4    | -    | 10   | μs    |

| T <sub>S_temp</sub> <sup>(1)(2)</sup> | ADC sampling time when reading the temperature | 17.1 | -    | -    | μs    |

1. Guaranteed by design, not tested in production.

2. Shortest sampling time can be determined in the application by multiple iterations.

# 6.3.17 V<sub>BAT</sub> monitoring characteristics

#### Table 53. V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                           |   | Тур | Max | Unit |

|---------------------------------------|---------------------------------------------------------------------|---|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                |   | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                               |   | 2   | -   |      |

| Er <sup>(1)</sup>                     | Error on Q                                                          |   | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(1)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1mV accuracy | 5 | -   | -   | μs   |

1. Guaranteed by design, not tested in production.

2. Shortest sampling time can be determined in the application by multiple iterations.

### 6.3.18 Timer characteristics

The parameters given in *Table 54* are guaranteed by design.

Refer to *Section 6.3.13: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                | Parameter                                       | Conditions                    | Min  | Мах                     | Unit                 |

|-----------------------|-------------------------------------------------|-------------------------------|------|-------------------------|----------------------|

| t <sub>res(TIM)</sub> | Timer resolution time                           |                               | 1    | -                       | t <sub>TIMxCLK</sub> |

|                       |                                                 | f <sub>TIMxCLK</sub> = 48 MHz | 20.8 | -                       | ns                   |

| f <sub>EXT</sub>      | Timer external clock<br>frequency on CH1 to CH4 |                               | 0    | f <sub>TIMxCLK</sub> /2 | MHz                  |

|                       |                                                 | f <sub>TIMxCLK</sub> = 48 MHz | 0    | 24                      | MHz                  |

| Res <sub>TIM</sub>    | Timer resolution                                | TIMx (except TIM2)            | -    | 16                      | bit                  |

|                       |                                                 | TIM2                          | -    | 32                      |                      |

Table 54.

TIMx<sup>(1)</sup> characteristics

| Symbol                                  | Parameter                        | Conditions                                            | Min   | Max   | Unit |  |

|-----------------------------------------|----------------------------------|-------------------------------------------------------|-------|-------|------|--|

| <sup>f</sup> cк                         | I <sup>2</sup> S clock frequency | Master mode (data: 16 bits, Audio frequency = 48 kHz) | 1.597 | 1.601 | MHz  |  |

| 1/t <sub>c(CK)</sub>                    |                                  | Slave mode                                            | 0     | 6.5   |      |  |

| t <sub>r(CK)</sub>                      | I <sup>2</sup> S clock rise time | Capacitive load $C_1 = 15  \text{pF}$                 | -     | 10    |      |  |

| t <sub>f(CK)</sub>                      | I <sup>2</sup> S clock fall time | $-$ Capacitive load $C_L = 15 \text{ pr}$             | -     | 12    |      |  |

| t <sub>w(CKH)</sub> <sup>(1)</sup>      | I2S clock high time              | Master f <sub>PCLK</sub> = 16 MHz, audio              | 306   | -     |      |  |

| t <sub>w(CKL)</sub> <sup>(1)</sup>      | I2S clock low time               | frequency = 48 kHz                                    | 312   | -     |      |  |

| t <sub>v(WS)</sub> <sup>(1)</sup>       | WS valid time                    | Master mode                                           | 2     | -     | ns   |  |

| t <sub>h(WS)</sub> <sup>(1)</sup>       | WS hold time                     | Master mode                                           | 2     | -     |      |  |

| t <sub>su(WS)</sub> <sup>(1)</sup>      | WS setup time                    | Slave mode                                            | 7     | -     |      |  |

| t <sub>h(WS)</sub> <sup>(1)</sup>       | WS hold time                     | Slave mode                                            | 0     | -     | 1    |  |

| DuCy(SCK)                               | I2S slave input clock duty cycle | clock duty Slave mode                                 |       | 75    | %    |  |

| t <sub>su(SD_MR)</sub> <sup>(1)</sup>   | Data input setup time            | Master receiver                                       | 6     | -     |      |  |

| t <sub>su(SD_SR)</sub> <sup>(1)</sup>   | Data input setup time            | Slave receiver                                        | 2     | -     |      |  |

| t <sub>h(SD_MR)</sub> <sup>(1)(2)</sup> | Data innut hald time             | Master receiver                                       | 4     | -     |      |  |

| t <sub>h(SD_SR)</sub> (1)(2)            | Data input hold time             | Slave receiver                                        | 0.5   | -     |      |  |

| t <sub>v(SD_ST)</sub> (1)(2)            | Data output valid time           | Slave transmitter (after enable edge)                 | -     | 20    | ns   |  |

| t <sub>h(SD_ST)</sub> <sup>(1)</sup>    | Data output hold time            | Slave transmitter (after enable edge)                 | 13    | -     |      |  |

| t <sub>v(SD_MT)</sub> <sup>(1)(2)</sup> | Data output valid time           | Master transmitter (after enable edge)                | -     | 4     |      |  |

| t <sub>h(SD_MT)</sub> <sup>(1)</sup>    | Data output hold time            | Master transmitter (after enable edge)                | 0     | -     |      |  |

Table 60.I<sup>2</sup>S characteristics

1. Data based on design simulation and/or characterization results, not tested in production.

2. Depends on  $f_{PCLK}.$  For example, if  $f_{PCLK}{=}8$  MHz, then  $T_{PCLK}{=}1/f_{PLCLK}{=}125$  ns.

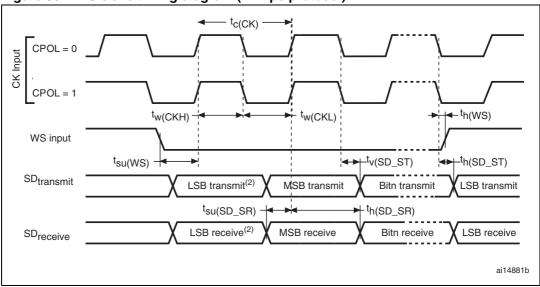

Figure 30. I2S slave timing diagram (Philips protocol)

- 1. Measurement points are done at CMOS levels:  $0.3 \times VDD$  and  $0.7 \times VDD$ .

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

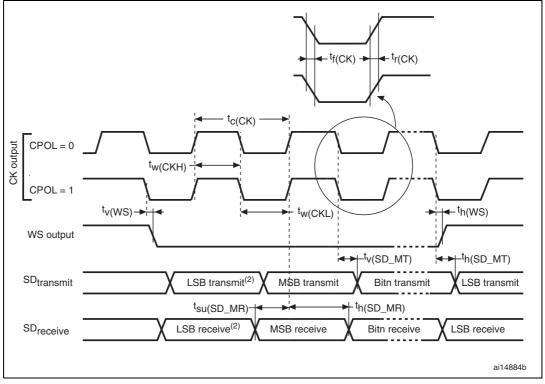

#### Figure 31. I2S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

Figure 34. UFQFPN32 - 5 x 5 mm, 32-lead ultra thin fine pitch quad flat no-lead package outline

1. Drawing is not to scale.

2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

3. There is an exposed die pad on the underside of the UFQFPN package. This pad is used for the device ground and must be connected. It is referred to as pin 0 in *Table 8: Pin definitions*.

| Table 62. | UFQFPN32 – 5 x 5 mm, 32-lead ultra thin fine pitch quad flat no-lead package |

|-----------|------------------------------------------------------------------------------|

|           | mechanical data                                                              |

| Dim  |      | millimeters |      | inches <sup>(1)</sup> |        |        |

|------|------|-------------|------|-----------------------|--------|--------|

| Dim. | Min  | Тур         | Max  | Min                   | Тур    | Max    |

| А    | 0.5  | 0.55        | 0.6  | 0.0197                | 0.0217 | 0.0236 |

| A1   | 0.00 | 0.02        | 0.05 | 0                     | 0.0008 | 0.0020 |

| A3   |      | 0.152       |      |                       | 0.006  |        |

| b    | 0.18 | 0.23        | 0.28 | 0.0071                | 0.0091 | 0.0110 |

| D    | 4.90 | 5.00        | 5.10 | 0.1929                | 0.1969 | 0.2008 |

| D2   |      | 3.50        |      |                       | 0.1378 |        |

| E    | 4.90 | 5.00        | 5.10 | 0.1929                | 0.1969 | 0.2008 |

| E2   | 3.40 | 3.50        | 3.60 | 0.1339                | 0.1378 | 0.1417 |

| е    |      | 0.500       |      |                       | 0.0197 |        |

| L    | 0.30 | 0.40        | 0.50 | 0.0118                | 0.0157 | 0.0197 |

| ddd  |      | 0.08        |      |                       | 0.0031 |        |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

### 7.2 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 15: General operating conditions on page 39.*

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma ~(\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                         | Value | Unit |

|-----------------|-------------------------------------------------------------------|-------|------|

| Θ <sub>JA</sub> | <b>Thermal resistance junction-ambient</b><br>LQFP48 - 7 × 7 mm   | 55    | °C/W |

|                 | <b>Thermal resistance junction-ambient</b><br>UFQFPN32 - 5 × 5 mm | 38    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>UFQFPN28 - 4 × 4 mm | 118   | C/ W |

|                 | Thermal resistance junction-ambient<br>TSSOP20                    | 110   |      |

#### 7.2.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

#### 7.2.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Part numbering*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F05xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

Doc ID 023683 Rev 1

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 80$  °C (measured according to JESD51-2),  $I_{DDmax} = 50$  mA,  $V_{DD} = 3.5$  V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL} = 8$  mA,  $V_{OL} = 0.4$  V and maximum 8 I/Os used at the same time in output at low level with  $I_{OL} = 20$  mA,  $V_{OL} = 1.3$  V

$P_{INTmax} = 50 \text{ mA} \times 3.5 \text{ V} = 175 \text{ mW}$

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} + 8 \times 20 \text{ mA} \times 1.3 \text{ V} = 272 \text{ mW}$

This gives:  $P_{INTmax} = 175 \text{ mW}$  and  $P_{IOmax} = 272 \text{ mW}$ :

```

P_{Dmax} = 175 + 272 = 447 \text{ mW}

```

Using the values obtained in *Table 65* T<sub>Jmax</sub> is calculated as follows:

For LQFP48, 55 °C/W

T<sub>.lmax</sub> = 80 °C + (55°C/W × 447 mW) = 80 °C + 24.585 °C = 104.585 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ) see *Table 15: General operating conditions on page 39.*

In this case, parts must be ordered at least with the temperature range suffix 6 (see *Section 8: Part numbering*).

Note: With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 7).

Suffix 6:  $T_{Amax} = T_{Jmax} - (55^{\circ}C/W \times 447 \text{ mW}) = 105-24.585 = 80.415 ^{\circ}C$ Suffix 7:  $T_{Amax} = T_{Jmax} - (55^{\circ}C/W \times 447 \text{ mW}) = 125-24.585 = 100.415 ^{\circ}C$

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 100$  °C (measured according to JESD51-2),  $I_{DDmax} = 20$  mA,  $V_{DD} = 3.5$  V, maximum 20 I/Os used at the same time in output at low level with  $I_{OI} = 8$  mA,  $V_{OI} = 0.4$  V

$P_{INTmax} = 20 \text{ mA} \times 3.5 \text{ V} = 70 \text{ mW}$

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 64 \text{ mW}$ :

$P_{Dmax} = 70 + 64 = 134 \text{ mW}$

Thus: P<sub>Dmax</sub> = 134 mW

Using the values obtained in *Table 65* T<sub>Jmax</sub> is calculated as follows:

For LQFP48, 55 °C/W

$T_{Jmax} = 100 \text{ °C} + (55 \text{ °C/W} \times 134 \text{ mW}) = 100 \text{ °C} + 7.37 \text{ °C} = 107.37 \text{ °C}$

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Part numbering*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Doc ID 023683 Rev 1